# **MPQ7231**

MPSafe<sup>™</sup> 42V, 3A Buck or 2.4A Buck-Boost, Synchronous Infrared LED Driver, AEC-Q100 Qualified

#### DESCRIPTION

The MPQ7231 is a fixed-frequency, constant current, infrared (IR) LED driver with integrated eye safety features. The device operates across a 6V to 42V input voltage ( $V_{IN}$ ) range. It can be configured to either buck or buck-boost mode, and achieve up to 3A and 2.4A of peak current ( $I_{LED\_PEAK}$ ), respectively. The MPQ7231 is ideal for driving one or two IR LEDs.

The MPQ7231 provides ultra-low on resistance (R<sub>DS(ON)</sub>) MOSFETs, with a 44m $\Omega$  high-side MOSFET (HS-FET) and 40m $\Omega$  low-side MOSFET (LS-FET), using MPS's advanced BCD FET technology to minimize ohmic losses. This improves the total system loss up to a factor of 10 times compared to the traditional, non-synchronous architecture with a Schottky diode. As a result, the system runs cooler and is significantly more efficient.

The MPQ7231 can support a 10Hz to 2kHz pulse-width modulation (PWM) dimming frequency range, which is compatible with IR LED applications that require 30fps, 60fps, or 120fps dimming. Constant frequency hysteretic control mode provides extremely fast transient response without loop compensation. Frequency spread spectrum (FSS) modulation improves EMC performance.

Eye-safety features include LED current limiting and factory preset dimming on-time limits (1ms, 3ms, or 5ms) to support the system in achieving ASIL requirements. The MPQ7231 provides a dedicated fault pin as well as protection features including LED short to battery (or ground) protection, LED open protection, over-current protection (OCP) with latch, thermal derating, and thermal shutdown.

The MPQ7231 requires a minimal number of readily available, standard external components to ensure a simple, compact, and efficient system design. It is available in a space-saving QFN-19 (3mmx4mm) package.

#### **FEATURES**

- Built for Infrared (IR) LED Applications:

- 10Hz to 2kHz Pulse-Width Modulation (PWM) Dimming Frequency

- Compatible with 30fps, 60fps, and 120fps Dimming

- Improved Efficiency and Thermals:

- Integrated Current-Sense Resistor

- $\circ$  44mΩ/40mΩ On Resistance (R<sub>DS(ON)</sub>) Internal MOSFETs

- Optimized for EMC/EMI:

- 2.4MHz (Buck) or 1.25MHz (Buck-Boost) Switching Frequency (f<sub>SW</sub>) with Frequency Spread Spectrum (FSS)

- EMI Reduction Techniques

- Functional Safety:

- Eye Safety Features Include:

- LED Current Limit

- Dimming On Time Limit (1ms, 3ms, or 5ms)

- Functional Safety Documents Available

- Fault Indication for LED Short (Battery and Ground), LED Open, OVP, and Thermal Shutdown

- Over-Current Protection (OCP) with Latch

- Additional Features:

- Wide 6V to 42V Operating V<sub>IN</sub> Range

- 3A Buck or 2.4A Buck-Boost I<sub>L\_PEAK</sub>

- Configurable Thermal Derating via NTC Remote Temperature Sensing

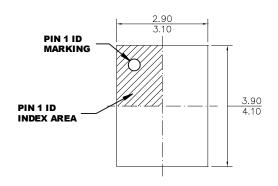

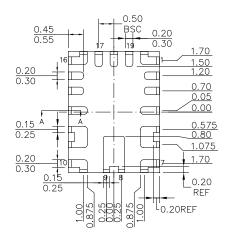

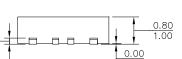

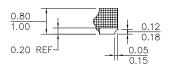

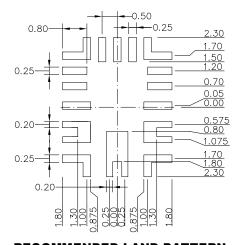

- Available in a QFN-19 (3mmx4mm)

Package with Wettable Flanks

- Available in AEC-Q100 Grade 1

#### **APPLICATIONS**

- Driver Monitoring Systems (DMS)

- IR Illumination for Automotive Cameras

- Surveillance Systems

All MPS parts are lead-free, halogen-free, and adhere to the RoHS directive. For MPS green status, please visit the MPS website under Quality Assurance. "MPS", the MPS logo, and "Simple, Easy Solutions" are trademarks of Monolithic Power Systems, Inc. or its subsidiaries.

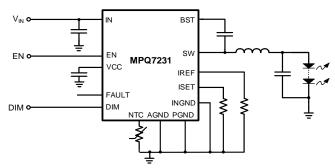

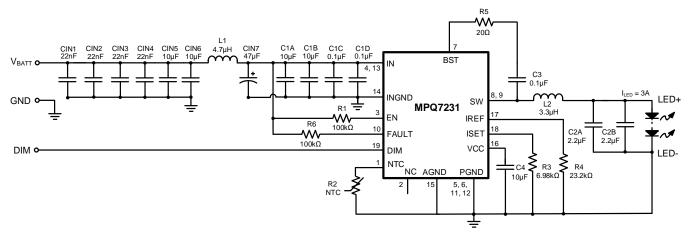

#### **TYPICAL APPLICATION**

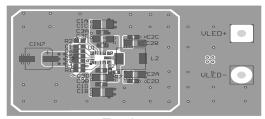

Figure 1: Typical Application Circuit (Buck Topology, ≥14.7kΩ R<sub>IREF</sub> to Select Mode)

Efficiency vs. Input Voltage vs.

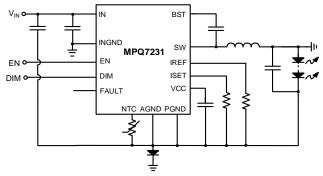

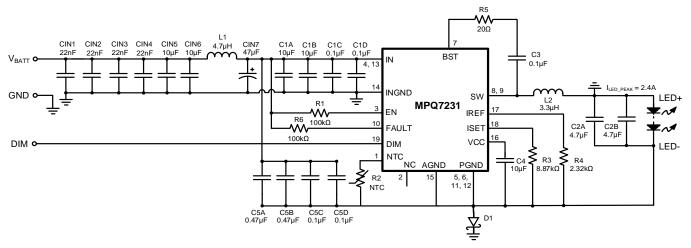

Figure 2: Typical Application Circuit (Buck-Boost Topology, ≤9.09kΩ R<sub>IREF</sub> to Select Mode)

#### **ORDERING INFORMATION**

| Part Number*           | Package          | Top Marking | MSL Rating** |

|------------------------|------------------|-------------|--------------|

| MPQ7231GLE-D00-AEC1*** |                  |             |              |

| MPQ7231GLE-D10-AEC1*** | OEN 10 (2mmy/mm) | See Below   | 4            |

| MPQ7231GLE-D30-AEC1*** | QFN-19 (3mmx4mm) |             | I            |

| MPQ7231GLE-D50-AEC1*** |                  |             |              |

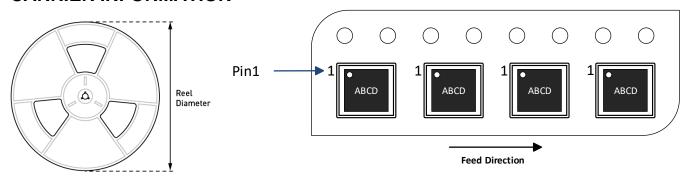

<sup>\*</sup> For Tape & Reel, add suffix -Z (e.g. MPQ7231GLE-D00-AEC1-Z).

#### **TOP MARKING**

MPYW 7231 LLL E

MP: MPS prefix Y: Year code W: Week code 7231: Part number LLL: Lot number E: Wettable lead flank

#### **PACKAGE REFERENCE**

|           | TOP VIEW          |               |

|-----------|-------------------|---------------|

|           | DIM ISET IREF     |               |

| NTC 1     | 19                | 16 VCC        |

| NC [2]    |                   | (<br>(15 AGND |

| EN 3 )    |                   | ( INGND       |

| VIN 4)    |                   | (13) VIN      |

| PGND 5    | <i></i>           | 12 PGND       |

| PGND 6    |                   | 11 PGND       |

| BST 7 7 1 | <br>         <br> | FAULT         |

| QI        | FN-19 (3mmx4m     | m)            |

<sup>\*\*</sup> Moisture Sensitivity Level Rating

\*\*\* Wettable Flank

# **PIN FUNCTIONS**

| PIN FUN<br>Pin # | Name  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|------------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIN#             | Name  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 1                | NTC   | <b>Remote temperature sense.</b> Connect a negative temperature coefficient (NTC) resistor network (R <sub>NTC</sub> ) between the NTC and AGND pins to configure the temperature derating starting point. NTC short to PGND as well as NTC short to AGND are protected.                                                                                                                                                                                                                                                                                                                                                                                          |

| 2                | NC    | Not connected. Connect the NC pin to PGND on the board externally.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 3                | EN    | <b>Enable.</b> Pull the EN pin above 1V to enable the chip; pull EN below 0.9V to shut down the chip. Connect EN to the VIN pin via a resistor for automatic start-up once $V_{IN}$ and $V_{CC}$ exceed their respective under-voltage lockout (UVLO) thresholds. EN is pulled low via an internal resistor, meaning the chip is off by default if EN is floating.                                                                                                                                                                                                                                                                                                |

| 4, 13            | VIN   | <b>Supply voltage.</b> The MPQ7231 operates from a 6V to 42V input voltage ( $V_{IN}$ ) and requires an input capacitor ( $C_{IN}$ ) to decouple the input rail. Connect the VIN pin to the input rail using a wide PCB trace.                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 5, 6, 11, 12     | PGND  | <b>Power ground.</b> The PGND pin is the power device's reference ground, including the configuration pins, and requires careful consideration during PCB layout. PGND is also used to dissipate the thermal heat.                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 7                | BST   | <b>Bootstrap.</b> The BST pin requires a capacitor connected between the SW and BST pins to form a floating supply across the high-side MOSFET (HS-FET) driver. Place a resistor between SW and the BST capacitor (C <sub>BST</sub> ) to reduce the SW spike voltage and improve EMI performance.                                                                                                                                                                                                                                                                                                                                                                 |

| 8, 9             | SW    | <b>Switch output.</b> The SW pin is the middle point of the HS-FET and low-side MOSFET (LS-FET). It is recommended to use a wide trace and overall small-size SW node for the PCB to reduce noise coupling and improve EMI.                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 10               | FAULT | <b>Fault indicator.</b> The FAULT pin is an open-drain output with an internal, $300k\Omega$ pull-up resistor connected to VIN and a $4M\Omega$ pull-down resistor connected to INGND. Pull FAULT low if an LED short, LED open, over-temperature (OT), over-current (OC), or false mode detection condition occurs. Connect FAULT to VIN continuously using a pull-up resistor.                                                                                                                                                                                                                                                                                  |

| 14               | INGND | <b>VIN, EN, DIM, and FAULT ground for buck-boost topology.</b> For buck topology, connect the INGND pin to PGND or AGND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 15               | AGND  | <b>Analog ground.</b> The AGND pin is the reference ground of the logic circuit. Connect AGND to the PGND pin via an external trace.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 16               | VCC   | Internal bias supply. The VCC pin supplies power to the internal control circuit and gate drivers. Place a ≥3µF decoupling capacitor to ground, close to VCC. Considering the capacitance derating, a 10µF/10V or 16V X7R capacitor is strongly recommended.                                                                                                                                                                                                                                                                                                                                                                                                      |

| 17               | IREF  | <b>Mode selection and NTC reference current setting.</b> Connect a $\leq 9.09 k\Omega$ resistor at the IREF pin to select buck-boost mode; connect a $\geq 14.7 k\Omega$ at IREF to select buck mode. The IREF pin voltage (V <sub>IREF</sub> ) is set to 0.57V after mode detection finishes. Connect a resistor (R <sub>IREF</sub> ) from IREF to ground to obtain a 0.57V/R <sub>IREF</sub> reference current. If IREF is shorted to ground or an IREF open fault is detected, the part latches off and FAULT asserts. The NTC pin's current is 50 or 5 times of IREF's reference current (I <sub>REF</sub> ) for buck mode and buck-boost mode, respectively. |

| 18               | ISET  | <b>LED current setting.</b> Connect an external resistor from the ISET pin to ground to set the LED average current. If ISET is shorted to ground or a SET open fault is detected, the part latches off and FAULT asserts.                                                                                                                                                                                                                                                                                                                                                                                                                                        |

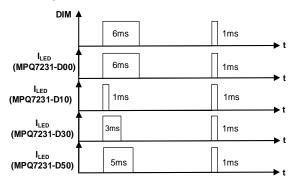

| 19               | DIM   | <b>Dimming control.</b> Apply an external pulse-width modulation (PWM) signal to the DIM pin for PWM dimming. Pull the DIM pin above 1V to turn dimming on; pull DIM below 0.9V to turn dimming off. Ensure that the dimming on time is at least 100µs to avoid mistriggering FAULT. A long dimming high signal on DIM does not generate a FAULT. LED on time is limited to 1ms, 3ms, and 5ms, based on different trim options. The dimming off time can last as long as 100ms, allowing the device to support a low to 10Hz dimming frequency for 30Hz IR LED driver applications.                                                                               |

| ABSOLUTE MAXIMUM RATINGS (1)                                                                                                     |

|----------------------------------------------------------------------------------------------------------------------------------|

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                             |

| V <sub>DIM</sub> - V <sub>PGND</sub> , V <sub>AGND</sub> 0.3V to +50V<br>V <sub>SW</sub> - V <sub>PGND</sub> , V <sub>AGND</sub> |

| $\begin{array}{llllllllllllllllllllllllllllllllllll$                                                                             |

| Lead temperature                                                                                                                 |

| ESD Ratings Human body model (HBM)Class 2 (3) Charged-device model (CDM) Class C2b (4)                                           |

| Recommended Operating Conditions                                                                                                 |

| Supply voltage (V <sub>IN</sub> - V <sub>PGND</sub> )6V to 42V LED current (I <sub>LED</sub> ) at buck mode                      |

| Up to 3A Continuous I <sub>LED</sub> at buck-boost mode                                                                          |

| Peak LED current (I <sub>LED_PEAK</sub> ) at buck-boost mode                                                                     |

| 7 37 22 22 27 27 27 27 27 27 27 27 27 27 27                                                                                      |

| Thermal Resistance | $oldsymbol{	heta}$ JA | $oldsymbol{	heta}$ JC |

|--------------------|-----------------------|-----------------------|

| QFN-19 (3mmx4mm)   |                       |                       |

| JESD51-7           | 48                    | 11°C/W (5)            |

| EVQ7231-L-00A      | 32                    | 6.°C/W <sup>(6)</sup> |

#### Notes:

- 1) Exceeding these ratings may damage the device.

- 2) The maximum allowable power dissipation is a function of the maximum junction temperature, T<sub>J</sub> (MAX), the junction-to-ambient thermal resistance, θ<sub>JA</sub>, and the ambient temperature, T<sub>A</sub>. The maximum allowable continuous power dissipation at any ambient temperature is calculated by P<sub>D</sub> (MAX) = (T<sub>J</sub> (MAX) T<sub>A</sub>) / θ<sub>JA</sub>. Exceeding the maximum allowable power dissipation can produce an excessive die temperature, which causes the regulator to go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

- 3) Per AEC-Q100-002.

- 4) Per AEC-Q100-011.

- 5) Measured on a JESD51-7, 4-layer PCB. The values given in this table are only valid for comparison with other packages and cannot be used for design purposes. These values were calculated in accordance with JESD51-7, and simulated on a specified JEDEC board. They do not represent the performance obtained in an actual application. The  $\theta_{\rm JC}$  value shows the thermal resistance from the junction-to-case bottom.

- 6) Measured on an MPS standard EVB for the MPQ7231: a 4-layer, 2oz PCB (83.5mmx83.5mm). The  $\theta_{JC}$  value shows the thermal resistance from the junction-to-case top.

#### **ELECTRICAL CHARACTERISTICS**

$V_{IN}$  = 13.5V,  $V_{EN}$  = 2V,  $T_J$  = -40°C to +150°C, typical values are at  $T_J$  = 25°C, unless otherwise noted. BUCK MODE

| Parameter                            | Symbol                   | Condition                                                                    | Min   | Тур   | Max   | Units           |

|--------------------------------------|--------------------------|------------------------------------------------------------------------------|-------|-------|-------|-----------------|

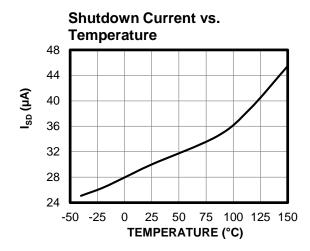

| Shutdown supply current              | I <sub>SD</sub>          | $V_{EN} = 0V$                                                                |       | 30    | 80    | μΑ              |

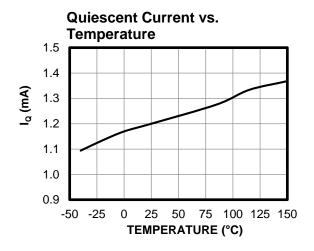

| Quiescent supply current             | lα                       | $V_{EN} = 2V$ , no switching, float IREF (exclude $I_{REF}$ and NTC current) |       | 1.2   | 2     | mA              |

|                                      |                          | FAULT latch                                                                  |       |       | 2     | mA              |

| High-side MOSFET                     | R <sub>DS(ON)_HS</sub>   | $V_{BST-SW} = 5V$ , $R_{ISET} = 10.5k\Omega$                                 |       | 44    | 85    | mΩ              |

| (HS-FET) on resistance               | IXDS(ON)_HS              | $V_{BST-SW} = 5V$ , $R_{ISET} = 40.2k\Omega$                                 |       | 85    | 160   | mΩ              |

| Low-side MOSFET                      | R <sub>DS(ON)_LS</sub>   | $V_{CC} = 5.2V$ , $R_{ISET} = 10.5k\Omega$                                   |       | 40    | 80    | mΩ              |

| (LS-FET) on resistance               | INDS(ON)_LS              | $V_{CC} = 5.2V$ , $R_{ISET} = 40.2k\Omega$                                   |       | 80    | 150   | mΩ              |

| Switch leakage                       | low we                   | V <sub>EN</sub> = 0V, V <sub>SW</sub> =13.5V, T <sub>J</sub> = 25°C          |       |       | 1     | μA              |

| Switch leakage                       | Isw_LKG                  | $V_{EN} = 0V$ , $V_{SW} = 13.5V$                                             |       |       | 5     | μA              |

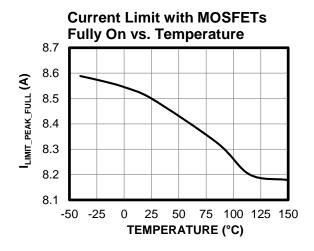

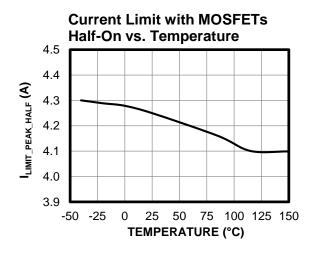

| Peak current limit (7)               | Lunez pene               | $R_{ISET} = 40.2k\Omega$                                                     | 3.61  | 4.25  | 4.89  | Α               |

| reak current iiniit 🗥                | ILIMIT_PEAK              | $R_{ISET} = 10.5k\Omega$                                                     | 6.85  | 8     | 9.15  | Α               |

| Zero-current detection (ZCD) (7)     |                          |                                                                              |       | 50    |       | mA              |

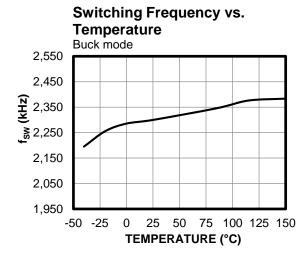

| Switching frequency                  | fsw                      | FSS activated                                                                | 2000  | 2400  | 2800  | kHz             |

| Minimum on time (7)                  | ton_min                  |                                                                              |       | 55    | 80    | ns              |

| Minimum off time (7)                 | toff_min                 |                                                                              |       | 75    | 100   | ns              |

| Maximum duty cycle (7)               | D <sub>MAX</sub>         | Low-dropout                                                                  | 95    | 98    |       | %               |

| Frequency spread spectrum (FSS) (7)  |                          |                                                                              |       | 15    |       | kHz             |

| FSS range (7)                        |                          |                                                                              |       | ±10%  |       | f <sub>SW</sub> |

| LED assessed                         |                          | $R_{ISET} = 10.5k\Omega$ , $T_J = 25$ °C to $100$ °C                         | 1.9   | 2     | 2.1   | Α               |

| LED current                          | ILED                     | $R_{ISET} = 10.5k\Omega$                                                     | 1.7   |       | 2.3   | Α               |

| LED current threshold for cut MOSFET | ILED_CUT                 |                                                                              |       | 800   | 950   | mA              |

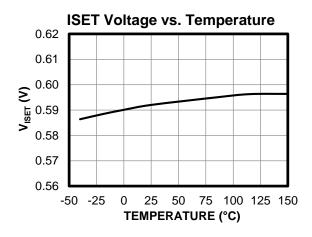

| ISET voltage                         | VISET                    | I <sub>ISET</sub> = 45µA                                                     | 0.573 | 0.592 | 0.606 | V               |

| ISET current threshold for           |                          | ILED < ILED_CUT                                                              | 180   | 220   | 260   | μA              |

| pin short                            |                          | ILED > ILED_CUT                                                              | 270   | 330   | 390   | μA              |

| ISET current threshold for pin open  |                          |                                                                              | 0.5   | 1.4   | 5     | μΑ              |

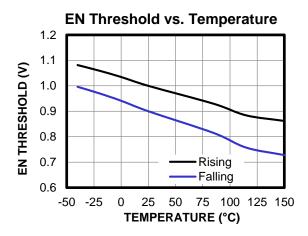

| EN rising threshold                  | V <sub>EN_RISING</sub>   | Ven - Vingnd                                                                 |       | 1     | 1.6   | V               |

| EN falling threshold                 | V <sub>EN_FALLING</sub>  | V <sub>EN</sub> - V <sub>INGND</sub>                                         | 0.7   | 0.9   |       | V               |

| EN threshold hysteresis              | V <sub>EN_HYS</sub>      | Ven - Vingnd                                                                 |       | 100   |       | mV              |

| EN language account of               | 1                        | VEN - VINGND = 2V                                                            |       | 2     | 8     | μA              |

| EN input current                     | IEN                      | VEN - VINGND = 0V                                                            |       | 0     | 0.2   | μA              |

| DIM rising threshold                 | V <sub>DIM_RISING</sub>  | V <sub>DIM</sub> - V <sub>INGND</sub>                                        |       | 1     | 1.6   | V               |

| DIM falling threshold                | V <sub>DIM_FALLING</sub> | Vdim - Vingnd                                                                | 0.7   | 0.9   |       | V               |

| DIM threshold hysteresis             | V <sub>DIM_HYS</sub>     | Vdim - Vingnd                                                                |       | 100   |       | mV              |

© 2023 MPS. All Rights Reserved.

$V_{IN}$  = 13.5V,  $V_{EN}$  = 2V,  $T_J$  = -40°C to +150°C, typical values are at  $T_J$  = 25°C, unless otherwise noted. BUCK MODE

| Parameter                                                      | Symbol                   | Condition                                             | Min  | Тур  | Max  | Units |

|----------------------------------------------------------------|--------------------------|-------------------------------------------------------|------|------|------|-------|

| DIM on time limit of the MPQ7231GLE-D10                        |                          |                                                       | 0.8  | 1    | 1.2  | ms    |

| DIM on time limit of the MPQ7231GLE-D30                        | t <sub>DIM_ON</sub>      |                                                       | 2.4  | 3    | 3.6  | ms    |

| DIM on time limit of the MPQ7231GLE-D50                        |                          |                                                       | 4    | 5    | 6    | ms    |

| DIM input current                                              | $I_{DIM}$                | $V_{DIM} - V_{INGND} = 2V$                            |      | 2    | 8    | μΑ    |

| Divi input current                                             | IDIM                     | V <sub>DIM</sub> - V <sub>INGND</sub> = 0V            |      | 0    | 0.2  | μΑ    |

| DIM turn-off delay (7)                                         | tdim_d_off               |                                                       | 100  |      |      | ms    |

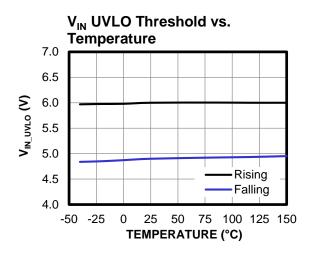

| V <sub>IN</sub> under-voltage lockout (UVLO) rising threshold  | VIN_UVLO_VTH_R           | Vin - Vingnd                                          | 5.75 | 6    | 6.25 | V     |

| V <sub>IN</sub> UVLO falling threshold                         | VIN_UVLO_VTH_F           | Vin - Vingnd                                          | 4.4  | 4.9  | 5.2  | V     |

| V <sub>IN</sub> UVLO hysteresis<br>threshold                   | VIN_UVLO_HYS             | Vin - Vingnd                                          |      | 1.1  |      | V     |

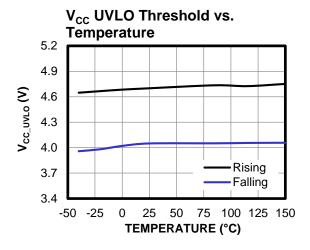

| Vcc UVLO rising threshold                                      | Vcc_uvlo_vth_r           | Vcc - Vagnd                                           | 4.4  | 4.7  | 5    | V     |

| Vcc UVLO falling threshold                                     | Vcc_uvlo_vth_f           | Vcc - Vagnd                                           | 3.4  | 4.05 | 4.7  | V     |

| V <sub>CC</sub> UVLO hysteresis threshold                      | Vcc_uvlo_hys             | Vcc - Vagnd                                           |      | 650  |      | mV    |

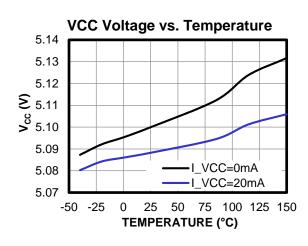

| VCC regulator                                                  | Vcc                      | Icc = 0mA                                             | 4.9  | 5.1  | 5.3  | V     |

| VCC load regulation                                            |                          | Icc = 20mA                                            | 4.7  |      |      | V     |

| VCC maximum current ability                                    |                          | $V_{CC} = V_{CC\_UVLO} + 100 \text{mV},$ no switching | 50   | 80   | 120  | mA    |

| VCC source current ability (7)                                 |                          | Vcc = Vcc_uvlo + 100mV, switching                     |      | 25   |      | mA    |

| Output under-voltage (UV) threshold                            | Vuv_vth                  |                                                       | 0.6  | 1.2  | 1.7  | V     |

| LED low current threshold                                      |                          | ILED_SETTING < ILED_CUT                               | 85   | 100  | 130  | mA    |

| LLD low current threshold                                      |                          | ILED_SETTING > ILED_CUT                               | 180  | 220  | 260  | mA    |

| FAULT assert delay time at start-up                            | t <sub>ft_d_</sub> start |                                                       | 3    | 4    | 5    | ms    |

| FAULT assert deglitch time after start-up (7)                  | t <sub>FT_D</sub>        |                                                       |      | 20   |      | μs    |

| FAULT assert low sink                                          | I==                      | VFAULT = 12V                                          | 10   | 30   | 50   | mA    |

| current ability                                                | IFAULT_SINK              | VFAULT = 0.2V                                         | 5    | 12   |      | mA    |

| FAULT pull-up resistor                                         |                          |                                                       | 100  | 330  | 500  | kΩ    |

| IREF current for mode detection                                |                          |                                                       | 200  | 240  | 280  | μA    |

| IREF voltage (V <sub>IREF</sub> ) threshold for mode detection |                          |                                                       | 2.6  | 2.7  | 2.8  | V     |

$V_{IN}$  = 13.5V,  $V_{EN}$  = 2V,  $T_J$  = -40°C to +150°C, typical values are at  $T_J$  = 25°C, unless otherwise noted. BUCK MODE

| Parameter                                                               | Symbol | Condition                                        | Min   | Тур  | Max   | Units |

|-------------------------------------------------------------------------|--------|--------------------------------------------------|-------|------|-------|-------|

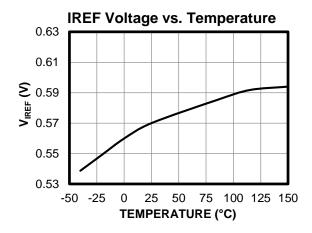

| IREF voltage                                                            | Viref  | I <sub>IREF</sub> = 20µA                         | 0.51  | 0.57 | 0.63  | V     |

| IREF current threshold for pin short detection                          |        |                                                  | 60    | 85   | 120   | μA    |

| IREF current threshold for pin open detection                           |        |                                                  |       | 3    | 6     | μA    |

| NTC source current                                                      | Intc   | V <sub>NTC</sub> = 1.5V, I <sub>REF</sub> = 20µA | 930   | 1020 | 1090  | μA    |

| NTO 16 OF S                                                             |        | I <sub>LED</sub> = 98% of nominal voltage        | -2.5% | 1.25 | +2.5% | V     |

| NTC voltage (V <sub>NTC</sub> ) for current derating                    |        | I <sub>LED</sub> = 74% of nominal voltage        | -2.5% | 0.89 | +2.5% | V     |

| current deraining                                                       |        | I <sub>LED</sub> = 50% of nominal voltage        | -2.5% | 0.53 | +2.5% | V     |

| V <sub>NTC</sub> threshold for over-<br>temperature protection<br>(OTP) |        |                                                  |       | 0.37 |       | V     |

| V <sub>NTC</sub> deglitch time for OTP                                  |        | V <sub>NTC</sub> = 0.3V                          | 180   | 256  | 320   | μs    |

| V <sub>NTC</sub> recovery threshold for OTP                             |        |                                                  |       | 0.48 |       | V     |

| Thermal shutdown (7)                                                    |        |                                                  | 155   | 170  | 185   | °C    |

$V_{IN}$  = 13.5V,  $V_{EN}$  = 2V,  $T_J$  = -40°C to +150°C, typical values are at  $T_J$  = 25°C, unless otherwise noted. BUCK-BOOST MODE

| Parameter                              | Symbol                   | Condition                                                                                 | Min   | Тур   | Max   | Units |

|----------------------------------------|--------------------------|-------------------------------------------------------------------------------------------|-------|-------|-------|-------|

| Shutdown supply current                | I <sub>SD</sub>          | V <sub>EN</sub> = 0V                                                                      |       | 30    | 80    | μA    |

| Quiescent supply current               | lα                       | V <sub>EN</sub> = 2V, no switching, float IREF (exclude I <sub>REF</sub> and NTC current) |       | 1.2   | 2     | mA    |

|                                        |                          | FAULT latch                                                                               |       |       | 2     | mA    |

| HS-FET on resistance                   | R <sub>DS(ON)_HS</sub>   | $V_{BST-SW} = 5V$ , $R_{ISET} = 10.5k\Omega$                                              |       | 44    | 85    | mΩ    |

| LS-FET on resistance                   | R <sub>DS(ON)_LS</sub>   | $V_{CC} = 5.2V$ , $R_{ISET} = 10.5k\Omega$                                                |       | 40    | 80    | mΩ    |

| Curitala la alca ma                    |                          | V <sub>EN</sub> = 0V, V <sub>SW</sub> = 13.5V, T <sub>J</sub> = 25°C                      |       |       | 1     | μΑ    |

| Switch leakage                         | Isw_Lkg                  | V <sub>EN</sub> = 0V, V <sub>SW</sub> = 13.5V                                             |       |       | 5     | μΑ    |

| Peak current limit (7)                 | ILIMIT_PEAK              |                                                                                           | 6.85  | 8     | 9.15  | Α     |

| ZCD (7)                                |                          |                                                                                           |       | 50    |       | mA    |

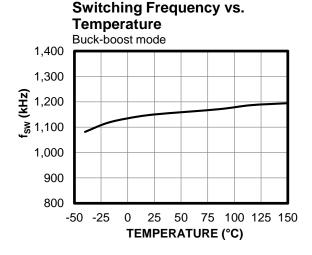

| Switching frequency                    | fsw                      | FSS activated                                                                             | 1020  | 1250  | 1600  | kHz   |

| Minimum on time (7)                    | ton_min                  |                                                                                           |       | 55    | 80    | ns    |

| Minimum off time (7)                   | toff_min                 |                                                                                           |       | 75    | 100   | ns    |

| Maximum duty cycle (7)                 | D <sub>MAX</sub>         | Low dropout                                                                               | 95    | 98    |       | %     |

| FSS <sup>(7)</sup>                     |                          |                                                                                           |       | 15    |       | kHz   |

| FSS range (7)                          |                          |                                                                                           |       | ±10%  |       | fsw   |

| LED .                                  |                          | R <sub>ISET</sub> = $10.5k\Omega$ , T <sub>J</sub> = $25^{\circ}$ C to $100^{\circ}$ C    | 1.9   | 2     | 2.1   | •     |

| LED current                            | I <sub>LED</sub>         | $R_{ISET} = 10.5k\Omega$                                                                  | 1.7   |       | 2.3   | Α     |

| ISET voltage                           | VISET                    | I <sub>ISET</sub> = 45µA                                                                  | 0.573 | 0.592 | 0.606 | V     |

| Down doughting ratio                   |                          | V <sub>IN</sub> = 6.6V, V <sub>ISET</sub> relative to nominal voltage                     |       | 95    |       | %     |

| Power derating ratio                   |                          | $V_{IN} = 5.3V$ , $V_{ISET}$ relative to nominal voltage                                  |       | 75    |       | %     |

| ISET current threshold for pin short   |                          |                                                                                           | 130   | 160   | 190   | μΑ    |

| ISET current threshold for pin open    |                          |                                                                                           | 0.5   | 1.4   | 5     | μΑ    |

| EN rising threshold                    | V <sub>EN_RISING</sub>   | V <sub>EN</sub> - V <sub>INGND</sub>                                                      |       | 1     | 1.6   | V     |

| EN falling threshold                   | V <sub>EN_</sub> FALLING | VEN - VINGND                                                                              | 0.7   | 0.9   |       | V     |

| EN threshold hysteresis                | V <sub>EN_HYS</sub>      | VEN - VINGND                                                                              |       | 100   |       | mV    |

| TNI in part or recent                  |                          | V <sub>EN</sub> = 2V                                                                      |       | 2     | 8     | μΑ    |

| EN input current                       | I <sub>EN</sub>          | V <sub>EN</sub> = 0V                                                                      |       | 0     | 0.2   | μΑ    |

| DIM rising threshold                   | V <sub>DIM_RISING</sub>  | Vdim - Vingnd                                                                             |       | 1     | 1.6   | V     |

| DIM falling threshold                  | V <sub>DIM_FALLING</sub> | V <sub>DIM</sub> - V <sub>INGND</sub>                                                     | 0.7   | 0.9   |       | V     |

| DIM threshold hysteresis               | V <sub>DIM_HYS</sub>     | V <sub>DIM</sub> - V <sub>INGND</sub>                                                     |       | 100   |       | mV    |

| DIM on time limit of<br>MPQ7231GLE-D10 |                          |                                                                                           | 0.8   | 1     | 1.2   | ms    |

| DIM on time limit of<br>MPQ7231GLE-D30 | t <sub>DIM_ON</sub>      |                                                                                           | 2.4   | 3     | 3.6   | ms    |

| DIM on time limit of<br>MPQ7231GLE-D50 |                          |                                                                                           | 4     | 5     | 6     | ms    |

$V_{IN}$  = 13.5V,  $V_{EN}$  = 2V,  $T_J$  = -40°C to +150°C, typical values are at  $T_J$  = 25°C, unless otherwise noted. BUCK-BOOST MODE

| Parameter                                              | Symbol                           | Condition                                                    | Min  | Тур  | Max  | Units |

|--------------------------------------------------------|----------------------------------|--------------------------------------------------------------|------|------|------|-------|

| DIM input correct                                      |                                  | V <sub>DIM</sub> - V <sub>INGND</sub> = 2V                   |      | 2    | 8    | μΑ    |

| DIM input current                                      | І <sub>ОІМ</sub>                 | V <sub>DIM</sub> - V <sub>INGND</sub> = 0V                   |      | 0    | 0.2  | μΑ    |

| DIM turn-off delay (7)                                 | t <sub>DIM_D_OFF</sub>           |                                                              | 100  |      |      | ms    |

| V <sub>IN</sub> UVLO rising threshold                  | VIN_UVLO_<br>RISING              | Vin - Vingnd                                                 | 5.75 | 6    | 6.25 | V     |

| V <sub>IN</sub> UVLO falling threshold                 | VIN_UVLO_<br>FALLING             | Vin - Vingnd                                                 | 4.4  | 4.9  | 5.2  | V     |

| V <sub>IN</sub> UVLO hysteresis threshold              | V <sub>IN_UVLO_HYS</sub>         | V <sub>IN</sub> - V <sub>INGND</sub>                         |      | 1.1  |      | V     |

| V <sub>CC</sub> UVLO rising threshold                  | Vcc_uvlo_<br>RISING              | V <sub>CC</sub> - V <sub>AGND</sub>                          | 4.4  | 4.7  | 5    | V     |

| V <sub>CC</sub> UVLO falling threshold                 | V <sub>CC_UVLO_</sub><br>FALLING | Vcc - Vagnd                                                  | 3.4  | 4.05 | 4.7  | V     |

| Vcc UVLO hysteresis threshold                          | Vcc_uvlo_hys                     | Vcc - Vagnd                                                  |      | 650  |      | mV    |

| VCC regulator                                          | Vcc                              | Icc = 0mA                                                    | 4.9  | 5.1  | 5.3  | V     |

| VCC load regulation                                    |                                  | I <sub>CC</sub> = 20mA                                       | 4.7  |      |      | V     |

| VCC maximum current ability                            |                                  | Vcc = Vcc_uvlo + 100mV, no switching                         | 50   | 80   | 120  | mA    |

| VCC source current ability (7)                         |                                  | V <sub>CC</sub> = V <sub>CC_UVLO</sub> + 100mV,<br>switching |      | 25   |      | mA    |

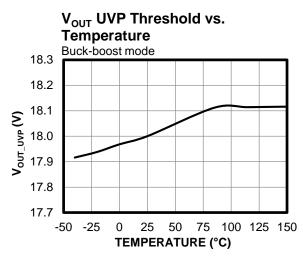

| Output over-voltage protection (OVP) threshold         | Vout_ovp                         | Vingnd - Vagnd                                               | 17   | 18   | 19   | V     |

| Output under-voltage protection (UVP) threshold        | Vout_uvp                         | Vingnd - Vagnd                                               | 1    | 1.35 | 1.7  | V     |

| V <sub>IN</sub> load dump protection threshold         |                                  |                                                              | 38   | 40   | 42   | V     |

| V <sub>IN</sub> load dump protection falling threshold |                                  |                                                              | 37   | 39   | 41   | V     |

| V <sub>IN</sub> load dump protection hysteresis        |                                  |                                                              |      | 1    |      | V     |

| Output discharge current for                           |                                  | Vingnd - Vpgnd > 5V                                          | 40   | 100  | 180  | mA    |

| load dump protection                                   |                                  | VINGND - VPGND = 1V                                          | 20   | 45   | 90   | mA    |

| FAULT assert delay time at start-up                    | tft_d_start                      |                                                              | 3    | 4    | 5    | ms    |

| FAULT assert deglitch time after start-up              | t <sub>FT_D</sub>                |                                                              |      | 20   |      | μs    |

| FAULT assert low sink current                          | IFAULT_SINK                      | VFAULT = 12V                                                 | 10   | 30   | 50   | mA    |

| ability                                                | IFAULI_SINK                      | VFAULT = 0.2V                                                | 5    | 12   |      | mA    |

| FAULT pull-up resistor                                 |                                  |                                                              | 100  | 330  | 500  | kΩ    |

$V_{IN}$  = 13.5V,  $V_{EN}$  = 2V,  $T_J$  = -40°C to +150°C, typical values are at  $T_J$  = 25°C, unless otherwise noted. BUCK-BOOST MODE

| Parameter                                      | Symbol            | Condition                                 | Min   | Тур  | Max   | Units |

|------------------------------------------------|-------------------|-------------------------------------------|-------|------|-------|-------|

| IREF current for mode detection                |                   |                                           | 200   | 240  | 280   | μA    |

| V <sub>IREF</sub> threshold for mode detection |                   |                                           | 2.6   | 2.7  | 2.8   | V     |

| IREF voltage                                   | V <sub>IREF</sub> | I <sub>REF</sub> = 20µA                   | 0.51  | 0.57 | 0.63  | V     |

| IREF current threshold for pin short detection |                   |                                           | 650   | 800  | 1000  | μA    |

| IREF current threshold for pin open detection  |                   |                                           |       | 40   | 55    | μA    |

| NTC source current                             | I <sub>NTC</sub>  | $V_{NTC} = 1.5V$ , $I_{REF} = 200\mu A$   | 930   | 1020 | 1090  | μΑ    |

|                                                |                   | I <sub>LED</sub> = 98% of nominal voltage | -2.5% | 1.25 | +2.5% | V     |

| V <sub>NTC</sub> for current derating          |                   | I <sub>LED</sub> = 74% of nominal voltage | -2.5% | 0.89 | +2.5% | V     |

|                                                |                   | I <sub>LED</sub> = 50% of nominal voltage | -2.5% | 0.53 | +2.5% | V     |

| V <sub>NTC</sub> threshold for OTP             |                   |                                           |       | 0.37 |       | V     |

| V <sub>NTC</sub> deglitch time for OTP         |                   | $V_{NTC} = 0.3V$                          | 180   | 256  | 320   | μs    |

| V <sub>NTC</sub> recovery threshold for OTP    |                   |                                           |       | 0.48 |       | V     |

| Thermal shutdown (7)                           |                   |                                           | 155   | 170  | 185   | °C    |

#### Note:

<sup>7)</sup> Not tested in production. Guaranteed by design and characterization.

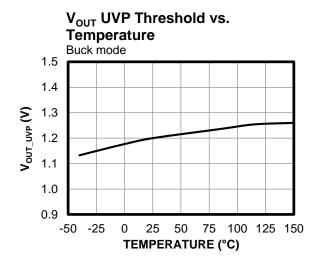

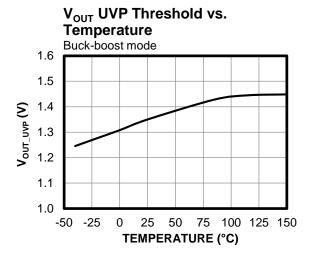

#### TYPICAL CHARACTERISTICS

$V_{IN} = 12V$ ,  $T_{J} = -40$ °C to +150°C, unless otherwise noted.

$V_{IN} = 12V$ ,  $T_{J} = -40$ °C to +150°C, unless otherwise noted.

$V_{IN} = 12V$ ,  $T_{J} = -40$ °C to +150°C, unless otherwise noted.

#### TYPICAL PERFORMANCE CHARACTERISTICS

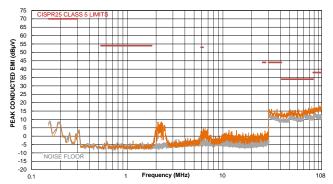

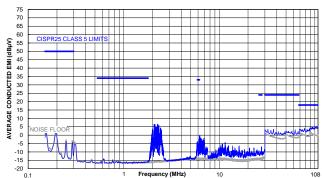

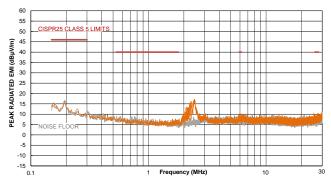

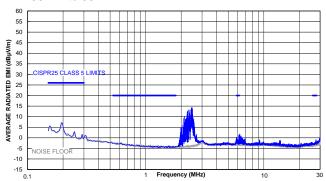

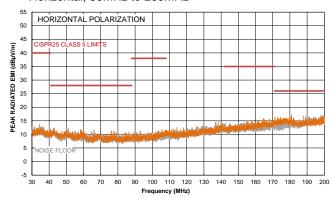

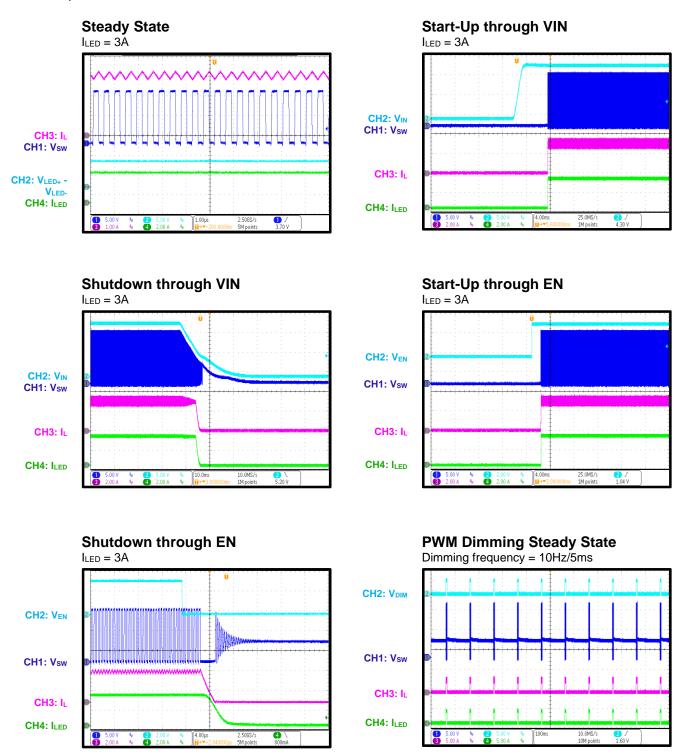

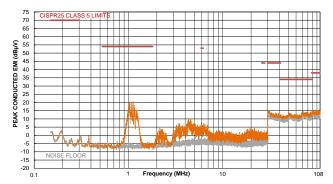

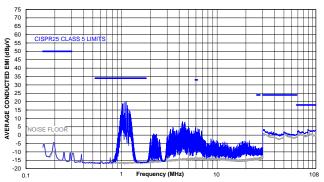

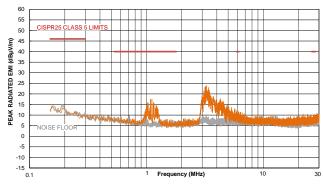

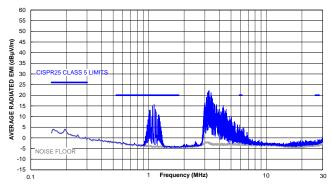

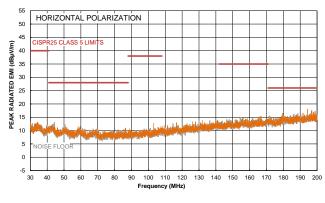

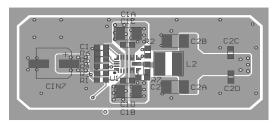

Buck mode, two LEDs in series ( $V_{LED}$  = 6V),  $V_{IN}$  = 13.5V,  $I_{LED}$  = 3A,  $f_{SW}$  = 2.4MHz, L = 3.3 $\mu$ H, with EMI filters,  $T_A$  = 25°C, unless otherwise noted. (8)

#### CISPR25 Class 5 Peak Conducted Emissions

150kHz to 108MHz

# **CISPR25 Class 5 Average Conducted Emissions**

150kHz to 108MHz

#### CISPR25 Class 5 Peak Radiated Emissions

150kHz to 30MHz

# CISPR25 Class 5 Average Radiated Emissions

150kHz to 30MHz

#### CISPR25 Class 5 Peak Radiated Emissions

Horizontal, 30MHz to 200MHz

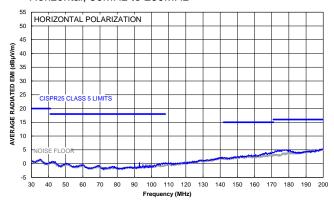

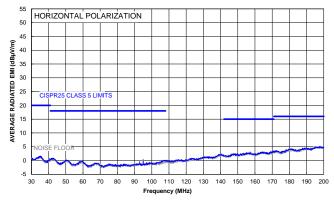

# CISPR25 Class 5 Average Radiated Emissions

Horizontal, 30MHz to 200MHz

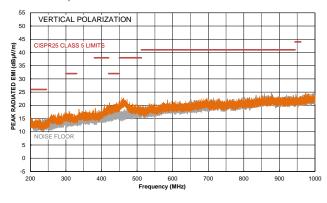

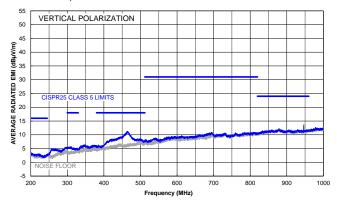

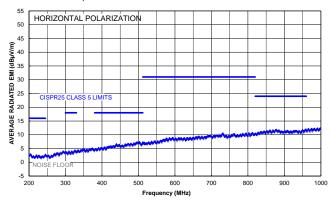

Buck mode, two LEDs in series ( $V_{LED}$  = 6V),  $V_{IN}$  = 13.5V,  $I_{LED}$  = 3A,  $f_{SW}$  = 2.4MHz, L = 3.3 $\mu$ H, with EMI filters,  $T_A$  = 25°C, unless otherwise noted. (8)

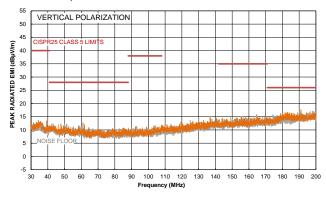

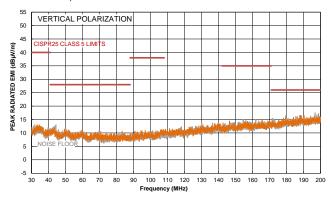

#### CISPR25 Class 5 Peak Radiated Emissions

Vertical, 30MHz to 200MHz

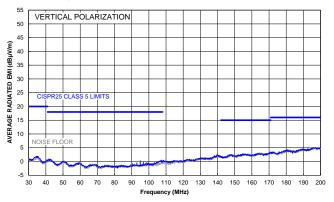

# CISPR25 Class 5 Average Radiated Emissions

Vertical, 30MHz to 200MHz

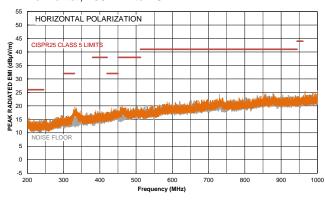

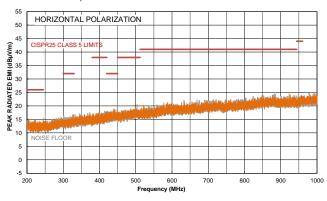

#### CISPR25 Class 5 Peak Radiated Emissions

Horizontal, 200MHz to 1GHz

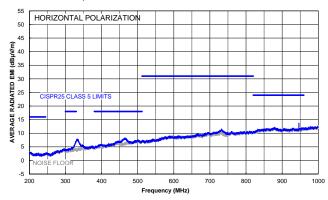

# CISPR25 Class 5 Average Radiated Emissions

Horizontal, 200MHz to 1GHz

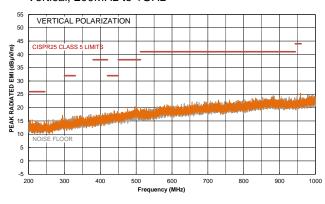

#### CISPR25 Class 5 Peak Radiated Emissions

Vertical, 200MHz to 1GHz

#### CISPR25 Class 5 Average Radiated Emissions

Vertical, 200MHz to 1GHz

#### Note:

8) The MPQ7231's buck mode EMC test results are based on Figure 10 on page 46.

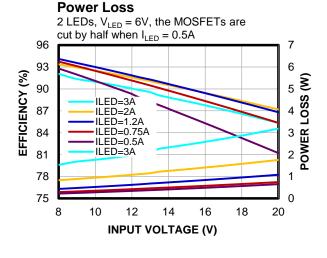

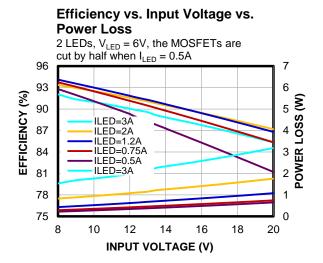

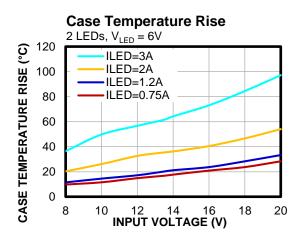

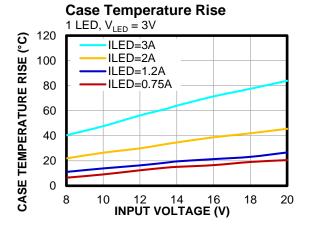

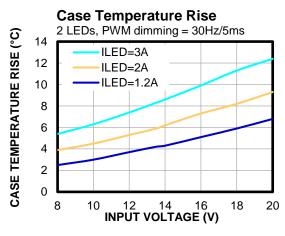

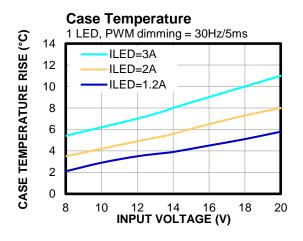

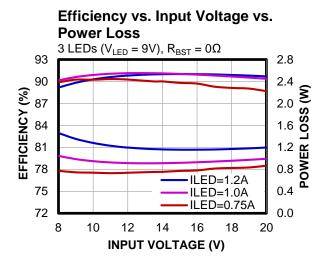

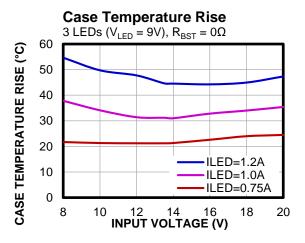

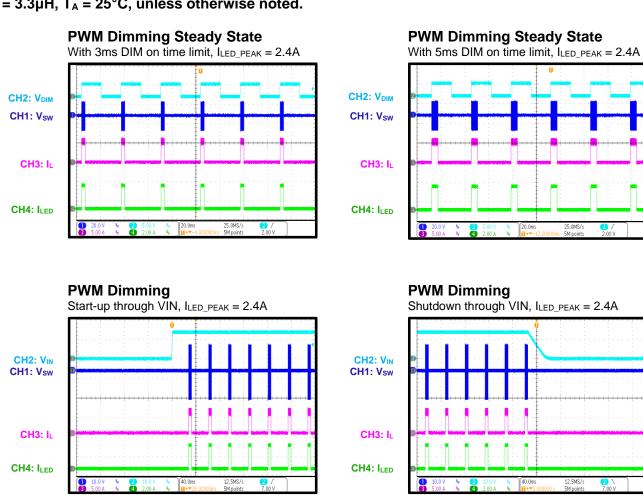

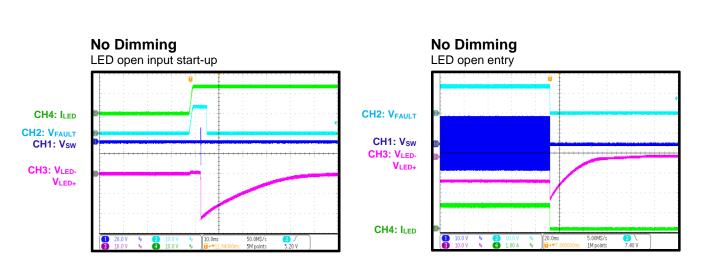

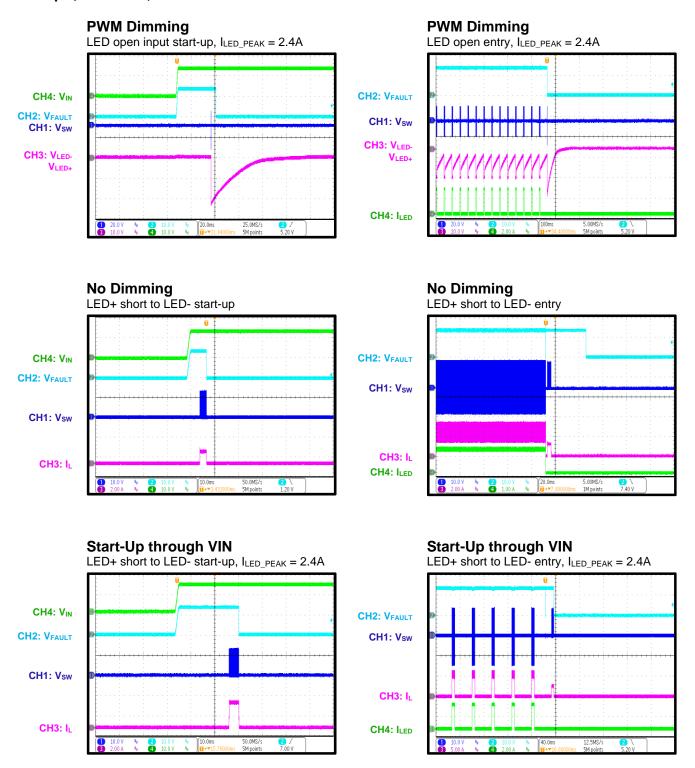

Buck mode, two LEDs in series ( $V_{LED}$  = 6V),  $V_{IN}$  = 13.5V,  $f_{SW}$  = 2.4MHz, L = 3.3 $\mu$ H,  $T_A$  = 25°C, unless otherwise noted. (9)

#### Note:

9) The efficiency and thermal curves are based on Figure 10 on page 46 when R<sub>BST</sub> = 0Ω, and the output and input filters have been removed. L = 3.3μH (XEL4030-332MEB).

© 2023 MPS. All Rights Reserved.

Buck mode, two LEDs in series (V<sub>LED</sub> = 6V),  $V_{IN}$  = 13.5V,  $I_{LED}$  = 3A,  $f_{SW}$  = 2.4MHz, L = 3.3 $\mu$ H,  $T_A$  = 25°C, unless otherwise noted.

Buck mode, two LEDs in series ( $V_{LED}=6V$ ),  $V_{IN}=13.5V$ ,  $I_{LED}=3A$ ,  $f_{SW}=2.4MHz$ ,  $L=3.3\mu H$ ,  $T_A=25^{\circ}C$ , unless otherwise noted.

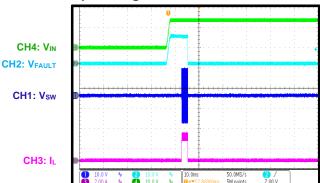

#### False Mode Detection during Start-Up through VIN

Buck-boost mode, three LEDs in series ( $V_{LED}$  = 9V),  $V_{IN}$  = 13.5V,  $I_{LED}$  = 1.2A,  $f_{SW}$  = 1.25MHz, L = 3.3 $\mu$ H, with EMI filters,  $T_A$  = 25°C, unless otherwise noted. (10)

#### CISPR25 Class 5 Peak Conducted Emissions

150kHz to 108MHz

# **CISPR25 Class 5 Average Conducted Emissions**

150kHz to 108MHz

# CISPR25 Class 5 Peak Radiated Emissions

150kHz to 30MHz

# CISPR25 Class 5 Average Radiated Emissions

150kHz to 30MHz

#### CISPR25 Class 5 Peak Radiated Emissions

Horizontal, 30MHz to 200MHz

#### CISPR25 Class 5 Average Radiated Emissions

Horizontal, 30MHz to 200MHz

Buck-boost mode, three LEDs in series ( $V_{LED} = 9V$ ),  $V_{IN} = 13.5V$ ,  $I_{LED} = 1.2A$ ,  $f_{SW} = 1.25MHz$ ,  $L = 3.3\mu H$  with EMI filters,  $T_A = 25$ °C, unless otherwise noted. (10)

# CISPR25 Class 5 Peak Radiated Emissions

Vertical, 30MHz to 200MHz

# CISPR25 Class 5 Average Radiated Emissions

Vertical, 30MHz to 200MHz

#### CISPR25 Class 5 Peak Radiated Emissions

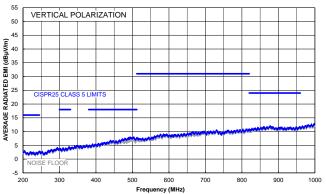

Horizontal, 200MHz to 1GHz

#### CISPR25 Class 5 Average Radiated Emissions

Horizontal, 200MHz to 1GHz

# CISPR25 Class 5 Peak Radiated Emissions

Vertical, 200MHz to 1GHz

# CISPR25 Class 5 Average Radiated Emissions

Vertical, 200MHz to 1GHz

#### Note:

10) The MPQ7231's buck-boost mode EMC test results are based on Figure 11 on page 46.

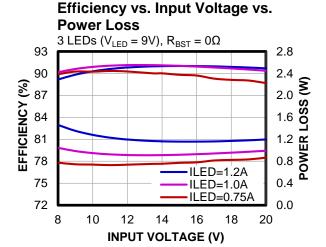

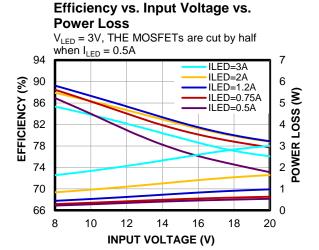

Buck-boost mode, three LEDs in series ( $V_{LED}$  = 9V),  $V_{IN}$  = 13.5V,  $f_{SW}$  = 1.25MHz, L = 3.3 $\mu$ H,  $T_A$  = 25°C, unless otherwise noted. (11)

#### Note:

11) The efficiency and thermal curves are based on Figure 11 on page 46 when  $R_{BST} = 0\Omega$ , and the output and input filters have been removed. L = 3.3 $\mu$ H (XEL4030-332MEB).

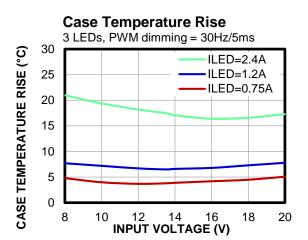

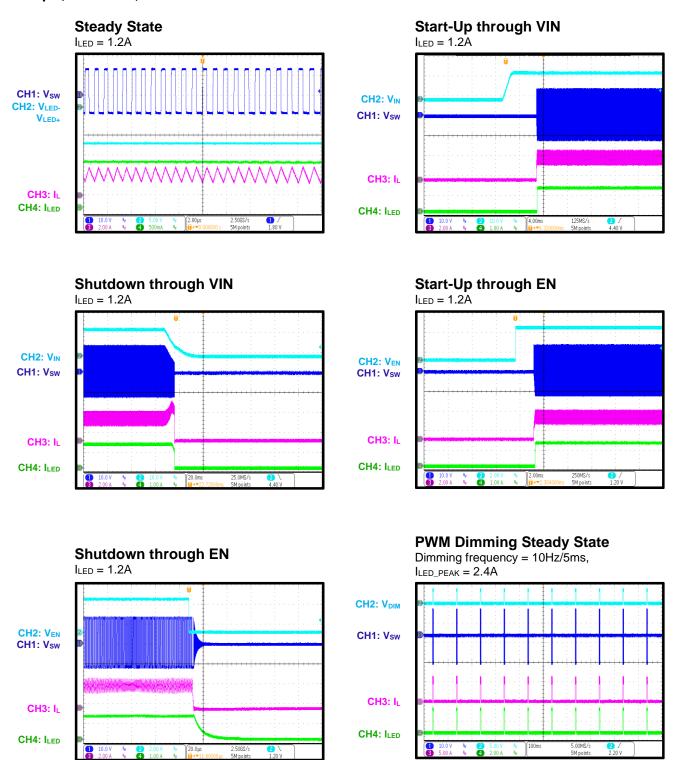

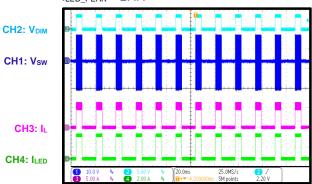

Buck-boost mode, three LEDs in series ( $V_{LED}$  = 9V),  $V_{IN}$  = 13.5V,  $I_{LED}$  = 1.2A,  $f_{SW}$  = 1.25MHz, L = 3.3 $\mu$ H,  $T_A$  = 25°C, unless otherwise noted.

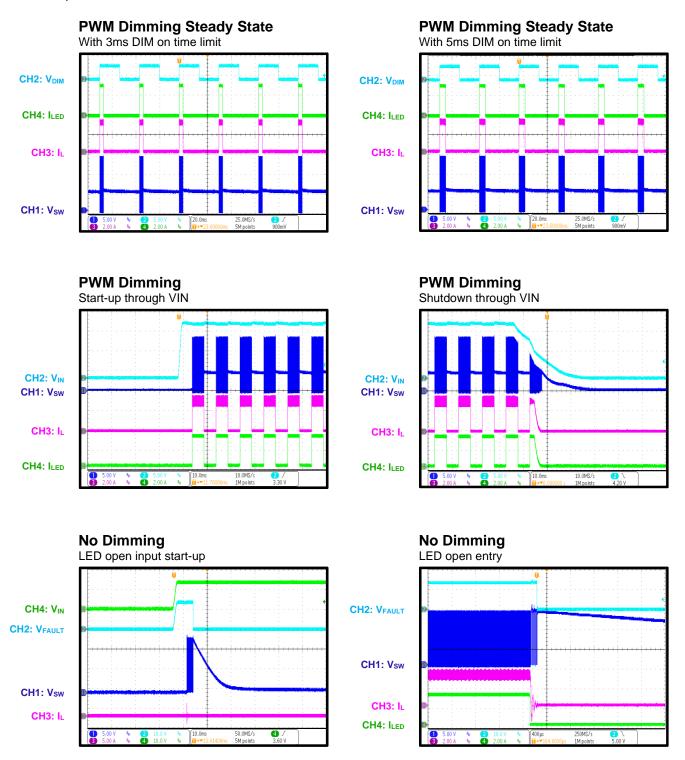

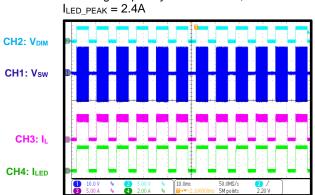

# PWM Dimming Steady State Dimming frequency = 30Hz/5ms, ILED\_PEAK = 2.4A CH1: Vsw CH3: IL CH4: ILED 10.00 V b 20.00 V b 30.00 V b 3

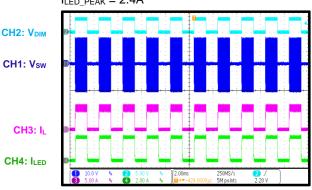

# **PWM Dimming Steady State**

Dimming frequency = 60Hz/5ms,  $I_{LED\_PEAK} = 2.4A$

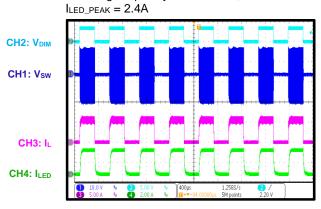

#### **PWM Dimming Steady State**

Dimming frequency = 120Hz/5ms,

#### **PWM Dimming Steady State**

Dimming frequency = 500Hz/50%,  $I_{LED\ PEAK} = 2.4A$

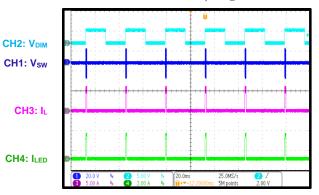

#### **PWM Dimming Steady State**

Dimming frequency = 2kHz/50%,

#### **PWM Dimming Steady State**

With 1ms DIM on time limit, ILED PEAK = 2.4A

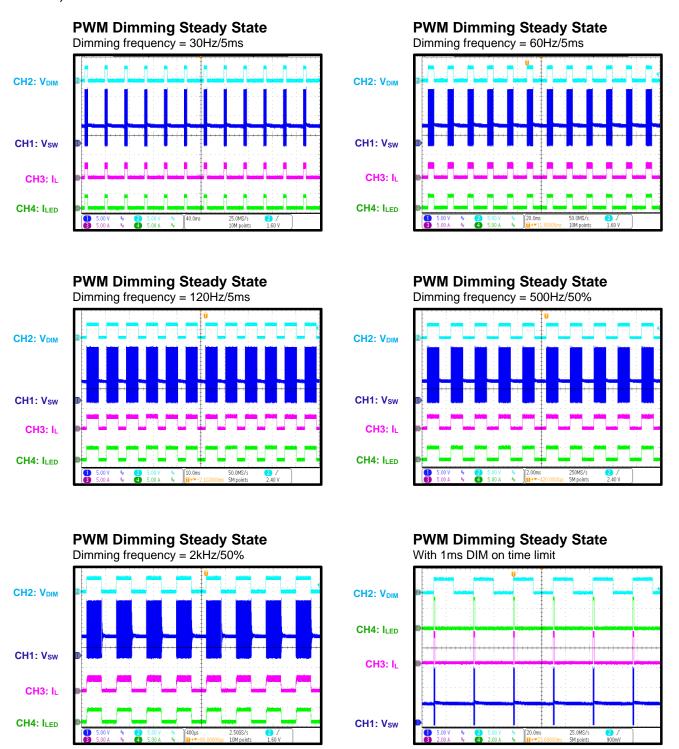

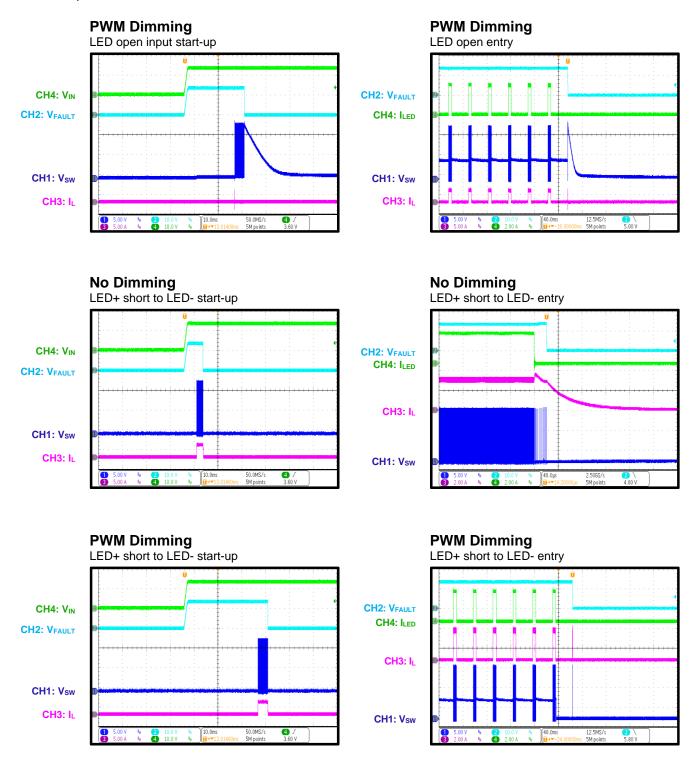

Buck-boost mode, three LEDs in series ( $V_{LED}$  = 9V),  $V_{IN}$  = 13.5V,  $I_{LED}$  = 1.2A,  $f_{SW}$  = 1.25MHz, L = 3.3 $\mu$ H,  $T_A$  = 25°C, unless otherwise noted.

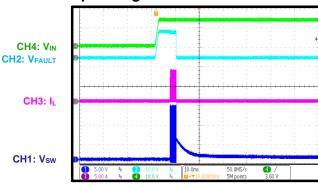

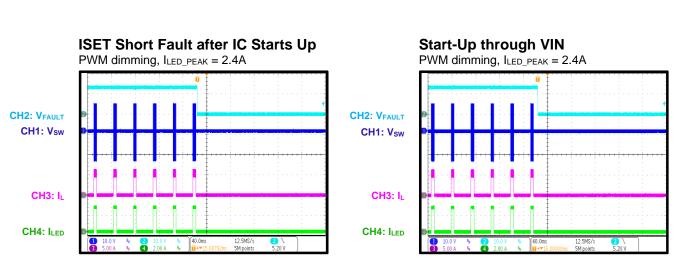

#### False Mode Detection during Start-Up through VIN

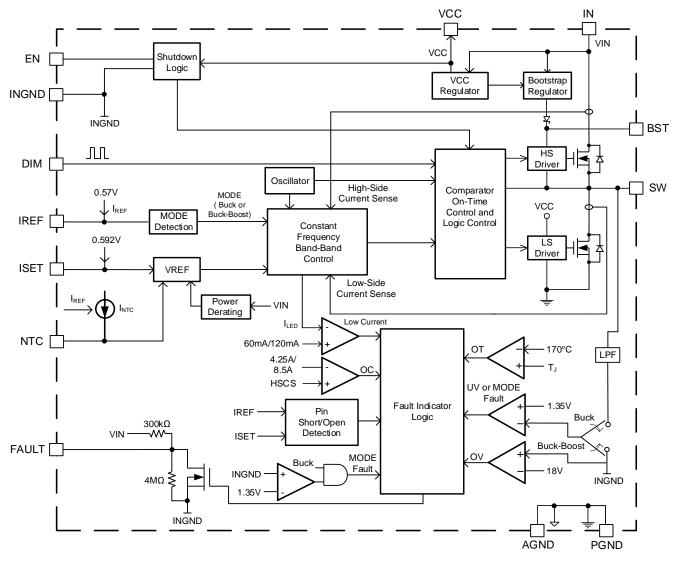

#### **FUNCTIONAL BLOCK DIAGRAM**

Figure 3: Functional Block Diagram

#### **OPERATION**

MPQ7231 The fixed-frequency. is а synchronous, rectified, buck-boost or buck, switch-mode LED driver with integrated power MOSFETs. In buck mode, it offers a very compact solution to achieve 3A of continuous output current (I<sub>LED</sub>). The MPQ7231 can also be configured to buck-boost mode to provide up to 1.2A of constant load current and 2.4A of peak current (ILED PEAK). with low pulse-width modulation (PWM) dimming frequencies at small dimming duty cycles. The device has excellent load and line regulation across a 6V to 42V input supply range.

#### **Fixed-Frequency Band-Band Control**

The MPQ7231 provides fixed-frequency bandband control combined with frequency spread (FSS) to reduce EMC spectrum noise. Compared to fixed-frequency PWM control, band-band control offers the advantages of a simpler control loop and faster transient response. The loop is stable without requiring an output capacitor. Band-band control compares the inductor current (IL) to its internal peak current (I<sub>BAND PEAK</sub>) and valley (IBAND VALLEY). If IL exceeds IBAND PEAK, the highside MOSFET (HS-FET) turns off. If IL drops below I<sub>BAND\_VALLEY</sub>, the HS-FET turns on. (I<sub>BAND PEAK</sub> + I<sub>BAND VALLEY</sub>) / 2 is controlled by a PID loop to regulate the LED current (I<sub>LED</sub>). I<sub>BAND PEAK</sub> - IBAND VALLEY is controlled by a PLL loop to regulate the switching frequency (f<sub>SW</sub>) at 2.4MHz in buck mode or 1.25MHz in buck-boost mode. If the minimum on time (ton MIN) or minimum off time (toff MIN) is triggered, fsw is extended and the real  $f_{SW}$  is D /  $t_{ON\ MIN}$  or (1 - D) /  $t_{OFF\ MIN}$ , where D is the required duty cycle, and ton MIN and toff MIN are both at 80ns (max).

FSS employs a 15kHz modulation frequency with a triangular profile to spread the internal  $f_{SW}$  across a  $\pm 10\%$  nominal  $f_{SW}$  window.

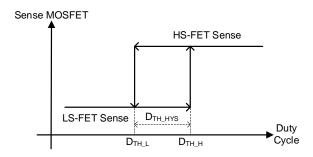

#### **Middle Point Inductor Current Sense**

The MPQ7231 senses  $I_{LED}$  via the middle point of the inductor current ( $I_{L\_MID}$ ).  $I_{LMID}$  is sensed via the HS-FET or low-side MOSFET (LS-FET) depending on the duty cycle. If the duty cycle exceeds a set value ( $D_{TH\_H}$ ) (55% in buck or 60% in buck-boost), then  $I_{LMID}$  is sensed via the HS-

FET; if the duty cycle drops below  $D_{TH\_L}$  (45% in buck or 40% in buck-boost), then  $I_{LMID}$  is sensed through the LS-FET. The duty cycle hysteresis ( $D_{TH\_HYS}$ ) (10% in buck or 20% in buck-boost) is triggered to prevent the current sense switching between the HS-FET and LS-FET frequently at critical duty cycles.

Figure 4: Current-Sense MOSFET vs. Duty Cycle

$I_{LED}$  is equal to  $I_{LMID}$  in buck topology, while  $I_{LED}$  is equal to  $I_{LMID}$  x  $V_{IN}$  / ( $V_{IN}$  +  $V_{OUT}$ ) in buck-boost topology.

#### **Selecting Buck and Buck-Boost Mode**

The MPQ7231 can be configured to buck or buck-boost topology by connecting different resistors (R<sub>IREF</sub>) at the IREF pin.  $I_{LMID}$  is sensed via the sensing MOSFET.  $I_{LED}$  is equal to  $I_{LMID}$  in buck topology, while  $I_{LED}$  is equal to  $I_{LMID}$  x  $V_{IN}$  / ( $V_{IN}$  +  $V_{OUT}$ ) in buck-boost topology.

Mode detection begins when V<sub>CC</sub> reaches its UVLO threshold (VCC\_UVLO) (4.7V). A 240µA current source (IREF DET) flows from the IREF pin to detect the resistor voltage at the pin when the device is turned on. If the voltage generated by I<sub>REF DET</sub> x R<sub>IREF</sub> < 2.6V, then buck-boost mode is selected; if the voltage generated by IREF DET X R<sub>IREF</sub> > 2.8V, then buck mode is selected. The corresponding R<sub>IREF</sub> is ≤9.09kΩ for buck-boost mode and  $\geq 14.7k\Omega$  for buck mode. To prevent an IREF short in buck-boost mode, set RIREF between  $1.05k\Omega$  and  $9.09k\Omega$ . To prevent an IREF open fault in buck mode, set Riref between 14.7k $\Omega$  and 80.6k $\Omega$ . Once detection is finished. the mode latches and IREF is set to 0.57V/RIREF as the NTC pin current's reference. The latched mode signal is reset by V<sub>CC UVLO</sub>; it cannot be reset by pulling EN or DIM low. An internal 1MHz filter combined with a 250µs deglitch time protects the part from false mode detection, which is caused by noise coupling at the pin.

Monitor  $V_{\text{INGND}}$  -  $V_{\text{PGND}}$  to ensure the detected mode is consistent with the real topology connection. If buck mode is detected with  $V_{\text{INGND}}$  -  $V_{\text{PGND}}$  exceeding 1.35V, or buck-boost mode is detected with  $V_{\text{INGND}}$  -  $V_{\text{PGND}}$  below 1.35V (detected as output UV), then the part latches off and FAULT asserts low.

# **Internal Regulator**

The 5.1V internal regulator (VCC) powers most of the internal circuitries. VCC ramps up once the input voltage (V<sub>IN</sub>) reaches its rising UVLO threshold (V<sub>IN UVLO VTH R</sub>), regardless of whether EN is high or low. VCC is the reference for PGND and AGND but not for INGND. Thus, in buckboost mode, the ground level should not match between VCC and INGND. An insufficient VCC capacitor causes V<sub>CC</sub> ringing and leads to switch instability. It is recommended to use a ≥3µF decoupling ceramic capacitor at the VCC pin. When choosing a real capacitor, consider the capacitance derating to ensure a ≥3µF real capacitance. A 10µF (X7R) capacitor with a ≥10V DC rated voltage is recommended. V<sub>CC</sub> has a UVLO rising threshold ( $V_{CC\ UVLO\ VTH\ R}$ ) (4.7V) and а UVLO falling (V<sub>CC\_UVLO\_VTH\_F</sub>) (4.05V). In addition to powering internal circuitries, VCC can power external circuitries in the system with a 25mA current capability.

# Continuous Conduction Mode (CCM) and Discontinuous Conduction Mode (DCM)

The MPQ7231 provides continuous conduction mode (CCM) to ensure that the part works with a fixed frequency across a no load to full-load range. The advantage of CCM is the controllable frequency and lower output ripple under light-load conditions. If IBAND\_VALLEY is set to 0A, the MPQ7231 enters discontinuous conduction mode (DCM), and the LS-FET works as an ideal diode. Select a proper inductor to ensure that the part does not enter DCM, including during power or thermal derating. Otherwise, ILED precision cannot be guaranteed.

#### **Enable (EN) Control**

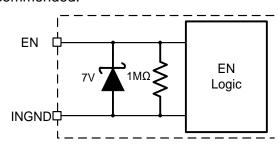

EN is a control pin that turns the LED driver on and off. Drive  $V_{\text{EN}}$  -  $V_{\text{INGND}}$  above 1V to turn on the regulator; drive  $V_{\text{EN}}$  -  $V_{\text{INGND}}$  below 0.9V to turn the part off and reset FAULT. Note that the MPQ7231 begins thermal detection when EN is

on, resulting in a delay of ~0.9ms between startup through EN and switching.

An internal  $1M\Omega$  resistor placed between EN and INGND enables floating EN to shut down the chip. An integrated Zener diode is placed in parallel with EN to clamp the pin to 7V (see Figure 5). The MPQ7231 enables connecting EN to VIN via a pull-up resistor in both buck mode and buck-boost mode, or connecting EN to VCC via a pull-up resistor in buck mode. Once  $V_{IN}$  and  $V_{CC}$  exceed their respective UVLO thresholds, the chip automatically starts up. Choose a sufficient pull-up resistance to limit the EN input current below 1mA. A  $100k\Omega$  resistor is recommended.

Figure 5: Internal EN Circuit

# **ISET Pin Configuration**

The average  $I_{LED}$  can be configured by connecting a resistor at the ISET pin ( $R_{ISET}$ ).  $I_{LED}$  can be calculated with Equation (1):

$$I_{LED}(A) = 21.3 / R_{ISET}(k\Omega)$$

(1)

The nominal voltage of ISET ( $V_{\text{ISET}}$ ) is 0.592V.  $V_{\text{ISET}}$  is adjusted to below 0.592V to decrease  $I_{\text{LED}}$  in the power or thermal derating.

During the buck mode detection period at startup, ISET current (I<sub>SET</sub>) is monitored to detect whether I<sub>LED</sub> is set above or below 600mA. If I<sub>SET</sub> exceeds 22.2µA during this period, then ILED is detected above 600mA and the MOSFETs are fully on. If I<sub>LED</sub> is detected below 600mA, then the HS-FET and LS-FET is cut by half to improve current-sense accuracy. When the MOSFET is cut by half, the current limit (ILIMIT) is also reduced from 8A to 4,25A. The signal to indicate above or below 800mA is latched once detection completes and can only be reset by V<sub>CC UVLO</sub>. After I<sub>LED</sub> detection, the MOSFET on resistance (R<sub>DS(ON)</sub>) does not change although I<sub>LED</sub> exceeds or drops below 800mA. While in buck-boost mode, the MOSFET remains fully on, and ILIMIT is constant at 8A.

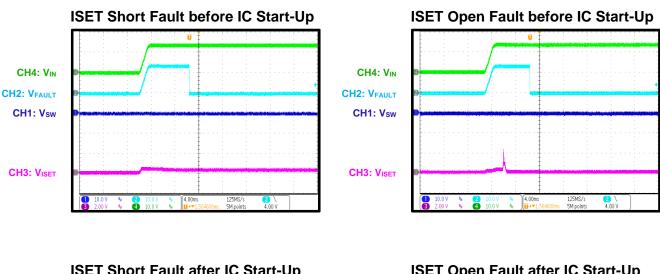

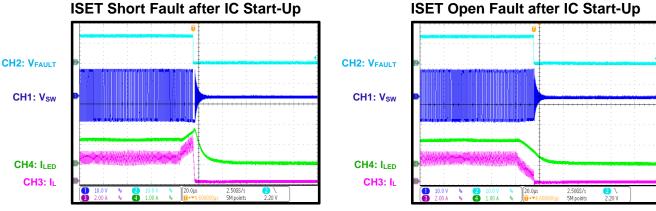

During normal operation, ISET is continuously monitored to detect open fault or short to ground conditions. When I<sub>SET</sub> exceeds a set value, a pin short to ground is detected.

If  $I_{LED}$  is set below 800mA, the ISET short detection threshold is 220 $\mu$ A, corresponding to a 2.67k $\Omega$  resistor or 7.92A  $I_{LED}$ . If  $I_{LED}$  is set above 800mA, the threshold is 330 $\mu$ A, corresponding to a 1.78k $\Omega$  resistor or 11.87A  $I_{LED}$ .

If  $I_{SET}$  is below 1.4 $\mu$ A, corresponding to a 422 $k\Omega$  resistor or 50.37mA  $I_{LED}$ , then a pin open fault is detected.

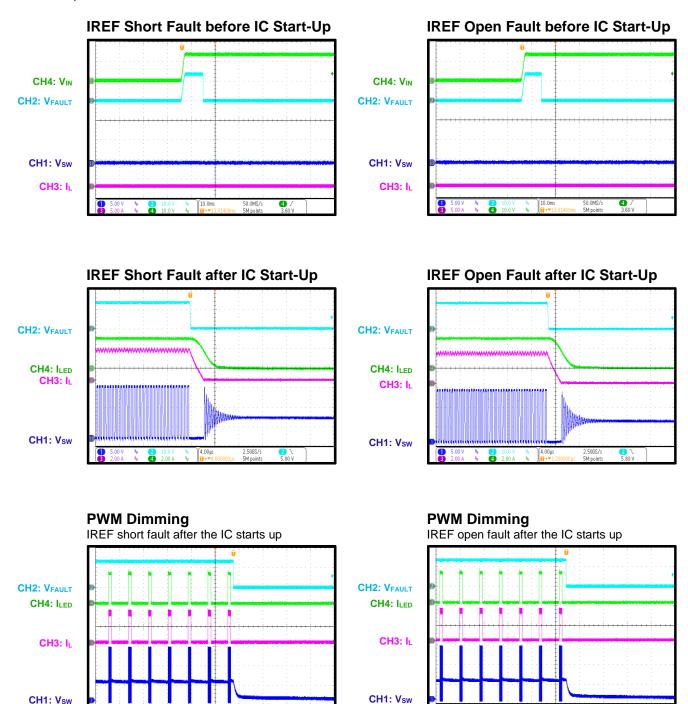

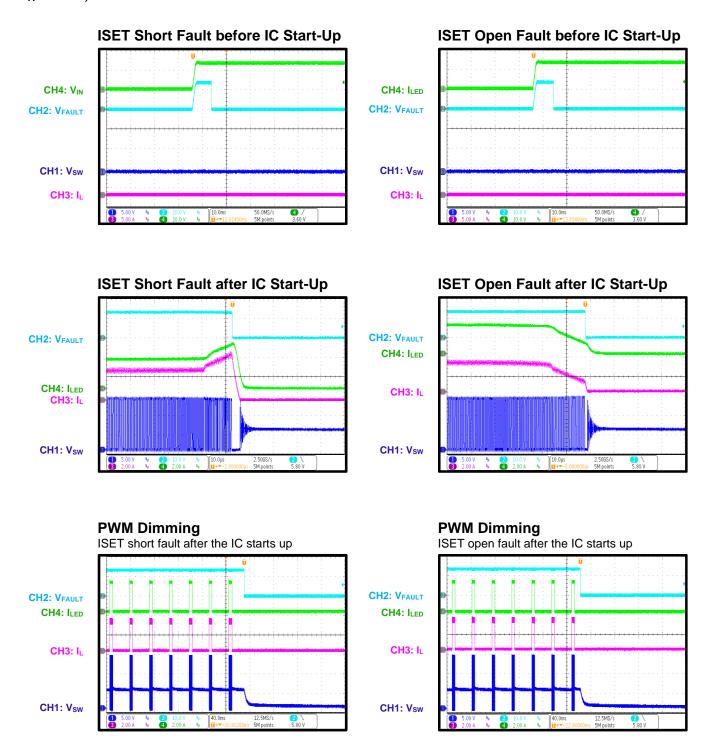

The part latches off once ISET detects a short or open fault, regardless of whether FAULT asserts. FAULT asserts low immediately if ISET detects a short or open fault after start-up. There is a 3ms to 5ms delay for FAULT assertion if a short or open fault is detected during start-up.

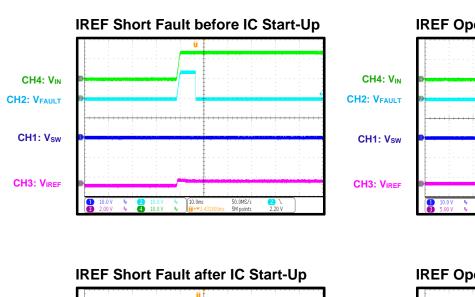

#### **IREF Pin Configuration**

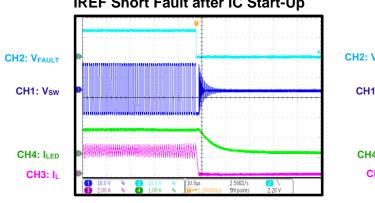

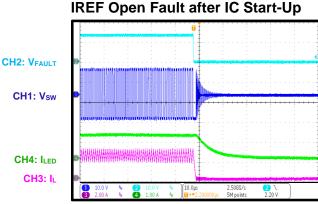

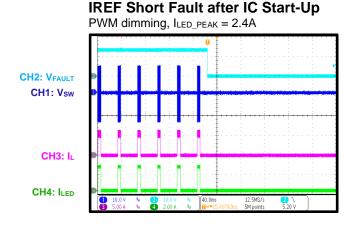

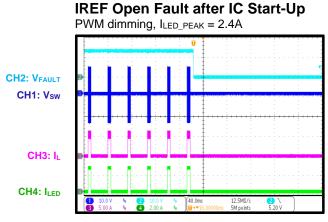

The IREF pin configures buck or buck-boost mode (see Buck and Buck-Boost Mode Selection section on page 42). IREF then sets the current in the external NTC. After mode detection finishes, the IREF pin voltage (V<sub>IREF</sub>) is set to 0.57V with a 10.5% tolerance. Connect RIREF between IREF and ground to obtain a current (I<sub>REF</sub>) equal to 0.57V/R<sub>IREF</sub>. I<sub>REF</sub> is used as the reference for the NTC's current source, where the NTC current is I<sub>RFF</sub> x 50 in buck mode and IREF x5 in buck-boost mode. IREF is also continuously monitored to detect open fault as well short to ground conditions. If IREF exceeds 85µA in buck mode (corresponding to a  $6.7k\Omega$ resistor) and 800µA in buck-boost mode (corresponding to a  $0.71k\Omega$  resistor), then the pin is shorted to ground. If IREF is below 3µA in buck mode (corresponding to a 190k $\Omega$  resistor) and 40µA in buck-boost mode (corresponding to a  $14.3k\Omega$  resistor), then a pin open fault is detected.

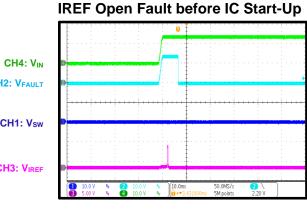

The part latches off once a IREF short or open is detected, regardless of whether FAULT asserts. FAULT asserts low immediately if a pin short or open is detected after start-up. There is a 3ms to 5ms delay for FAULT assertion if a short or open is detected during start-up.

#### **Pulse-Width Modulation (PWM) Dimming**

An external 10Hz to 2kHz PWM waveform can be applied to the DIM pin to implement PWM

dimming. The MPQ7231 stops switching when the DIM pin voltage ( $V_{\text{DIM}}$ ) is below 0.9V and  $I_{\text{LED}}$  is at 0A. It resumes normal operation with a nominal  $I_{\text{LED}}$  when  $V_{\text{DIM}}$  exceeds 1V. The average  $I_{\text{LED}}$  is then proportional to the PWM duty. The maximum LED on time of the MPQ7231-D10, MPQ7231-D30, and MPQ7231-D50 is limited to 1ms, 3ms, and 5ms, respectively, even if the DIM high time is longer than 5ms. The MPQ7231-D00 has no dimming on time limit (see Figure 6).

Figure 6: DIM High vs. LED Current

For applications a with low PWM dimming frequencies at small dimming duty cycles, the error amplifier (EA) output voltage (V<sub>COMP</sub>) may be discharged by the leakage if the dimming off time is too long. The chip can support the maximum DIM low time for as long as 100ms, meaning the dimming frequency can reach below 10Hz.

Note that the DIM high voltage period should remain longer than 100µs. Otherwise, the part might not stop switching and latch even an LED open fault is detected.

#### **Under-Voltage Lockout (UVLO)**

UVLO protects the chip from operating at an insufficient supply voltage. Both  $V_{\text{IN}}$  -  $V_{\text{INGND}}$  and  $V_{\text{CC}}$  have their respective UVLO thresholds. The  $V_{\text{IN}}$  -  $V_{\text{INGND}}$  UVLO rising threshold is 6V, with a 1.1V hysteresis.  $V_{\text{CC\_UVLO\_VTH\_R}}$  is 4.7V with a 0.65V hysteresis. The  $V_{\text{IN}}$  and  $V_{\text{CC}}$  UVLO thresholds do not trigger faults.

# **Fault Detection and Indicator**

The MPQ7231 also provides fault indication. FAULT is the open-drain pin of a MOSFET and is pulled to VIN via a  $300k\Omega$  resistor, as well as a  $4M\Omega$  resistor pulled down to INGND. During normal operation, FAULT is pulled high. During

fault conditions such as LED short, LED open, thermal shutdown, false mode detection, and over-current (OC) conditions, FAULT is pulled low to indicate a fault status. ISET or IREF pin short/open faults during or after start-up can both assert FAULT.

The MPQ7231 senses the output by monitoring the average SW voltage ( $V_{SW}$ ) in buck mode and INGND voltage ( $V_{INGND}$ ) in buck-boost mode. If a LED+ short to LED- or ground is detected, then the output voltage ( $V_{OUT}$ ) drops below the undervoltage (UV) threshold, a short circuit is detected, and FAULT asserts. If a LED+ short to battery or LED open fault is detected, then an output overvoltage (OV) occurs in buck-boost mode, the LS-FET and HS-FET current is detected in buck mode, and FAULT asserts.

If the low current rising threshold is falling when I<sub>LED</sub> is set below 800mA, it reaches 82mA with a 22mA hysteresis; if the low current rising threshold is falling when ILED is set above 800mA in buck mode, it reaches 166mA with a 46mA hysteresis. If the low current rising threshold is falling in buck-boost mode, it reaches 166mA with a 46mA hysteresis. In buck mode, the low current detection is disabled when V<sub>IN</sub> drops below 7.5V to avoid latching the part under coldcrank conditions. In buck-boost mode, if a LED+ (INGND) short to battery is detected, V<sub>IN</sub> - V<sub>INGND</sub> is below its UV threshold, and FAULT cannot assert. If a LED- (PGND) short to INGND is detected, V<sub>INGND</sub> is below the V<sub>INGND</sub> UV threshold, and FAULT asserts. If an LED open fault is detected, V<sub>INGND</sub> exceeds its OV threshold, and FAULT asserts.

At high temperatures, the MPQ7231 continues to operate with a lower current level. The part only shuts down when the internal temperature reaches the 170°C over-temperature protection (OTP) threshold, after which FAULT asserts.

During normal operation, the MPQ7231 stops switching immediately once a fault condition is detected. The FAULT output asserts after 20µs, and then the part latches. During latching, VCC remains present, and the part's consumption current is <2mA.

FAULT can be reset by  $V_{\text{CC\_UVLO}}$  and EN going low. During start-up, FAULT remains not activated for at least 30ms and becomes activated within a maximum of 40ms. This prevents any false function of the system when the FAULT pins of multiple parts are connected together and share the same EN signal. However, individual parts are self-protected and latch off immediately once a fault condition detected, regardless of whether FAULT asserts.

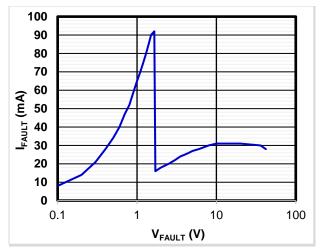

FAULT can withstand a 30mA current and protect itself, even if the pin shorts to a high voltage such as battery voltage ( $V_{BATT}$ ). At a low FAULT pin voltage ( $V_{FAULT}$ ) (e.g. <1.6V), FAULT sink current is increased to improve pull-down capability. Figure 7 shows the FAULT sink current when the pin is pulled low at different  $V_{FAULT}$  levels.

Figure 7: FAULT Sink Current vs. FAULT Voltage

During PWM dimming, fault conditions are not detected properly if the dimming on time is below 100µs. Ensure that the dimming on time remains above 100µs to ensure that fault detection operates correctly.

Table 1 on page 40 lists the fault detection under various conditions.

#### Table 1: Fault Detection (12)

|                                                 | Detection                                                                                                                                                       |                          |                                                                                |  |  |

|-------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|--------------------------------------------------------------------------------|--|--|

| Fault Conditions                                | Buck                                                                                                                                                            |                          | Buck-Boost                                                                     |  |  |

| LED+ short to LED-                              | Vоит UV (Vоит < 1.1V)                                                                                                                                           |                          | INGND UV (VINGND - VPGND < 1.35V) (13)                                         |  |  |

| LED+ short to PGND                              | Vout UV (Vo                                                                                                                                                     | оит < 1.1V)              | INGND UV (VINGND - VPGND < 1.35V) (13)                                         |  |  |

| LED+ short to INGND                             | Vout UV (Vo                                                                                                                                                     | оит < 1.1V)              | Normal conditions                                                              |  |  |

| LED+ short to battery                           | Low I <sub>LED</sub>                                                                                                                                            |                          | Cannot assert FAULT due to V <sub>IN</sub> - V <sub>INGNE</sub> UVLO threshold |  |  |

| LED- short to INGND                             | Normal co                                                                                                                                                       | onditions                | INGND UV (V <sub>INGND</sub> - V <sub>PGND</sub> < 1.35V) (13)                 |  |  |

| LED- short to battery                           | Cannot assert FAULT due to V <sub>IN</sub> - V <sub>INGND</sub> UVLO threshold                                                                                  |                          | N/A <sup>(14)</sup>                                                            |  |  |

| LED open                                        | Low I <sub>LED</sub>                                                                                                                                            |                          | INGND OV (VINGND - VPGND > 18V)                                                |  |  |

| False MODE detection                            | VINGND - VPGND > 1.35V                                                                                                                                          |                          | INGND UV (VINGND - VPGND < 1.35V)                                              |  |  |

| Over-temperature protection (OTP)               | T <sub>J</sub> > 170°C or V <sub>NTC</sub> < 0.37V for >256µs                                                                                                   |                          |                                                                                |  |  |

| ISET short (15)                                 | I <sub>SET</sub> > 220μA when I <sub>LED_SETTING</sub> < 800mA, I <sub>SET</sub> > 330μA when I <sub>LED_SETTING</sub> > 800mA                                  |                          |                                                                                |  |  |

| ISET open (15)                                  |                                                                                                                                                                 | I <sub>ISET</sub> <1.4μA |                                                                                |  |  |

| IREF short (15)                                 | I <sub>REF</sub> > 85µA                                                                                                                                         | I <sub>REF</sub> >800μA  |                                                                                |  |  |

| IREF open (15)                                  | I <sub>REF</sub> < 3µA                                                                                                                                          | I <sub>REF</sub> <40µA   |                                                                                |  |  |

| Over-current protection (OCP)                   | Current limit triggered three times continuously                                                                                                                |                          |                                                                                |  |  |

| Low I <sub>LED</sub> protection <sup>(16)</sup> | ILED_RISIING < 82mA with a 22mA hysteresis if falling when ILED_SETTING < 800mA,  ILED_RISING < 166mA with 46mA hysteresis if falling when ILED_SETTING > 800mA |                          | I <sub>LED_RISING</sub> < 166mA with a 46mA hysteresis if falling              |  |  |

#### Notes:

- 12) Once FAULT is detected, the part latches and FAULT asserts, unless otherwise noted.

13) If a LED+ short to LED- is detected with a long cable, then FAULT might glitch if V<sub>INGND</sub> V<sub>PGND</sub> is pulled below -0.3V.

- 14) Not applicable. Similar to an LED- short to battery in buck-boost mode, the negative voltage (V<sub>INGND-PGND</sub>) risks damage to the IC. 15) The part latches when the ISET or IREF pin detect a short or open fault before or after start-up, with FAULT pulled low.

- 16) In order to avoid mistriggering low ILED protection, ILED should not be set below the low ILED rising threshold. In addition, ensure ILED does not drop below the low I<sub>LED</sub> rising threshold when the power derating is active in buck-boost mode.

# **Over-Current Protection (OCP)**

The MPQ7231 supports cycle-by-cycle peak current-limit protection.  $I_L$  is monitored while the HS-FET is on. If  $I_L$  exceeds the current limit (8A when  $I_{LED}$  is set above 800mA, and 4.25A when  $I_{LED}$  is set below 800mA), the HS-FET turns off immediately. Then the LS-FET turns on to discharge the energy and  $I_L$  decreases. The HS-FET remains off unless  $I_L$  drops to 0A. Afterward, another HS-FET on cycle begins. If an OC condition remains after three continuous attempts, then the part latches off and reports a failure with FAULT asserted.

#### **Load Dump Protection**