# FAN7085\_GF085 High Side Gate Driver with Recharge FET

#### **Features**

- · Qualified to AEC Q100

- Floating channel designed for bootstrap operation fully operational up to 300V.

- · Tolerance to negative transient voltage on VS pin

- dv/dt immune.

- · Gate drive supply range from 4.5V to 20V

- · Under-voltage lockout

- · CMOS Schmitt-triggered inputs with pull-down and pull-up

- · High side output out of phase with input (Inverted input)

- · Reset input

- · Internal recharge FET for bootstrap refresh

#### **Typical Applications**

- · Diesel and gasoline injectors/valves

- · MOSFET-and IGBT high side driver applications

For Fairchild's definition of "green" Eco Status, please visit: <a href="http://www.fairchildsemi.com/company/green/rohs\_green.html">http://www.fairchildsemi.com/company/green/rohs\_green.html</a>

#### Description

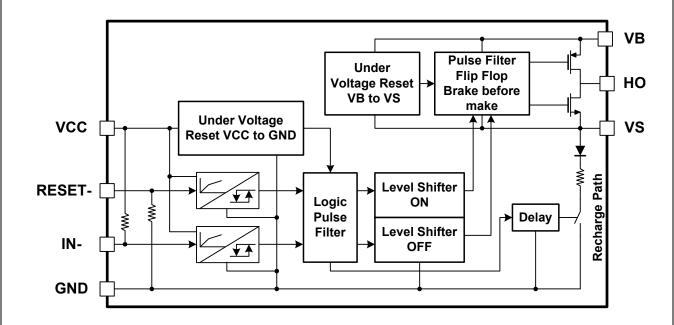

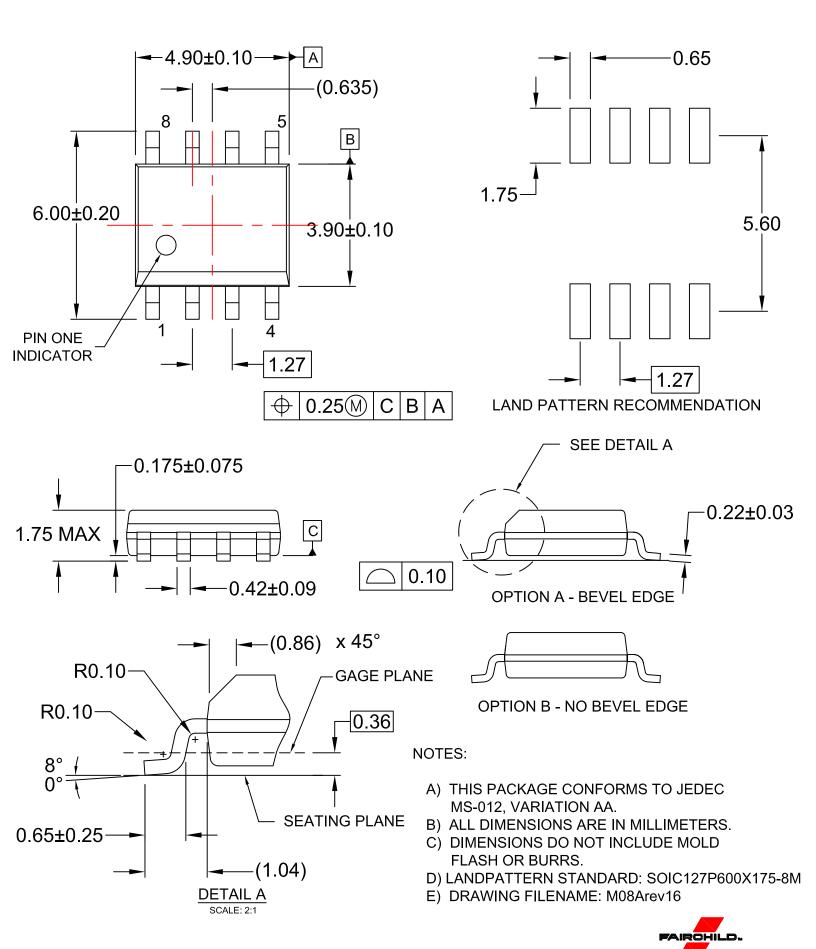

The FAN7085\_GF085 is a high-side gate drive IC with reset input and built-in recharge FET. It is designed for high voltage and high speed driving of MOSFET or IGBT, which operates up to 300V. Fairchild's high-voltage process and common-mode noise cancellation technique provide stable operation in the high side driver under high-dV/dt noise circumstances. Logic input is compatible with standard CMOS outputs. The UVLO circuits prevent from malfunction when VCC and VBS are lower than the specified threshold voltage. It is available with space saving SOIC-8 Package. Minimum source and sink current capability of output driver is 250mA and 250mA. Built-in recharge FET to refresh bootstrap circuit is very useful for circuit topology requiring switches on low and high side of load.

#### **Ordering Information**

| Device          | Package | Operating Temp. |  |  |

|-----------------|---------|-----------------|--|--|

| FAN7085M_GF085  | SOIC-8  | -40 °C ~ 125 °C |  |  |

| FAN7085MX_GF085 | SOIC-8  | -40 °C ~ 125 °C |  |  |

X: Tape & Reel type

# **Block Diagrams**

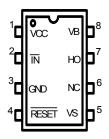

## **Pin Assignments**

#### **Pin Definitions**

| Pin Number | Pin Name | I/O | Pin Function Description                               |

|------------|----------|-----|--------------------------------------------------------|

| 1          | VCC      | Р   | Driver supply voltage, typically 5V                    |

| 2          | IN-      | I   | Driver control signal input (Negative Logic)           |

| 3          | GND      | Р   | Ground                                                 |

| 4          | RESET-   | I   | Driver enable input signal (Negative Logic)            |

| 5          | VS       | Р   | High side floating offset for MOSFET Source connection |

| 6          | NC       | -   | No connection (No Bond wire)                           |

| 7          | НО       | Α   | High side drive output for MOSFET Gate connection      |

| 8          | VB       | Р   | Driver output stage supply                             |

### **Absolute Maximum Ratings**

Absolute Maximum Ratings indicate sustained limits beyond which damage to the device may occur. All voltage parameters are absolute voltages referenced to GND.

| Parameter                                                                         | Symbol           | Min.   | Max.    | Unit |

|-----------------------------------------------------------------------------------|------------------|--------|---------|------|

| High side floating supply voltage                                                 | VBS              | -0.3   | 25      | V    |

| High side driver output stage voltage Neg. transient: 0.5 ms, external MOSFET off | VB               | -5     | 325     | V    |

| High side floating supply offset voltage Neg. transient 0.2 us                    | Vs               | -25    | 300     | V    |

| High side floating output voltage                                                 | VHO              | VS-0.3 | VB+0.3  | V    |

| Supply voltage                                                                    | Vcc              | -0.3   | 25      | V    |

| Input voltage for IN-                                                             | VIN              | -0.3   | Vcc+0.3 | V    |

| Input voltage for RESET-                                                          | VRES             | -0.3   | Vcc+0.3 | V    |

| Power Dissipation 1)                                                              | Pd               |        | 0.625   | W    |

| Thermal resistance, junction to ambient 1)                                        | Rthja            |        | 200     | °C/W |

| Electrostatic discharge voltage<br>(Human Body Model)                             | V <sub>ESD</sub> | 1.5K   |         | V    |

| Charge device model                                                               | $V_{CDM}$        | 500    |         | V    |

| Junction Temperature                                                              | Tj               |        | 150     | °C   |

| Storage Temperature                                                               | T <sub>S</sub>   | -55    | 150     | °C   |

Note: 1) The thermal resistance and power dissipation rating are measured bellow conditions;

# **Recommended Operating Conditions**

For proper operation the device should be used within the recommended conditions.-40°C <= Ta <= 125°C

| Parameter                                                          | Symbol                | Min.   | Max.  | Unit |

|--------------------------------------------------------------------|-----------------------|--------|-------|------|

| High side floating supply voltage(DC) Transient:-10V@ 0.2 us       | VB                    | VS+4.5 | VS+20 | V    |

| High side floating supply offset voltage(DC) @VBS=7V               | Vs                    | -3     | 300   | V    |

| High side floating supply offset voltage(Transient) 0.2us @VBS<25V | Vs                    | -25    | 300   | V    |

| High side floating output voltage                                  | VHO                   | Vs     | VB    | V    |

| Allowable offset voltage Slew Rate 1)                              | dv/dt                 | -      | 50    | V/ns |

| Supply voltage for logic part                                      | Vcc                   | 4.5    | 20    | V    |

| Input voltage for IN-                                              | VIN                   | 0      | Vcc   | V    |

| Input voltage for RESET-                                           | VRESET                | 0      | Vcc   | V    |

| Switching frequency <sup>2)</sup>                                  | Fs                    |        | 200K  | Hz   |

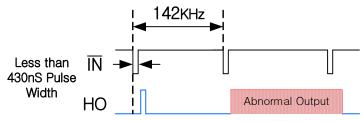

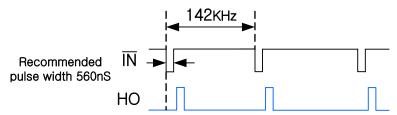

| Minimum low input width 3)                                         | tIN(low,min)          | 560    | -     | ns   |

| Minimum high input width 3)                                        | tIN(high,min)         | 60     | -     | ns   |

| Minimum operating voltage of VB related to GND                     | VB(MIN) <sup>4)</sup> | 4      | -     | V    |

| Ambient temperature                                                | Та                    | -40    | 125   | °C   |

Note: 1) Guaranteed by design.

JESD51-2: Integrated Circuit Thermal Test Method Environmental Conditions - Natural condition(StillAir)

JESD51-3: Low Effective Thermal Conductivity Test Board for Leaded Surface Mount Package

<sup>2)</sup> Duty = 0.5, VBS >=7V

<sup>3)</sup> Guaranteed by design. Pulse widths below the specified values, may be ignored. Output will either follow the input signal or will ignore it. No false output state is guaranteed when minimum input width is smaller than tin 4) Guaranteed by design

#### **Statics Electrical Characteristics**

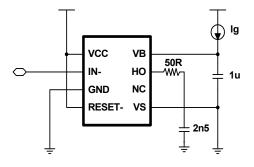

Unless otherwise specified, -40°C <= Ta <= 125°C, VCC = 5V, VBS = 7V, VS = 0V, VRESET = 5V, RL =  $50\Omega$ , CL = 2.5nF.

| Parameter                                                 | Symbol           | Conditions                                                  | Min.       | Тур. | Max.     | Unit     |  |

|-----------------------------------------------------------|------------------|-------------------------------------------------------------|------------|------|----------|----------|--|

| VCC and VBS Supply Characteristics                        |                  |                                                             |            |      |          |          |  |

| VCC and VBS supply under voltage positive going threshold | VCCUV+<br>VBSUV+ | VCc and VBS rising from 0V                                  | -          | 3.7  | 4.3      | V        |  |

| VCC and VBS supply under voltage negative going threshold | VCCUV-<br>VBSUV- | Vcc and VBS dropping from 5V                                | 2.8        | 3.4  | -        | V        |  |

| VCC and VBS under voltage hysteresis                      | VCCUVH<br>VBSUVH | -                                                           | 0.02       | 0.3  | -        | V        |  |

| Under voltage lockout response time                       | tduvcc<br>tduvbs | VCC: 6.5V->2.4V or 2.4V->6.5V VBS: 6.5V->2.4V or 2.4V->6.5V | 0.5<br>0.5 |      | 20<br>20 | us<br>us |  |

| Offset supply leakage current                             | ILK              | VB=VS=300V                                                  | -          | -    | 200      | uA       |  |

| Quiescent Vcc supply current                              | IQCC             | Vcc=20V                                                     | -          | -    | 500      | uA       |  |

| Quiescent VBS supply current                              | IQBS1            | Static mode,<br>VBS=7V, VIN=0 or 5V                         |            |      | 100      | uA       |  |

| Quiescent VBS supply current                              | IQBS2            | Static mode,<br>VBS=16V, VIN=0 or 5V                        |            |      | 200      | uA       |  |

| VBS drop due to output turn-on (Design guaranty)          | ΔVBS             | VBS=7V, Cbs=1uF, tdig-in=3uS,<br>tTEST=100uS                |            |      | 210      | mV       |  |

| Input Characteristics                                     | l .              |                                                             |            |      | <u> </u> |          |  |

| High logic level input voltage for IN-                    | VIH              |                                                             | 0.6VCC     | -    | -        | V        |  |

| Low logic level input voltage for IN-                     | VIL              |                                                             | -          | -    | 0.28VCC  | V        |  |

| Low logic level input bias current for IN-                | IIN-             | VIN=0                                                       | 5          | 25   | 60       | uA       |  |

| High logic level input bias current for IN-               | lin+             | VIN=5V                                                      | -          | -    | 5        | uA       |  |

| Full up resistance at IN                                  | RIN              |                                                             | 83         | 200  | 1000     | ΚΩ       |  |

| High logic level input voltage for RESET-                 | VRH              |                                                             | 0.6Vcc     | -    | -        | V        |  |

| Low logic level input voltage for RESET-                  | VRL              |                                                             |            |      | 0.28Vcc  | V        |  |

| High logic level input current for RESET-                 | IRES+            | VRESET=5V                                                   | 5          | 25   | 60       | uA       |  |

| Low logic level input bias current for RESET-             | IRES-            | VRESET=0                                                    |            |      | 5        | uA       |  |

| Full down resistance at RESET-                            | RRES             |                                                             | 83         | 200  | 1000     | ΚΩ       |  |

| Output characteristics                                    |                  |                                                             |            |      |          |          |  |

| High level output voltage, VB - VHO                       | Voн              | IO=0                                                        | -          | -    | 0.1      | V        |  |

| Low level output voltage, VHO-GND                         | VOL              | IO=0                                                        | -          | -    | 0.1      | V        |  |

| Peak output source current                                | IO+              | VIN=5V                                                      | 250        | 450  | -        | mA       |  |

| Peak output sink current                                  | IO-              | VIN=0                                                       | 250        | 450  | -        | mA       |  |

| Equivalent output resistance                              | Rop              |                                                             |            | 15.5 | 28       | Ω        |  |

|                                                           | Ron              |                                                             |            | 15.5 | 28       | Ω        |  |

| Recharge Characteristics                                  |                  |                                                             |            |      |          |          |  |

| Recharge TR turn-on propagation delay                     | Ton_rech         |                                                             | 4          | 7.9  | 9.8      | us       |  |

| Recharge TR turn-off propagation delay                    | Toff_rech        |                                                             |            | 0.2  | 0.4      | us       |  |

| Recharge TR on-state voltage drop                         | VRECH            | Is=1mA, VIN=5V @125°C                                       |            |      | 1.2      | V        |  |

| Dead Time Characteristics                                 |                  |                                                             |            |      |          |          |  |

| High side turn-off to recharge gate turn-on               | DTHOFF           | Vcc=5V, Vs=7V                                               | 4          | 7.8  | 9.8      | us       |  |

| Recharge gate turn-off to high side turn-on               | <b>D</b> THON    | Vcc=5V, VS=7V                                               | 0.1        | 0.4  | 0.7      | us       |  |

Note: The input parameter are referenced to GND. The VO and IO parameters are referenced to GND.

# **Dynamic Electrical Characteristics**

Unless otherwise specified, -40°C <= Ta <= 125°C, VCC = 5V, VBS = 7V, VS = 0V, VRESET = 5V, RL = 50Ω, CL = 2.5nF.

| Parameter                                  | Symbol   | Conditions                                      | Min. | Тур. | Max. | Unit |

|--------------------------------------------|----------|-------------------------------------------------|------|------|------|------|

| Input-to-output turn-on propagation delay  | tplh     | 50% input level to 10% output level,<br>VS = 0V |      | 0.56 | 1    | us   |

| Input-to-output turn-off propagation delay | tphl     | 50% input level to 90% output level VS = 0V     | -    | 0.15 | 0.5  | us   |

| RESET-to-output turn-off propagation delay | tphl_res | 50% input level to 90% output level             | -    | 0.17 | 0.5  | us   |

| RESET-to-output turn-on propagation delay  | tplh_res | 50% input level to 10% output level             | -    | 0.56 | 1    | us   |

| Output rising time                         | tr1      | Tj=25°C                                         | -    | 65   | 200  | ns   |

|                                            | tr2      |                                                 |      | -    | 400  | ns   |

|                                            | tr3      | Tj=25°C,V <sub>BS</sub> =16V                    |      | 65   | 200  | ns   |

|                                            | tr4      | V <sub>B</sub> S=16V                            |      | -    | 400  | ns   |

| Output falling time                        | tf1      | Tj=25°C                                         | -    | 25   | 200  | ns   |

|                                            | tf2      |                                                 |      | -    | 300  | ns   |

|                                            | tf3      | Tj=25°C,V <sub>BS</sub> =16V                    |      | 25   | 200  | ns   |

|                                            | tf4      | V <sub>B</sub> S=16V                            |      | -    | 300  | ns   |

# **Application Information**

# 1. Logic Tables

| VCC        | VBS        | RESET- | IN-  | Но  | RechFET |

|------------|------------|--------|------|-----|---------|

| < VCCUVLO- | Х          | Х      | X    | OFF | ON      |

| X          | Х          | LOW    | X    | OFF | ON      |

| X          | Х          | X      | HIGH | OFF | ON      |

| > VCCUVLO+ | > VBSUVLO+ | HIGH   | LOW  | ON  | OFF     |

| > VCCUVLO+ | < VBSUVLO- | HIGH   | LOW  | OFF | OFF     |

#### Notes:

X means independent from signal

IN-=LOW indicates that the high side NMOS is ON

IN-=HIGH indicates that the high side NMOS is OFF

RechFET =ON indicates that the recharge MOSFET is ON

RechFET =OFF indicates that the recharge MOSFET is OFF

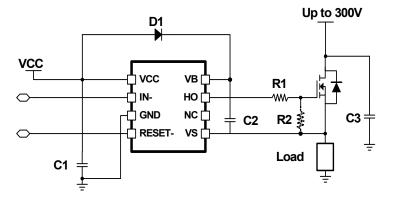

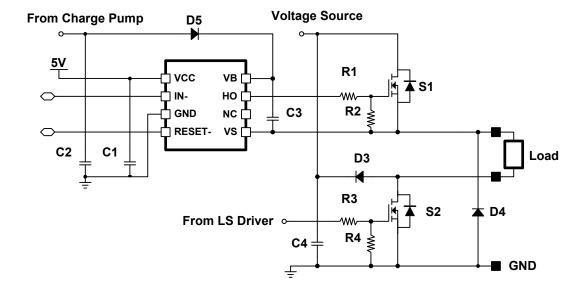

# **Typical Application Circuit**

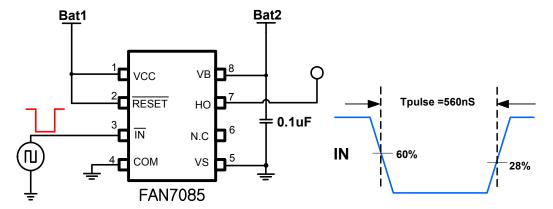

## 1. Typical Application Circuit

#### 2. Application Example

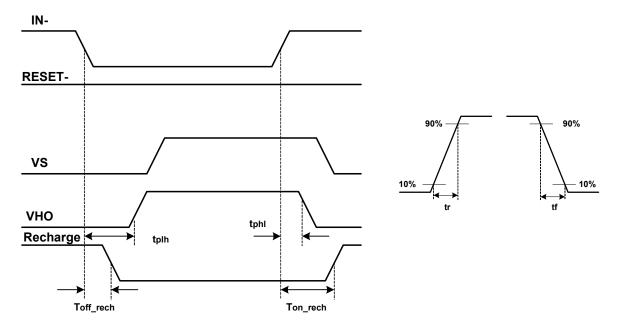

# **Input-Output Waveforms**

#### 1. Input/Output Timing Diagrams

Figure.1 Input and Output Timing Diagram and Switching Time Waveform Definition

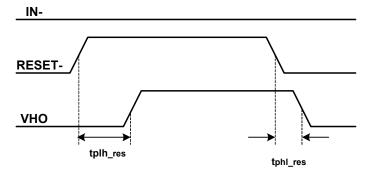

#### 2. Reset Timing Diagrams

Figure.2 Reset and Output Timing Diagram

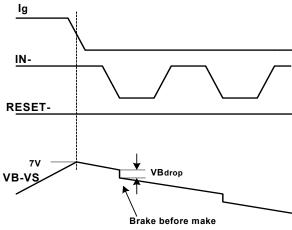

#### 3.VB Drop Voltage Diagram

Figure 3.a VB Drop Voltage Diagram

Figure 3.b VB Drop Voltage Test Circuit

#### 4.Recommendation Min. Short Pulse Width

Figure 4a.Short Pulse Width Test Circuit and Pulse Width Waveform

Figure 4b. Abnormal Output Waveform with short pulse width

Figure 4c. Recommendation of pulse width Output Waveform

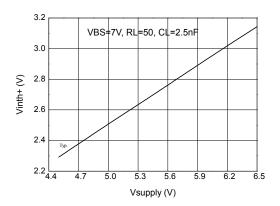

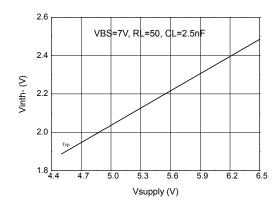

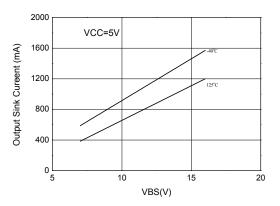

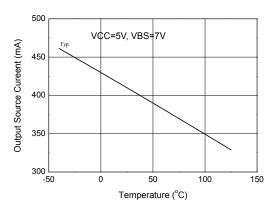

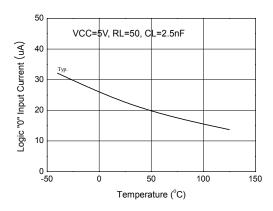

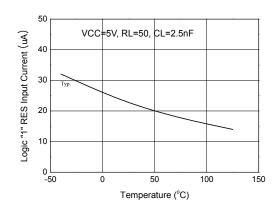

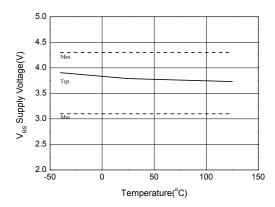

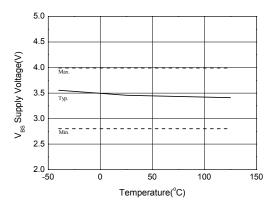

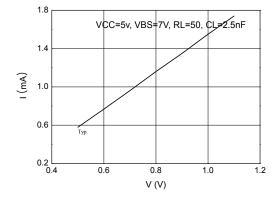

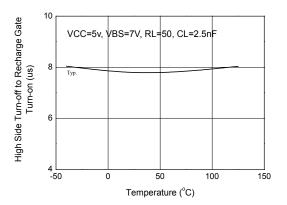

#### **Performance Graphs**

This performance graphs based on ambient temperature -40°C ~125°C

Figure 5a. Positive IN and RESET Threshold vs VCC Supply

Figure 5b. Negative IN and RESET Threshold vs VCC Supply

Figure6a. Output Sink Current vs VBS Supply

Figure6b. Output Source Current vs Temperature

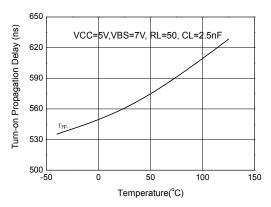

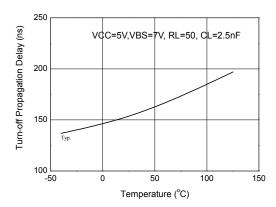

Figure 7a. Turn-On Propagation Delay Time vs Temperature

Figure 7b. Turn-Off Propagation Delay Time vs Temperature

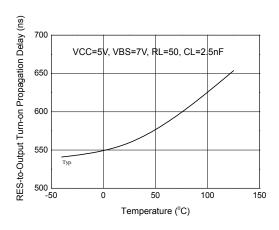

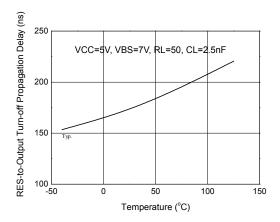

Figure 8a. RES to Output Turn-On Propagation Delay vs Temperature Figure 8b. RES to Output Turn-Off Propagation Delay vs Temperatur

Figure 9. Logic "0" IN Input Current vs Temperature

Figure 10. Logic "1" RESET Input Current vs Temperature

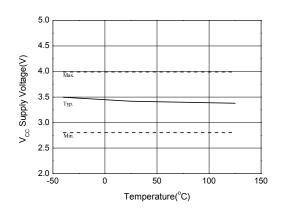

Figure 11a. VBS Under Voltage Threshold(+) vs Temperature

Figure 11b. VBS Under Voltage Threshold(-) vs Temperature

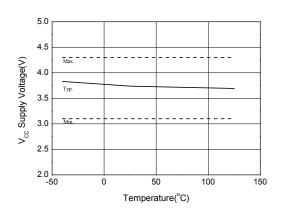

Figure 12a. VCC Under Voltage Threshold(+) vs Temperature

Figure 12b. VCC Under Voltage Threshold(-) vs Temperature

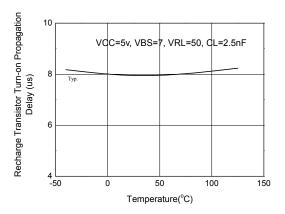

Figure 13. Recharge FET Turn-on Delay time

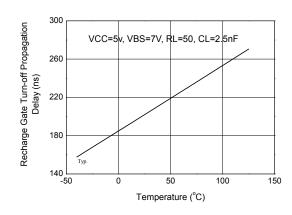

Figure 14. Recharge FET Turn-off Delay time

Figure 15. Recharge FET I-V curve

Figure 16. High Side Turn-off to Recharge FET turn-on VS Temperature

#### TRADEMARKS

The following includes registered and unregistered trademarks and service marks, owned by Fairchild Semiconductor and/or its global subsidiaries, and is not intended to be an exhaustive list of all such trademarks.

AccuPower™ F-PFS™ AttitudeEngine™ FRFET®

Global Power Resource<sup>SM</sup> Awinda<sup>®</sup> AX-CAP®\* GreenBridge™

BitSiC™ Green FPS™ Build it Now™ Green FPS™ e-Series™

CorePLUS™ Gmax™ CorePOWER™ GTO™ CROSSVOLT™ IntelliMAX™ CTL™ ISOPLANAR™

Current Transfer Logic™ Making Small Speakers Sound Louder

**DEUXPEED®** and Better™ Dual Cool™ MegaBuck™ EcoSPARK® MIČROCOUPLER™ EfficientMax™ MicroFET™ **ESBC™**

MicroPak™ **-**® MicroPak2™ MillerDrive™ Fairchild® MotionMax™ Fairchild Semiconductor® MotionGrid® FACT Quiet Series™ MTi<sup>®</sup> FACT MTx® FAST<sup>®</sup> MVN®

FastvCore™ mWSaver® FETBench™ OptoHiT™ **FPSTM** OPTOLOGIC® OPTOPLANAR®

PowerTrench® PowerXS™

Programmable Active Droop™

**QFET** QS™ Quiet Series™ RapidConfigure™

Saving our world, 1mW/W/kW at a time™

SignalWise™ SmartMax™ SMART START™

Solutions for Your Success™

SPM® STEAL TH™ SuperFET® SuperSOT™-3 SuperSOT™-6 SuperSOT™-8 SupreMOS® SyncFET™ Sync-Lock™

SYSTEM SYSTEM

TinyBoost<sup>®</sup> TinyBuck<sup>®</sup> TinyCalc™ TinyLogic<sup>®</sup> TINYOPTO™ TinvPower™ TinyPWM™ TinyWire™ TranSiC™ TriFault Detect™

TRUECURRENT®\* uSerDes™

UHC

Ultra FRFET™ UniFET™  $VCX^{TM}$ VisualMax™ VoltagePlus™ XSTM. Xsens™ 仙童™

\* Trademarks of System General Corporation, used under license by Fairchild Semiconductor.

#### DISCLAIMER

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION, OR DESIGN. TO OBTAIN THE LATEST, MOST UP-TO-DATE DATASHEET AND PRODUCT INFORMATION, VISIT OUR WEBSITE AT HTTP://WWW.FAIRCHILDSEMI.COM. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS. THESE SPECIFICATIONS DO NOT EXPAND THE TERMS OF FAIRCHILD'S WORLDWIDE TERMS AND CONDITIONS. SPECIFICALLY THE WARRANTY THEREIN, WHICH COVERS THESE PRODUCTS.

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION.

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury of the user.

- 2. A critical component in any component of a life support, device, or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

#### **ANTI-COUNTERFEITING POLICY**

Fairchild Semiconductor Corporation's Anti-Counterfeiting Policy. Fairchild's Anti-Counterfeiting Policy is also stated on our external website, www.fairchildsemi.com, under Sales Support.

Counterfeiting of semiconductor parts is a growing problem in the industry. All manufacturers of semiconductor products are experiencing counterfeiting of their parts. Customers who inadvertently purchase counterfeit parts experience many problems such as loss of brand reputation, substandard performance, failed applications, and increased cost of production and manufacturing delays. Fairchild is taking strong measures to protect ourselves and our customers from the proliferation of counterfeit parts. Fairchild strongly encourages customers to purchase Fairchild parts either directly from Fairchild or from Authorized Fairchild Distributors who are listed by country on our web page cited above. Products customers buy either from Fairchild directly or from Authorized Fairchild Distributors are genuine parts, have full traceability, meet Fairchild's quality standards for handling and storage and provide access to Fairchild's full range of up-to-date technical and product information. Fairchild and our Authorized Distributors will stand behind all warranties and will appropriately address any warranty issues that may arise. Fairchild will not provide any warranty coverage or other assistance for parts bought from Unauthorized Sources. Fairchild is committed to combat this global problem and encourage our customers to do their part in stopping this practice by buying direct or from authorized distributors.

#### PRODUCT STATUS DEFINITIONS

| Definition of Terms      |                       |                                                                                                                                                                                                     |

|--------------------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Datasheet Identification | Product Status        | Definition                                                                                                                                                                                          |

| Advance Information      | Formative / In Design | Datasheet contains the design specifications for product development. Specifications may change in any manner without notice.                                                                       |

| Preliminary              | First Production      | Datasheet contains preliminary data; supplementary data will be published at a later date. Fairchild Semiconductor reserves the right to make changes at any time without notice to improve design. |

| No Identification Needed | Full Production       | Datasheet contains final specifications. Fairchild Semiconductor reserves the right to make changes at any time without notice to improve the design.                                               |

| Obsolete                 | Not In Production     | Datasheet contains specifications on a product that is discontinued by Fairchild Semiconductor. The datasheet is for reference information only.                                                    |

Rev. 173