# X20DO4613

Data sheet 2.50 (September 2024)

#### **Publishing information**

B&R Industrial Automation GmbH B&R Strasse 1 5142 Eggelsberg Austria

Telephone: +43 7748 6586-0

Fax: +43 7748 6586-26

office@br-automation.com

#### Disclaimer

All information in this document is current as of its creation. The contents of this document are subject to change without notice. B&R Industrial Automation GmbH assumes unlimited liability in particular for technical or editorial errors in this document only (i) in the event of gross negligence or (ii) for culpably inflicted personal injury. Beyond that, liability is excluded to the extent permitted by law. Liability in cases in which the law stipulates mandatory unlimited liability (such as product liability) remains unaffected. Liability for indirect damage, consequential damage, business interruption, loss of profit or loss of information and data is excluded, in particular for damage that is directly or indirectly attributable to the delivery, performance and use of this material.

B&R Industrial Automation GmbH notes that the software and hardware designations and brand names of the respective companies used in this document are subject to general trademark, brand or patent protection.

Hardware and software from third-party suppliers referenced in this document is subject exclusively to the respective terms of use of these third-party providers. B&R Industrial Automation GmbH assumes no liability in this regard. Any recommendations made by B&R Industrial Automation GmbH are not contractual content, but merely non-binding information for which no liability is assumed. When using hardware and software from third-party suppliers, the relevant user documentation of these third-party suppliers must additionally be consulted and, in particular, the safety guidelines and technical specifications contained therein must be observed. The compatibility of the products from B&R Industrial Automation GmbH described in this document with hardware and software from third-party suppliers is not contractual content unless this has been separately agreed in individual cases; in this respect, warranty for such compatibility is excluded in any case, and it is the sole responsibility of the customer to verify this compatibility in advance.

#### **Version history**

B&R makes every effort to keep documents as current as possible. The most current versions are available for download on the B&R website (www.br-automation.com).

# 1 General information

## 1.1 Other applicable documents

For additional and supplementary information, see the following documents.

## Other applicable documents

| Document name | Title                     |

|---------------|---------------------------|

| MAX20         | X20 System user's manual  |

| MAEMV         | Installations / EMV guide |

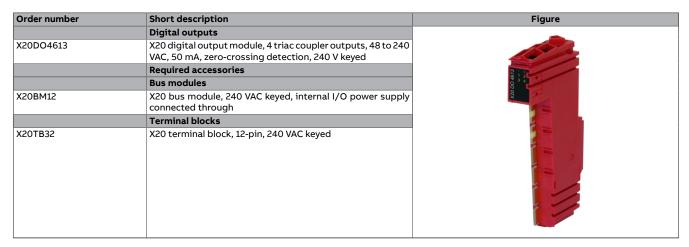

## 1.2 Order data

Table 1: X20DO4613 - Order data

## 1.3 Module description

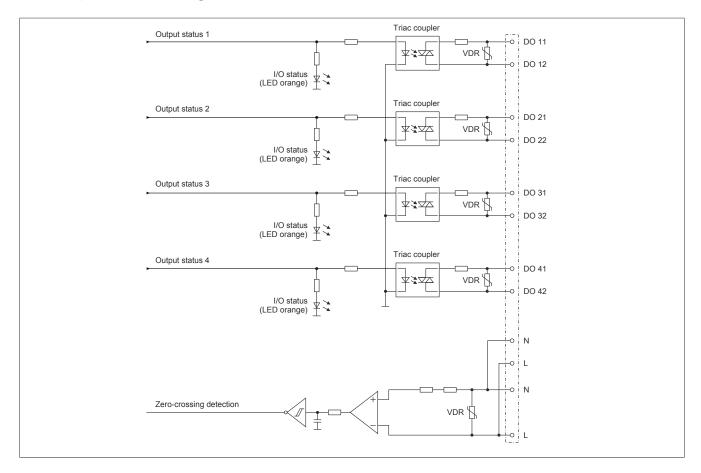

The module is a digital output module that is equipped with 4 opto-triac outputs using phase-angle control. L and N are fed to the module for zero-crossing detection.

The 4 outputs are electrically isolated from one another and are used for controlling external power triacs or nonparallel thyristors.

#### **Functions:**

- Phase angle control

- Digital outputs

- OSP mode

#### Phase angle control

Phase angle control can be used to control resistive and inductive loads.

#### **OSP** mode

In mode "OSP" (Operator Set Predefined), the user defines a digital pattern. This OSP value is output as soon as the communication between the module and master is aborted.

## Danger!

## Risk of electric shock!

The terminal block is only permitted to conduct voltage when it is connected. It is not permitted to be disconnected or connected while voltage is applied or have voltage applied to it while it is removed under any circumstances!

This module is not permitted to be the last module connected on the X2X Link network. At least one subsequent X20ZF dummy module must provide protection against contact.

4

# 2 Technical description

## 2.1 Technical data

| Order number                                  | X20D04613                                                                                  |

|-----------------------------------------------|--------------------------------------------------------------------------------------------|

| Short description                             |                                                                                            |

| I/O module                                    | 4 digital outputs for controlling external power triacs or non-parallel thyristors         |

| General information                           | . 5                                                                                        |

| B&R ID code                                   | 0xAD05                                                                                     |

| Status indicators                             | I/O function per channel, operating state, module status                                   |

| Diagnostics                                   | ,                                                                                          |

| Module run/error                              | Yes, using LED status indicator and software                                               |

| Outputs                                       | Yes, using LED status indicator                                                            |

| Power consumption                             | res, using LEB states indicates                                                            |

| Bus                                           | 0.8 W                                                                                      |

| Internal I/O                                  |                                                                                            |

| External I/O                                  |                                                                                            |

| Additional power dissipation caused by actua- | +1 W                                                                                       |

| tors (resistive) [W] 1)                       |                                                                                            |

| Certifications                                |                                                                                            |

| CE                                            | Yes                                                                                        |

| UKCA                                          | Yes                                                                                        |

| ATEX                                          | Zone 2, II 3G Ex nA nC IIA T5 Gc<br>IP20, Ta (see X20 user's manual)<br>FTZÚ 09 ATEX 0083X |

| UL                                            | cULus E115267<br>Industrial control equipment                                              |

| HazLoc                                        | cCSAus 244665 Process control equipment for hazardous locations                            |

| KC                                            | Class I, Division 2, Groups ABCD, T5 Yes                                                   |

|                                               | Tes .                                                                                      |

| Digital outputs                               | Onto trico                                                                                 |

| Variant                                       | Opto-triac                                                                                 |

| Circuit                                       | Normally open contact                                                                      |

| Nominal voltage                               | 48 to 240 VAC                                                                              |

| Max. voltage                                  | 264 VAC                                                                                    |

| Rated frequency                               | 47 to 63 Hz                                                                                |

| Nominal current at 25°C                       | 00 4                                                                                       |

| Nominal output current                        | 80 mA                                                                                      |

| Total nominal current                         | 320 mA                                                                                     |

| Current over entire temperature range         |                                                                                            |

| Output current                                | 50 mA                                                                                      |

| Summation current                             | 200 mA                                                                                     |

| Connection type                               | 2-wire connections                                                                         |

| Zero-crossing detection                       | Yes                                                                                        |

| Holding current                               | Max. 3.5 mA                                                                                |

| Leakage current                               | Max. 1.5 mA (per channel)                                                                  |

| Residual voltage (on-state voltage)           | Max. 3 V                                                                                   |

| Phase-angle control                           |                                                                                            |

| Area                                          | 5 to 95%                                                                                   |

| Resolution                                    | 1%                                                                                         |

| Accuracy (60 to 240 VAC)                      | <100 µs                                                                                    |

| Voltage monitoring L - N                      | No                                                                                         |

| Recommended wiring                            | Twisted pair cabling to the terminal pairs                                                 |

| Line length                                   | Max. 10 m                                                                                  |

| Overvoltage protection between L and N        | Yes                                                                                        |

| Insulation voltages                           |                                                                                            |

| Channel - Bus                                 | Tested at 2300 VAC                                                                         |

| Channel - Channel                             | Tested at 2300 VAC                                                                         |

| Protective circuit                            |                                                                                            |

| External                                      | Generally fuse                                                                             |

| Internal                                      | Snubber circuit (RC element) and varistor                                                  |

| Electrical properties                         |                                                                                            |

| Electrical isolation                          | Channel isolated from channel, bus and I/O power supply                                    |

Table 2: X20DO4613 - Technical data

#### **Technical description**

| Order number                           | X20DO4613                                                                           |  |  |

|----------------------------------------|-------------------------------------------------------------------------------------|--|--|

| Operating conditions                   |                                                                                     |  |  |

| Mounting orientation                   |                                                                                     |  |  |

| Horizontal                             | Yes                                                                                 |  |  |

| Vertical                               | Yes                                                                                 |  |  |

| Installation elevation above sea level |                                                                                     |  |  |

| 0 to 2000 m                            | No limitation                                                                       |  |  |

| >2000 m                                | Not permitted                                                                       |  |  |

| Degree of protection per EN 60529      | IP20                                                                                |  |  |

| Ambient conditions                     |                                                                                     |  |  |

| Temperature                            |                                                                                     |  |  |

| Operation                              |                                                                                     |  |  |

| Horizontal mounting orientation        | -25 to 60°C                                                                         |  |  |

| Vertical mounting orientation          | -25 to 50°C                                                                         |  |  |

| Derating                               | •                                                                                   |  |  |

| Storage                                | -40 to 85°C                                                                         |  |  |

| Transport                              | -40 to 85°C                                                                         |  |  |

| Relative humidity                      |                                                                                     |  |  |

| Operation                              | 5 to 95%, non-condensing                                                            |  |  |

| Storage                                | 5 to 95%, non-condensing                                                            |  |  |

| Transport                              | 5 to 95%, non-condensing                                                            |  |  |

| Mechanical properties                  |                                                                                     |  |  |

| Note                                   | Order 1x terminal block X20TB32 separately. Order 1x bus module X20BM12 separately. |  |  |

| Pitch                                  | 12.5 <sup>+0.2</sup> mm                                                             |  |  |

Table 2: X20DO4613 - Technical data

Number of outputs x Residual voltage (on-state voltage) x Nominal output current. For a calculation example, see section "Mechanical and electrical configuration" in the X20 system user's manual.

## 2.2 Status LEDs

For a description of the various operating modes, see section "Additional information - Diagnostic LEDs" in the X20 System user's manual.

| Figure             | LED   | Color                       | Status         | Description                                                    |

|--------------------|-------|-----------------------------|----------------|----------------------------------------------------------------|

|                    | r     | Green                       | Off            | Module supply not connected                                    |

|                    |       |                             | Single flash   | RESET mode                                                     |

| I processor was to |       |                             | Blinking       | PREOPERATIONAL mode                                            |

| r e                |       |                             | On             | RUN mode                                                       |

| 1 2 4              |       |                             | Flickering     | Module is in OSP state                                         |

| - 3 4              |       |                             | (approx. 10 Hz |                                                                |

| 8                  | е     | Red                         | Off            | Module supply not connected or everything OK                   |

| X20                |       |                             | On             | Error or reset status                                          |

| $\times$           |       |                             | Single flash   | Loss of zero-crossing signal (input voltage absent or too low) |

| 1                  | e + r | Red on / Green single flash |                | Invalid firmware                                               |

|                    | 1 - 4 | Orange                      |                | Control status of the corresponding digital output             |

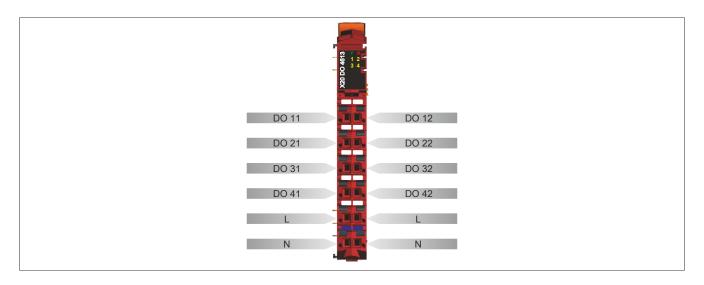

## 2.3 Pinout

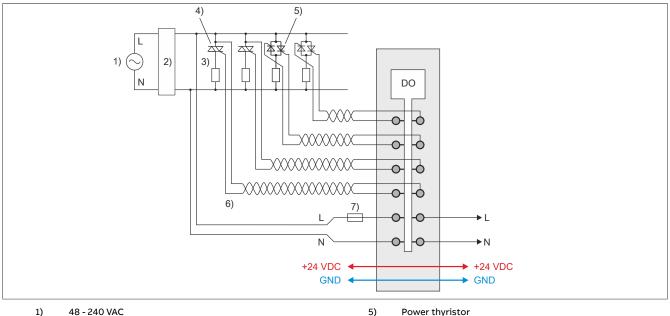

## 2.4 Connection example

- Line filter 2)

- 3) Load

- Power triac

- Twisted lines 6)

- Fuse, 0.5 A slow-blow

## 2.5 Output circuit diagram

# **3 Function description**

## 3.1 Phase angle control

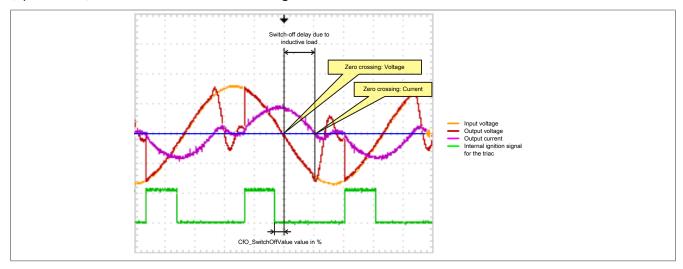

The digital output module was designed for phase angle control of resistive and inductive loads.

The module has internal zero-crossing detection. The zero-crossing detection forms the basis for a software PLL that generates 200 times the zero-crossing frequency. The output signal of the PLL forms the base clock for the PWM outputs in both digital and analog mode.

If a failure of periods or periods that are too short is detected, control of the outputs is deactivated until the PLL has settled correctly. The settling procedure can take several seconds. In addition, bit "ZeroCrossingStatus" is set, and LED Error is enabled (valid frequency range of the power supply is 45 to 65 Hz).

#### Information:

The jitter of the output signals generated by the PLL and communication can reach 0.5%.

#### Operation with inductive loads

By design, the triac output is switched off at the current zero crossing. Due to the delayed current zero crossing with inductive loads, the effect occurs that at higher output values (depending on the inductance of the load, between 50 and 100%) the triac is fired again even though it has not yet been switched off. A full wave is therefore output. This results in the available control range (0 to 100%) being changed.

The physically output value no longer changes if the activation goes beyond the point of full-wave control (up to 100%). However, this does not damage the module.

#### 3.1.1 Output values

8

The output value of the outputs defined as analog (unit: percent) is switched through to the drive ports synchronously with the mains. The analog value is output to the triac drive port with a resolution of 1% in the range (Output value > SwitchOffValue) and (Output value  $\leq 95\%$ ).

Changes to the output value are applied with the next positive half-wave.

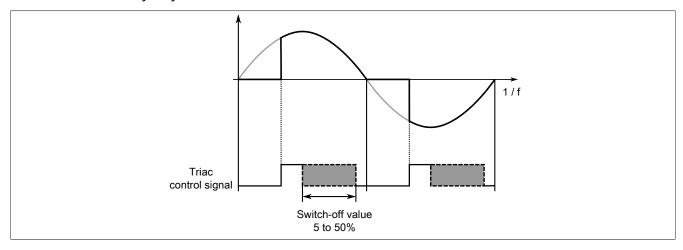

#### 3.1.2 Deactivation time

The deactivation time defines how far before the zero crossing the internal control signal for the triac is switched off. Adjusting this value may be necessary in order to avoid misfiring of the triac in the event of slight disturbances in the mains frequency.

For small loads, it is important to ensure that the switch-off value is not set too high (too early) in order to avoid premature deactivation.

The triac can naturally only be fired before the set deactivation time.

## 3.1.3 Behavior with zero-crossing faults

The switching behavior of the trigger can be adjusted. After a configured number of zero crossing errors, the output is switched off for at least 3 periods.

This is followed by one of the following possible synchronizations to the zero signal:

#### Quick adjustment

With this option, the trigger point of the firing is regulated after each individual zero crossing and input jitter.

- Advantage: Extended tolerance and faster response to mains frequency fluctuations

- **Disadvantage:** Increased switch-on jitter of the firing signal of ±100 μs to the zero-crossing signal

## PLL adjustment

With this option, the intervals between the zero crossings are measured and the PLL frequency is adjusted according to this measurement.

- Advantage: Jitter-free firing signal

- **Disadvantage:** After switching off the output, additional measuring phases are required before the output can be switched on again.

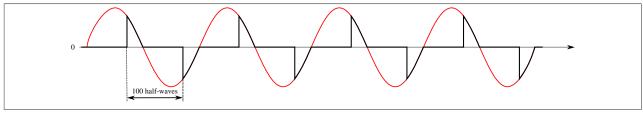

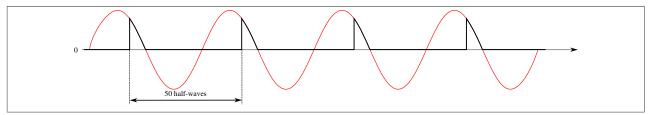

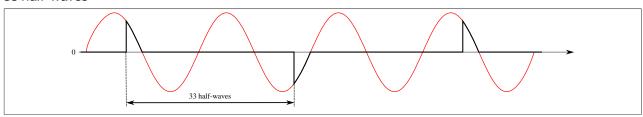

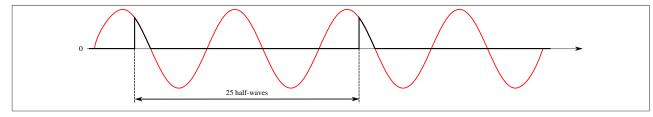

#### 3.1.4 Setting the half-wave pattern

In "Function model 2 - Frequency mode", the output of half-wave patterns can be set in different frequencies. The commutation angle of the outputs is not affected by this. The following frequency patterns can be configured:

· 100 half-waves

50 half-waves

· 33 half-waves

· 25 half-waves

In multi-channel operation, the different channels should be operated with delayed half-waves to ensure a more even load on the module.

## 3.2 Digital outputs

This module is equipped with 4 digital outputs.

The output state of the outputs defined as digital is transferred to the output ports of the drive circuit in synchronization with the connected mains. The switch-on state is applied at the voltage zero crossing of the positive half-wave and the switch-off state at the current zero crossing of each half-wave.

Packed outputs (only function model 0 - Standard)

Setting "Packed outputs" in the Automation Studio I/O configuration can be used to determine whether all bits of the register should be applied as individual data points in the Automation Studio I/O mapping (e.g. "DigitalOutput01 to DigitalOutputxx") or whether the register should be displayed as a single USINT data point (e.g. "DigitalOutput").

## Information:

The register is described in "Switching state of digital outputs 1 to 4" on page 14.

#### 3.3 OSP mode

In function model "OSP" (Operator Set Predefined), the user defines a digital pattern. This OSP value is output as soon as the communication between the module and master is aborted.

#### 3.3.1 Hardware requirements

In order to use OSP mode sensibly, it should be ensured when setting up the application that the power supply of the output module and controller are designed to be independent of each other.

#### 3.3.2 Functionality

The user has the choice between 2 OSP modes:

- · Retain last valid value

- · Replace with static value

In the first case, the module retains the last value recognized as a valid output status.

When selecting mode "Replace with static value", a plausible output value must be entered in the associated value register. When an OSP event occurs, this value is output instead of the value currently requested by the task.

If an OSP event occurs, e.g. communication between the module and master controller aborted, then bit OSPValid is reset on the module. The module enters the OSP state and output occurs according to the configuration in register OSPMode.

#### The following generally applies:

Even after regeneration of the communication channel, the OSP replacement value is still pending. The OSP state is only exited again when a set OSPValid bit is transferred.

When the master controller is restarted, bit OSPValid bit is reinitialized in the master controller. It must be set once more by the application and transferred via the bus. In the event of brief communication errors between the module and master controller (e.g. due to EMC), the cyclic registers fail to refresh for several bus cycles. Within the module, bit OSPValid is reset; the set bit is retained in the controller, however. During the next successful transfer, the module-internal OSPValid bit is set again and the module automatically returns to normal mode.

If the task in the master controller needs the information about which output mode the module is currently in, bit ModulOK can be evaluated.

## Warning!

If bit OSPValid bit is reset to "0" by the module, the output status no longer depends on the responsible task in the master controller. Nevertheless, output is made depending on the configuration of the OSP replacement value.

## Information:

The registers are described in "Function model "OSP"" on page 18.

# 4 Commissioning

## 4.1 Using the module on the bus controller

Function model 254 "Bus controller" is used by default only by non-configurable bus controllers. All other bus controllers can use other registers and functions depending on the fieldbus used.

For detailed information, see section "Additional information - Using I/O modules on the bus controller" in the X20 user's manual (version 3.50 or later).

## 4.1.1 CAN I/O bus controller

The module occupies 1 analog logical slot on CAN I/O.

# **5 Register description**

## 5.1 General data points

In addition to the registers described in the register description, the module has additional general data points. These are not module-specific but contain general information such as serial number and hardware variant.

General data points are described in section "Additional information - General data points" in the X20 System user's manual.

## 5.2 Function model 0 - Standard and Function model 2 - Frequency mode

The only difference between function model 2 and function model 0 is the possibility of generating half-wave patterns in various frequencies. Register 18 "CfO\_Frequency" is an additional register for this.

| Register     | Name                              | Data type | R      | tead       | Write  |            |

|--------------|-----------------------------------|-----------|--------|------------|--------|------------|

|              |                                   |           | Cyclic | Non-cyclic | Cyclic | Non-cyclic |

| Configuratio | on - General                      |           |        |            |        |            |

| 2 + N * 2    | AnalogOutput0N (Index N = 1 to 4) | USINT     |        |            | •      |            |

| 18           | CfO_Frequency                     | UINT      |        |            |        | •          |

| 18 + N * 2   | ConfigOutput0N (Index N = 1 to 4) | USINT     |        |            |        | •          |

| 28           | ConfigOutput05                    | USINT     |        |            |        | •          |

| 29           | CfO_OutputTolerance               | USINT     |        |            |        | •          |

| Communicat   | ion                               |           |        |            |        |            |

| 2            | DigitalOutput                     | USINT     |        |            | •      |            |

|              | DigitalOutput01                   | Bit 0     |        |            |        |            |

|              |                                   |           |        |            |        |            |

|              | DigitalOutput04                   | Bit 3     |        |            |        |            |

| 30           | StatusInput01                     | USINT     | •      |            |        |            |

|              | ZeroCrossingInput                 | Bit 4     |        |            |        |            |

|              | ZeroCrossingStatus                | Bit 7     |        |            |        |            |

## 5.3 Function model 1 - OSP

| Register     | Name                                      | Data type | Read   |            | Write  |            |

|--------------|-------------------------------------------|-----------|--------|------------|--------|------------|

|              |                                           |           | Cyclic | Non-cyclic | Cyclic | Non-cyclic |

| Configuratio | n - General                               |           |        |            |        |            |

| 2 + N * 2    | AnalogOutputON (Index N = 1 to 4)         | USINT     |        |            | •      |            |

| 18 + N * 2   | ConfigOutput0N (Index N = 1 to 4)         | USINT     |        |            |        | •          |

| 28           | ConfigOutput05                            | USINT     |        |            |        | •          |

| 29           | CfO_OutputTolerance                       | USINT     |        |            |        | •          |

| Configuratio | n - OSP                                   | <u> </u>  |        |            |        |            |

| 34           | Enabling OPS output in the module         | USINT     |        |            | •      |            |

|              | OSPValid                                  | Bit 0     |        |            |        |            |

| 32           | CfgOSPMode                                | USINT     |        |            |        | •          |

| 36           | CfgOSPValue                               | USINT     |        |            |        | •          |

| 36 + N * 2   | CfgOSPValue0N (Index N = 1 to 4)          | USINT     |        |            |        | •          |

| Communicat   | ion                                       |           |        |            |        |            |

| 2            | Switching state of digital outputs 1 to 4 | USINT     |        |            | •      |            |

|              | DigitalOutput01                           | Bit 0     |        |            |        | 1          |

|              |                                           |           |        |            |        |            |

|              | DigitalOutput04                           | Bit 3     |        |            |        |            |

| 30           | Status of the outputs                     | USINT     | •      |            |        |            |

|              | ZeroCrossingInput                         | Bit 4     |        |            |        |            |

|              | ZeroCrossingStatus                        | Bit 7     |        |            |        |            |

## 5.4 Function model 254 - Bus controller

| Register      | Offset                  | Name                              | Data type | Read   |            | Write  |            |  |  |

|---------------|-------------------------|-----------------------------------|-----------|--------|------------|--------|------------|--|--|

|               |                         |                                   |           | Cyclic | Non-cyclic | Cyclic | Non-cyclic |  |  |

| Configuration | Configuration - General |                                   |           |        |            |        |            |  |  |

| 2 + N * 2     | (N-1) * 2               | AnalogOutputON (Index N = 1 to 4) | USINT     |        |            | •      |            |  |  |

| 18 + N * 2    | -                       | ConfigOutputON (Index N = 1 to 4) | USINT     |        |            |        | •          |  |  |

| 28            | -                       | ConfigOutput05                    | USINT     |        |            |        | •          |  |  |

| 29            | -                       | CfO_OutputTolerance               | USINT     |        |            |        | •          |  |  |

| Communication | on                      |                                   |           |        |            |        |            |  |  |

| 30            | 0                       | Status of the outputs             | USINT     | •      |            |        |            |  |  |

|               |                         | ZeroCrossingInput                 | Bit 4     |        |            |        |            |  |  |

|               |                         | ZeroCrossingStatus                | Bit 7     |        |            |        |            |  |  |

<sup>1)</sup> The offset specifies the position of the register within the CAN object.

## 5.5 Digital outputs

The output state of the outputs defined as digital is transferred to the output ports of the drive circuit in synchronization with the connected mains.

## 5.5.1 Switching state of digital outputs 1 to 4

Name:

DigitalOutput

DigitalOutput01 to DigitalOutput04

This register stores the switching state of digital outputs 1 to 4.

| Data type | Values                 | Information <sup>1)</sup>                              |  |

|-----------|------------------------|--------------------------------------------------------|--|

| USINT     | 0 to 15                | Packed outputs = On                                    |  |

|           |                        | Data point: "DigitalOutput"                            |  |

|           | See the bit structure. | Packed outputs = Off or function model ≠ 0 - Standard. |  |

|           |                        | Data points: "DigitalOutput01" to "DigitalOutput04"    |  |

See "Digital outputs" on page 10.

#### Bit structure:

| Bit | Name            | Value | Information             |

|-----|-----------------|-------|-------------------------|

| 0   | DigitalOutput01 | 0     | Digital output 01 reset |

|     |                 | 1     | Digital output 01 set   |

|     |                 |       |                         |

| 3   | DigitalOutput04 | 0     | Digital output 04 reset |

|     |                 | 1     | Digital output 04 set   |

## Information:

The states in these registers are only applied if the configuration of the channels in "Configuration of the output channels" on page 17 is set to DIGITAL accordingly.

When using setting "Packed outputs", ALL channels must be set to DIGITAL. Mixed operation is not possible.

## 5.6 Phase angle control

## 5.6.1 Commutation angle for analog outputs 1 - 4

Name:

AnalogOutput01 to AnalogOutput04

These registers are used to set the commutation angle for phase angle control.

Values between 0 and 100 correspond to the output value for the respective channel in percent. Values above 100 correspond to 100%.

| Data type | Value    |

|-----------|----------|

| USINT     | 0 to 100 |

## Information:

The switch-on angles of the phase angle control set in these registers are only applied if the configuration of the channels in "ConfigOutput05" on page 17 is set to ANALOG accordingly.

## 5.6.2 Status of the outputs

Name:

ZeroCrossingInput ZeroCrossingStatus StatusInput01

The operating status of the outputs is mapped in this register.

| Data type | Value                  | Information <sup>1)</sup>                                 |  |

|-----------|------------------------|-----------------------------------------------------------|--|

| USINT     | 0 to 17                | Packed outputs = On                                       |  |

|           |                        | Data point: "StatusInput01"                               |  |

|           | See the bit structure. | Packed outputs = Off or function model ≠ 0 - Standard.    |  |

|           |                        | Data points: "ZeroCrossingInput" and "ZeroCrossingStatus" |  |

<sup>1)</sup> See "Digital outputs" on page 10.

#### Bit structure:

| Bit   | Name               | Value | Information                                     |

|-------|--------------------|-------|-------------------------------------------------|

| 0 - 3 | Reserved           | -     |                                                 |

| 4     | ZeroCrossingInput  | 0     | Zero cross signal during the negative half-wave |

|       |                    | 1     | Zero cross signal during the positive half-wave |

| 5 - 6 | Reserved           | -     |                                                 |

| 7     | ZeroCrossingStatus | 0     | Zero cross signal OK                            |

|       |                    | 1     | Zero cross signal has dropped out               |

#### 5.6.3 Configuring the half-wave pattern

Name:

CfO Frequency

This register can only be used in function model 2 - Frequency mode and makes it possible to configure the output of half-wave patterns in various frequencies. For details, see Setting the half-wave pattern.

| Data type | Values                 |

|-----------|------------------------|

| UINT      | See the bit structure. |

#### Bit structure:

| Bit     | Description | Value        | Information                                  |

|---------|-------------|--------------|----------------------------------------------|

| 0 - 3   | Channel 1   | 0000         | 100 half-waves/second                        |

|         |             | 0001         | 50 half-waves/second                         |

|         |             | 0010         | 25 half-waves/second                         |

|         |             | 0011         | 33 half-waves/second                         |

|         |             | 0101         | 50 half-waves/second delayed by 1 half-wave  |

|         |             | 0110         | 25 half-waves/second delayed by 2 half-waves |

|         |             | 0111         | 33 half-waves/second delayed by 1 half-wave  |

| 4 - 7   | Channel 2   | 0000 to 0111 | See channel 1.                               |

| 8 - 11  | Channel 3   | 0000 to 0111 | See channel 1.                               |

| 12 - 15 | Channel 4   | 0000 to 0111 | See channel 1                                |

## Information:

This function is only available with firmware version 940 or later. This can be installed starting with hardware variant 8.

## 5.6.4 Setting the switch-off time

Name

ConfigOutput01 to ConfigOutput04

This register defines how far before the zero crossing the internal drive signal for the triac is switched off. Increasing this value may be necessary in order to avoid misfiring of the triac in the event of slight disturbances in the mains frequency. For details, see "Deactivation time" on page 9.

"SwitchOffValue" in the Automation Studio I/O configuration.

| Data type | Value   | Description                       |

|-----------|---------|-----------------------------------|

| USINT     | 5 to 50 | Switch-off time in %.             |

|           |         | Bus controller default setting: 0 |

|           | *       |                                   |

## 5.6.5 Configuration of the output channels

Name:

ConfigOutput05

The configuration of the output channels is stored in this register.

"Output type digital/analog" and "Output type full/half wave" in the Automation Studio I/O configuration

| Data type | Values                 | Bus controller default setting |

|-----------|------------------------|--------------------------------|

| USINT     | See the bit structure. | 15                             |

#### Bit structure:

| Bit | Description                                          | Value | Information                                                                                                                                             |

|-----|------------------------------------------------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | Channel 1: Digital/Analog output                     | 0     | Output channel 1 is defined as a digital output. The output status is defined by bit 0 in registers "DigitalOutput 1 - 4" on page 14.                   |

|     |                                                      | 1     | Output channel 1 is defined as an analog output. The output status is defined by register "AnalogOutput01" on page 15 (bus controller default setting). |

|     |                                                      |       |                                                                                                                                                         |

| 3   | Channel 4: Digital/Analog output                     | 0     | Output channel 4 is defined as a digital output. The output status is defined by bit 1 in registers "DigitalOutput 1 - 4" on page 14.                   |

|     |                                                      | 1     | Output channel 2 is defined as an analog output. The output status is defined by register "AnalogOutput04" on page 15 (bus controller default setting). |

| 4   | Channel 1: Full-wave/Half-wave control <sup>1)</sup> | 0     | Full-wave control on output channel 1 (bus controller default setting)                                                                                  |

|     |                                                      | 1     | Negative half-wave on output channel 1 is suppressed.                                                                                                   |

|     |                                                      |       |                                                                                                                                                         |

| 7   | Channel 4: Full-wave/Half-wave control <sup>1)</sup> | 0     | Full-wave control on output channel 4 (bus controller default setting)                                                                                  |

|     |                                                      | 1     | Negative half-wave on output channel 4 is suppressed.                                                                                                   |

<sup>1)</sup> Not available in function model 2 - Frequency mode.

## 5.6.6 Switching behavior for zero-crossing errors

Name:

CfO\_OutputTolerance

This register can be used to set the switching behavior of the trigger. After the number of zero-crossing errors configured in Bit 0 to 4, the output is switched off for at least 3 periods. This is followed by synchronization with the zero signal according to Bit 7.

| Data type | Values                 | Bus controller default setting |

|-----------|------------------------|--------------------------------|

| USINT     | See the bit structure. | 0                              |

#### Bit structure:

| Bit   | Description        | Value   | Information                                       |

|-------|--------------------|---------|---------------------------------------------------|

| 0 - 4 | Trigger for Resync | 0 to 30 | Number of zero crossing errors.                   |

|       |                    |         | Bus controller default setting: 0                 |

| 5 - 6 | Reserved           | -       |                                                   |

| 7     | Fast settling      | 0       | Quick adjustment (bus controller default setting) |

|       |                    | 1       | PLL adjustment                                    |

## Information:

This function is available starting with Firmware version 928. This can be installed with hardware version 7 and hardware revision B4 or higher.

#### 5.7 Function model "OSP"

In function model "OSP" (Operator Set Predefined), the user defines a digital pattern. This OSP value is output as soon as the communication between the module and master is aborted.

## 5.7.1 Enabling OPS output in the module

Name:

**OSPValid**

This data point makes it possible to start the output of the module and request the use of OSP during operation.

Bit OSPValid exists once on the module and is managed by the user task. It must be set to start the enabled channels. As long as bit OSPValid remains set in the module, the module behaves the same as in function model "Standard".

| Data type | Values                 |

|-----------|------------------------|

| USINT     | See the bit structure. |

#### Bit structure:

| Bit   | Description | Value | Information                                                        |

|-------|-------------|-------|--------------------------------------------------------------------|

| 0     | 0 OSPValid  | 0     | Request OSP operation (after initial startup or module in standby) |

|       |             | 1     | Request normal operation                                           |

| 1 - 7 | Reserved    | 0     |                                                                    |

## 5.7.2 Setting OSP mode

Name:

CfgOSPMode

This register controls the behavior of a channel when using OSP.

| Data type | Values | Explanation               |  |

|-----------|--------|---------------------------|--|

| USINT     | 0      | Replace with static value |  |

| 1         |        | Retain last valid value   |  |

#### 5.7.3 Defining an OSP-digital output value

Name:

**CfgOSPValue**

This register contains the digital output value that is output in "Replace with static value" mode during OSP mode.

| Data type | Values                 |

|-----------|------------------------|

| USINT     | See the bit structure. |

#### Bit structure:

| Bit | Description | Value  | Information                                  |

|-----|-------------|--------|----------------------------------------------|

| 0   |             | 0 or 1 | OSP output value for channel DigitalOutput00 |

|     |             |        |                                              |

| x   |             | 0 or 1 | OSP output value for channel DigitalOutput0x |

## Warning!

"OSPValue" is only applied by the module if bit "OSPValid" has been set in the module.

## 5.7.4 Define the OSP analog output value

Name:

CfgOSPValue01 to CfgOSPValue04

This register contains the analog output value, which is output in "Replace with static value" mode during OSP operation.

| Data type | Value    |

|-----------|----------|

| USINT     | 0 to 100 |

## Warning!

"OSPValue" is only applied by the module if bit "OSPValid" has been set in the module.

## 5.8 Minimum cycle time

The minimum cycle time specifies how far the bus cycle can be reduced without communication errors occurring. It is important to note that very fast cycles reduce the idle time available for handling monitoring, diagnostics and acyclic commands.

| Minimum cycle time |        |  |

|--------------------|--------|--|

| All channels       | 250 μs |  |

## 5.9 Minimum I/O update time

The minimum I/O update time specifies how far the bus cycle can be reduced so that an I/O update is performed in each cycle.

| Minimum I/O update time |        |  |

|-------------------------|--------|--|

| All channels            | 150 μs |  |