# Datasheet

## SL917 NCP Module

Version 0.7

### **Revision History**

|              | Date        | sion  | Notes           | Contributors   | Approver  |

|--------------|-------------|-------|-----------------|----------------|-----------|

| Dave Neperud | 19 Feb 2025 | 0.7 1 | Initial Release | Dave Drogowski | Andy Ross |

|              |             |       |                 | Dave Neperud   |           |

## ezurio

### Contents

| 1.  | Feature List                                      | 2  |

|-----|---------------------------------------------------|----|

| 2.  | Ordering Information                              | 5  |

| 3.  | Applications                                      | 6  |

| 4.  | Block Diagrams                                    | 7  |

| 5.  | System Overview                                   | 9  |

| 6.  | Pinout and Pin Description1                       | 3  |

| 7.  | Electrical Specifications 2                       | 22 |

| 8.  | Reference Schematics, BOM and Layout Guidelines 4 | -5 |

| 9.  | Package Specifications                            | 3  |

| 10. | Soldering Recommendations 6                       | ;9 |

| 11. | Tape and Reel                                     | '0 |

| 12. | Certifications                                    | '1 |

| 13. | Documentation and Support                         | '5 |

| 14. | Revision History                                  | '6 |

| 15. | Additional Information                            | 7  |

# ezurio

## SL917 Wi-Fi<sup>®</sup> and Bluetooth<sup>®</sup> LE Network Co-Processor Connectivity Module Datasheet

Ezurio's SL917 Network Co-Processor Connectivity module is based on the Silicon Labs SiWN917M, which is our lowest power Wi-Fi 6 silicon, ideal for ultra-low power IoT wireless devices using Wi-Fi®, Bluetooth, and IP networking for secure cloud connectivity. It has an integrated built-in wireless subsystem, advanced security, and integrated power- management. It has a multi-threaded Network Wireless Processor (NWP) running up to 160 MHz. All the networking and wireless stacks run on independent threads of the multi-threaded processor. The SL917 includes an ultra-low power Wi-Fi 6 plus Bluetooth Low Energy (LE) 5.4 wireless CPU subsystem, baseband digital signal processing, analog front end, 2.4 GHz RF transceiver and integrated power amplifier, embedded SRAM, FLASH and power management subsystem all in a single 16 x 21.1 x 2.3 mm PCB module package thus providing a fully integrated solution that is ready for a wide range of embedded wireless IoT applications. The SL917 module is a complete solution offered with robust and fully-upgradeable software stacks, global regulatory certifications, advanced development and debugging tools, and documentation that simplifies and minimizes the development cycle of your end-product, helping to accelerate its time-to-market. The modules come with modular radio type approvals for various countries, including USA (FCC), Canada (IC/ISED) and Japan (MIC), and are in compliance with the relevant EN standards (including EN 300 328 v2.2.2) for the conformity with the directives and regulations in EU and UK.

SL917 applications include:

- Smart Home

- Security Cameras

- HVAC

- Smart Sensors

- Smart Appliances

- Health and Fitness

- Pet Tracker

- Smart Cities

- Smart Meters

- Industrial Wearable

- Smart Buildings

- Asset Tracking

- Smart hospitals

#### KEY FEATURES

- Wi-Fi 6 Single Band 2.4 GHz 20MHz 1x1 stream IEEE 802.11 b/g/n/ax

- Bluetooth LE 5.4

- Wi-Fi 6 Benefits: TWT for improved efficiency and longer battery life, MU-MIMO/OFDMA for Higher Throughput, network capacity and low latency

- Best in Class Device and Wireless Security

- WLAN Tx power up to +17.5 dBm with integrated PA

- Bluetooth LE Tx power up to +17 dBm with integrated PA

- WLAN Rx sensitivity as low as -95 dBm

- + Wi-Fi Standby Associated mode current: 78  $\mu A$  @ 1-second beacon listen interval

- In-package Flash up to 4MB,

- Embedded Wi-Fi, Bluetooth LE and networking stacks supporting wireless coexistence

- Operating temperature: -40 °C to +85 °C

- Operating supply range: 3.0 V 3.63 V

- Supply voltage for GPIOs: 1.71 V to 3.63 V

### 1. Feature List

- Memory

- Embedded Static Random Access Memory (SRAM) up to 672 KB total for multi-threaded processor

- Flash up to 4 MB (embedded)

- Security

- Secure Boot

- Secure firmware upgrade through boot-loader, Secure OTA.

- · Secure Key storage and HW device identity with PUF

- Secure Zone

- Secure XIP (Execution in place) from flash

- Secure Attestation

- Hardware Accelerators: Advanced Encryption Standard (AES) 128/256/192, Secure Hash Algorithm (SHA) 256/384/512, Hash Message Authentication Code (HMAC), Random Number Generator (RNG), Cyclic Redundancy Check (CRC), SHA3, AES-Galois Counter Mode (GCM)/ Cipher based Message Authentication Code (CMAC), ChaCha-poly, True Random Number Generator (TRNG)

- Software Accelerators: RSA, ECC

- · Programmable Secure Hardware Write protect for Flash sectors

- Anti Rollback

- Debug Lock

- Wi-Fi<sup>1</sup>

- · Compliant to single-spatial stream IEEE 802.11 b/g/n/ax with single band (2.4 GHz) support

- Support for 20 MHz channel bandwidth for 802.11n and 802.11ax

- Operating Modes: Wi-Fi 4 STA, Wi-Fi 6 (802.11ax) STA, Wi-Fi 4 AP, Enterprise STA, Wi-Fi 6 STA + Wi-Fi 4 AP, Wi-Fi + BLE

- Support for 802.11ax 20 MHz non-AP STA mandatory features (such as OFDMA, MU-MIMO) and optional features of individual Target wake-up time (iTWT), Broadcast TWT (bTWT)<sup>3</sup>, Intra PPDU power save<sup>3</sup>, SU extended range (ER), DCM (Dual Carrier Modulation). DL MU-MIMO, DL/UL OFDMA, MBSSID, BFRP, Spatial Re-use, BSS Coloring, and NDP feedback upto 4 antennas

- Transmit power up to +17.5 dBm with integrated PA

- · Receive sensitivity as low as -95 dBm

- Data Rates: 802.11b: 1, 2, 5.5, 11; 802.11g: 6, 9, 12, 18, 24, 36, 48, 54Mbps; 802.11n: MCS0 to MCS7; 802.11ax: MCS0 to MCS7

- Operating Frequency Range [MHz]: 2412-2462 (North America, default), 2412-2472 (Europe, and other countries where applicable), 2412-2484 (Japan)

- PTA Coexistence with Zigbee/Thread/Bluetooth

- Intelligent Power Management

- · Power optimizations leveraging multiple power domains and partitioned sub systems

- · Many system-, component-, and circuit-level innovations and optimizations

- Different Power Modes

- Deep sleep mode with only timer active with and without RAM retention

### Bluetooth

- Transmit power up to +17 dBm with integrated PA

- Receive sensitivity LE: -93 dBm, LR 125 Kbps: -104.5 dBm

- Operating Frequency Range 2.402 GHz 2.480 GHz

- Supports Bluetooth<sup>®</sup> Low Energy (LE): High Speed (1 Mbps and 2 Mbps) and Long Range (LE Coded PHYs, 125 Kbps and 500 Kbps; these are referred to as "LR" throughout this data sheet)

- · Advertising extensions

- · Data length extensions

- LL privacy

- LE dual role

- BLE acceptlist

- 2 Simultaneous BLE Connections (2 Peripheral, 2 Central, or 1 Central & 1 Peripheral)<sup>3</sup>

- RF Features

- · Integrated baseband processor with calibration memory

- Integrated RF transceiver, high-power amplifier, balun and T/R switch

- Embedded Wi-Fi Stack<sup>1</sup>

- · Support for Embedded Wi-Fi STA mode, Wi-Fi Access point mode and Concurrent (AP+STA) mode

- Supports advanced Wi-Fi Security features: WPA Personal, WPA2 Personal, WPA3 Personal, WPA/WPA2/WPA3

Enterprise in STA mode

- Networking: Integrated IPv4/IPv6 stack, TCP, UDP, ICMP, ICMPv6, ARP, DHCP Client/Server, DHCPv6 Client, DNS Client, SSL3.0/TLS1.3 Client, SNTP, SNI

- Applications: HTTP/s Client, HTTP/s Server<sup>3</sup>, MQTT/s Client, AWS Client, Azure Client<sup>3</sup>

- Sockets: BSD Sockets, IoT Sockets

- Over-the-Air (OTA) Wireless firmware update

- Provisioning using Wi-Fi AP<sup>3</sup> or BLE

- Embedded Bluetooth Stack

- Support GAP profile

- Support GATT profile

- Support SMP

- Support LE L2CAP

### Wireless Sub-System Power Consumption

- Wi-Fi 4 Standby Associated mode current: 78 µA @ 1-second beacon listen interval

- Wi-Fi 1 Mbps Listen current: 14 mA

- Wi-Fi LP mode Rx current: 21 mA

- Deep sleep current 5  $\mu$ A, Standby current (352K RAM retention) 12.5  $\mu$ A

- Operating Conditions

- Operating supply range : 3.0 V to 3.63 V

- Supply voltage for GPIOs: 1.71 V to 3.63 V

- Operating temperature: -40 °C to +85 °C

- Software and Regulatory Certifications

- Wi-Fi Alliance: Wi-Fi 4<sup>3</sup>, Wi-Fi 6<sup>3</sup>

- Bluetooth SIG Qualification<sup>3</sup>

- Regulatory certifications: [FCC (USA), IC/ISED (Canada), CE (EU), UKCA (UK), MIC (Japan), KC (South Korea), NCC (Taiwan), SRRC (China), ACMA (Australia), RSM (New Zealand)]<sup>3</sup>

### Note:

- 1. For a detailed list of software features and available profiles, refer to the Software Reference Manuals or contact Ezurio for availability.

- 2. All power and performance numbers are under ideal conditions.

- 3. For information about Software roadmap features and additional certification information, contact Ezurio for availability and timeline. Currently, we have certifications for FCC (USA), IC/ISED (Canada), CE (EU), UKCA (UK), MIC (Japan), ACMA (Australia), RSM (New Zealand), but not yet for KC (South Korea), NCC (Taiwan), SRRC (China). These last three are pending.

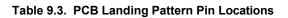

### 2. Ordering Information

| Part #     | Description                                                           |

|------------|-----------------------------------------------------------------------|

| 453-00219R | Module, Veda SL917, 4MB Flash, NCP, Trace Pad, Tape and Reel          |

| 453-00219C | Module, Veda SL917, 4MB Flash, NCP, Trace Pad, Cut Tape               |

| 453-00221R | Module, Veda SL917, 4MB Flash, NCP, Integrated Antenna, Tape and Reel |

| 453-00221C | Module, Veda SL917, 4MB Flash, NCP, Integrated Antenna, Cut Tape      |

### Veda Click Boards (from MIKROE.com)

| Part #                                                 | Description                                                          | Link              |

|--------------------------------------------------------|----------------------------------------------------------------------|-------------------|

| Veda SL917 Click (Integrated Antenna)                  | Click Board - Veda SL917 NCP Module – Integrated Antenna             | See at MIKROE.com |

| Veda SL917 Click (RF Trace Pad or<br>External Antenna) | Click Board - Veda SL917 NCP Module - RF Trace Pad + FlexPIFA (MHF4) | See at MIKROE.com |

### 3. Applications

### Smart Home

Smart Locks, Motion/Entrance Sensors, Water Leak sensors, Smart plugs/switches, Light Emitting Diode (LED) lights, Door-bell cameras, Washers/Dryers, Refrigerators, Thermostats, Consumer Security cameras, Voice Assistants, etc.

### **Other Consumer Applications**

Toys, Anti-theft tags, Smart dispensers, Weighing scales, Fitness Monitors, Smart Glasses, Blood pressure monitors, Blood sugar monitors, Portable cameras, etc.

### Other Applications (Medical, Industrial, Retail, Agricultural, Smart City, etc.)

Healthcare Tags, Industrial Wearables, Infusion pumps, Sensors/actuators in Manufacturing, Electronic Shelf labels, Agricultural sensors, Product tracking tags, Smart Meters, Parking sensors, Street LED lighting, Automotive After-market, Security Cameras, Gate- ways, etc.

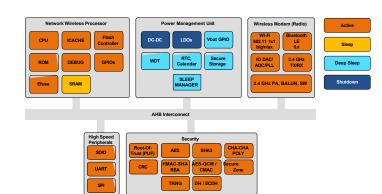

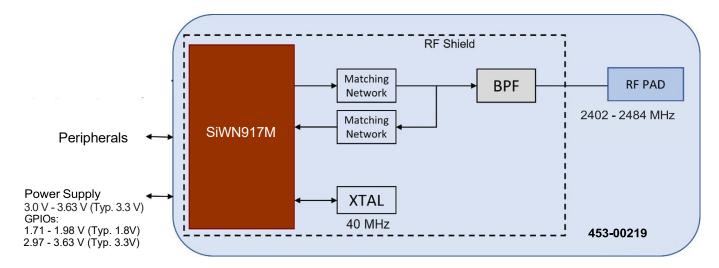

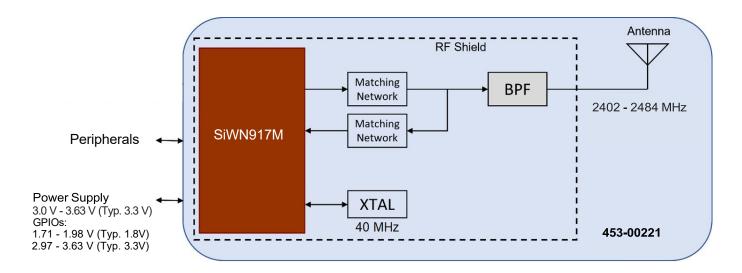

### 4. Block Diagrams

Figure 4.1. 453-00219 (Without Antenna) Module Block Diagram

Figure 4.2. 453-00221 (With Antenna) Module Block Diagram

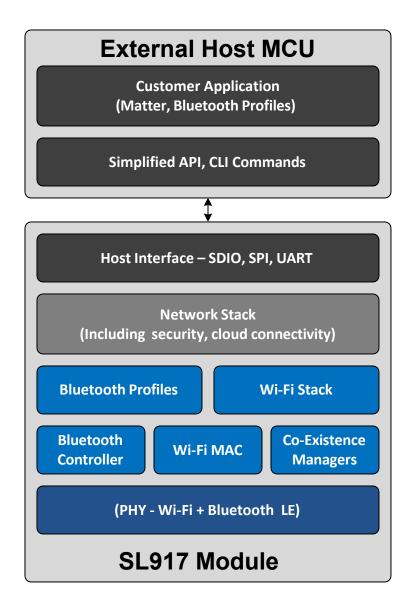

Note: Customer can connect multiple hosts, but only one host interface can be active after power-on.

### 5. System Overview

### 5.1 Introduction

An SL917 module running the NCP mode of operation includes a Network Wireless Processor (NWP) 4-Threaded processor running up to 160 MHz. All the networking and wireless stacks run on independent threads of the NWP. In addition, the NWP subsystem also acts as the secure processing domain and takes care of secure boot, secure firmware update and provides access to security accelerators and secure peripherals through pre-defined APIs. The NWP based "Networking, Security and Wireless subsystem" have power, clocks/ PLLs, bus-matrices, and memory.

### 5.2 WLAN

- Compliant to single-spatial stream IEEE 802.11 b/g/n/ax with single band (2.4 GHz) support

- Support for 20 MHz channel bandwidth for 802.11n and 802.11ax.

- Operating Modes: Wi-Fi 4 STA, Wi-Fi 6 (802.11ax) STA, Wi-Fi 4 AP, Enterprise STA, Wi-Fi 6 STA + Wi-Fi 4 AP, Wi-Fi + BLE

- Wi-Fi 6 Features: Individual Target wake-up time (iTWT), Broadcast TWT (bTWT),SU extended range (ER), DCM (Dual Carrier Modulation), DL MU-MIMO, DL/UL OFDMA, MBSSID, BFRP, Spatial Re-use, BSS Coloring, and NDP feedback up to 4 antennas

- Integrated PA

- Data Rates—802.11b: up to 11 Mbps; 802.11g: up to 54 Mbps; 802.11n: MCS0 to MCS7; 802.11ax: MCS0 to MCS7

- Operating Frequency Range [MHz]: 2412-2462 (North America, default), 2412-2472 (Europe, and other countries where applicable), 2412-2484 (Japan)

### 5.2.1 MAC

- · Conforms to IEEE 802.11b/g/n/ax standards for MAC

- · Hardware accelerators for AES

- WPA, WPA2, WPA3 and WMM support

- · AMPDU aggregation for high performance

- · Firmware downloaded from host based on application

- · Hardware accelerators for DH (for WPS) and ECDH

### 5.2.2 Baseband Processing

- Supports 11b: DSSS for 1, 2 Mbps and CCK for 5.5, 11 Mbps

- · Supports all OFDM data rates:

- 802.11g: 6, 9, 12, 18, 24, 36, 48, 54 Mbps

- 802.11ax, 802.11n: MCS 0 to MCS 7

- High-performance multipath handling in OFDM, DSSS, and CCK modes

### 5.3 Bluetooth

### **Key Features**

- · Transmit power up to +17 dBm with integrated PA

- Receive sensitivity LE: -93 dBm, LR 125 Kbps: -104.5 dBm

- Operating Frequency Range 2.402 GHz 2.480 GHz

- Supports Bluetooth® Low Energy (LE): High Speed (1 Mbps and 2 Mbps) and Long Range (LE Coded PHYs, 125 Kbps and 500 Kbps)

- Advertising extensions

- Data length extensions

- LL privacy

- LE dual role

- BLE acceptlist

- Two simultaneous BLE connections (2 peripheral or 2 central, or 1 central and 1 peripheral)

### 5.3.1 MAC

### Link Manager

- Creation, modification & release of physical links

- · Connection establishment between Link managers of two Bluetooth devices

- Link supervision is implemented in Link Manager

- · Link power control is done depending on the inputs from Link Controller

- · Enabling & disabling of encryption & decryption on logical links

- · AES hardware acceleration

### Link Controller

- · Encodes and decodes header of BLE packets

- · Manages flow control, acknowledgment, re-transmission requests, etc.

- · Stores the last packet status for all physical transports

- · Indicates the success status of packet transmission to upper layers

- · Indicates the link quality to the LMP layer

### **Device Manager**

- Executes HCI Commands

- · Controls Scan & Connection processes

- · Controls all BLE Device operations except data transport operations

- · BLE Controller state transition management

- · Anchor point synchronization & management

- Scheduler

### 5.3.2 Baseband Processing

• Supports BLE 1Mbps, 2Mbps and long range 125kbps, 500kbps

### 5.4 RF Transceiver

- The SL917 features two highly configurable RF transceivers supporting WLAN 11b/g/n/ax and Bluetooth LE wireless protocols. Both RF transceivers together operating in multiple modes covering High Performance (HP) and Low Power (LP) operations. List of operating modes are given in next section.

- It contains two fully integrated fractional-N frequency synthesizers having reference from internal oscillator with 40 MHz crystal. One of the synthesizer is a low power architecture which also caters single-bit data modulation feature for Bluetooth LE protocols.

### 5.4.1 Receiver and Transmitter Operating Modes

The available radio operating modes are as follows:

- WLAN HP TX WLAN High-Performance Transmitter

- WLAN HP RX WLAN High-Performance Receiver

- WLAN LP RX WLAN Low-Power Receiver

- BLE HP TX Bluetooth LE High-Performance Transmitter

- BLE HP RX Bluetooth LE High-Performance Receiver

- BLE LP TX Bluetooth LE Low-Power Transmitter

- BLE LP RX Bluetooth LE Low-Power Receiver

Note: All the TX / RX modes are automatically controlled by radio firmware and not individually selectable.

### 5.5 Security Features

- Secure Boot

- Secure OTA Firmware update

- TRNG : Generates high-entropy random numbers based on RF noise, increasing the effort/time needed to expose secret keys

- Secure Zone

- · Secure Key storage : HW device identity and key storage with PUF

- Debug Lock

- Anti Rollback : Firmware downgrade to a lower version is prohibited through OTP to prevent the use of older, potentially vulnerable FW version

- · Encrypted XIP from flash with XTS/CTR mode

- Secure Attestation : Allows a device to authenticate its identity using a cryptographically signed token and exchange of secret keys

- Hardware Accelerators: AES128/256/192, SHA256/384/512, HMAC, RNG, CRC, SHA3, AES-GCM/ CMAC, ChaCha-poly

- Software Implementation: RSA and ECC

### 5.6 Embedded Wi-Fi Software

- The wireless software package supports Embedded Wi-Fi (802.11 b/g/n/ax) Client mode, Wi-Fi Access point mode (up to 4 clients), and Enterprise Security in client mode.

- The software package includes complete firmware and application profiles.

- It has a wireless coexistence manager to arbitrate between protocols.

### 5.6.1 Security

Wireless software supports multiple levels of security capabilities available for the development of IoT devices.

- Accelerators: AES128/256

- WPA/WPA2/WPA3-Personal, WPA/WPA2/WPA3 Enterprise for Client

### 5.7 Power Architecture

The Power Control Hardware implements the control sequences for transitioning between different power states (Active/Standby/Sleep/ Shutdown).

### 5.7.1 Highlights

- Two integrated buck switching regulators (High performance and ULP) to enable efficient Voltage Scaling across wide operating mode currents ranging from <1 μA to 250 mA</li>

- Multiple voltage domains with Independent voltage scaling of each domain.

- Fine grained power-gating including peripherals, buses and pads, thereby reducing power consumption when the peripheral/buses/ pads are inactive.

- Flexible switching between different Active states with controls from Software.

- Hardware based wakeup from Standby/Sleep/Shutdown states.

- All the peripherals are clock gated by default thereby reducing the power consumption in inactive state.

- · Low wakeup times as configurable by Software.

### 5.7.2 Power Management

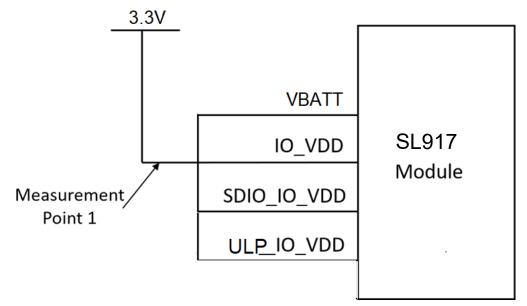

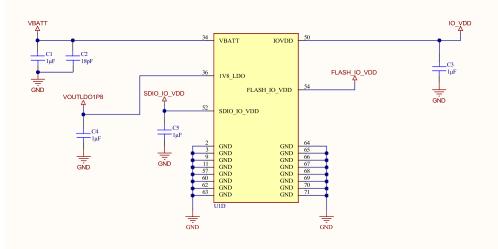

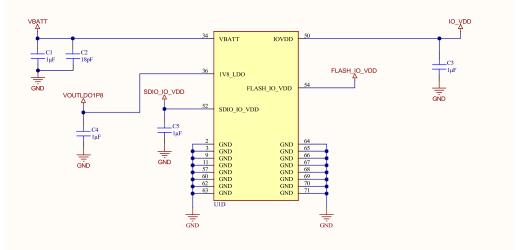

The SL917 NCP modules have an internal power management subsystem, including DC-DC converters and linear regulators. This subsystem generates all the voltages required by the module to operate from a wide variety of input sources.

- Input voltage (3.3 V) on pin VBATT

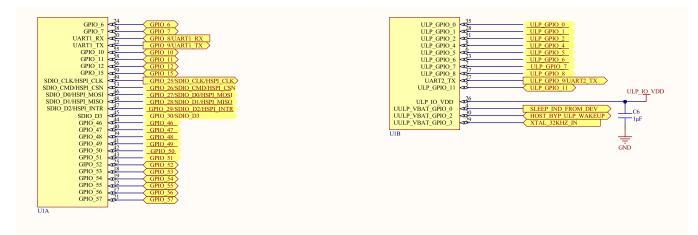

- Input voltage (1.8 V or 3.3 V) on pin IO\_VDD, SDIO\_IO\_VDD and ULP\_IO\_VDD

- Input voltage (1.8 V) on pin FLASH\_IO\_VDD

- Nominal Output 1.8 V and 48 mA maximum load on pin 1V8\_LDO

### 5.8 Memory Architecture

There are on chip Read Only Memory(ROM), Random Access Memory(RAM) and in-package flash connectivity. Sizes of ROM/RAM/ flash will vary depending on the chip configuration.

The NWP processor has the following memory:

- · Embedded SRAM up to 672 KB total

- · 448 KB of ROM which holds the Secure primary bootloader, Network Stack, Wireless stacks and security functions

- 16 KB of Instruction cache (I cache)

- Flash up to 4 MB (in-package)

- eFuse of 1024 bytes (used to store primary boot configuration, security and calibration parameters)

### 5.9 Low Power Modes

It supports Ultra-low power consumption with multiple power modes to reduce system energy consumption.

- Voltage and Frequency Scaling

- Deep sleep (ULP) mode with only the sleep timer active with and without RAM retention

- Wi-Fi standby associated mode with automatic periodic wake-up

- Automatic clock gating of the unused blocks or transit the system from Normal to ULP mode.

### 5.9.1 ULP Mode

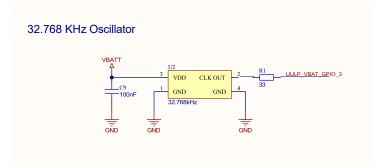

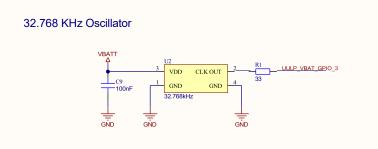

In Ultra Low Power mode, the deep sleep manager has control over the processors and subsystems and controls their active and sleep states. During deep sleep, the always-on logic domain operates on a lowered supply and a 32 kHz low-frequency clock to reduce power consumption. The ULP mode supports the following wake-up options:

- Timeout wakeup Exit sleep state after programmed timeout value.

- GPIO Based Wakeup: Exit sleep state when GPIO goes High/Low based on programmed polarity.

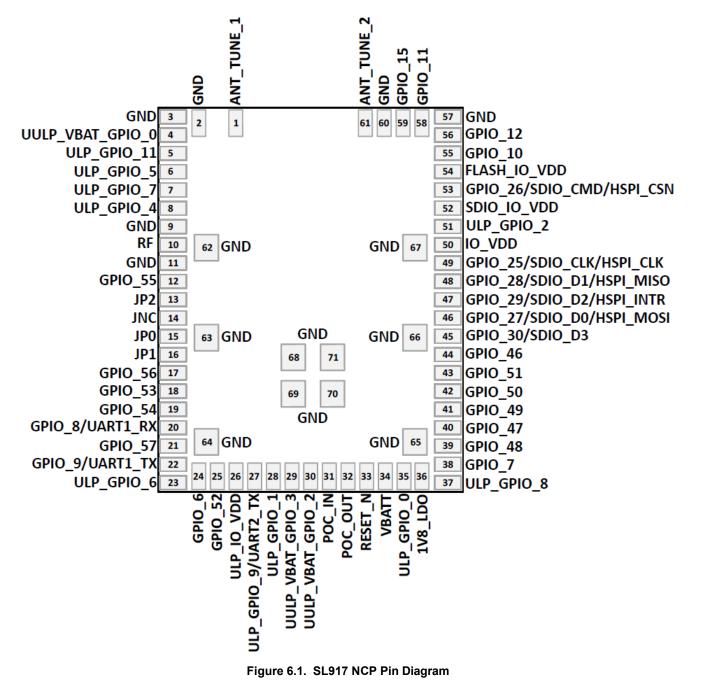

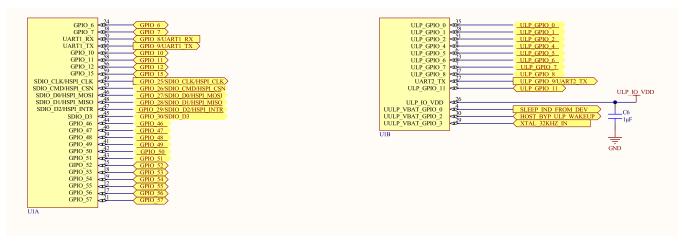

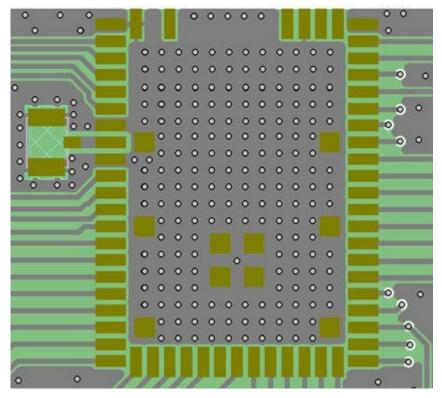

### 6. Pinout and Pin Description

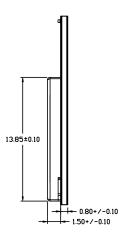

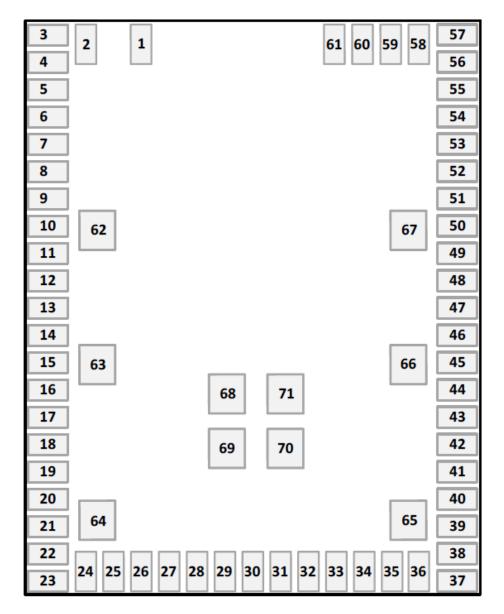

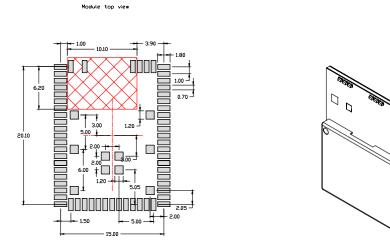

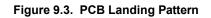

### 6.1 Pin Diagram

### 6.2 Pin Description

| Pin Name         | QFN I/O Supply Domain | Direction | Initial State (Power up,<br>Active Reset) | Description                          |

|------------------|-----------------------|-----------|-------------------------------------------|--------------------------------------|

| RF_BLETX         | RF_AVDD               | Output    | NA                                        | BLE 8 dBm RF Output                  |

| ULP_GPIO_10      | ULP_IO_VDD            | Inout     | HighZ                                     | Default: HighZ<br>Sleep: HighZ       |

| XTAL_32KHZ_P     | NA                    | Inout     | NA                                        | Analog Pin. 32KHZ XTAL<br>Connection |

| XTAL_32KHZ_N     | NA                    | Inout     | NA                                        | Analog Pin. 32KHZ XTAL<br>Connection |

| UULP_VBAT_GPIO_1 | VBATT                 | Inout     | HighZ                                     | Default: High<br>Sleep: High         |

### Table 6.1. List of Pins in IC (SiWN917M), Not Available in the Modules

### 6.2.1 RF and Control Interfaces

| Table 6.2. | Chip Packages - R | F and Control Interfaces |

|------------|-------------------|--------------------------|

|------------|-------------------|--------------------------|

| Pin Name   | Pin<br>No. | I/O Supply Do-<br>main | Direction | Initial State<br>(Power up<br>Active Reset) | Description                                                                                                                                                                                                                                                                |

|------------|------------|------------------------|-----------|---------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

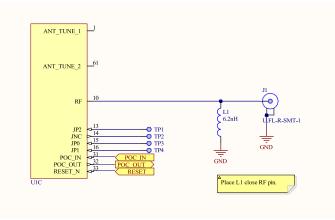

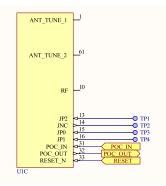

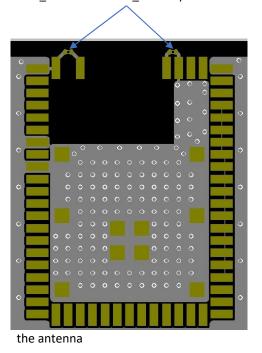

| ANT_TUNE_1 | 1          | N/A                    | Input     | N/A                                         | <b>453-00221:</b> External fine-tuning option for<br>the integral antenna; connect same tun- ing<br>circuit on both ANT_TUNE1 and<br>ANT_TUNE2 pins; leave floating if no fine-<br>tuning is desired on the integral antenna;<br><b>453-00219:</b> leave this pin floating |

| RF         | 10         | VBATT                  | Inout     | N/A                                         | Connect to antenna with a 50- $\Omega$ impedance as per the reference schematics                                                                                                                                                                                           |

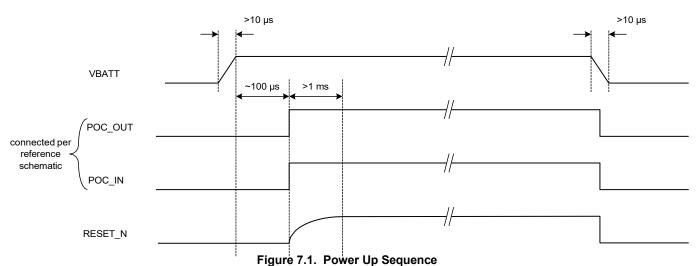

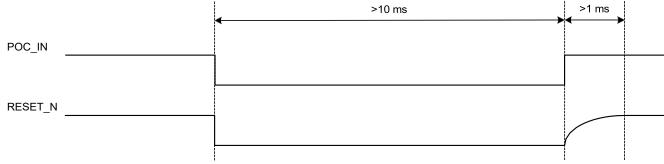

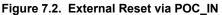

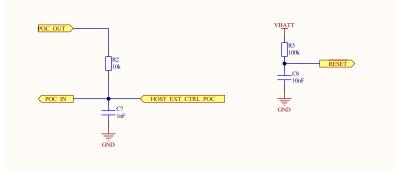

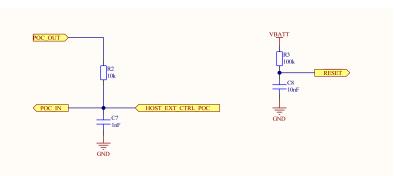

| POC_IN     | 31         | VBATT                  | Input     | NA                                          | This is an input to the chip which resets all<br>analog and digital blocks in the device. It<br>should be made high only after supplies<br>are valid.                                                                                                                      |

| POC_OUT    | 32         | VBATT                  | Output    | NA                                          | This is internally generated. Initially, it is<br>low. But it becomes high when the supply<br>(VBATT) is valid.                                                                                                                                                            |

| RESET_N    | 33         | VBATT                  | Inout     | NA                                          | Active-low reset asynchronous reset signal,<br>which resets only digital blocks. RESET_N<br>will be pulled low if POC_IN is low.                                                                                                                                           |

| ANT_TUNE_2 | 61         | N/A                    | Input     | N/A                                         | <b>453-00221:</b> External fine-tuning option for the integral antenna; connect same tun- ing circuit on both ANT_TUNE1 and ANT_TUNE2 pins; leave floating if no fine-tuning is desired on the integral antenna; <b>453-00219:</b> leave this pin floating                 |

### 6.2.2 Power and Ground Pins

| Pin Name     | Pin No.                             | Туре   | Direction | Description                                                                                                    |

|--------------|-------------------------------------|--------|-----------|----------------------------------------------------------------------------------------------------------------|

| ULP_IO_VDD   | 26                                  | Power  | Input     | I/O supply for ULP I/Os.                                                                                       |

| VBATT        | 34                                  | Power  | Input     | Power supply for the module.                                                                                   |

| 1V8_LDO      | 36                                  | Power  | Output    | Output of 1.8V LDO which is used for Flash supply.                                                             |

| IO_VDD       | 50                                  | Power  | Input     | I/O Supply for GPIOs. Refer to GPIOs section for details on which GPIOs have this as the I/O supply.           |

| SDIO_IO_VDD  | 52                                  | Power  | Input     | I/O Supply for SDIO I/Os. Refer to GPIOs section<br>for details on which GPIOs have this as the I/O<br>supply. |

| FLASH_IO_VDD | 54                                  | Power  | Input     | I/O Supply for module embedded flash. Connect to 1V8_LDO as per Reference Schematics.                          |

| GND          | 2, 3, 9,<br>11, 57,<br>60,<br>62-71 | Ground |           | Common ground pins.                                                                                            |

### 6.2.3 Peripheral Interfaces

### Table 6.4. Chip Packages - Perpheral Interfaces

| Pin Name         | Pin<br>No. | I/O Supply Do-<br>main | Direction | Initial State<br>(Power up | Description                                                                                                                                                                                                                                                                            |

|------------------|------------|------------------------|-----------|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                  |            |                        |           | Active Reset)              |                                                                                                                                                                                                                                                                                        |

| UULP_VBAT_GPIO_0 | 4          | VBATT                  | Output    | High                       | Default: High                                                                                                                                                                                                                                                                          |

|                  |            |                        |           |                            | Sleep: High                                                                                                                                                                                                                                                                            |

|                  |            |                        |           |                            | <ul> <li>This pin can be configured by software to be any of the following.</li> <li>SLEEP_IND_FROM_DEV: This signal is used to send an indication to the Host processor. An indication is sent when the chip enters (logic low) and exits (logic high) the ULP Sleep mode.</li> </ul> |

| ULP_GPIO_11      | 5          | ULP_IO_VDD             | Inout     | HighZ                      | Default: HighZ                                                                                                                                                                                                                                                                         |

|                  |            |                        |           |                            | Sleep: HighZ                                                                                                                                                                                                                                                                           |

| ULP_GPIO_5       | 6          | ULP_IO_VDD             | Inout     | HighZ                      | Default: HighZ                                                                                                                                                                                                                                                                         |

|                  |            |                        |           |                            | Sleep: HighZ                                                                                                                                                                                                                                                                           |

| ULP_GPIO_7       | 7          | ULP_IO_VDD             | Inout     | HighZ                      | Default: HighZ                                                                                                                                                                                                                                                                         |

|                  |            |                        |           |                            | Sleep: HighZ                                                                                                                                                                                                                                                                           |

| ULP_GPIO_4       | 8          | ULP_IO_VDD             | Inout     | HighZ                      | Default: HighZ                                                                                                                                                                                                                                                                         |

|                  |            |                        |           |                            | Sleep: HighZ                                                                                                                                                                                                                                                                           |

| GPIO_55          | 12         | IO_VDD                 | Inout     | HighZ                      | Default: HighZ                                                                                                                                                                                                                                                                         |

|                  |            |                        |           |                            | Sleep: HighZ                                                                                                                                                                                                                                                                           |

| JP2              | 13         | IO_VDD                 | Input     | Pullup                     | Default: JP2                                                                                                                                                                                                                                                                           |

|                  |            |                        |           |                            | Sleep: HighZ                                                                                                                                                                                                                                                                           |

|                  |            |                        |           |                            | JP2 - Reserved. Connect to a test point for debugging purposes                                                                                                                                                                                                                         |

| JNC              | 14         | IO_VDD                 | Output    | Pullup                     | Default: JNC                                                                                                                                                                                                                                                                           |

|                  |            |                        |           |                            | Sleep: HighZ                                                                                                                                                                                                                                                                           |

|                  |            |                        |           |                            | JNC - Reserved. Connect to a test point for debugging purposes                                                                                                                                                                                                                         |

| JP0              | 15         | IO_VDD                 | Input     | Pullup                     | Default: JP0                                                                                                                                                                                                                                                                           |

|                  |            |                        |           |                            | Sleep: HighZ                                                                                                                                                                                                                                                                           |

|                  |            |                        |           |                            | JP0 - Reserved. Connect to a test point for debugging purposes                                                                                                                                                                                                                         |

| JP1              | 16         | IO_VDD                 | Input     | Pullup                     | Default: JP1                                                                                                                                                                                                                                                                           |

|                  |            |                        |           |                            | Sleep: HighZ                                                                                                                                                                                                                                                                           |

|                  |            |                        |           |                            | JP1 - Reserved. Connect to a test point for debugging purposes                                                                                                                                                                                                                         |

| Pin Name                | Pin<br>No. | I/O Supply Do-<br>main | Direction | Initial State<br>(Power up<br>Active Reset) |                                                              | Description                                                                             |                 |

|-------------------------|------------|------------------------|-----------|---------------------------------------------|--------------------------------------------------------------|-----------------------------------------------------------------------------------------|-----------------|

| GPIO_56                 | 17         | IO_VDD                 | Inout     | HighZ                                       | Default: High                                                | Z                                                                                       |                 |

|                         |            |                        |           |                                             | Sleep: HighZ                                                 |                                                                                         |                 |

| GPIO_53                 | 18         | IO_VDD                 | Inout     | HighZ                                       | Default: High                                                | Z                                                                                       |                 |

|                         |            |                        |           |                                             | Sleep: HighZ                                                 |                                                                                         |                 |

| GPIO_54                 | 19         | IO_VDD                 | Inout     | HighZ                                       | Default: High                                                | Z                                                                                       |                 |

|                         |            |                        |           |                                             | Sleep: HighZ                                                 |                                                                                         |                 |

| GPIO_8/UART1_RX         | 20         | IO_VDD                 | Inout     | HighZ                                       | Host                                                         | Default                                                                                 | Sleep           |

|                         |            |                        |           | UART                                        | UART1_RX<br>- UART Host<br>interface se-<br>rial input.      | HighZ                                                                                   |                 |

|                         |            |                        |           |                                             | Non UART                                                     | HighZ                                                                                   | HighZ           |

| GPIO_57                 | 21         | IO_VDD                 | Inout     | HighZ                                       | Default: High                                                | Z                                                                                       |                 |

|                         |            |                        |           |                                             | Sleep: HighZ                                                 |                                                                                         |                 |

| GPIO_9/UART1_TX         | 22         | IO_VDD                 | Inout     | HighZ                                       | Host                                                         | Default                                                                                 | Sleep           |

|                         |            |                        |           |                                             | UART                                                         | UART1_TX -<br>UART Host<br>interface se-<br>rial output.                                |                 |

|                         |            |                        |           |                                             | Non UART                                                     | HighZ                                                                                   | HighZ           |

| ULP_GPIO_6              | 23         | ULP_IO_VDD             | Inout     | HighZ                                       | Default: High                                                | Z                                                                                       |                 |

|                         |            |                        |           |                                             | Sleep: HighZ                                                 |                                                                                         |                 |

|                         |            |                        |           |                                             | <ul><li>be any of the</li><li>PTA_PRIC part of 3-w</li></ul> | e configured by<br>following.<br>): "PTA Priority"<br>ire coexistence<br>on) interface. | input signal is |

| GPIO_6                  | 24         | IO_VDD                 | Inout     | HighZ                                       | Default: High                                                | Z                                                                                       |                 |

|                         |            |                        |           |                                             | Sleep: HighZ                                                 |                                                                                         |                 |

| GPIO_52                 | 25         | IO_VDD                 | Inout     | HighZ                                       | Default: High                                                | Z                                                                                       |                 |

|                         |            |                        |           |                                             | Sleep: HighZ                                                 |                                                                                         |                 |

| ULP_GPIO_9/<br>UART2_TX | 27         | ULP_IO_VDD             | Inout     | HighZ                                       | <b>Default:</b> UAR face serial ou                           | T2_TX- Debug<br>tput                                                                    | UART Inter-     |

|                         |            |                        |           |                                             | Sleep: HighZ                                                 |                                                                                         |                 |

### SL917 NCP Module

Datasheet

| Pin Name         | Pin<br>No. | I/O Supply Do-<br>main | Direction | Initial State<br>(Power up<br>Active Reset) | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|------------------|------------|------------------------|-----------|---------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ULP_GPIO_1       | 28         | ULP_IO_VDD             | Inout     | HighZ                                       | <ul> <li>Default: HighZ</li> <li>Sleep: HighZ</li> <li>This pin can be configured by software to be any of the following</li> <li>PTA_REQ: "PTA Request" input signal is part of 3-wire coexistence (Packet Traffic Arbitration) interface.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                     |

| UULP_VBAT_GPIO_3 | 29         | VBATT                  | Inout     | HighZ                                       | <ul> <li>Default: HighZ</li> <li>Sleep: EXT_32KHZ_IN</li> <li>This pin can be configured by software to be any of the following.</li> <li>EXT_32KHZ_IN: This pin can be used to feed external clock from a host processor or from external crystal oscillator.</li> </ul>                                                                                                                                                                                                                                                                                                                                                  |

| UULP_VBAT_GPIO_2 | 30         | VBATT                  | Inout     | HighZ                                       | <ul> <li>Default: HighZ</li> <li>Sleep: ULP_WAKEUP</li> <li>This pin can be configured by software to be any of the following.</li> <li>HOST_BYP_ULP_WAKEUP: This signal has two functionalities – one during the bootloading process and one after the bootloading. During bootloading, this signal is an active-high input to indicate that the bootloader should bypass any inputs from the Host processor and continue to load the default firmware from Flash. After bootloading, this signal is an active-high input to indicate that the module should wakeup from its Ultra Low Power (ULP) sleep mode.</li> </ul> |

| ULP_GPIO_0       | 35         | ULP_IO_VDD             | Inout     | HighZ                                       | Default: HighZ<br>Sleep: HighZ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| ULP_GPIO_8       | 37         | ULP_IO_VDD             | Inout     | HighZ                                       | Default: HighZ<br>Sleep: HighZ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| GPIO_7           | 38         | IO_VDD                 | Inout     | HighZ                                       | Default:HighZ<br>Sleep: HighZ<br>This pin can be configured by software to<br>be any of the following.<br>PTA_GRANT: "PTA Grant" output signal is<br>part of 3-wire coexistence (Packet Traffic<br>Arbitration) interface.                                                                                                                                                                                                                                                                                                                                                                                                 |

| GPIO_48          | 39         | IO_VDD                 | Inout     | HighZ                                       | Default: HighZ<br>Sleep: HighZ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| GPIO_47          | 40         | IO_VDD                 | Inout     | HighZ                                       | Default: HighZ<br>Sleep: HighZ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Pin Name                      | Pin<br>No. | I/O Supply Do-<br>main | Direction | Initial State<br>(Power up<br>Active Reset) |                 | Description                                                                     |       |

|-------------------------------|------------|------------------------|-----------|---------------------------------------------|-----------------|---------------------------------------------------------------------------------|-------|

| GPIO_49                       | 41         | IO_VDD                 | Inout     | HighZ                                       | Default: High   | Z                                                                               |       |

|                               |            |                        |           |                                             | Sleep: HighZ    |                                                                                 |       |

| GPIO_50                       | 42         | IO_VDD                 | Inout     | HighZ                                       | Default: High   | Z                                                                               |       |

|                               |            |                        |           |                                             | Sleep: HighZ    |                                                                                 |       |

| GPIO_51                       | 43         | IO_VDD                 | Inout     | HighZ                                       | Default: High   | Z                                                                               |       |

|                               |            |                        |           |                                             | Sleep: HighZ    |                                                                                 |       |

| GPIO_46                       | 44         | IO_VDD                 | Inout     | HighZ                                       | Default: High   | Ζ                                                                               |       |

| GPIO_30/SDIO_D3               | 45         | SDIO_IO_VDD            | Inout     | Pullup                                      | Sleep: HighZ    |                                                                                 |       |

| GPIO_30/SDIO_D3               | 40         |                        | mout      | Pullup                                      | Host            | Default                                                                         | Sleep |

|                               |            |                        |           |                                             | SDIO            | SDIO_D3 -<br>SDIO inter-<br>face Data3<br>signal                                | HighZ |

|                               |            |                        |           |                                             | Non<br>SDIO,SPI | HighZ                                                                           | HighZ |

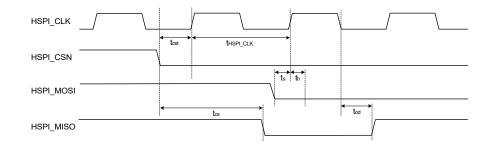

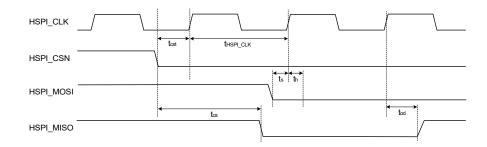

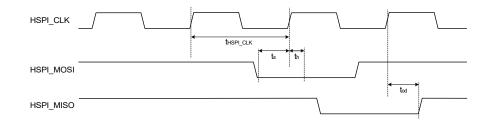

| GPIO_27/SDIO_D0/<br>HSPI_MOSI | 46         | SDIO_IO_VDD            | Inout     | HighZ                                       | Host            | Default                                                                         | Sleep |

|                               |            |                        |           |                                             | SDIO            | SDIO_D0 -<br>SDIO inter-<br>face Data0<br>signal                                | HighZ |

|                               |            |                        |           |                                             | SPI             | HSPI_MOSI<br>- SPI Slave<br>interface<br>Master-Out-<br>Slave-In sig-<br>nal    | HighZ |

|                               |            |                        |           |                                             | Non<br>SDIO,SPI | HighZ                                                                           | HighZ |

| GPIO_29/SDIO_D2/              | 47         | SDIO_IO_VDD            | Inout     | HighZ                                       | Host            | Default                                                                         | Sleep |

| HSPI_INTR                     |            |                        |           |                                             | SDIO            | SDIO_D2 -<br>SDIO inter-<br>face Data2<br>signal                                | HighZ |

|                               |            |                        |           |                                             | SPI             | HSPI_INTR<br>- SPI Slave<br>interface In-<br>terrupt Sig-<br>nal to the<br>Host | HighZ |

|                               |            |                        |           |                                             | Non<br>SDIO,SPI | HighZ                                                                           | HighZ |

### SL917 NCP Module

Datasheet

| Pin Name                      | Pin<br>No. | I/O Supply Do-<br>main | Direction | Initial State<br>(Power up<br>Active Reset) |                                         | Description                                                                      |       |

|-------------------------------|------------|------------------------|-----------|---------------------------------------------|-----------------------------------------|----------------------------------------------------------------------------------|-------|

| GPIO_28/SDIO_D1/<br>HSPI_MISO | 48         | SDIO_IO_VDD            | Inout     | HighZ                                       | Host                                    | Default                                                                          | Sleep |

|                               |            |                        |           |                                             | SDIO                                    | SDIO_D1 -<br>SDIO inter-<br>face Data1<br>signal                                 | HighZ |

|                               |            |                        |           |                                             | SPI                                     | HSPI_MISO<br>- SPI Slave<br>interface<br>Master-In-<br>Slave-Out<br>signal       | HighZ |

|                               |            |                        |           |                                             | Non<br>SDIO,SPI                         | HighZ                                                                            | HighZ |

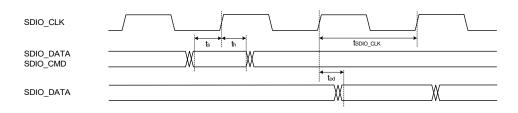

| GPIO_25/SDIO_CLK/<br>HSPI_CLK | 49         | SDIO_IO_VDD            | Inout     | HighZ                                       | Host                                    | Default                                                                          | Sleep |

| Hori_OEK                      |            |                        |           | SDIO                                        | SDIO_CLK -<br>SDIO inter-<br>face clock | HighZ                                                                            |       |

|                               |            |                        |           |                                             | SPI                                     | HSPI_CLK -<br>SPI Slave in-<br>terface clock                                     | HighZ |

|                               |            |                        |           |                                             | Non<br>SDIO,SPI                         | HighZ                                                                            | HighZ |

| ULP_GPIO_2                    | 51         | ULP_IO_VDD             | Input     | HighZ                                       | Default: High                           | ıΖ                                                                               |       |

|                               |            |                        |           |                                             | Sleep: HighZ                            |                                                                                  |       |

| GPIO_26/SDIO_CMD/<br>SPI_CSN  | 53         | SDIO_IO_VDD            | Inout     | HighZ                                       | Host                                    | Default                                                                          | Sleep |

|                               |            |                        |           |                                             | SDIO                                    | SDIO_CMD<br>- SDIO inter-<br>face CMD<br>signal                                  | HighZ |

|                               |            |                        |           |                                             | SPI                                     | HSPI_CSN -<br>Active-low<br>Chip Select<br>signal of SPI<br>Slave inter-<br>face | HighZ |

|                               |            |                        |           |                                             | Non<br>SDIO,SPI                         | HighZ                                                                            | HighZ |

### SL917 NCP Module

Datasheet

| Pin Name | Pin<br>No. | I/O Supply Do-<br>main | Direction | Initial State<br>(Power up<br>Active Reset) | Description                                                                                                                                                                                                                                                                                                                                                                                                                   |

|----------|------------|------------------------|-----------|---------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GPIO_10  | 55         | IO_VDD                 | Inout     | HighZ                                       | Default: HighZ                                                                                                                                                                                                                                                                                                                                                                                                                |

|          |            |                        |           |                                             | Sleep: HighZ                                                                                                                                                                                                                                                                                                                                                                                                                  |

|          |            |                        |           |                                             | <ul> <li>This pin can be configured by software to be any of the following.</li> <li>HOST_WAKEUP_IND: This is used as indication from host to dev that host is ready to take the packet and device can transfer the packet to host. This is supported only in UART host mode.</li> <li>It is part of Wake-on-Wireless functionality. Please check with Silabs for availability of this functionality</li> </ul>               |

| GPIO_12  | 56         | IO_VDD                 | Inout     | HighZ                                       | Default: HighZ                                                                                                                                                                                                                                                                                                                                                                                                                |

|          |            |                        |           |                                             | Sleep: HighZ                                                                                                                                                                                                                                                                                                                                                                                                                  |

|          |            |                        |           |                                             | <ul> <li>This pin can be configured by software to be any of the following.</li> <li>UART1_RTS - UART interface Request to Send, if UART Host Interface flow control is enabled.</li> </ul>                                                                                                                                                                                                                                   |

| GPIO_11  | 58         | IO_VDD                 | Inout     | HighZ                                       | Default: HighZ                                                                                                                                                                                                                                                                                                                                                                                                                |

|          |            |                        |           |                                             | Sleep: HighZ                                                                                                                                                                                                                                                                                                                                                                                                                  |

|          |            |                        |           |                                             | <ul> <li>This pin can be configured by software to be any of the following.</li> <li>WAKEUP_FROM_DEV: Used as a wakeup indication to host from device.</li> <li>It is part of Wake-on-Wireless functionality. It is recommended that one use an external weak pull-down resistor on this pin and software has to be configured suitably.</li> <li>Please check with Silabs for availability of this functionality.</li> </ul> |

| GPIO_15  | 59         | IO_VDD                 | Inout     | HighZ                                       | Default: HighZ                                                                                                                                                                                                                                                                                                                                                                                                                |

|          |            |                        |           |                                             | <ul> <li>Sleep: HighZ</li> <li>This pin can be configured by software to be any of the following.</li> <li>UART1_CTS - UART interface Clear to Send, if UART Host Interface flow control is enabled.</li> </ul>                                                                                                                                                                                                               |

### 7. Electrical Specifications

### 7.1 Absolute Maximum Ratings

Stresses beyond those listed below may cause permanent damage to the device. This is a stress rating only and functional operation of the devices at those or any other conditions beyond those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability. For more information on the available quality and reliability data, see the Quality and Reliability Monitor Report at https://www.silabs.com/about-us/quality.

Note: All the specifications are preliminary and subject to change.

| Symbol              | Test Conditon                                                                                                                             | Min                                                                                                                                       | Тур                                                                                                                                                                                                                                                                                                                    | Max                                                                                                                                                                                                                                                                                                      | Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| T <sub>store</sub>  |                                                                                                                                           | -40                                                                                                                                       | _                                                                                                                                                                                                                                                                                                                      | 125                                                                                                                                                                                                                                                                                                      | °C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| T <sub>j(max)</sub> |                                                                                                                                           |                                                                                                                                           | _                                                                                                                                                                                                                                                                                                                      | 125                                                                                                                                                                                                                                                                                                      | °C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| VBATT               |                                                                                                                                           | -0.5                                                                                                                                      | _                                                                                                                                                                                                                                                                                                                      | 3.63                                                                                                                                                                                                                                                                                                     | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

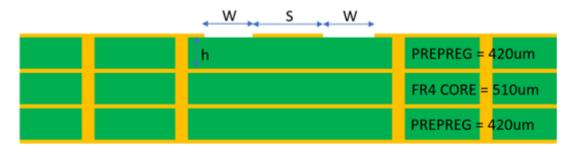

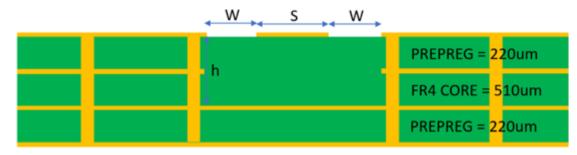

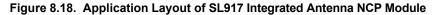

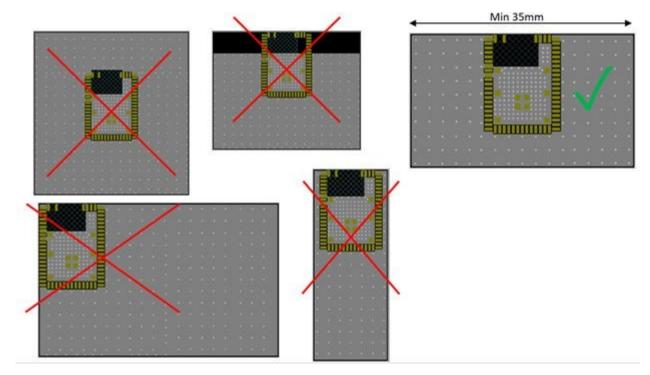

| IO_VDD              |                                                                                                                                           | -0.5                                                                                                                                      | _                                                                                                                                                                                                                                                                                                                      | 3.63                                                                                                                                                                                                                                                                                                     | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |