# 2/4 Outputs Ultra-Low Additive Jitter PCIe 1/2/3/4/5/6 Clock Buffer for Automotive

#### **Features**

- Two (SYA75603A/03B) and Four (SYA75604A/04B) PCIe 1/2/3/4/5/6 Compliant Outputs

- Ultra-Low Additive Jitter 10 fs (PCIe Gen5) and 6 fs (PCIe Gen6)

- · Supports Frequencies of up to 250 MHz

- · Transparent for Spread Spectrum

- Supports 1.8V ±10%, 2.5V ±10% and 3.3V ±10% Power Supplies

- Outputs Low Power HCSL with Embedded  $85\Omega$  (SYA75603A/04A) and  $100\Omega$  (SYA75603B/04B) Termination Resistors

- Individual Glitch Free Output Enable (OExb) Control Pins

- Accepts DC Coupled HCSL Input Signal and AC Coupled PECL, LVDS and CML

- Extended Temperature Range: -40°C to +105°C

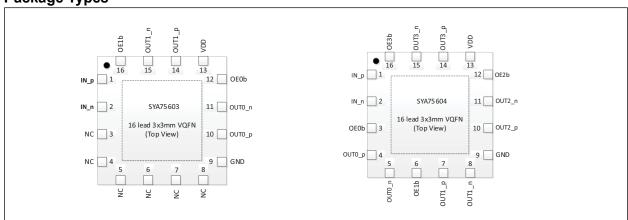

- 3 mm x 3 mm VQFN Package

#### **Applications**

- ADAS

- · PCIe Based SSD drives

- · Infotainment System

#### **General Description**

The SYA75603A, SYA75603B, SYA75604A, and SYA75604B are industry leading PCIe clock buffers with ultra-low additive jitter:

- 6 fs (PCIe 6.0)

- 10 fs (PCle 5.0)

- 20 fs (PCIe 3.0/4.0)

- 52 fs in the 12 kHz to 20 MHz band

They can be used in all PCIe 1/2/3/4/5/6 common clock and SRIS applications.

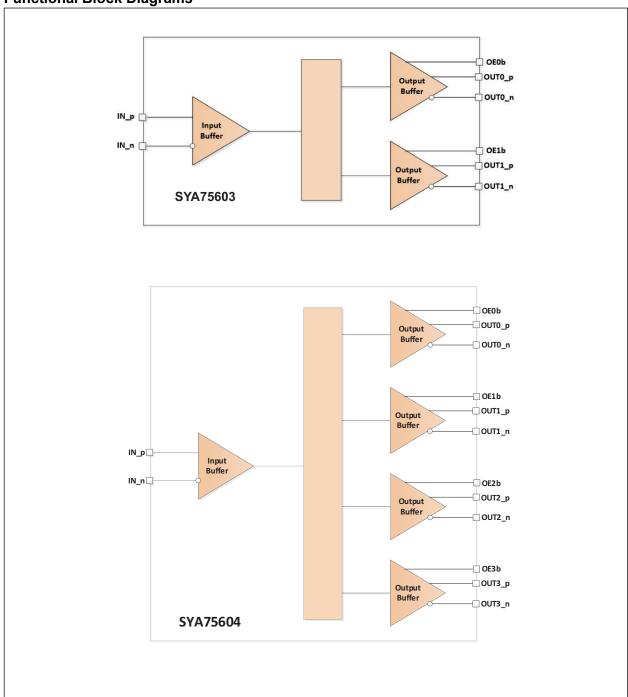

SYA75603A/03B and SYA75604A/04B are two and four output (respectively) PCle clock buffers with glitch free per-output enable/disable control hardware pins. Both devices are packaged in a 3 mm x 3 mm VQFN.

The SYA75603A/03B/604A/04B have embedded low-dropout regulators (LDO) for superior power noise supply rejection. They support 1.8V, 2.5V, and 3.3V supplies with tolerance of  $\pm 10\%$  which exceeds  $\pm 9\%$  required by PCIe Card Electro Mechanical Specification.

All parts are Automotive Grade 2 compliant: –40°C to +105°C

#### **Package Types**

#### **Functional Block Diagrams**

#### 1.0 ELECTRICAL CHARACTERISTICS

#### **Absolute Maximum Ratings †**

| Supply Voltage (V <sub>DD</sub> ) | –0.5V to +4.6V |

|-----------------------------------|----------------|

| Input Voltage (V <sub>IN</sub> )  |                |

| Input ESD Protection (HBM)        | 2 kV           |

#### **Operating Ratings ‡**

| 1.8V Operating Voltage (V <sub>DD</sub> ) | +1.62V to +1.98V |

|-------------------------------------------|------------------|

| 2.5V Operating Voltage (V <sub>DD</sub> ) |                  |

| 3.3V Operating Voltage (V <sub>DD</sub> ) |                  |

- **† Notice:** Permanent device damage may occur if absolute maximum ratings are exceeded. This is a stress rating only and functional operation is not implied at conditions other than those detailed in the operational sections of this data sheet. Exposure to absolute maximum ratings conditions may affect device reliability.

- **‡ Notice:** The data sheet limits are not guaranteed if the device is operated beyond the recommended operating conditions.

#### **ELECTRICAL CHARACTERISTICS**

**Electrical Characteristics:**  $V_{DD} = 3.3V \pm 10\%$ ,  $2.5V \pm 10\%$ ;  $1.8V \pm 10\%$ T<sub>A</sub> = -40°C to +105°C, unless noted.

| Parameter                                                                           | Symbol                     | Min.                 | Тур. | Max.                 | Units      | Conditions                                                                                                                       |  |  |  |

|-------------------------------------------------------------------------------------|----------------------------|----------------------|------|----------------------|------------|----------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Current Consumption                                                                 |                            |                      |      |                      |            |                                                                                                                                  |  |  |  |

| Core Device Current                                                                 | I <sub>DD</sub>            | _                    | 9    | 13                   |            | All outputs disabled                                                                                                             |  |  |  |

| Current dissipation per each LP-HCSL output (100Ω)                                  | I <sub>OUT_HCSL_100Ω</sub> | _                    | 3.5  | 3.9                  | mA         | Note 1                                                                                                                           |  |  |  |

| Current dissipation per each LP-HCSL output (85Ω)                                   | I <sub>OUT_HCSL_85Ω</sub>  | _                    | 4.0  | 4.4                  | mA         | Note 1                                                                                                                           |  |  |  |

| Power Supply Noise Reje                                                             | ction Ratio Cl             | naracteris           | tics |                      |            |                                                                                                                                  |  |  |  |

| Power Supply Noise<br>Rejection Ratio                                               | PSNRR <sub>HSCL</sub>      | _                    | 70   | _                    | dB         | Note 3, 100 mV <sub>PP</sub> , 100 kHz<br>noise injected to V <sub>DD</sub> . Clock<br>Frequency 100 MHz, V <sub>DD</sub> = 3.3V |  |  |  |

| Input Characteristics                                                               |                            |                      |      |                      |            |                                                                                                                                  |  |  |  |

| Input Slew Rate                                                                     | SR <sub>IN</sub>           | 0.6                  | _    | _                    | V/ns       | Note 3                                                                                                                           |  |  |  |

| Differential Input High<br>Voltage                                                  | V <sub>IH</sub>            | 0.15                 | _    | _                    | V          | _                                                                                                                                |  |  |  |

| Differential Input Low Voltage                                                      | V <sub>IL</sub>            | _                    | _    | -0.15                | V          | _                                                                                                                                |  |  |  |

| Input Voltage Swing                                                                 | V <sub>SWING</sub>         | 0.15                 | _    | _                    | $V_{DIFF}$ | _                                                                                                                                |  |  |  |

| Absolute Crossing Point Voltage                                                     | V <sub>CROSS</sub>         | 0.25                 | _    | 0.55                 | V          | Note 3                                                                                                                           |  |  |  |

| Variation of V <sub>CROSS</sub> Over All Edges                                      | V <sub>CROSS_DELTA</sub>   | _                    | _    | 0.14                 | ٧          | Note 3                                                                                                                           |  |  |  |

| Voltage High for Output<br>Enable                                                   | V <sub>IH_OE</sub>         | 0.7* V <sub>DD</sub> | _    | _                    | ٧          | _                                                                                                                                |  |  |  |

| Voltage Low for Output Enable                                                       | V <sub>IL_OE</sub>         | _                    | _    | 0.3* V <sub>DD</sub> | V          | _                                                                                                                                |  |  |  |

| Input Leakage Current                                                               | I <sub>IL_IN</sub>         | <b>-</b> 5           | _    | 5                    | μA         | $V_{IN} = V_{IN(MAX)}, V_{IN} = GND$                                                                                             |  |  |  |

| Input Capacitance                                                                   | C <sub>IN</sub>            | _                    | _    | 5                    | pF         | Note 3                                                                                                                           |  |  |  |

| Input Leakage Current for OExb Inputs (Includes Current due to Pull-Down Resistors) | I <sub>IL_OE</sub>         | <b>-</b> 5           | _    | 50                   | μА         | $V_{IN} = V_{DD}, V_{IN} = GND$                                                                                                  |  |  |  |

#### **ELECTRICAL CHARACTERISTICS (CONTINUED)**

**Electrical Characteristics:**  $V_{DD} = 3.3V \pm 10\%$ ,  $2.5V \pm 10\%$ ;  $1.8V \pm 10\%$   $T_A = -40^{\circ}$ C to  $+105^{\circ}$ C, unless noted.

| Parameter                                                              | Symbol                | Min. | Тур. | Max. | Units | Conditions |

|------------------------------------------------------------------------|-----------------------|------|------|------|-------|------------|

| Single Ended Input Common<br>Mode Voltage (IN_p) (HCSL<br>Common Mode) | V <sub>SIC</sub>      | 0.25 | _    | 0.55 | V     | _          |

| Single Ended Input Voltage<br>Swing for IN_p                           | $V_{SID}$             | 0.3  |      | 1.45 | V     | _          |

| Maximum Input Voltage                                                  | $V_{IN}(MAX)$         | _    | _    | 1.15 | V     | _          |

| Minimum Input Voltage                                                  | V <sub>IN</sub> (MIN) | -0.3 | _    | _    | V     | _          |

| Input Frequency (Differential)                                         | f <sub>IN</sub>       | 0    | _    | 250  | MHz   | Note 2     |

| Input Frequency (Single Ended)                                         | f <sub>IN_SE</sub>    | 0    | _    | 250  | MHz   | Note 2     |

| Input Duty Cycle                                                       | DC                    | 35   | _    | 65   | %     | Note 3     |

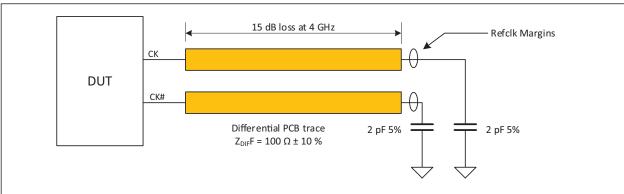

- Note 1: Tested with 100 MHz clock with outputs driving 5" long trace terminated with 2 pF capacitors to ground.

- 2: Output Enable control pins are synchronous with the input clock and it takes four rising edges before outputs get enabled and five rising edges before outputs get disabled. Hence the minimum input frequency is greater than 0 Hz. Once the outputs are enabled the input clock frequency can be reduced to 0 Hz.

- 3: Ensured by design and/or characterization, not tested in production.

#### **OUTPUT ELECTRICAL CHARACTERISTICS**

**Electrical Characteristics:**  $V_{DD}$  = 3.3V ±10%, 2.5V±10%; 1.8V±10% $T_A$  = -40°C to +105°C,  $C_{LOAD}$  = 2 pF unless noted.

| Parameter                                                                                     | Symbol                   | Min. | Тур. | Max. | Units | Conditions                                                               |

|-----------------------------------------------------------------------------------------------|--------------------------|------|------|------|-------|--------------------------------------------------------------------------|

| Rising Edge Rate                                                                              | _                        | 1    | 2.5  | 4    | V/ns  | Note 2, Note 3                                                           |

| Falling Edge Rate                                                                             | _                        | 1    | 2.5  | 4    | V/ns  | Note 2, Note 3                                                           |

| Differential Output High Voltage                                                              | V <sub>OH</sub>          | 0.6  | _    | 0.9  | V     | Note 2                                                                   |

| Differential Output Low Voltage                                                               | V <sub>OL</sub>          | -0.9 | _    | -0.6 | V     | Note 2                                                                   |

| Absolute Crossing Voltage                                                                     | V <sub>CROSS</sub>       | 0.25 | _    | 0.55 | V     | Note 1, Note 4, Note 5,<br>Note 13                                       |

| Variation of V <sub>CROSS</sub> Over All Rising Clock Edges                                   | V <sub>CROSS_DELTA</sub> | _    |      | 0.14 | V     | Note 1, Note 4, Note 8,<br>Note 13                                       |

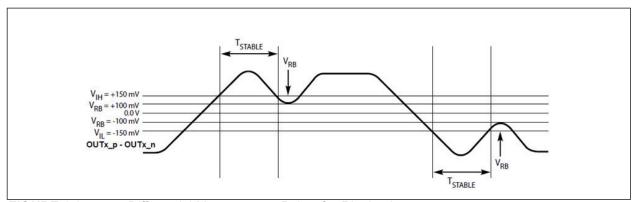

| Ring Back Voltage Margin                                                                      | $V_{RB}$                 | -0.1 |      | 0.1  | V     | Note 2, Note 10, Note 13                                                 |

| Time Before V <sub>RB</sub> is Allowed                                                        | t <sub>STABLE</sub>      | 500  | _    | _    | ps    | Note 2, Note 10, Note 13                                                 |

| Cycle-to-Cycle Additive Jitter                                                                | t <sub>CCJITTER</sub>    | _    | 6.5  | 8.1  | ps    | Note 2, Note 13                                                          |

| Absolute Maximum Output Voltage                                                               | V <sub>MAX</sub>         | _    | _    | 1.15 | V     | Note 1, Note 6                                                           |

| Absolute Minimum Output Voltage                                                               | V <sub>MIN</sub>         | -0.3 | _    |      | V     | Note 1, Note 7                                                           |

| Output Duty Cycle                                                                             | V <sub>DC</sub>          | 48   | 50   | 52   | %     | When input has 50%<br>duty cycle and V <sub>IN</sub> ≥<br>200 mV, Note 2 |

| Rising to Falling Edge Matching                                                               | Rise-Fall<br>Matching    | _    | _    | 20   | %     | Note 1, Note 11                                                          |

| Clock Source DC Impedance (OUTx_p) for parts with $100\Omega$ differential embedded impedance | Z <sub>C-DC_OUT_p</sub>  | 40   | _    | 60   | Ω     | _                                                                        |

| Clock Source DC Impedance (OUTx_n) for parts with 100Ω differential embedded impedance        | Z <sub>C-DC_OUT_n</sub>  | 40   |      | 60   | Ω     | _                                                                        |

#### **OUTPUT ELECTRICAL CHARACTERISTICS (CONTINUED)**

**Electrical Characteristics:**  $V_{DD}$  = 3.3V ±10%, 2.5V±10%; 1.8V±10% $T_A$  = -40°C to +105°C,  $C_{LOAD}$  = 2 pF unless noted.

| Parameter                                                                                    | Symbol                  | Min. | Тур. | Max. | Units  | Conditions |

|----------------------------------------------------------------------------------------------|-------------------------|------|------|------|--------|------------|

| Clock Source DC Impedance (OUTx_p) for parts with 85Ω differential embedded impedance        | Z <sub>C-DC_OUT_p</sub> | 34   | _    | 51   | Ω      | _          |

| Clock Source DC Impedance (OUTx_n) for parts with $85\Omega$ differential embedded impedance | Z <sub>C-DC_OUT_n</sub> | 34   |      | 51   | Ω      | _          |

| Output Frequency                                                                             | F <sub>MAX</sub>        | 0    | _    | 250  | MHz    | _          |

| Output to Output Skew                                                                        | t <sub>oosk</sub>       |      | _    | 30   | ps     | Note 13    |

| Part to Part Output Skew                                                                     | t <sub>POOSK</sub>      |      | _    | 50   | ps     | Note 13    |

| Input to Output Delay                                                                        | t <sub>IOD</sub>        | 0.9  | 1.2  | 1.5  | ns     | _          |

| Output Enable Time                                                                           | t <sub>EN</sub>         | _    | _    | 3.5  | cycles | Note 12    |

| Output Disable Time                                                                          | t <sub>DIS</sub>        | _    | _    | 4.5  | cycles | Note 12    |

- Note 1: Measurement taken from single ended waveform.

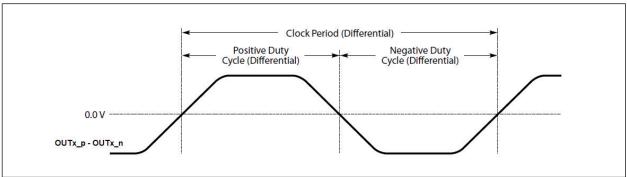

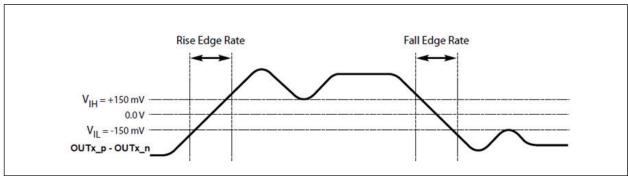

- 2: Measurement taken from differential waveform.

- 3: Measured from -150 mV to +150 mV on the differential waveform (derived from OUTx\_p to OUTx\_n). The signal must be monotonic through the measurement region for rise and fall time. The 300 mV measurement window is centered on the differential zero crossing. See Figure 1-5.

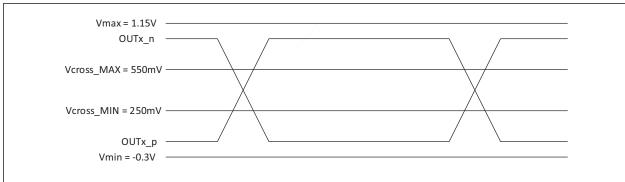

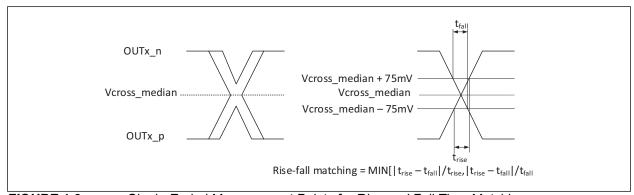

- **4:** Measured at crossing point where the instantaneous voltage value of the rising edge of OUTx\_p equals the falling edge of OUTx\_n. See Figure 1-1.

- 5: Refers to the total variation from the lowest crossing point to the highest, regardless of which edge is crossing. Refers to all crossing points for this measurement. See Figure 1-1.

- 6: Defined as the maximum instantaneous voltage including overshoot. See Figure 1-1.

- 7: Defined as the minimum instantaneous voltage including undershoot. See Figure 1-1.

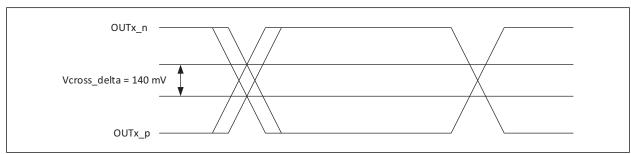

- 8: Defined as the total variation of all crossing voltages of Rising OUTx\_p and Falling OUTx\_n. This is the maximum allowed variance in V<sub>CROSS</sub> for any particular system. See Figure 1-2.

- **9:** System board compliance measurements must use the test load card described in Figure 1-7. OUTx\_p and OUTx\_n are to be measured at the load capacitors C<sub>LOAD</sub>. Single ended probes must be used for measurements requiring single ended measurements. Either single ended probes with math or differential probe can be used for differential measurements.

- 10: T<sub>STABLE</sub> is the time the differential clock must maintain a minimum ±150 mV differential voltage after rising/falling edges before it is allowed to droop back into the V<sub>RB</sub> ±100 mV differential range. See Figure 1-6.

- 11: Matching applies to rising edge rate for OUTx\_p and falling edge rate for OUTx\_n. It is measured using a ±75 mV window centered on the median cross point where OUTx\_p rising meets OUTx\_n falling. The median cross point is used to calculate the voltage thresholds the oscilloscope is to use for the edge rate calculations. The Rise Edge Rate of OUTx\_p should be compared to the Fall Edge Rate of OUTx\_n; the maximum allowed difference should not exceed 20% of the slowest edge rate. See Figure 1-3.

- 12: Output Enable control pins are synchronous with the input clock and it takes four rising edges before outputs get enabled and five rising edges before outputs get disabled. Hence the minimum input frequency is greater than 0 Hz. Once the outputs are enabled the input clock frequency can be reduced to 0 Hz.

- 13: Ensured by design and/or characterization, not tested in production.

#### **JITTER AND PHASE NOISE**

| Parameter                                                                     | Symbol                      | Min. | Тур. | Max. | Units             | Conditions                                |

|-------------------------------------------------------------------------------|-----------------------------|------|------|------|-------------------|-------------------------------------------|

| Peak-to-Peak Additive Jitter                                                  | p-p A <sub>JRMS</sub>       | _    | _    | 4.5  | ps                | Note 1, Note 2, Note 4                    |

| Additive Jitter as per PCle 1.0 (1.5 MHz to 22 MHz)                           | t <sub>jPCle_1.0</sub>      | _    | 0.7  | 0.8  | ps <sub>RMS</sub> | Note 1, Note 2, Note 4                    |

| Additive Jitter as per PCle 2.0 high band (1.5 MHz to 50 MHz)                 | t <sub>jPCle_2.0_high</sub> | _    | 70   | 90   | fs <sub>RMS</sub> | Note 1, Note 2, Note 4                    |

| Additive Jitter as per PCle 2.0 low band (10 kHz to 1.5 MHz)                  | t <sub>jPCle_2.0_low</sub>  | _    | 14   | 20   | fs <sub>RMS</sub> | Note 1, Note 2, Note 4                    |

| Additive Jitter as per PCle 2.0 mid band (5 MHz to 16 MHz)                    | tjPCle_2.0_mid              | _    | 55   | 74   | fs <sub>RMS</sub> | Note 1, Note 2, Note 4                    |

| Additive Jitter as per PCle 3.0 (PLL_BW = 2 to 5 MHz, CDR = 10 MHz)           | t <sub>jPCle_3.0</sub>      | _    | 18   | 22   | fs <sub>RMS</sub> | Note 1, Note 2, Note 4                    |

| Additive Jitter as per PCle 4.0 (PLL_BW = 2 to 5 MHz, CDR = 10 MHz)           | t <sub>jPCle_4.0</sub>      | _    | 18   | 22   | fs <sub>RMS</sub> | Note 1, Note 2, Note 4                    |

| Additive Jitter as per PCle 5.0 (PLL_BW = 0.5 to 1.8 MHz, CDR for 32 GT/s CC) | <sup>t</sup> jPCle_5.0      | _    | 7.5  | 10   | fs <sub>RMS</sub> | Note 2, Note 3, Note 4                    |

| Additive Jitter as per PCle 6.0 (PLL_BW = 0.5 to 1 MHz, CDR for 64 GT/s CC)   | t <sub>j</sub> PCle_6.0     | _    | 4.5  | 6    | fs <sub>RMS</sub> | Note 2, Note 3, Note 4                    |

| Additive jitter as per Intel QPI 9.6 Gbps                                     | t <sub>jQPI</sub>           | _    | 35   | 45   | fs <sub>RMS</sub> | Note 1, Note 2, Note 4                    |

| Additive DMS litter in 4 MHz to 20 MHz bond                                   |                             | _    | 51   | 66   | fs <sub>RMS</sub> | Note 1, Note 2, Note 4<br>(100 MHz clock) |

| Additive RMS jitter in 1 MHz to 20 MHz band                                   | t <sub>j_1M_20M</sub>       | _    | 40   | 54   | fs <sub>RMS</sub> | Note 1, Note 2, Note 4<br>(133 MHz clock) |

| A 1 1111 - PMO 1111 - 1 40 111 - 1 00 MI - 1                                  | #: 40k 00M                  | _    | 52   | 68   | fs <sub>RMS</sub> | Note 1, Note 2, Note 4<br>(100 MHz clock) |

| Additive RMS jitter in 12 kHz to 20 MHz band                                  | tj_12k_20M                  | _    | 44   | 58   | fs <sub>RMS</sub> | Note 1, Note 2, Note 4<br>(133 MHz clock) |

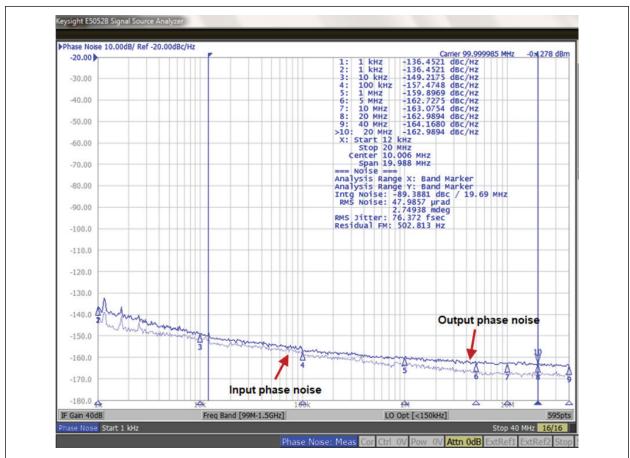

| Notes Elece                                                                   | NE                          | _    | -165 | -163 | dBc/Hz            | Note 1, Note 2, Note 4<br>(100 MHz clock) |

| Noise Floor                                                                   | NF                          | _    | -165 | -163 | dBc/Hz            | Note 1, Note 2, Note 4<br>(133 MHz clock) |

Note 1: Measured into AC test load as per Figure 1-7.

<sup>2:</sup> Measured from differential crossing point to differential crossing point.

<sup>3:</sup> Measured with  $50\Omega$  termination in instrument without a test load.

**<sup>4:</sup>** Ensured by design and/or characterization, not tested in production.

#### **TEMPERATURE SPECIFICATIONS**

| Parameters                                           |                             | Min. | Тур. | Max. | Unit | Condition      |

|------------------------------------------------------|-----------------------------|------|------|------|------|----------------|

| Temperature Ranges                                   |                             |      |      |      |      |                |

| Ambient Operating Temperature Range                  | T <sub>A</sub>              | -40  | _    | +105 | °C   | _              |

| Storage Temperature Range                            | T <sub>S</sub>              | -65  | _    | +150 | °C   | _              |

| Package Thermal Resistances                          | Package Thermal Resistances |      |      |      |      |                |

|                                                      |                             | _    | 35.7 | _    |      | Still air      |

| Junction to Ambient Thermal Resistance               | $\theta_{JA}$               | _    | 30.8 | _    | °C/W | 1m/s airflow   |

|                                                      |                             | _    | 28.6 | _    |      | 2.5m/s airflow |

| Junction to Board Thermal Resistance                 | $\theta_{JB}$               |      | 5    | _    | °C/W | _              |

| Junction to Case Thermal Resistance                  | $\theta_{\sf JC}$           |      | 49.5 |      | °C/W | _              |

| Thermal Characterization, Junction to Top of Package | $\Psi_{ m JT}$              |      | 3    | _    | °C/W | Still air      |

FIGURE 1-1: Single-Ended Measurement Points for Absolute Cross Point and Swing.

FIGURE 1-2: Single-Ended Measurement Points for Delta Cross Point.

FIGURE 1-3: Single-Ended Measurement Points for Rise and Fall Time Matching.

FIGURE 1-4: Differential Measurement Points for Duty Cycle and Period.

FIGURE 1-5: Differential Measurement Points for Rise and Fall Time.

FIGURE 1-6: Differential Measurement Points for Ringback.

FIGURE 1-7: PCIe Test Load.

#### 2.0 TYPICAL OPERATING CHARACTERISTICS

FIGURE 2-1: Typical Expected Phase Noise.

#### 3.0 PIN DESCRIPTIONS

All device inputs and outputs are LP-HCSL unless described otherwise. The Type column uses the following symbols:

• P: Power supply

The descriptions of the pins are listed in Table 3-1.

TABLE 3-1: SYA75604A/B AND SYA75603A/B PIN FUNCTION TABLE

| IABLE 3-1.   | TABLE 3-1: SYA75604A/B AND SYA75603A/B PIN FUNCTION TABLE |                         |      |                                                                                                                                                                                                                                                                                                  |  |                                         |  |  |

|--------------|-----------------------------------------------------------|-------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|-----------------------------------------|--|--|

| Pin Number   | Pin Name<br>SYA75604A/B                                   | Pin Name<br>SYA75603A/B | Туре | Description                                                                                                                                                                                                                                                                                      |  |                                         |  |  |

| Input Refere | ence                                                      |                         |      |                                                                                                                                                                                                                                                                                                  |  |                                         |  |  |

| 1            | IN_p                                                      | IN_p                    |      | Differential/Single Ended Input Reference                                                                                                                                                                                                                                                        |  |                                         |  |  |

|              |                                                           |                         |      | Input frequency range >0 Hz to 250 MHz  Note 1: >0 Hz means frequency higher than DC. Output Enable control pins (OExb) need 3.5 clock cycles of the input clock to enable and 4.5 clock to disable the output. This feature ensures                                                             |  |                                         |  |  |

| 2            | IN_n                                                      | IN_n                    | I    | glitch free transition of the outputs.                                                                                                                                                                                                                                                           |  |                                         |  |  |

|              |                                                           |                         |      | <b>Note 2:</b> The differential input has hysteresis of 30 mV that prevents outputs from randomly toggling when both p and n inputs are at the same voltage level. For example, when p and n inputs are held low, as in the case when the buffer is driven from an HCSL driver that is disabled. |  |                                         |  |  |

| Output Cloc  | ks                                                        |                         |      |                                                                                                                                                                                                                                                                                                  |  |                                         |  |  |

| 4            | OUT0_p                                                    | NC                      |      |                                                                                                                                                                                                                                                                                                  |  |                                         |  |  |

| 5            | OUT0_n                                                    | NC                      |      | Ultra-Low Additive Jitter Differential Outputs 0 to 1                                                                                                                                                                                                                                            |  |                                         |  |  |

| 7            | OUT1_p                                                    | NC                      |      | (SYA75603A/B) and 0 to 3 (SYA75604A/B)                                                                                                                                                                                                                                                           |  |                                         |  |  |

| 8            | OUT1_n                                                    | NC                      | 0    | Output frequency range >0 Hz to 250 MHz                                                                                                                                                                                                                                                          |  |                                         |  |  |

| 10           | OUT2_p                                                    | OUT0_p                  |      |                                                                                                                                                                                                                                                                                                  |  | Output frequency range >0 Hz to 250 MHz |  |  |

| 11           | OUT2_n                                                    | OUT0_n                  |      | NC are no connect pins. They are not bonded to the die but they                                                                                                                                                                                                                                  |  |                                         |  |  |

| 14           | OUT3_p                                                    | OUT1_p                  |      | should be soldered to the board for mechanical reasons.                                                                                                                                                                                                                                          |  |                                         |  |  |

| 15           | OUT3_n                                                    | OUT1_n                  |      |                                                                                                                                                                                                                                                                                                  |  |                                         |  |  |

| Control Inp  | uts                                                       |                         |      |                                                                                                                                                                                                                                                                                                  |  |                                         |  |  |

| 3            | OE0b                                                      | NC                      |      | Output Enable Control                                                                                                                                                                                                                                                                            |  |                                         |  |  |

| 6            | OE1b                                                      | NC                      |      | N/I OF                                                                                                                                                                                                                                                                                           |  |                                         |  |  |

| 12           | OE2b                                                      | OE0b                    |      | When OExb is low the output x where $x = \{0,1\}$ for SYA75603A/B and $x = \{0,1,2,3\}$ for SYA75604A/B is active.                                                                                                                                                                               |  |                                         |  |  |

| 16           | OE3b                                                      | OE1b                    | IPD  | OExb is synchronous and takes 3.5 clock cycles of the input clock to enable and 4.5 clock to disable the output. OExb pins are pulled-down with 100 k $\Omega$ resistor NC are no connect pins. They are not bonded to the die but they                                                          |  |                                         |  |  |

|              |                                                           |                         |      | should be soldered to the board for mechanical reasons.                                                                                                                                                                                                                                          |  |                                         |  |  |

| Power and    | Ground                                                    |                         |      |                                                                                                                                                                                                                                                                                                  |  |                                         |  |  |

| 13           | VDD                                                       | VDD                     | Р    | <b>Positive Supply Voltage:</b> Connect to either 3.3V, 2.5V, or 1.8V supply.                                                                                                                                                                                                                    |  |                                         |  |  |

| 9<br>ePad    | GND                                                       | GND                     | Р    | Ground: Connect to ground.                                                                                                                                                                                                                                                                       |  |                                         |  |  |

#### 4.0 FUNCTIONAL DESCRIPTION

The SYA75603A/03B/604A/04B are PCle clock buffers with ultra-low additive jitter. They can be used in all PCle 1/2/3/4/5/6 common clock and SRIS applications.

SYA75603A/03B and SYA75604A/04B are two and four output PCle clock buffers with glitch free per-output enable/disable control hardware pins. Both devices are packaged in 3 mm x 3 mm VQFN.

They have embedded low-dropout regulators (LDO) for superior power noise supply rejection. They support 1.8V, 2.5V, and 3.3V supplies with tolerance of ±10% which exceeds ±9% required by PCIe Card Electro Mechanical Specification.

#### 4.1 Clock Input

Please refer to the Functional Block Diagrams for how to terminate different signals fed to the input of the device.

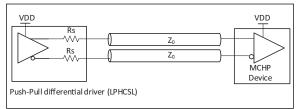

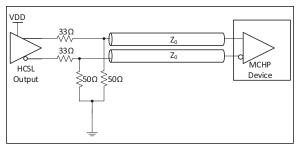

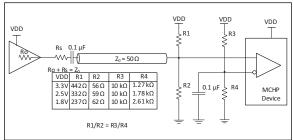

Figure 4-1 and Figure 4-2 show how to terminate input of the device in most common cases: Low Power HCSL (LPHCSL), HCSL, and single ended LVCMOS.

FIGURE 4-1: Input Driven by LPHCSL Driver.

FIGURE 4-2: Input Driven by HCSL Driver.

Figure 4-3 shows how to terminate a single ended output such as LVCMOS. This example assumes  $50\Omega$  transmission line which is the most common for single ended CMOS signaling. Ideally, resistors R1 and R2 should be  $100\Omega$  each and  $R_O$  +  $R_S$  should be  $50\Omega$  so that the transmission line is terminated at both ends with characteristic impedance. If the driving strength of the output driver is not sufficient to drive low impedance, the value of series resistor  $R_S$  should be increased. This will reduce the voltage swing at the input but this should be fine as long as the input voltage swing requirement is not violated (0.3V). The source

resistors of  $R_S$  = 270 $\Omega$  could be used for standard LVCMOS driver. This will provide 516 mV of voltage swing for 3.3V LVCMOS driver with load current of (3.3V/2) \*  $(1/(270\Omega + 50\Omega))$  = 5.16 mA.

For optimum performance both differential input pins (\_p and \_n) need to be DC biased to the same voltage. Hence, the ratio R1/R2 should be equal to the ratio R3/R4.

FIGURE 4-3: Input Driven from a Single-Ended CMOS Output.

The differential input has hysteresis of 30 mV that prevents outputs from randomly toggling when both p and n inputs are at the same voltage level. For example, when p and n inputs are held low, as in the case when the buffer is driven from an HCSL driver that is disabled.

#### 4.2 Clock Outputs

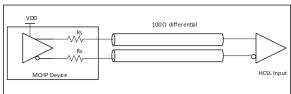

Differential outputs have embedded termination resistors as shown in Figure 4-4. This provides significant saving relative to traditional current based HCSL outputs which require four resistors per differential output.

FIGURE 4-4: Terminating Differential Outputs.

Embedded termination resistors in SYA75603A/03B/604A/04B are matched for  $100\Omega$  differential transmission line.

#### 4.3 Output Enable

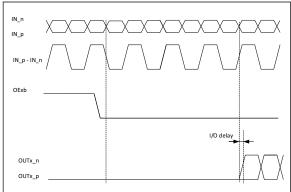

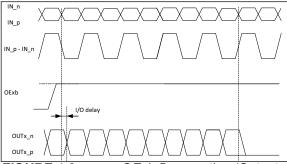

Each output of SYA75603A/03B/604A/04B has an active-low Output Enable (OExb) control pin. The Output Enable and Disable function is synchronous with the input clock, which results in glitchless transitions as shown in Figure 4-5 and Figure 4-6. The OExb is sampled on the falling edge of the differential input (or falling edge of IN\_p signal). It takes 3.5 clock cycles of the input clock to enable an output and 4.5 clock cycles to disable the output, after the change of OExb is sampled.

FIGURE 4-5: OExb Assertion (Output Enable) Timing Diagram.

FIGURE 4-6: OExb Deassertion (Output Disable) Timing Diagram.

#### 5.0 PACKAGING INFORMATION

#### 5.1 Package Marking Information

16-Lead VQFN\*

Example

Legend: XX...X Product code or customer-specific information Υ Year code digit (last of calendar year) YY Year code (last 2 digits calendar year) of WW Week code (week of January 1 is week '01') NNN Alphanumeric traceability code  $\mathsf{JEDEC}^{\mathbb{B}}$ (e3) Pb-free designator for Matte Tin (Sn) This package is Pb-free. The Pb-free JEDEC designat(e3) can be found on the outer packaging for this package.

•, ▲, ▼ Pin one index is identified by a dot, delta up, or delta down (triangle mark).

**Note**: In the event the full Microchip part number cannot be marked on one line, it will be carried over to the next line, thus limiting the number of available characters for customer-specific information. Package may or may not include the corporate logo.

Underbar (\_) and/or Overbar (\_) symbol may not be to scale.

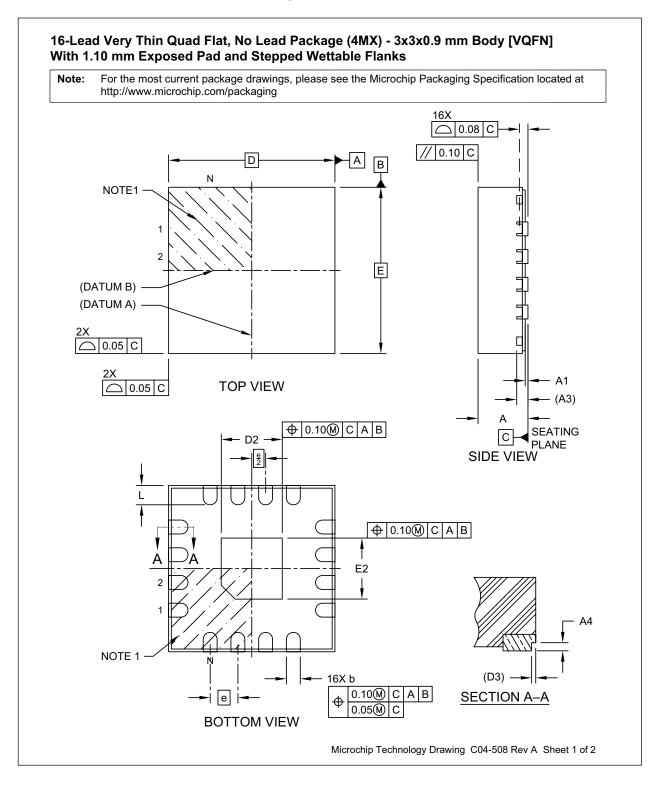

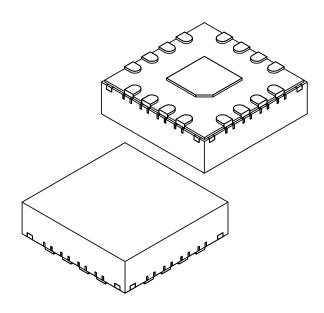

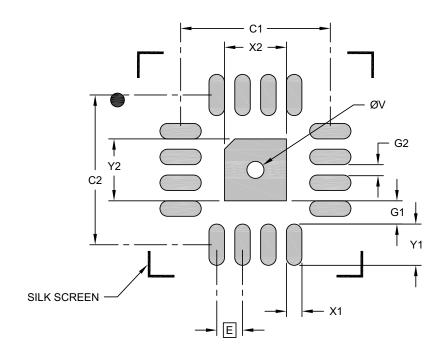

#### 16-Lead VQFN 3.0 mm x 3.0 mm Package Outline and Recommended Land Pattern

#### 16-Lead Very Thin Quad Flat, No Lead Package (4MX) - 3x3x0.9 mm Body [VQFN] With 1.10 mm Exposed Pad and Stepped Wettable Flanks

For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | MILLIMETERS |                |          |      |  |

|----------------------------|-------------|----------------|----------|------|--|

| Dimension                  | Limits      | MIN            | NOM      | MAX  |  |

| Number of Terminals        | N           |                | 16       |      |  |

| Pitch                      | е           |                | 0.50 BSC |      |  |

| Overall Height             | Α           | 0.80           | 0.85     | 0.90 |  |

| Standoff                   | A1          | 0.00           | 0.02     | 0.05 |  |

| Terminal Thickness         | A3          | 0.203 REF      |          |      |  |

| Overall Length             | D           |                | 3.00 BSC |      |  |

| Exposed Pad Length         | D2          | 1.00           | 1.10     | 1.20 |  |

| Overall Width              | Е           |                | 3.00 BSC |      |  |

| Exposed Pad Width          | E2          | 1.00           | 1.10     | 1.20 |  |

| Terminal Width             | b           | 0.20 0.25 0.30 |          |      |  |

| Terminal Length            | L           | 0.25 0.35 0.45 |          |      |  |

| Wettable Flank Step Length | D3          | 0.05 REF       |          |      |  |

| Wettable Flank Step Height | A4          | 0.10           | -        | 0.19 |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Package is saw singulated

- 3. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances. REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-508 Rev A Sheet 2 of 2

## 16-Lead Very Thin Quad Flat, No Lead Package (4MX) - 3x3x0.9 mm Body [VQFN] With 1.10 mm Exposed Pad and Stepped Wettable Flanks

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

#### RECOMMENDED LAND PATTERN

|                                  | ı     | /ILLIMETER | S        |      |

|----------------------------------|-------|------------|----------|------|

| Dimension                        | Units | MIN        | NOM      | MAX  |

| Contact Pitch                    | E     |            | 0.50 BSC |      |

| Optional Center Pad Width        | X2    |            |          | 1.20 |

| Optional Center Pad Length       | Y2    |            |          | 1.20 |

| Contact Pad Spacing              | C1    |            | 2.90     |      |

| Contact Pad Spacing              | C2    |            | 2.90     |      |

| Contact Pad Width (X16)          | X1    |            |          | 0.30 |

| Contact Pad Length (X16)         | Y1    |            |          | 0.80 |

| Contact Pad to Center Pad (X16)  | G1    | 0.45       |          |      |

| Contact Pad to Contact Pad (X12) | G2    | 0.20       |          |      |

| Thermal Via Diameter             | V     |            | 0.33     |      |

#### Notes:

- Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

- 2. For best soldering results, thermal vias, if used, should be filled or tented to avoid solder loss during reflow process

Microchip Technology Drawing C04-2508 Rev A

#### **APPENDIX A: REVISION HISTORY**

#### **Revision A (October 2021)**

Initial release of SYA75603A/03B/604A/04B as Microchip data sheet DS20006438A.

#### Revision B (July 2022)

• Added information specific to the  $85\Omega$  devices to the Current Consumption section of the Electrical Characteristics table.

#### Revision C (May 2023)

- Added PCIe Gen 6.0 information to Features, General Description, and Jitter and Phase Noise.

- Added temperature ratings to the Temperature Specifications table.

| NOTES: |  |  |

|--------|--|--|

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

#### PRODUCT IDENTIFICATION SYSTEM

To order or obtain information, e.g., on pricing or delivery, contact your local Microchip representative or sales office.

| xxx                                                                            | [-XX]                                                                                                                                                                                                                                                        | xxx                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Example                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | es:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|--------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 85Ω<br>SYA75603B: 2 Out<br>100Ω<br>SYA75604A: 4 Out<br>85Ω<br>SYA75604B: 4 Out | Clock Buffer for Autom tput Ultra-Low Additive 2 Clock Buffer for Autor tput Ultra-Low Additive Clock Buffer for Autom tput Ultra-Low Additive tput Ultra-Low Additive                                                                                       | otive<br>Jitter PCIe 1/2/3/4/5/6<br>notive<br>Jitter PCIe 1/2/3/4/5/6<br>otive<br>Jitter PCIe 1/2/3/4/5/6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | b) SYA7:<br>VAO:                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 5604BTWL-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | PCIe 1/2/3/4/5/6 85Ω Clock Buffer, 16-Lead 3 mm x 3 mm VQFN, 120/ Tube, Standard Automotive 4 Output Ultra-Low Additive Jitter PCIe 1/2/3/4/5/6 100Ω Clock Buffer, 16-Lead 3 mm x 3 mm VQFN, 120/ Tube, Standard Automotive 4 Output Ultra-Low Additive Jitter PCIe 1/2/3/4/5/6 85Ω Clock Buffer, 16-Lead 3 mm x 3 mm VQFN, 3,300/                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| TWL = 16-Lea                                                                   | ad 3 mm x 3 mm VQFN                                                                                                                                                                                                                                          | (Wettable Flank)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Reel, Standard Automotive                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| T/R = 3,300 $VXX = Automotive S$                                               | /Reel<br>Suffix in which "XX" is a                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Note 1: Tape and Reel identifier only appears in the catalog part number description. This identifier is used for ordering purposes and is not printed on the device package. Check with your Microchip Sales Office for package availability with the Tape and Reel option.                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                | Package  SYA75603A: 2 Ou 85Ω SYA75603B: 2 Ou 1000 SYA75604A: 4 Ou 85Ω SYA75604B: 4 Ou 1000  TWL = 16-Lea<br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br> | Package Media Type  SYA75603A: 2 Output Ultra-Low Additive 85Ω Clock Buffer for Autom SYA75603B: 2 Output Ultra-Low Additive 100Ω Clock Buffer for Autor SYA75604A: 4 Output Ultra-Low Additive 85Ω Clock Buffer for Autom SYA75604B: 4 Output Ultra-Low Additive 100Ω Clock Buffer for Autor TWL = 16-Lead 3 mm x 3 mm VQFN <a href="https://doi.org/10.1001/journal.com/">doi.org/10.1001/journal.com/</a> SYA75604B: 4 Output Ultra-Low Additive 100Ω Clock Buffer for Autor 100Ω Clock | Package Media Type Automotive Suffix  SYA75603A: 2 Output Ultra-Low Additive Jitter PCle 1/2/3/4/5/6 85Ω Clock Buffer for Automotive SYA75603B: 2 Output Ultra-Low Additive Jitter PCle 1/2/3/4/5/6 100Ω Clock Buffer for Automotive SYA75604A: 4 Output Ultra-Low Additive Jitter PCle 1/2/3/4/5/6 85Ω Clock Buffer for Automotive SYA75604B: 4 Output Ultra-Low Additive Jitter PCle 1/2/3/4/5/6 100Ω Clock Buffer for Automotive  TWL = 16-Lead 3 mm x 3 mm VQFN (Wettable Flank) | Package Media Type Automotive Suffix  SYA75603A: 2 Output Ultra-Low Additive Jitter PCle 1/2/3/4/5/6 85Ω Clock Buffer for Automotive Jitter PCle 1/2/3/4/5/6 100Ω Clock Buffer for Automotive SYA75604A: 4 Output Ultra-Low Additive Jitter PCle 1/2/3/4/5/6 85Ω Clock Buffer for Automotive SYA75604B: 4 Output Ultra-Low Additive Jitter PCle 1/2/3/4/5/6 85Ω Clock Buffer for Automotive SYA75604B: 4 Output Ultra-Low Additive Jitter PCle 1/2/3/4/5/6 100Ω Clock Buffer for Automotive  TWL = 16-Lead 3 mm x 3 mm VQFN (Wettable Flank) | Package Media Type Automotive Suffix  SYA75603A: 2 Output Ultra-Low Additive Jitter PCle 1/2/3/4/5/6 85Ω Clock Buffer for Automotive SYA75603B: 2 Output Ultra-Low Additive Jitter PCle 1/2/3/4/5/6 100Ω Clock Buffer for Automotive SYA75604A: 4 Output Ultra-Low Additive Jitter PCle 1/2/3/4/5/6 85Ω Clock Buffer for Automotive SYA75604B: 4 Output Ultra-Low Additive Jitter PCle 1/2/3/4/5/6 85Ω Clock Buffer for Automotive SYA75604B: 4 Output Ultra-Low Additive Jitter PCle 1/2/3/4/5/6 100Ω Clock Buffer for Automotive  TWL = 16-Lead 3 mm x 3 mm VQFN (Wettable Flank)  Solution  VXX = Automotive Suffix in which "XX" is assigned by Microchip. Standard value "AO" is for standard automotive  Mathematical SyA75603ATWL-VAO:  a) SYA75603ATWL-VAO:  b) SYA75604BTWL-VAO:  C) SYA75604BTWL-VAO:  TVAO:  NOTE: Tape and For Catalog parts a standard sutomotive Sales office Theorem Sales of Theor |

| NOTES: |  |  |

|--------|--|--|

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

#### Note the following details of the code protection feature on Microchip products:

- Microchip products meet the specifications contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is secure when used in the intended manner, within operating specifications, and under normal conditions.

- Microchip values and aggressively protects its intellectual property rights. Attempts to breach the code protection features of Microchip product is strictly prohibited and may violate the Digital Millennium Copyright Act.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of its code. Code protection does not

mean that we are guaranteeing the product is "unbreakable" Code protection is constantly evolving. Microchip is committed to

continuously improving the code protection features of our products.