# **Application note**

### **About this document**

### **Scope and purpose**

The scope of this application note is to describe the basic requirements of the CIPOS™ IPM series for bootstrap circuit design.

### **Intended audience**

Power electronics engineers who want to design a bootstrap circuit for the CIPOS™ IPM series.

### **Table of contents**

| About 1 | this documentthis document                                              |    |

|---------|-------------------------------------------------------------------------|----|

| Table o | of contents                                                             |    |

|         | Bootstrap circuit design                                                |    |

| 1.1     | Bootstrap circuit operation                                             |    |

| 1.1.1   | Internal bootstrap functionality characteristics                        | 2  |

| 1.1.2   | Initial charging of bootstrap capacitor                                 |    |

| 1.1.3   | Voltage drop during pause state of inverter operation                   | 5  |

| 1.2     | Bootstrap voltage (V <sub>BS</sub> ) charging during inverter operation | 5  |

| 1.2.1   | Charging scheme under the 3-phase SVPWM operation                       |    |

| 1.2.2   | Effects on charging situation by operating conditions                   | 11 |

| 1.2.3   | Selection of bootstrap capacitance of C <sub>BS</sub>                   | 15 |

| 1.2.3.1 | Characteristics of bootstrap capacitor, C <sub>BS</sub>                 | 16 |

| 1.2.4   | Effect of charging situation by other modulation scheme                 | 17 |

| 1.2.4.1 | Circuit current of gate driver IC                                       | 17 |

| 2 F     | Reference                                                               | 20 |

| Revisio | on history                                                              | 21 |

### **Application note**

**Bootstrap circuit design**

#### **Bootstrap circuit design** 1

#### 1.1 **Bootstrap circuit operation**

The  $V_{BS}$  voltage, which is the voltage difference between  $V_{B(U,V,W)}$  and  $V_{S(U,V,W)}$ , provides the supply to the highside gate driver (GD) IC within the CIPOS™ IPM. This supply voltage (V<sub>BS</sub>) is recommended to be in the range of 12.5 ~ 18.5 V to ensure that the GD IC can fully drive the high-side switches (IGBTs or MOSFETs). The CIPOS™ IPM includes an undervoltage detection function for the V<sub>BS</sub> to ensure that the GD IC does not drive the high-side switches if the VBS voltage drops below a specified voltage (see datasheet). This function prevents the switch from operating in a high dissipation mode. Please note here that the undervoltage lockout function of any highside section acts only on the triggered channel without any feedback to the control level.

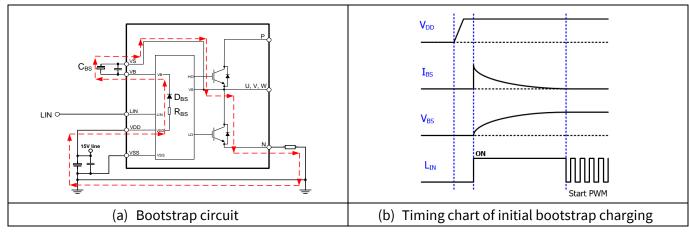

There are a number of ways in which the V<sub>BS</sub> floating supply can be generated. One of them is the bootstrap method described here. This method has the advantage of being simple and inexpensive. However, the duty cycle and on-time are limited by the requirement to refresh the charge in the bootstrap capacitor. The bootstrap supply is formed by a combination of a bootstrap diode (DBS), resistor (RBS) and capacitor (CBS) as shown in Figure 4 (a). The current flow path of the bootstrap circuit is shown in Figure 4 (a). When  $V_s$  is pulled down to ground (either through the low side or the load), C<sub>BS</sub> is charged through D<sub>BS</sub> and R<sub>BS</sub> from the V<sub>DD</sub> supply.

#### Internal bootstrap functionality characteristics 1.1.1

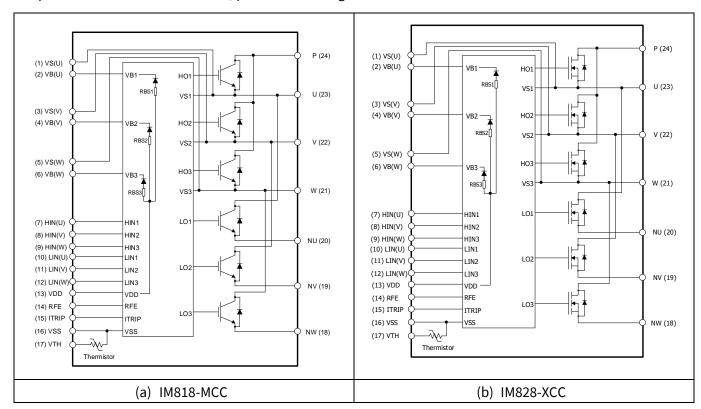

The CIPOS™ IPM integrates three bootstrap functionalities in the internal GD IC, which consist of three diodes and three resistors, as shown in Figure 1. A typical value of R<sub>BS</sub> of the CIPOS™ Maxi family is 120 Ω at room temperature. For more information, please refer to Figure 2 and Table 1.

Internal block diagram of CIPOS™ Maxi family Figure 1

### **Application note**

### **Bootstrap circuit design**

V<sub>DD</sub> of 15 V is recommended when only the integrated bootstrap circuitry is used.

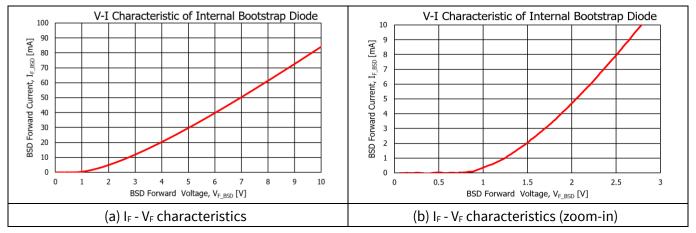

Figure 2 Internal bootstrap diode I<sub>F</sub> - V<sub>F</sub> characteristics

Table 1 Electrical characteristics of internal bootstrap parameters

| Description                     | Conditions                          | Symbol      | Value |      | 11   |      |

|---------------------------------|-------------------------------------|-------------|-------|------|------|------|

| Description                     |                                     |             | Min.  | Тур. | Max. | Unit |

| Repetitive peak-reverse voltage |                                     | $V_{RRM}$   | 1200  | 1    | -    | V    |

| Diode resistance                | Between $V_F = 4 V$ and $V_F = 5 V$ | $R_{BS}$    | -     | 120  | -    | Ω    |

| Diode forward voltage           | $I_F = 0.3 \text{ mA}$              | $V_{F\_BS}$ | -     | 0.9  | -    | V    |

### **Bootstrap circuit design**

#### Initial charging of bootstrap capacitor 1.1.2

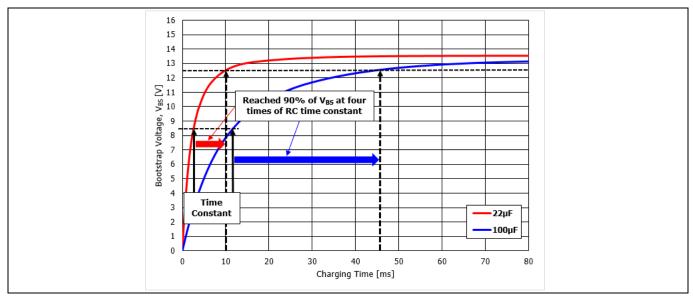

Once we assume that the user uses a single-pulse charging method, the time required for the initial charge depends on the capacitance of CBS, the forward voltage of bootstrap diode (VF BSD) and the resistance of RBS. The charge is performed with a time constant that is roughly calculated from the capacitance of CBS and the resistance of R<sub>BS</sub>.

Example of simulation charging waveform is shown in Figure 3.

Conditions: CIPOS<sup>TM</sup> Maxi IM818-MCC (1200 V / 10 A, D<sub>BS</sub> and R<sub>BS</sub> (120  $\Omega$ ) are embedded on GD IC), C<sub>BS</sub> = 22  $\mu$ F / 100  $\mu$ F,  $V_{DD}$  = 15 V and  $R_{SHUNT}$  = 20 m $\Omega$ .

Figure 3 **Example of initial charging of bootstrap**

As in Figure 3, the V<sub>BS</sub> does not reach the target voltage (only around 62%) by charging up to the time constant (e.g.  $\tau = R \times C = 120 \Omega \times 22 \mu F = 2.64 \text{ ms}$ ). To reach 90% of the target voltage (12.6 V), approximately four times the time constant  $(\tau)$  will be needed. Target voltage does not reach the control power supply voltage  $(V_{DD})$ . It will be approximately 1.0 V lower than V<sub>DD</sub> due to the voltage drop of the low-side IGBT (V<sub>CE(Sat)</sub>) and D<sub>BS</sub> (V<sub>F</sub>) which are in the charging path (see Figure 4 a).

**Bootstrap circuit operation and initial charging** Figure 4

### **Application note**

### **Bootstrap circuit design**

Initial charging needs to be performed until the  $V_{BS}$  (voltage of  $C_{BS}$ ) exceeds the recommended minimum bootstrap voltage ( $V_{BS\_min}$ ) 12.5 V. It is recommended to charge as high as possible taking into account the voltage drop between the end of charging and the start of inverter operation.

### 1.1.3 Voltage drop during pause state of inverter operation

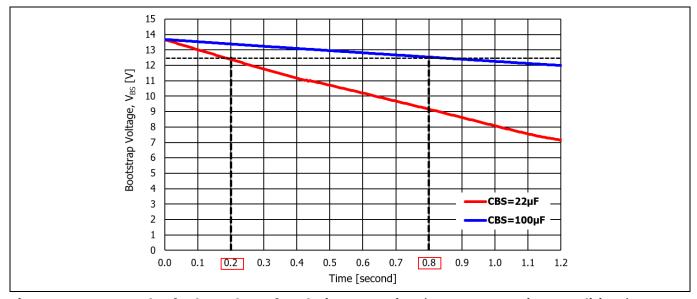

Bootstrap voltage ( $V_{BS}$ ) will gradually decrease due to the circuit current of the GD IC during the pause state of inverter operation. The  $V_{BS}$  drop ratio will be estimated by calculating the capacitance of  $C_{BS}$  and quiescent current of the high-side GD IC,  $I_{QBS}$  (e.g. typical 175  $\mu$ A at  $V_{DD} = 15$  V for CIPOS<sup>TM</sup> Maxi IM818-MCC).

$\Delta V_{BS}$  (voltage drop) =  $I_{QBS}$  x  $t_{discharge}$  /  $C_{BS}$

When the pause state continues for a long time, and  $V_{BS}$  goes below 12.5 V (the recommended minimum control voltage for  $V_{BS}$ ), it is necessary to recharge to  $C_{BS}$  before starting operation. An example of voltage drop calcuation for IM818-MCC is shown in Figure 5. Conditions are as follows: initial  $V_{BS}$  = 13.7 V,  $I_{QBS}$  is a variable value influenced by bootstrap volage ( $V_{BS}$ ),  $C_{BS}$  = 22 and 100  $\mu$ F)

Figure 5 Example of voltage drop of V<sub>BS</sub> during pause time (IM818-MCC at given conditions)

When the pause state continues over 0.2 s with  $C_{BS}$  = 22  $\mu$ F,  $V_{BS}$  will drop below 12.5 V. So, recharging will be required before a restart. If it continues over 0.7 s,  $V_{BS}$  will drop below 9.5 V (minimum voltage of undervoltage lockout function) and the undervoltage protection may work. This is only a calculation example, and ultimately needs to be evaluated in the actual system.

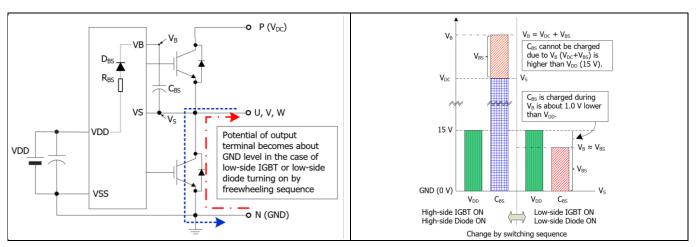

# 1.2 Bootstrap voltage (V<sub>BS</sub>) charging during inverter operation

The energy of  $C_{BS}$ , which was consumed by the internal circuit operating current (e.g. gate charge for high-side IGBT) during the inverter operation by PWM signals like 3-phase space vector pulse width modulation (SVPWM), is recharged through the bootstrap diode ( $D_{BS}$ ) when  $V_{BS}$  becomes lower than the 15 V control supply voltage ( $V_{DD}$ ), as the output terminal (U, V, W) is changed to the GND level during the low-side IGBT turn-on period or low-side freewheeling period after high-side IGBT turns off.

However, the charge current practically starts flowing when  $V_{BS}$  is approximately 1.0 V lower than the low-side control supply 15 V, as  $D_{BS}$  needs to turn on. (Figure 6)

### **Application note**

### **Bootstrap circuit design**

Figure 6 V<sub>BS</sub> charging conditions

Because the potential of the output terminal changes depending on the direction of the motor current flow, i.e. the device (low-side IGBT or diode) into which the current flows, the potential of C<sub>BS</sub> (V<sub>B</sub>), which goes by potential of output terminal, also changes. So, C<sub>BS</sub> is not always charged when the low-side IGBT or diode turns on. The charging situation is explained below.

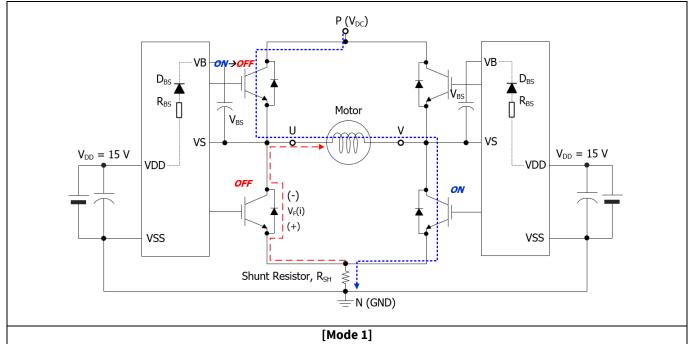

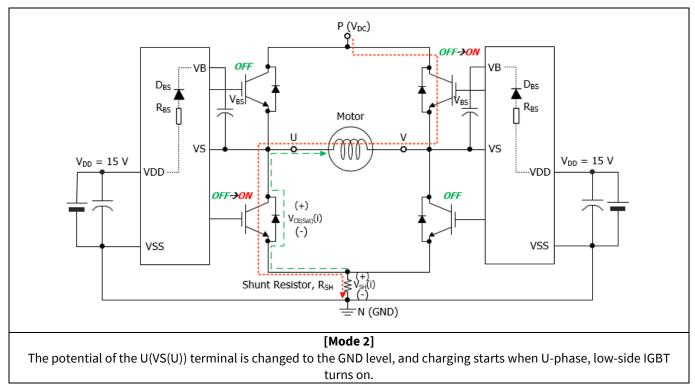

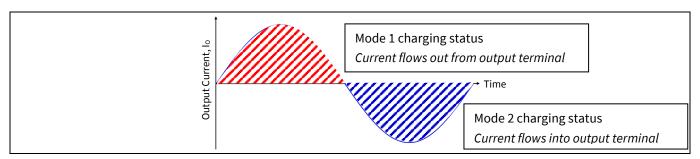

There are two different charging situations during inverter operation:

- Mode 1: Freewheeling situation of the low-side diode after high-side turns off

- Mode 2: Current flowing situation into the low-side IGBT

Current flow chart for both modes is illustrated in Figure 7. The charge mode is decided by the output current direction (Figure 8).

The potential of the U(VS(U)) terminal is changed to the GND level, and charging starts when the U-phase, low-side diode turns on as a result of the freewheeling current following turn-off of high-side IGBT.

### **Application note**

### **Bootstrap circuit design**

Figure 7 V<sub>BS</sub> charging mode when currents flows between U and V phases

Figure 8 Relationship between output current (Io) waveform and charging mode

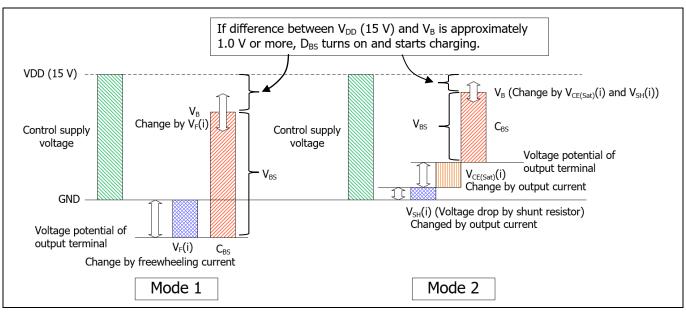

The potential of the output terminal (i.e. reference voltage of  $V_{BS}$ ) depends on the forward voltage ( $V_{F}(i)$ ) in Mode 1, or the saturation voltage of IGBT ( $V_{CE(Sat)}(i)$ ) and the voltage drop by the shunt resistor ( $V_{SH}(i)$ ) in Mode 2, as shown below.

- Mode 1: Voltage of output terminal = GND potential  $(0 \text{ V}) V_F(i)$ < 0 V

- Mode 2: Voltage of output terminal = GND potential (0 V) +  $V_{CE(Sat)}(i) + V_{SH}(i) > 0 V$

Because the V<sub>BS</sub> (voltage by charge stored in C<sub>BS</sub>) can be changed by the potential of the output terminal, the voltage potential of C<sub>BS</sub>(V<sub>B</sub>) then is as follows in Figure 9.

- Mode 1:  $V_B = V_{BS} V_F(i)$

- Mode 2:  $V_B = V_{BS} + V_{CE(Sat)}(i) + V_{SH}(i)$

### **Application note**

### **Bootstrap circuit design**

Figure 9 Difference of potential V<sub>CBS</sub> by charging modes

When the voltage difference between the control supply voltage ( $V_{DD} = 15 \text{ V}$ ) and  $V_B$  is about 1.0 V or more,  $D_{BS}$ turns on, and the charge current starts flowing. So the voltage of V<sub>B</sub>, at which C<sub>BS</sub> can be initially charged, is calculated as shown below.

Mode 1:  $15 \text{ V} - \text{V}_{B} \ge 1.0 \text{ V}$

15 V +  $V_F(i)$  – 1.0 V  $\geq V_{BS}$

$15 \text{ V} - \text{V}_{B} \ge 1.0 \text{ V}$ Mode 2:

15 V -  $V_{CE(Sat)}(i) - V_{SH}(i) - 1.0 V \ge V_B$

For example, in the case of CIPOS™ Maxi IM818-MCC at about 0 A and 10 A collector current, the maximum V<sub>BS</sub> (voltage by charge stored in CBS), at which CBS can start to be charged, is roughly estimated at each mode as below.

Conditions: At  $I_C = 10$  A,  $V_F = 1.76$  V,  $V_{CE(Sat)} = 2.06$  V and shunt resistance = 20 m $\Omega$ At  $I_C \approx 0$  A,  $V_F = 0.0$  V,  $V_{CE(Sat)} = 0$  V and shunt resistance = 20 m $\Omega$

Electrical characteristics of internal bootstrap parameters Table 2

|        | I <sub>C</sub> = 10 A                         | I <sub>c</sub> = 0 A                         |

|--------|-----------------------------------------------|----------------------------------------------|

| Mode 1 | 15.76 V (15 V + 1.76 V - 1.0 V)               | 14.0 V (15 V + 0.0 V - 1.0 V)                |

| Mode 2 | 11.84 V (15 V – 2.06 V - (0.02*10 A) - 1.0 V) | 14.0 V (15 V – 0.0 V - (0.02 * 0 A) - 1.0 V) |

In Table 2, it can be seen that the V<sub>BS</sub> charging at mode 1 is able to start at higher V<sub>BS</sub> than that at mode 2, i.e. V<sub>BS</sub> is needed to drop further to start charging at mode 2. Since C<sub>BS</sub> can start to be charged under this maximum voltage, it also means the maximum charged voltage by the bootstrap circuit depends on the output current and characteristics of power devices such as IGBTs and diodes.

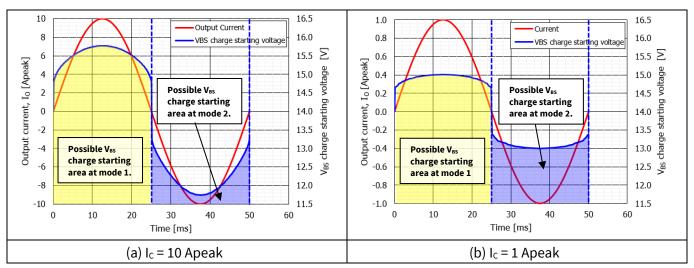

Calculated charge starting voltage is described in Figure 10 under the following conditions: output current (10 A / 1 A and 20Hz) for the DUT IM818-MCC. This has helped us to understand that bootstrap voltage V<sub>BS</sub> is related to output current amplitude.

### **Application note**

### **Bootstrap circuit design**

Expected  $V_{BS}$  charge starting voltage ( $F_0 = 20Hz$ ) Figure 10

### **Application note**

### **Bootstrap circuit design**

#### 1.2.1 Charging scheme under the 3-phase SVPWM operation

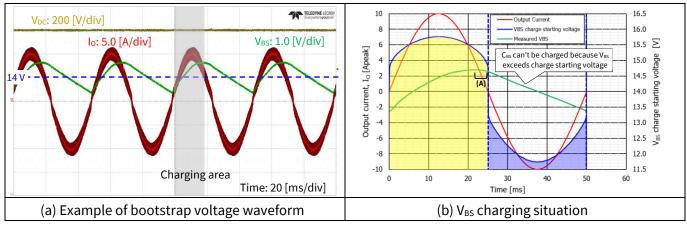

This section shows the details of a charging scheme in the case of a 3-phase SVPWM. Figure 11 (a) shows the V<sub>BS</sub> and output current waveforms of the CIPOS™ Maxi IM818-MCC (10 A / 1200 V) in real operation under the conditions shown below.

In this example, the capacitance of CBS is selected intentionally at a smaller value for easy confirmation of the V<sub>BS</sub> change in actual operation.

Conditions:  $V_{DC} = 600 \text{ V}$ ,  $V_{DD} = 15 \text{ V}$ ,  $F_{SW} = 10 \text{ kHz}$ ,  $I_0 = 10 \text{ Apeak}$ , PF = 0.99, MI = 0.56,  $F_0 = 20 \text{ Hz}$ ,  $C_{BS} = 10 \mu F$ ,  $R_{Shunt}$ = 20 mΩ, 3-phase SVPWM operation

Figure 11 Bootstrap voltage (V<sub>BS</sub>) charge and discharge sequence

From Figure 11 (a), it can be confirmed that charging for C<sub>BS</sub> was performed only in the Mode 1 period (positive output current), and discharging for C<sub>BS</sub> continued in the Mode 2 period (negative output current).

Figure 11 (b) shows that the V<sub>BS</sub> (voltage of C<sub>BS</sub>) waveform was overlapped in Figure 10 (a) at 10 A. In this figure, we can see that C<sub>BS</sub> can be charged during the positive output current period (Mode 1), but during the negative output current period (Mode 2), it cannot be charged, as the voltage of V<sub>BS</sub> is higher than the charge starting voltage. Therefore, C<sub>BS</sub> will mainly be charged in Mode 1 (positive current freewheeling to low-side diode) except for certain conditions like small capacitance of C<sub>BS</sub> or slow output frequency. Here there are noncharged periods despite V<sub>BS</sub> being lower than charge starting voltage. (Part A in Figure 11 (b)) The reasons are suggested below.

In part A, the voltage difference between the voltage of V<sub>BS</sub> and the charge starting voltage is smaller, i.e. the voltage applied to D<sub>BS</sub> is small and hence the charging current that flows into C<sub>BS</sub> also decreases. It leads to a drop in V<sub>BS</sub>, as the quantity of discharge exceeds that of the charge.

In addition, charging to C<sub>BS</sub> can also be affected by other inverter operating conditions. In the next section, the effects on the charging situation due to operating conditions by 3-phase SVPWM are explained using simulation waveforms.

### **Application note**

### **Bootstrap circuit design**

### 1.2.2 Effects on the charging situation by operating conditions

To consider the effects on the charging situation by operating conditions, the results of simulation of V<sub>BS</sub> with various conditions are described here. The simulation conditions are as follows:

- Normal conditions

- DUT : CIPOS<sup>™</sup> Maxi IM818-MCC (1200 V / 10 A),  $F_{SW} = 10$  kHz,  $F_0 = 20$  Hz,  $C_{BS} = 6.8$  µF, power factor = 0.8, modulation index = 0.8,  $V_{DC} = 600$  V,  $V_{DD} = 15$  V,  $R_{shunt} = 20$  m $\Omega$ , 3-phase SVPWM

- Comparative conditions (normal conditions are used, if not stated otherwise)

- Output frequency, F<sub>0</sub>: 10 / 20 / 60 / 120 Hz

- Switching frequency, F<sub>sw</sub>: 5 / 10 / 20 kHz

- Capacitance of C<sub>BS</sub>: 4.7 / 10 / 22 / 100 μF

- ➤ Output current, I<sub>0</sub>: 5 / 10 Apeak

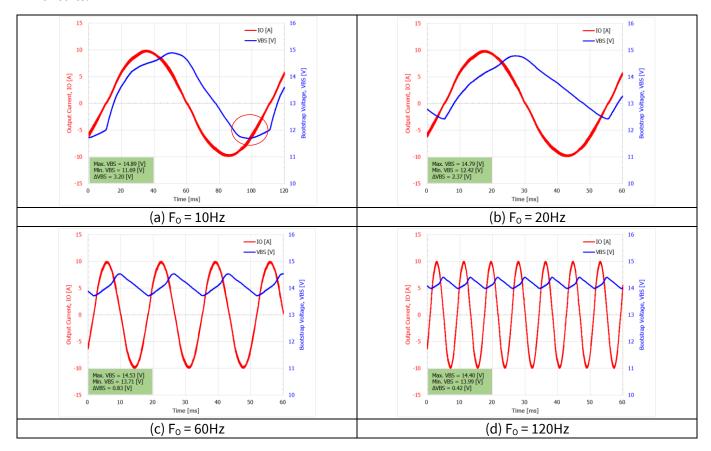

### (1) Comparison of output frequency, $F_0$ : 10 / 20 / 60 / 120 Hz

The results of simulation under four output-frequency conditions are shown in Figure 12. In Figure 12 (a) where the output frequency is 10 Hz, one cycle is longer and the Mode 2 period (negative output current area) is longer as well. The  $V_{BS}$  drops to under 12.5 V, which is the recommended minimum  $V_{BS}$  of IM818-MCC. Here,  $V_{BS}$  is partially charged under Mode 2 conditions due to excessive  $V_{BS}$  drops.

On the other hand, in Figure 12 (d) where the output frequency is 120 Hz, one cycle is shorter, so the  $V_{BS}$  drop is smaller. The ripple of the bootstrap voltage ( $\Delta V_{BS}$ ) is also smaller than one at 10 Hz.

Under these normal operating conditions, if the lower output frequency operation (below 10 / 20Hz) is needed in your system, the capacitance of  $C_{BS}$  (6.8  $\mu F$ ) in the given conditions is not suitable. The reason for this is that the lower  $V_{BS}$  can lead to high power dissipation or to a system stop via the IPM protection function, i.e. undervoltage lockout. Therefore, sufficient evaluation is needed when designing bootstrap circuits.

### **Application note**

# **Bootstrap circuit design**

#### Figure 12 **Comparison of output frequency**

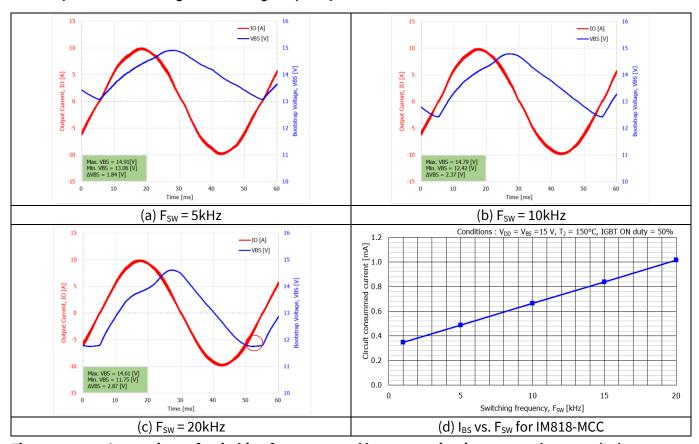

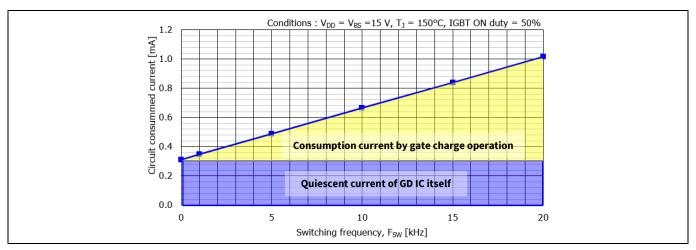

### (2) Comparison of switching frequency, F<sub>SW</sub>: 5 / 10 / 20 kHz

The results of the simulation with three switching-frequency conditions are shown in Figure 13 (a), (b), and (c). When the switching frequency (F<sub>SW</sub>) is increased, the amount of gate charge (circuit current of GD IC) increases by switching frequency accordingly as Figure 13 (d).

Therefore, the amount of discharge by the gate charge increase exceeds the amount of charge. Therefore  $\Delta V_{BS}$  increases depending on the switching frequency. So usually the capacitance of  $C_{BS}$  needs to increase when you want to use higher switching-frequency conditions.

Figure 13 Comparison of switching frequency and bootstrap circuit consumed current (IBS) vs. switching frequency (Fsw) for IM818-MCC

### **Application note**

### **Bootstrap circuit design**

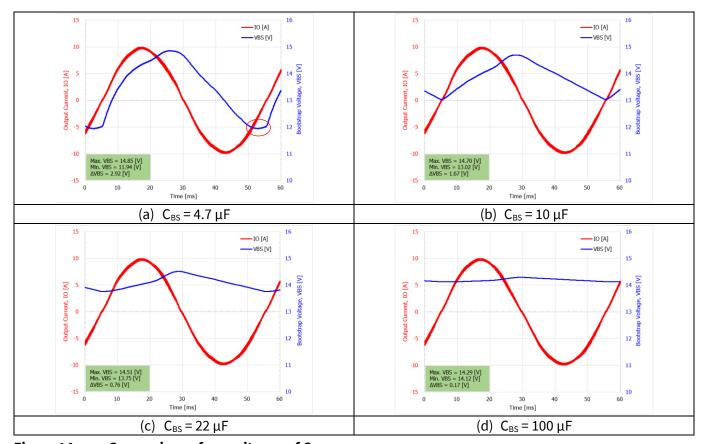

### (3) Comparison of bootstrap capacitance, $C_{BS}$ : 4.7 / 10 / 22 / 100 $\mu F$

The results of simulation with four conditions of capacitance of C<sub>BS</sub> are shown in Figure 14. When the capacitance C<sub>BS</sub> is quite small such as in Figure 14 (a), the voltage drop of V<sub>BS</sub> increases significantly. Then the minimum  $V_{BS}$  falls extremely low and the  $V_{BS}$  ripple voltage ( $\Delta V_{BS}$ ) rises. The increment of  $\Delta V_{BS}$  can affect the reduction of bootstrap capacitor lifetime. Therefore, the recommended value of ∆V<sub>BS</sub> for CIPOS™ IPM is within 1.0 Vp-p.

Figure 14 Comparison of capacitance of CBS

### **Application note**

### **Bootstrap circuit design**

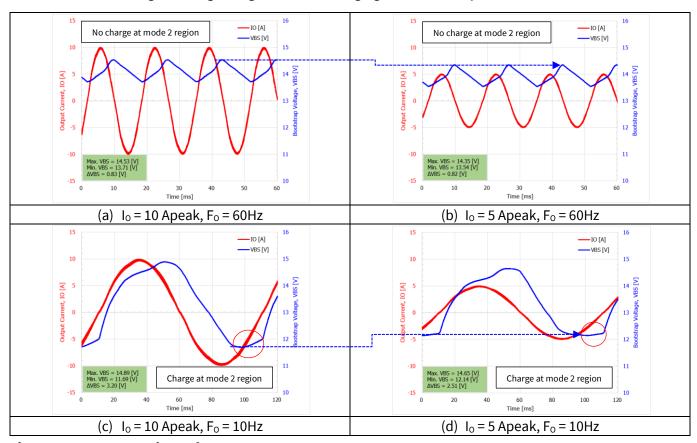

(4) Comparison output current,  $I_0$ : 5 / 10 Apeak at  $F_0$  = 10 / 60Hz

The results of simulation with four conditions of output current are shown in Figure 15. As mentioned in section 1.2, the charge-starting voltage is affected by output current. As shown in Figure 10, when the output current gets low, the charge-starting voltage decreases in Mode 1 (positive output current area) and increases in Mode 2 (negative output current area). So the maximum / minimum value of V<sub>BS</sub> changes accordingly. As shown in Figure 15 (a) and (b), the maximum V<sub>BS</sub> decreases at a lower output current condition. Also, as shown in Figure 15 (c) and (d), on which there is charging at Mode 2, minimum V<sub>BS</sub> will rise, since the charge-starting voltage rises, and charging becomes easily.

Figure 15 **Comparison of output current**

According to simulation results above  $(1) \sim (4)$ , with the exception of capacitance of bootstrap capacitor (CBS), we can consider that the operating conditions mostly affected by bootstrap voltage (VBS) are

- Output current frequency, Fo

- Switching frequency, F<sub>sw</sub>

Note that these results are only provided as examples. It is necessary to consider further evaluations and confirmation at the system-design stage. Becase bootstrap voltage is also affected by other operating conditions, such as PWM (e.g. discontinuous PWM), power factor, modulation index, power device (IGBT and MOSFET).

And above all, simulations are performed at a control supply voltage of  $V_{DD} = 15 \text{ V}$ . If  $V_{DD}$  is reduced to 14 V, it can lead to a drop of 1 V on all above results of V<sub>BS</sub> directly. So, the variation of V<sub>DD</sub> must also be considered.

### **Application note**

### **Bootstrap circuit design**

### 1.2.3 Selection of bootstrap capacitance of C<sub>BS</sub>

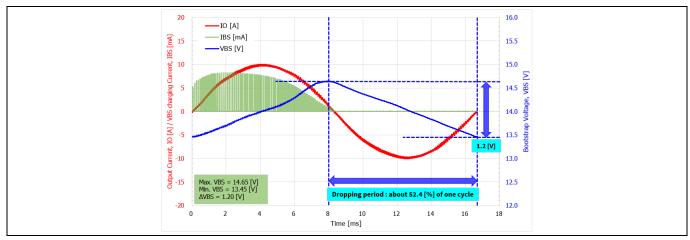

The charging state of  $C_{BS}$  changes due to continuously changing operating conditions. Therefore, it is not easy to estimate the exact value of bootstrap voltage ( $V_{BS}$ ). But the ripple voltage of  $V_{BS}$  ( $\Delta V_{BS}$ ) can be roughly estimated under the conditions without charging in Mode 2, as the bootstrap capacitor charging current ( $I_{BS}$ ) is almost zero in Mode 2. In this section, the estimation method of  $\Delta V_{BS}$  under the given conditions is explained in Figure 16.

• Conditions :  $V_{DC}$  = 600 V,  $V_{DD}$  = 15 V,  $F_{SW}$  = 10 kHz,  $I_{O}$  = 10 A,  $F_{O}$  = 60 Hz,  $C_{BS}$  = 4.7  $\mu$ F, 3-phase SVPWM, IM818-MCC

Figure 16 Charging waveform (based on simulation)

The waveform on the conditions is shown in Figure 16. As mentioned above, the charge of  $C_{BS}$  is performed during the period of positive current. Its voltage drop time is about 52.4 [%] of the output current cycle. The voltage drop for this period equals the ripple voltage at this condition. The  $\Delta V_{BS}$  can be estimated as the amount of discharge of  $C_{BS}$  for the dropping time and capacitance of  $C_{BS}$ .

•  $\Delta V_{BS}$  = Amount of discharge of  $C_{BS}$  for the dropping period  $\div$  capacitance of  $C_{BS}$

Amound of discharge of C<sub>BS</sub> is calculated as below

• Amount of discharge of  $C_{BS}$  = consumed current of GD IC × output current cycle × dropping time ratio

The consumed current of GD IC can be obtained from the graph of bootstrap circuit consumed current ( $I_{BS}$ ) vs. switching frequency ( $F_{SW}$ ) as shown in Figure 13 (d). So the  $\Delta V_{BS}$  under given conditions can be estimated roughly as:

•  $\Delta V_{BS} = (0.66 \text{ [mA] X } 16.67 \text{ [ms] X } 52.4 \text{ [\%]}) \div 4.7 \text{ [}\mu\text{F]} = 1.23 \text{ [V]}$

The recommended value of  $\Delta V_{BS}$  is within 1.0 Vp-p for CIPOS<sup>TM</sup> IPM. When designing capacitance of  $C_{BS}$ , it is necessary to consider various conditions such as operating conditions, tolerance of capacitance, and temperature characteristics of capacitance, DC bias and life time, and the tolerance of bootstrap circuit current of GD IC. Also the minimum voltage of  $V_{BS}$  during operation should remain above 12.5 V. For example, 3 ~ 4 times capacitance is recommended, which makes a 1.0 V voltage drop under typical conditions. In the above case, when type 5.6  $\mu$ F capacitor is used, its typical  $\Delta V_{BS}$  is approximately 1.0 V. So a value above 16 ~ 22  $\mu$ F, which is 3 ~ 4 times the 5.6  $\mu$ F, is the target value.

This estimation method is only an example under given conditions. If conditions are changed, the dropping period (52.4%) can be changed. Also, capacitance might have to be increased due to the characteristics of  $C_{BS}$  in Table 3. Therefore, sufficient evaluation in the real system is needed.

### **Application note**

**Bootstrap circuit design**

#### Characteristics of bootstrap capacitor, CBS 1.2.3.1

Electrolytic capacitors are used for CBS generally. And recently MLCC (multilayer ceramic capacitors) with large capacitance are also applied. But, the DC bias characteristics of the MLCC when applying DC voltage are considerably different from those of the electrolytic capacitor, especially the large capacitance type. Some differences in capacitance characteristics between electrolytic and ceramic capacitors are listed in Table 3.

Table 3 Difference of capacitance characteristics between electrolytic and ceramic capacitors

|                                                                 | Electrolytic capacitor                                                                                                         | MLCC                                                                                                                           |

|-----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|

| Temperature<br>characteristics (T <sub>A</sub> :<br>-20 ~ 85°C) | - Aluminum type: Low temp.: -10%, High temp.: +10% - Conductive polymer aluminum solide type: Low temp.: -5%, High temp.: +10% | - Difference due to temp.<br>characteristics:<br>Low temp.: -5% ~ 0%<br>High temp.: -5% ~ -10%<br>(with X5R, X7R)              |

| DC bias<br>characteristics<br>(applying DC 15 V)                | Nothing within rating voltage                                                                                                  | Difference due to temp.<br>characteristics, rating voltage,<br>package size and so on -50% ~ -15%<br>(with X7R, 50 VDC rating) |

### **Bootstrap circuit design**

#### Effect of charging by other modulation schemes 1.2.4

#### **Circuit current of gate driver IC** 1.2.4.1

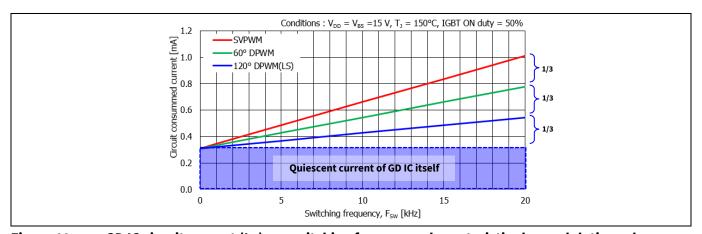

High-side, gate driver-IC circuit current that applies the bootstrap circuit varies according to the control method. The above Figure 13 (d) described the circuit current in the case of 3-phase SVPWM (continuous switching). In this section, the approximation method of the gate driver (GD) IC circuit current in the case of 60° discontinuous PWM and 120° discontinuous PWM is explained.

Bootstrap circuit current I<sub>BS</sub> vs. switching frequency characteristics for IM818-MCC (typical data), which are described in Figure 17, are re-described in Figure 13 (d).

Figure 17 Bootstrap-circuit consumed current (IBS) vs. switching frequency (FSW) for IM818-MCC

The total GD IC circuit current at each frequency consists of the quiescent current and the current by gate charge operation. GD IC circuit current at 0Hz is the quiescent current, which is consumed by GD IC itself regardless whether it is with or without switching. When the value exceeds 0 Hz, the sum of the quiescent current at 0 Hz and the consumption current caused by the gate charge operation during switching becomes the total GD IC circuit current.

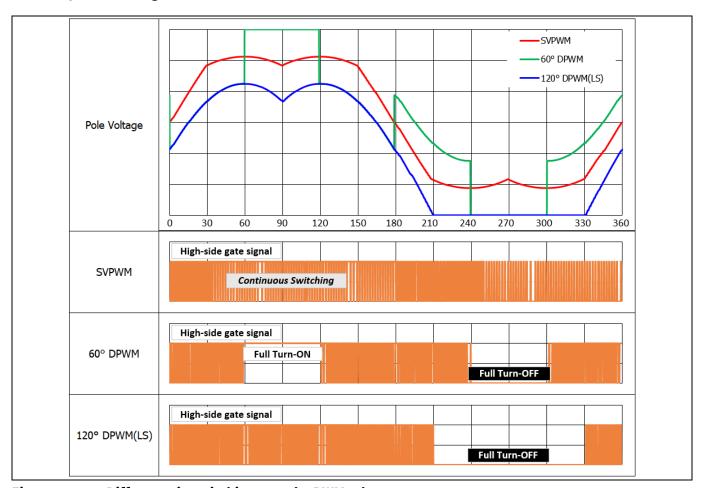

To estimate the circuit current in the case of discontinuous PWM, all modulation schemes are explained as follows:

- SVPWM: 3-phase space vector pulse-width modulation (continuous switching)

- 60° DPWM: discontinuous PWM with 60° continuous conduction periods in phase with the peak of the phase voltage

- 120° DPWM(LS): discontinuous PWM with 120° continuous conduction of each low-side switch

And, the difference between SVPWM and and two discontinuous PWM schemes is shown in Figure 18.

### **Application note**

### **Bootstrap circuit design**

Figure 18 Difference in switching state by PWM scheme

As shown in Figure 18, the difference in GD IC circuit current between these three methods equals the difference in switching times. Switching times in the case of 60° DPWM becomes two-thirds that of SVPWM, and switching times at 120° DPWM becomes one-third at SVPWM. So each GD IC circuit current is the sum of steady consumption current and two-thirds or one-third of the switching current, respectively, as seen in Figure 17. The calculated results of the GD IC circuit currents at each modulation scheme are shown in Figure 19.

Figure 19 GD IC circuit current (IBS) vs. switching frequency characteristics by modulation scheme

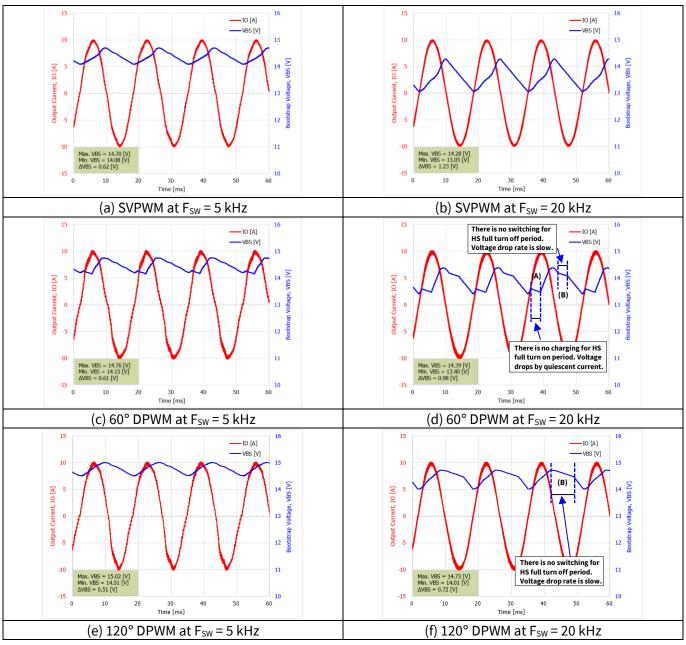

Example of simulation results of charging state at SVPWM and two discontinuous modulation schemes are described in Figure 20.

### **Application note**

### **Bootstrap circuit design**

• Conditions: CIPOS<sup>TM</sup> Maxi IM818-MCC (1200 V / 10 A),  $F_{SW} = 5$  / 20 kHz,  $F_0 = 60$  Hz,  $C_{BS} = 6.8 \mu F$ , power factor = 0.8, modulation index = 0.8,  $V_{DC} = 600 \text{ V}$ ,  $V_{DD} = 15 \text{ V}$ ,  $R_{shunt} = 20 \text{ m}\Omega$

Figure 20 Bootstrap voltage charging state according to modulation scheme

In the case of 60° DPWM (Figure 20 (d)), during the full turn-off period (B), the voltage drop rate gets smaller because gate charging is not performed, and the voltage drops by quiescent current. On the other hand, bootstrap voltage ( $V_{BS}$ ) charging is not performed during the full turn-on period (A) in the positive current region, in which charging normally has a good performance; the charging efficiency is worse. But in these results, since total GD IC circuit current in the case of 60° DPWM was smaller than at SVPWM, the minimum / maximum  $V_{BS}$  and  $\Delta V_{BS}$  improved somewhat.

In the case of 120° DPWM (Figure 20 (f)), during full turn-off period (B), the voltage drop rate is smaller, as gate charging is not performed, and the voltage drops due to quiescent current. So, in these simulation conditions, V<sub>BS</sub> charging efficiency of 120° DPWM is an improvement in comparison to the other schemes.

### **Application note**

### Reference

# 2 Reference

- [1] AN2020-41\_CIPOS™ MAXI IPM IM828 series application note, Infineon Technologies

- [2] AN2019-16\_CIPOS MAXI IPM IM818 series application note, Infineon Technologies

- [3] IM818-MCC and IM828-XCC datasheet, Infineon Technologies

# Error! Unknown document property name.

# **Bootstrap Circuit Design for the CIPOS™ IPM series**

**Application note**

**Revision history**

# **Revision history**

| Document version | Date of release               | Description of changes |

|------------------|-------------------------------|------------------------|

| 1.0              | 28 <sup>th</sup> , Dec., 2020 | Initial release        |

|                  |                               |                        |

|                  |                               |                        |

### Trademarks

Edition 2021-01-06

Published by

Infineon Technologies AG

81726 Munich, Germany

© 2021 Infineon Technologies AG. All Rights Reserved.

Do you have a question about this document?

Email: erratum@infineon.com

Document reference AN2020-14

### IMPORTANT NOTICE

The information contained in this application note is given as a hint for the implementation of the product only and shall in no event be regarded as a description or warranty of a certain functionality, condition or quality of the product. Before implementation of the product, the recipient of this application note must verify any function and other technical information given herein in the real application. Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind (including without limitation warranties of non-infringement of intellectual property rights of any third party) with respect to any and all information given in this application note.

The data contained in this document is exclusively intended for technically trained staff. It is the responsibility of customer's technical departments to evaluate the suitability of the product for the intended application and the completeness of the product information given in this document with respect to such application.

For further information on the product, technology delivery terms and conditions and prices please contact your nearest Infineon Technologies office (www.infineon.com).

Please note that this product is not qualified according to the AEC Q100 or AEC Q101 documents of the Automotive Electronics Council.

### WARNINGS

Due to technical requirements products may contain dangerous substances. For information on the types in question please contact your nearest Infineor Technologies office.

Except as otherwise explicitly approved by Infineor Technologies in a written document signed by authorized representatives of Infineor Technologies, Infineon Technologies' products may not be used in any applications where a failure of the product or any consequences of the use thereof car reasonably be expected to result in personal injury.