# **ZL30291B**

# **CK440Q Compliant Gen 6 PCIe and Platform Timing Clock Generator**

#### **Features**

- Fully Compliant with Intel CK440Q Specification

- Fully Compliant with PCIe Gen 1/2/3/4/5/6

- 19 Low-Power Push-Pull HCSL PCIe Outputs

- Seven Dedicated 100 MHz Outputs

- Three Dedicated 25 MHz Outputs

- Nine Selectable Outputs: 25 MHz or 100 MHz

- Embedded Source Terminations

- · Platform Time Input and Output Clocks

- · Ultra-Low Jitter: 80 fs Maximum

- · Programmable SSC on 100 MHz Outputs

- Embedded Low Dropout (LDO) Voltage Regulator Provides Superior Power Supply Noise Rejection

- Maximum Output-to-Output Skew of 50 ps

- · SMBus and Side-Band Interface

- 3.3V ±10% Power Supply Tolerance Meets PCIe Electromechanical Specification (3.3V ±9%)

#### **Applications**

- PCIe Gen1/2/3/4/5/6 Clock Generation

- · Platform Tuning

- Intel QPI/UPI

- Servers

- · Storage and Data Centers

- · Switches and Routers

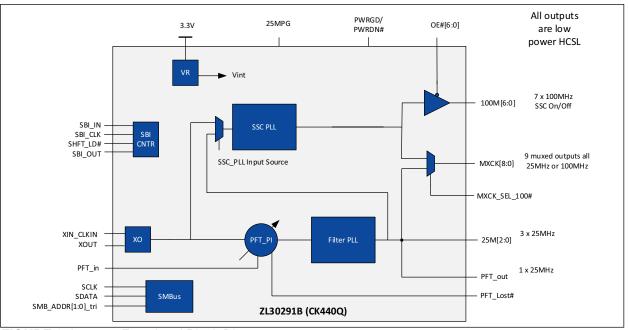

FIGURE 0-1: Functional Block Diagram.

#### TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at docerrors@microchip.com. We welcome your feedback.

#### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS300000000).

#### **Errata**

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include -literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

### **TABLE OF CONTENTS**

| 1.0 "Pin Description and Configuration"                      | . 6 |

|--------------------------------------------------------------|-----|

| 2.0 "Functional Description"                                 | 11  |

| 2.1 "Applications"                                           |     |

| 2.2 "Functional Description"                                 |     |

| 2.3 "Platform Timing Clock Input"                            | 12  |

| 2.4 "Clock Outputs"                                          | 13  |

| 2.5 "Termination of Unused Outputs"                          |     |

| 2.6 "OE# and Output Enables (Control Register)"              | 14  |

| 2.7 "OE[6:0]# Assertion (Transition from '1' to '0')"        | 14  |

| 2.8 "OE[6:0]# De-Assertion (Transition from '0' to '1')"     | 14  |

| 2.9 "25MPG"                                                  | 15  |

| 2.10 "PWRGD/PWRDN#"                                          | 15  |

| 2.11 "PWRDN# Assertion"                                      | 15  |

| 2.12 "PWRGD Assertion"                                       | 16  |

| 2.13 "SMB_ADR0_tri, SMB_ADR1_tri - Address Selection"        | 16  |

| 2.14 "SMBus Byte Read/Write"                                 | 17  |

| 2.15 "SMBus Block Read/Write"                                | 17  |

| 2.16 "Programming via Side-Band Interface"                   | 18  |

| 2.17 "Output Enable/Disable Priority"                        | 19  |

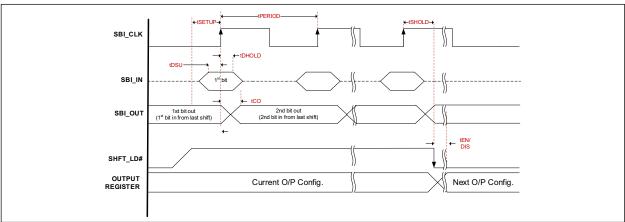

| 2.18 "Side-Band Interface Functionality and Detailed Timing" | 21  |

| 2.19 "Platform Time (PFT) Phase/Frequency Tracking"          | 22  |

| 3.0 "Register Map"                                           | 23  |

| 4.0 "Electrical Characteristics"                             | 29  |

| 4.1 "AC and DC Electrical Characteristics"                   | 29  |

| 4.2 "DC Electrical Specifications"                           | 29  |

| 4.3 "AC Electrical Specifications"                           | 31  |

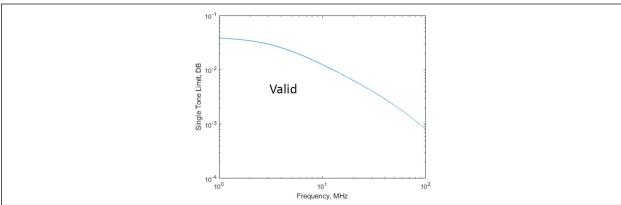

| 4.4 "Power Noise Tolerance"                                  | 33  |

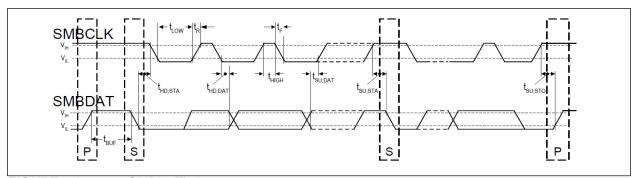

| 4.5 "SMBus Electrical Characteristics"                       | 34  |

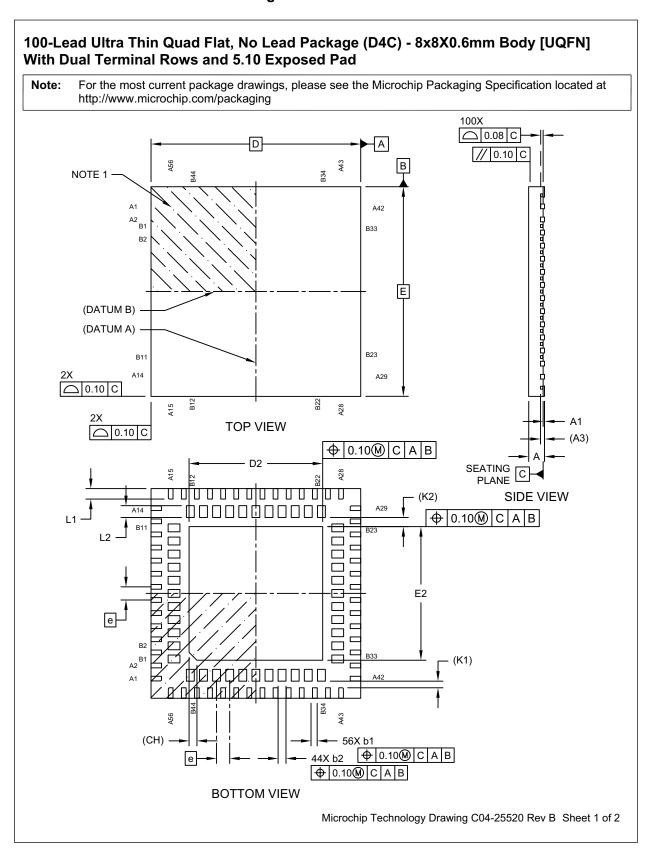

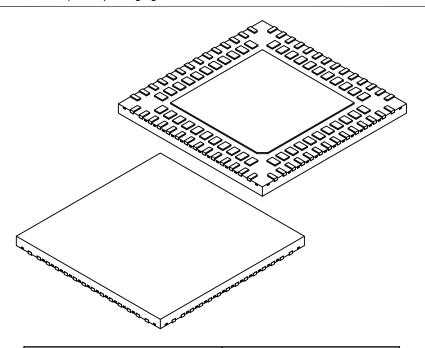

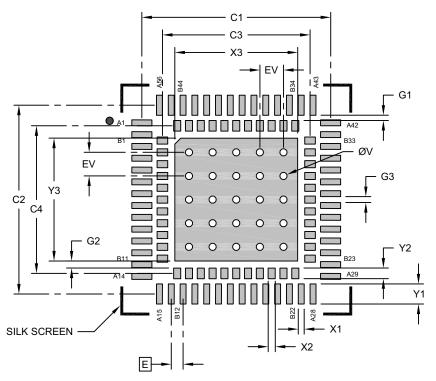

| 5.0 "Package Outline"                                        | 37  |

| 5.1 "Package Marking Information"                            |     |

| Appendix A: "Data Sheet Revision History"                    |     |

| "Product Identification System"                              |     |

### **List of Figures**

| FIGURE 0-1: "Functional Block Diagram."                                    | 1  |

|----------------------------------------------------------------------------|----|

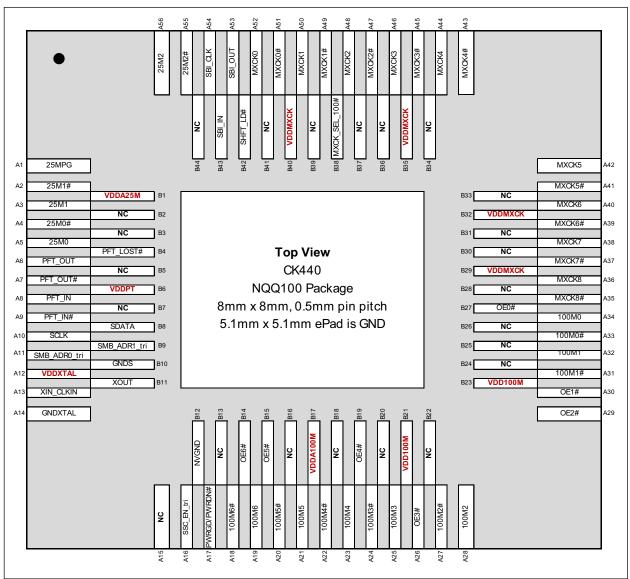

| FIGURE 1-1: "100-Lead 8 mm x 8 mm UQFN."                                   | 6  |

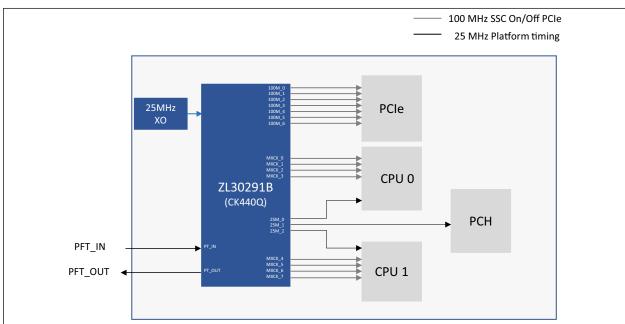

| FIGURE 2-1: "Server with Two CPUs."                                        | 11 |

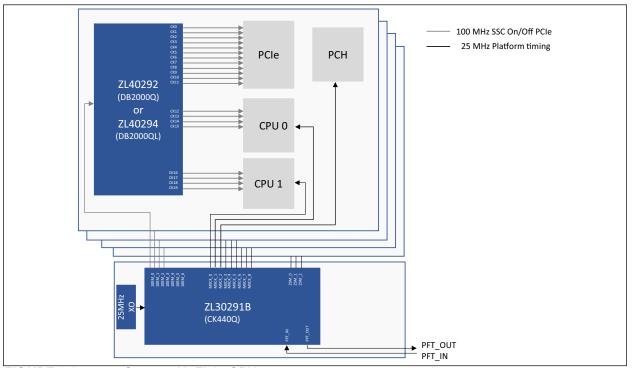

| FIGURE 2-2: "Server with Eight CPUs."                                      | 11 |

| FIGURE 2-3: "Input Driven by a Push-Pull Differential Output."             | 12 |

| FIGURE 2-4: "Input Driven by an HCSL Output."                              | 12 |

| FIGURE 2-5: "Input Driven by a Single-Ended Output."                       | 13 |

| FIGURE 2-6: "Terminating Differential Outputs."                            | 13 |

| FIGURE 2-7: "PWRDN# Assertion."                                            | 15 |

| FIGURE 2-8: "PWRGD and VDD Relationship Diagram."                          | 16 |

| FIGURE 2-9: "PWRGD Assertion."                                             |    |

| FIGURE 2-10: "SMBus Byte Read."                                            | 17 |

| FIGURE 2-11: "SMBus Byte Write."                                           | 17 |

| FIGURE 2-12: "SMBus Block Read."                                           | 17 |

| FIGURE 2-13: "SMBus Block Write."                                          | 18 |

| FIGURE 2-14: "Side-Band Interface Control Logic - Functional Description." | 19 |

| FIGURE 2-15: "Output Enable Logic (per Output)."                           | 19 |

| FIGURE 2-16: "Side-Band Shift Order."                                      | 20 |

| FIGURE 2-17: "Star SBI Topology for CK440Q."                               | 20 |

| FIGURE 2-18: "Daisy-Chain SBI Topology for CK440Q."                        | 21 |

| FIGURE 2-19: "Side-Band Interface Functional Timing."                      |    |

| FIGURE 2-20: "Frequency Lock."                                             |    |

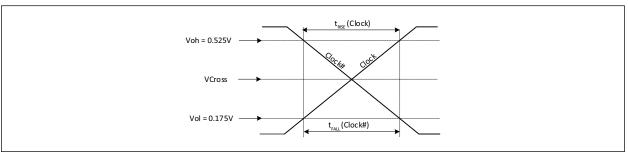

| FIGURE 4-1: "DC Test Load (in Accordance with CK440Q Specification)."      | 30 |

| FIGURE 4-2: "Single-Ended Measurement Points from tRISE and tFALL."        | 31 |

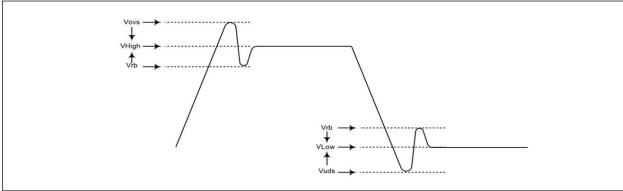

| FIGURE 4-3: "Single-Ended Measurement Points for VOVS, VUDS, VRB."         | 31 |

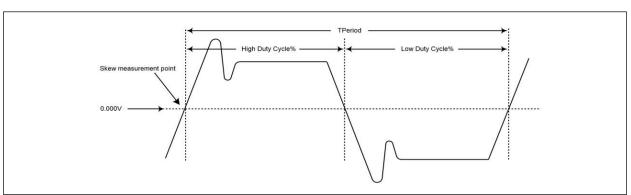

| FIGURE 4-4: "Differential Output Clock Measurement Points."                | 31 |

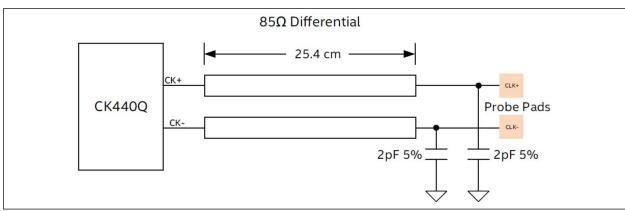

| FIGURE 4-5: "AC Test Load (in Accordance with CK440Q Specification)."      | 31 |

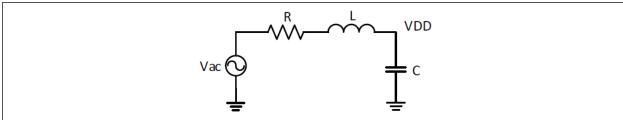

| FIGURE 4-6: "Simulation Model."                                            | 33 |

| FIGURE 4-7: "Power Noise Transfer Function."                               | 33 |

| FIGURE 4-8: "SMBus Timing."                                                | 35 |

| FIGURE 4-9: "Side-Band Interface Timing "                                  | 36 |

### **List of Tables**

| TABLE 1-1: "Pin Descriptions"                                                          | 7  |

|----------------------------------------------------------------------------------------|----|

| TABLE 2-1: "OE Functionality for 100M[6:0] Outputs"                                    | 14 |

| TABLE 2-2: "OE Functionality for 25M[2:0] and MXCK[8:0] Outputs"                       | 14 |

| TABLE 2-3: "25MPG PWRGD/PWRDN# Functionality"                                          | 15 |

| TABLE 2-4: "SMBus Address Table"                                                       |    |

| TABLE 2-5: "Platform Time Timing Parameters"                                           | 22 |

| TABLE 3-1: "Byte 0: Output Enable Control Register 0"                                  | 23 |

| TABLE 3-2: "Byte 1: Output Enable Control Register 1"                                  | 23 |

| TABLE 3-3: "Byte 2: Output Enable Control Register 2"                                  | 23 |

| TABLE 3-4: "Byte 3: PFT Control Register"                                              | 24 |

| TABLE 3-5: "Byte 4: PFT Frequency Delta Register 0 (least Significant Byte)"           | 24 |

| TABLE 3-6: "Byte 5: PFT Frequency Delta Register 1 (Most Significant Byte)"            | 24 |

| TABLE 3-7: "Byte 6: SSC PLL Control Register"                                          | 25 |

| TABLE 3-8: "Byte 7: OE# Realtime ReadBack Control Register"                            | 25 |

| TABLE 3-9: "Byte 8: Vendor/Revision Identification Control Register"                   | 26 |

| TABLE 3-10: "Byte 9: Device ID Control Register"                                       | 26 |

| TABLE 3-11: "Byte 10: Byte Count Register"                                             | 26 |

| TABLE 3-12: "Byte 11: Side-Band Interface Mask Register 0"                             |    |

| TABLE 3-13: "Byte 12: Side-Band Interface Mask Register 1"                             | 27 |

| TABLE 3-14: "Byte 13: Side-Band Interface Mask Register 2"                             | 27 |

| TABLE 3-15: "Byte 14: Side-Band Interface Readback Register 0"                         | 28 |

| TABLE 3-16: "Byte 15: Side-Band Interface Readback Register 1"                         |    |

| TABLE 3-17: "Byte 16: Side-Band Interface Readback Register 2"                         | 28 |

| TABLE 4-1: "Absolute Maximum Ratings"                                                  | 29 |

| TABLE 4-2: "DC Operating Characteristics"                                              | 29 |

| TABLE 4-3: "Differential DC Output Characteristics"                                    | 30 |

| TABLE 4-4: "Differential Output Clock AC Characteristics"                              | 32 |

| TABLE 4-5: "Differential Input Clock AC Characteristics (PFT_IN/PFT_IN#)"#             | 32 |

| TABLE 4-6: "Current Consumption"                                                       | 32 |

| TABLE 4-7: "Skew and Jitter"                                                           |    |

| TABLE 4-8: "Power Noise Tolerance: TA = -40 to +85°C; Supply Voltage VDD = 3.3 V ±10%" |    |

| TABLE 4-9: "SMBus Electrical Characteristics"                                          | 34 |

| TABLE 4-10: "Side-Band Interface Electrical Characteristics"                           | 35 |

| TABLE 4-11: "8 mm x 8 mm UQFN Package Thermal Properties"                              | 36 |

#### 1.0 PIN DESCRIPTION AND CONFIGURATION

**FIGURE 1-1:** 100-Lead 8 mm x 8 mm UQFN.

The I/O column uses the following symbols: I – input, IPDT – Input power down tolerant (must tolerate being driven by external signal while the device is powered down) O – output, ODPDT – open-drain power down tolerant output with internal 120 k $\Omega$  pull-up resistor, I/OD – Input/Output Open-Drain pin, PD1 (45 k $\Omega$ ), PD2 (120 k $\Omega$ ) – Pull-down resistor, PU1 (45 k $\Omega$ ), PU2 (120 k $\Omega$ ) – Pull-up resistor, NC – No connect pin, P – power supply pin, ITRI – Tri-level input pin.

TABLE 1-1: PIN DESCRIPTIONS

| IADLE 1-1.    | FIN DESCRIP           | 110110 |                                                                                                                                                                                  |  |  |

|---------------|-----------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Pin<br>Number | Pin Name              | I/O    | Description                                                                                                                                                                      |  |  |

| Crystal Osc   | illator, Input XO Clo | ck     |                                                                                                                                                                                  |  |  |

| A13           | XIN_CLKIN             | IPDT   | Passive crystal in/out or active CMOS single-ended input for XO                                                                                                                  |  |  |

| B11           | XOUT                  | 0      | Input frequency 25 MHz. Leave XOUT unconnected when XIN_CLKIN is connected to a crystal oscillator.  Please refer to ZLAN-825 for recommendations on Crystal Oscillator Circuit. |  |  |

| 100 MHz Ou    | tput Clocks           |        |                                                                                                                                                                                  |  |  |

| A34           | 100M0                 |        |                                                                                                                                                                                  |  |  |

| A33           | 100M0#                |        |                                                                                                                                                                                  |  |  |

| A32           | 100M1                 |        |                                                                                                                                                                                  |  |  |

| A31           | 100M1#                |        |                                                                                                                                                                                  |  |  |

| A28           | 100M2                 |        |                                                                                                                                                                                  |  |  |

| A27           | 100M2#                |        | 100 MHz Differential Outputs 0 to 6                                                                                                                                              |  |  |

| A25           | 100M3                 | 0      |                                                                                                                                                                                  |  |  |

| A24           | 100M3#                |        | 100 MITZ Differential Outputs 0 to 6                                                                                                                                             |  |  |

| A23           | 100M4                 |        |                                                                                                                                                                                  |  |  |

| A22           | 100M4#                |        |                                                                                                                                                                                  |  |  |

| A21           | 100M5                 |        |                                                                                                                                                                                  |  |  |

| A20           | 100M5#                |        |                                                                                                                                                                                  |  |  |

| A19           | 100M6                 |        |                                                                                                                                                                                  |  |  |

| A18           | 100M6#                |        |                                                                                                                                                                                  |  |  |

| 25 MHz Out    | put Clock             |        |                                                                                                                                                                                  |  |  |

| A5            | 25M0                  |        |                                                                                                                                                                                  |  |  |

| A4            | 25M0#                 |        |                                                                                                                                                                                  |  |  |

| A3            | 25M1                  | 0      | 25 MHz Differential Outputs 0 to 2                                                                                                                                               |  |  |

| A2            | 25M1#                 |        | 25 mm 2 2 moronium outputo o to 2                                                                                                                                                |  |  |

| A56           | 25M2                  |        |                                                                                                                                                                                  |  |  |

| A55           | 25M2#                 |        |                                                                                                                                                                                  |  |  |

TABLE 1-1: PIN DESCRIPTIONS (CONTINUED)

| Pin<br>Number | Pin Name            | 1/0          | Description                                                                                                                      |                                                                              |  |  |  |

|---------------|---------------------|--------------|----------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|--|--|--|

| 100 MHz or    | 25 MHz (Selectable) |              |                                                                                                                                  |                                                                              |  |  |  |

| A52           | MXCK0               |              |                                                                                                                                  |                                                                              |  |  |  |

| A51           | MXCK0#              |              |                                                                                                                                  |                                                                              |  |  |  |

| A50           | MXCK1               |              |                                                                                                                                  |                                                                              |  |  |  |

| A49           | MXCK1#              |              |                                                                                                                                  |                                                                              |  |  |  |

| A48           | MXCK2               |              |                                                                                                                                  |                                                                              |  |  |  |

| A47           | MXCK2#              |              |                                                                                                                                  |                                                                              |  |  |  |

| A46           | MXCK3               |              |                                                                                                                                  |                                                                              |  |  |  |

| A45           | MXCK3#              |              |                                                                                                                                  |                                                                              |  |  |  |

| A44           | MXCK4               | 0            | 100 MUz or 25 MUz (C                                                                                                             | alactable) Differential Outputs 0 to 9                                       |  |  |  |

| A43           | MXCK4#              |              | 100 MINZ OF 25 MINZ (5                                                                                                           | electable) Differential Outputs 0 to 8                                       |  |  |  |

| A42           | MXCK5               |              |                                                                                                                                  |                                                                              |  |  |  |

| A41           | MXCK5#              |              |                                                                                                                                  |                                                                              |  |  |  |

| A40           | MXCK6               |              |                                                                                                                                  |                                                                              |  |  |  |

| A39           | MXCK6#              | ,            | 1                                                                                                                                |                                                                              |  |  |  |

| A38           | MXCK7               |              |                                                                                                                                  |                                                                              |  |  |  |

| A37           | MXCK7#              |              |                                                                                                                                  |                                                                              |  |  |  |

| A36           | MXCK8               |              |                                                                                                                                  |                                                                              |  |  |  |

| A35           | MXCK8#              |              |                                                                                                                                  |                                                                              |  |  |  |

| Platform Tir  | ming                | •            |                                                                                                                                  |                                                                              |  |  |  |

| A8            | PFT_IN              |              | 25 MHz Differential Pla                                                                                                          |                                                                              |  |  |  |

| A9            | PFT_IN#             | IPDT         | PFT_IN is pulled down v<br>50 kΩ to ~500 mV. Lear                                                                                | with 50 k $\Omega$ to ground and PFT_IN# pulled up with we open if not used. |  |  |  |

| A6            | PFT_OUT             | 0            | 25 MHz Differential Pla                                                                                                          | otform Timing Output                                                         |  |  |  |

| A7            | PFT_OUT#            |              | 25 Winz Differential Pic                                                                                                         | ationin filming Output                                                       |  |  |  |

| B4            | PFT_LOST#           | ODPDT        | This output is asserte 10 kΩ resistor.                                                                                           | d when PFT_IN is lost. If used, pull up with                                 |  |  |  |

| Hardware C    | ontrol              |              |                                                                                                                                  |                                                                              |  |  |  |

| B27           | OE0#                |              |                                                                                                                                  |                                                                              |  |  |  |

| A30           | OE1#                |              | Output Enable for 100                                                                                                            | M Outputs.                                                                   |  |  |  |

| A29           | OE2#                | IDDT         | Logic level on these pin                                                                                                         | s enables/disables the corresponding output.                                 |  |  |  |

| A26           | OE3#                | IPDT,<br>PD1 |                                                                                                                                  |                                                                              |  |  |  |

| B19           | OE4#                | ] . 5.       | OE_n#                                                                                                                            | 100Mn/n#                                                                     |  |  |  |

| B15           | OE5#                |              | 0                                                                                                                                | Active                                                                       |  |  |  |

| B14           | OE6#                |              | 1                                                                                                                                | Low/Low both pulled low by 42.5Ω resistor                                    |  |  |  |

| B38           | MXCK_SEL_100#       | IPDT,<br>PD1 |                                                                                                                                  |                                                                              |  |  |  |

| A1            | 25MPG               | IPDT,<br>PD1 | <b>25M2/25M2# Enable for Platform Boot.</b> When this pin is pulled high 25M2/25M2# will stay active while PWRDN# is pulled low. |                                                                              |  |  |  |

TABLE 1-1: PIN DESCRIPTIONS (CONTINUED)

| Pin<br>Number | Pin Name      | 1/0          | Description                                                                                                                                               |                                                          |  |  |

|---------------|---------------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|--|--|

| A17           | PWRGD/PWRDN#  | I, PU1       | Power up/Power down. Refer to section PWRGD/PWRDN# for details.                                                                                           |                                                          |  |  |

|               |               |              | Tri-level Spread Spect                                                                                                                                    | rum Control                                              |  |  |

|               |               |              | SSC_ENABLE Pin SSC Modulation 0 Off                                                                                                                       |                                                          |  |  |

| A16           | SSC_En_tri    | ITRI,<br>PD2 |                                                                                                                                                           |                                                          |  |  |

|               |               | 1 02         | MID                                                                                                                                                       | -0.3%                                                    |  |  |

|               |               |              | HIGH -0.5%                                                                                                                                                |                                                          |  |  |

| SMBus Con     | trol          |              |                                                                                                                                                           |                                                          |  |  |

| A10           | SCLK          | IPDT         | SMBus Client Clock Ir ground, if not used.                                                                                                                | <b>nput.</b> Pull down with 10 kΩ resistor or connect to |  |  |

| В8            | SDATA         | IPDT/<br>OD  | Input/Open-Drain SME                                                                                                                                      | Bus Data. Pull up as per SMBUS specification.            |  |  |

| A11           | SMB_ADDR0_tri | ITRI,        | Tri-level Address Sele                                                                                                                                    |                                                          |  |  |

| В9            | SMB_ADDR1_tri | PD2,<br>PU2  | (Please refer to address Table 4-2)                                                                                                                       | ses in Table 2-4 and tri-level thresholds in             |  |  |

| Side Band I   | nterface      |              |                                                                                                                                                           |                                                          |  |  |

| B43           | SBI_IN        | IPDT,<br>PD1 | Side Band Interface D                                                                                                                                     | ata.                                                     |  |  |

| A54           | SBI_CLK       | IPDT,<br>PD1 | Side Band Interface C                                                                                                                                     | lock.                                                    |  |  |

| B42           | SHFT_LD#      | IPDT,<br>PD1 | Side Band Shift Register Load When this pin gets pulled low, the values stored in shift register get loaded to 20-bit SBI Output Enable Control Register. |                                                          |  |  |

| A53           | SBI_OUT       | 0            | Side Band Interface Output. Leave unconnected if not used.                                                                                                |                                                          |  |  |

| Power and     | Ground        |              |                                                                                                                                                           |                                                          |  |  |

| B29           |               |              |                                                                                                                                                           |                                                          |  |  |

| B32           | VDDMXCK       | Р            | Positive Supply Voltag                                                                                                                                    |                                                          |  |  |

| B35           | VBBINIXOIX    | •            | Connect to 3.3V supply.                                                                                                                                   |                                                          |  |  |

| B40           |               |              |                                                                                                                                                           |                                                          |  |  |

| B21           | VDD100M       | Р            | Positive Supply Voltage                                                                                                                                   |                                                          |  |  |

| B23           |               |              | Connect to 3.3V supply.                                                                                                                                   |                                                          |  |  |

| B17           | VDDA100M      | Р            | Positive Analog Supple<br>Connect to 3.3V supply                                                                                                          | .7                                                       |  |  |

| B6            | VDDPT         | Р            | Positive Supply Voltage<br>Connect 3.3V power su                                                                                                          | ge for Platform Timing<br>pply                           |  |  |

| B1            | VDDA25        | Р            | Positive Analog Suppl<br>Connect 3.3V power su                                                                                                            |                                                          |  |  |

| A12           | VDDXTAL       | Р            | Positive Supply Voltage for Crystal Oscillator Circuit Connect 3.3V power supply                                                                          |                                                          |  |  |

| A14           | GNDXTAL       | Р            | Ground for XTAL oscillator Connect to ground                                                                                                              |                                                          |  |  |

| B10           | GNDS          | Р            | Ground Connect to ground                                                                                                                                  |                                                          |  |  |

| B12           | NVGND         | Р            | Ground Connect to ground                                                                                                                                  |                                                          |  |  |

| ePad          | GND           | Р            | Ground. Connect to ground                                                                                                                                 |                                                          |  |  |

## **ZL30291B**

TABLE 1-1: PIN DESCRIPTIONS (CONTINUED)

| IADLL I-I.                                                                                                                                                | I III DEGGI | , ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | CONTINUED)                                                            |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-----------------------------------------|-----------------------------------------------------------------------|

| Pin<br>Number                                                                                                                                             | Pin Name    | I/O                                     | Description                                                           |

| No Connect                                                                                                                                                | Pins        |                                         |                                                                       |

| A15<br>B2<br>B3<br>B5<br>B7<br>B13<br>B16<br>B18<br>B20<br>B22<br>B24<br>B25<br>B26<br>B28<br>B30<br>B31<br>B33<br>B34<br>B36<br>B37<br>B39<br>B41<br>B44 | NC          | NC                                      | No Connect. These pins are not connected to the die. Leave them open. |

#### 2.0 FUNCTIONAL DESCRIPTION

#### 2.1 Applications

ZL30291B is a clock generator/synchronizer that is fully compliant with Intel CK440Q specification and PCIe Gen 1/2/3/4/5/6. Intel CK440Q defines requirements for a timing device to be used in server applications with Intel CPUs. ZL30291B provides a complete clock solution for PCIe and the platform timing. The following figures show typical applications. For larger servers (typically more than two CPUs) ZL30291B(CK440Q) will be used in conjunction with ZL40292/294 (DB2000Q/QL) clock buffers.

FIGURE 2-1: Server with Two CPUs.

FIGURE 2-2: Server with Eight CPUs.

#### 2.2 Functional Description

The ZL30291B is an ultra-low jitter, low power clock generator that is fully compliant with Intel CK440Q Standard.

The device can operate from  $3.3V\pm10\%$  supply to meet PCIe Electromechanical Specification that requires 3.3V supply tolerance of  $\pm9\%$ . Its operation is ensured over the industrial temperature range of -40°C to +85°C.

#### 2.3 Platform Timing Clock Input

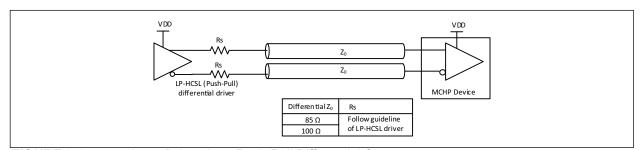

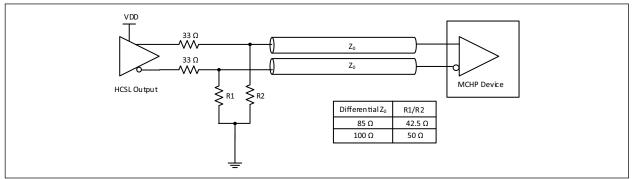

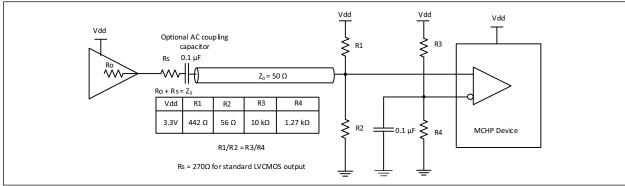

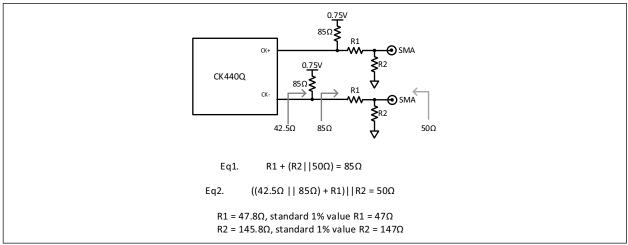

The following block diagrams show how to terminate different signals fed to the ZL30291B inputs.

The platform timing input (PFT\_IN) can be fed with transmission lines of any impedance. The examples below show only  $50\Omega$  single-ended,  $85\Omega$  differential, and  $100\Omega$  differential, which are the most common ones in practice. Figure 2-3 and Figure 2-4 show how to terminate the input when driven from a push-pull and traditional HCSL drivers respectively.

Figure 2-5 shows how to terminate a single-ended output, such as LVCMOS. This example assumes  $50\Omega$  transmission line, which is the most common for single-ended LVCMOS signaling. Resistors R1 and R2 are chosen to provide  $50\Omega$  termination and proper biasing and  $R_O + R_S$  ideally should be  $50\Omega$  so that the transmission line is terminated at both ends with its characteristic impedance. If the driving strength of the output driver is not sufficient to drive low impedance, the value of series resistor  $R_S$  should be increased. This will reduce the voltage swing at the input but this should be fine as long as the input voltage swing requirement is not violated (Figure 2-5). The source resistors of  $R_S = 270\Omega$  could be used for a standard LVCMOS driver. This will provide 516 mV of voltage swing for 3.3V LVCMOS driver with load current of  $(3.3V/2) * (1/(270\Omega + 50\Omega)) = 5.16$  mA. If the strength of output driver is sufficient to support voltage swing above 750 mV, then the biasing voltage determined with R1, R2, R3, and R4 resistors needs to be increased to avoid signal going below 0 volts.

For optimum performance both differential input pins (\_p and \_n) need to be DC biased to the same voltage. Hence, the ratio R1/R2 should be equal to the ratio R3/R4.

FIGURE 2-3: Input Driven by a Push-Pull Differential Output.

FIGURE 2-4: Input Driven by an HCSL Output.

FIGURE 2-5: Input Driven by a Single-Ended Output.

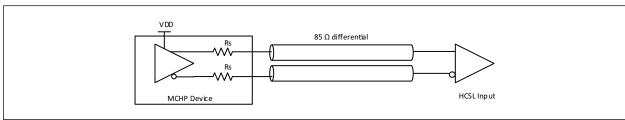

#### 2.4 Clock Outputs

Differential outputs have embedded termination resistors as shown in Figure 2-6. This provides significant saving relative to traditional current based HCSL outputs which require four resistors per differential pair.

Embedded series termination resistors are matched for  $85\Omega$  differential transmission line.

FIGURE 2-6: Terminating Differential Outputs.

#### 2.5 Termination of Unused Outputs

Unused outputs should be left unconnected.

#### 2.6 OE# and Output Enables (Control Register)

The ZL30291B has three methods for enabling and disabling outputs. In order for an output to be enabled, all three methods must enable the output. If any method disables the output, the output will be disabled.

The first is the traditional method of OE# pins that are used for PCI Express clock enabling at the PCIe connector. Each of the 7 dedicated 100 MHz clock outputs can be enabled or disabled with the OE[6:0]# pins individually. The OE# pin must be pulled low to enable the output.

The second method is by using the SMBus output enable bits. Any of the 19 outputs have dedicated SMBus output enable bits in Bytes[0:2] of the SMBus register set that can enable or disable the clock outputs. The Output Enable bits in the SMBus registers are active high and are set to enable by default.

The third is using the Side Band Interface (SBI). This is a DB2000QL compatible method of enabling outputs using a hardware shift/load method.

Refer to Table 2-1 for the truth table for enabling and disabling 100M outputs via hardware and software. In addition to the PWRGD/PWRDN# pin, all three output enabling methods must be set to "enable" for the clock to be active on that pin.

Refer to Table 2-2 for the truth table for enabling and disabling MXCK or 25M or PFT\_OUT outputs via software. In addition to the PWRGD/PWRDN# pin, both the SMBus method and SBI method must be set to "enable" for the clock to be active on that pin.

Clocks always start and stop in a glitch free manner, meaning duty cycle requirements are still met.

TABLE 2-1: OE FUNCTIONALITY FOR 100M[6:0] OUTPUTS

| Inputs           | OE# Hardware Pins,<br>Control Register Bits, and SBI |   |   |          |  |  |

|------------------|------------------------------------------------------|---|---|----------|--|--|

| PWRGD/<br>PWRDN# | OE# Pin SBI SMBus 100M[6:0] 100M[6:0]#               |   |   |          |  |  |

| 0                | X                                                    | Х | X | Disabled |  |  |

|                  | 0                                                    | 1 | 1 | Running  |  |  |

| 4                | 1                                                    | X | X | Disabled |  |  |

| '                | X                                                    | 0 | X | Disabled |  |  |

|                  | X                                                    | Х | 0 | Disabled |  |  |

TABLE 2-2: OE FUNCTIONALITY FOR 25M[2:0] AND MXCK[8:0] OUTPUTS

| Inputs           | PFT_OU | PFT_OUT, OE Control Register Bits, and SBI                     |          |  |  |  |

|------------------|--------|----------------------------------------------------------------|----------|--|--|--|

| PWRGD/<br>PWRDN# | SBI    | PFT_OUT/PFT_OUT#<br>25M[2:0]/25M[2:0]#<br>MXCK[8:0]/MXCK[8:0]# |          |  |  |  |

| 0                | X      | X                                                              | Disabled |  |  |  |

|                  | 1      | 1                                                              | Running  |  |  |  |

| 1                | 0      | X                                                              | Disabled |  |  |  |

|                  | X      | 0                                                              | Disabled |  |  |  |

#### 2.7 OE[6:0]# Assertion (Transition from '1' to '0')

All differential outputs that were disabled are to resume normal operation in a glitch free manner. The latency from the assertion to active outputs is 0 to 10 CK (differential output) clock periods.

#### 2.8 OE[6:0]# De-Assertion (Transition from '0' to '1')

The impact of de-asserting OE# is each corresponding output will transition from normal operation to disabled in a glitch free manner. A minimum of four valid clocks will be provided after the de-assertion of OE#. The maximum latency from the de-assertion to disabled outputs is 10 CK clock periods.

#### 2.9 25MPG

The 25MPG pin enables output 25M[2]/25M[2]# while the rest of the chip is still in reset. The pin shall not be asserted before  $V_{DD}$  reaches  $V_{DD(MIN)}$ . Prior to the power supply reaching  $V_{DD(MIN)}$ , 25MPG must be held low (less than 0.5V) De-assertion of 25MPG does not gate 25M[2]/25M[2]# outputs if PWRGD is asserted. Essentially PWRGD/PWRDN# and 25MPG are OR-ed and this signal is used as a glitchless Output Enable of 25M[2]/25M[2]# output.

TABLE 2-3: 25MPG PWRGD/PWRDN# FUNCTIONALITY

| PWRGD/PWRDN# | 25MPG | 25M2 OE bit in Byte 2 | 25M[2]/25M[2]#  |

|--------------|-------|-----------------------|-----------------|

| 0            | 0     | 1                     | Disabled        |

| X            | 1     | 1                     | Running         |

| 1            | 0     | 1                     | Running, Note 1 |

| X            | X     | 0                     | Disabled        |

Note 1: Refer to next section for details on PWRGD/PWRDN# operation.

#### 2.10 PWRGD/PWRDN#

PWRGD is asserted high and deasserted low. Deassertion of PWRGD (pulling the signal low) is equivalent to indicating a power-down condition. PWRGD (assertion) is used by the ZL30291B to sample initial configurations such as SMB ADR0 tri, SMB ADR1 tri, SSC EN tri, and MXCK SEL 100# selections.

After PWRGD has been asserted high for the first time, the pin becomes a PWRDN# (Power Down) pin, which is used to disable (drive low/low) all clocks cleanly and instruct the device to invoke power savings mode. PWRDN# is a completely asynchronous active-low input. When entering power savings mode, PWRDN# should be asserted low prior to shutting off the input clock or power to ensure all clocks shut down in a glitch free manner. When PWRDN# is deasserted high, all clocks will start and stop without any abnormal behavior and will meet all AC and DC parameters.

The assertion and de-assertion of PWRDN# is asynchronous. Refer to Table 2-1, Table 2-2, and Table 2-3 for details on PWRGD/PWRDN# functionality.

#### 2.11 PWRDN# Assertion

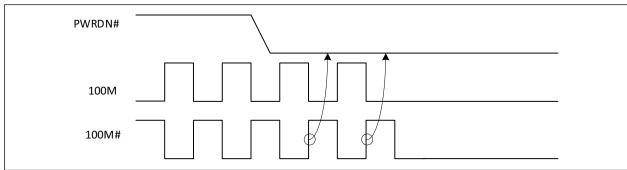

When PWRDN# is sampled low by two consecutive rising edges of CK#, all differential outputs will be disabled on the next CK# high to low transition. It is possible that PWRDN# transition occurs right after the rising edge of 100M clock because PWRDN# transition is asynchronous with 100M clock. In this case it will take up to three clock cycles to disable the outputs.

FIGURE 2-7: PWRDN# Assertion.

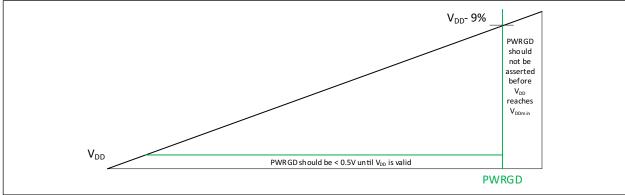

#### 2.12 PWRGD Assertion

PWRGD to the clock buffer should not be asserted before  $V_{DD}$  reaches  $V_{DD(MIN)}$  = 3.3V – 9%. Prior to  $V_{DD(MIN)}$ , it is recommended to hold PWRGD low (less than 0.5V).

FIGURE 2-8: PWRGD and V<sub>DD</sub> Relationship Diagram.

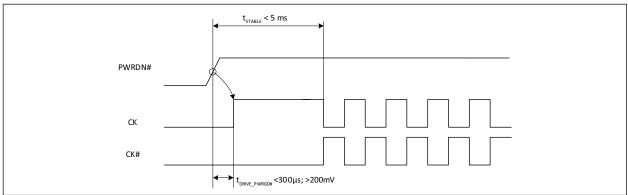

The power-up latency  $t_{\text{STABLE}}$  is to be less than 5 ms. This is the time from the assertion of the PWRGD signal to the time that stable clocks are output from the buffer chip. All differential outputs that are stopped in a Low/Low condition resulting from power down must be driven to high/low differential output in less than 300  $\mu$ s of PWRGD assertion to a voltage greater than 200 mV.

FIGURE 2-9: PWRGD Assertion.

#### 2.13 SMB\_ADR0\_tri, SMB\_ADR1\_tri - Address Selection

SMB\_ADR0\_tri and SMB\_ADR1\_tri are tri-level hardware pins, which program the appropriate address for the ZL30291B. The two tri-level input pins can configure the ZL30291B to nine different addresses as indicated in Table 2-4 (refer to Table 3-16 for VIL\_tri, VIM\_tri, VIH\_tri signal level).

TABLE 2-4: SMBUS ADDRESS TABLE

| SMBUS_ADR1_tri | SMBUS_ADR0_tri | SMBus Address |

|----------------|----------------|---------------|

| L              | L              | D2            |

| L              | M              | D4            |

| L              | Н              | D6            |

| M              | L              | B2            |

| M              | M              | B4            |

| M              | Н              | B6            |

| Н              | L              | BA            |

| Н              | M              | BC            |

| Н              | Н              | BE            |

#### 2.14 SMBus Byte Read/Write

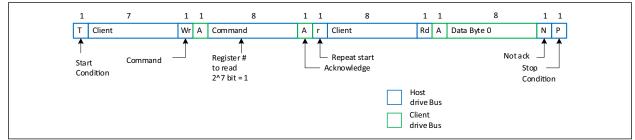

Reading or writing a register in a SMBus client device in byte mode always involves specifying the register number.

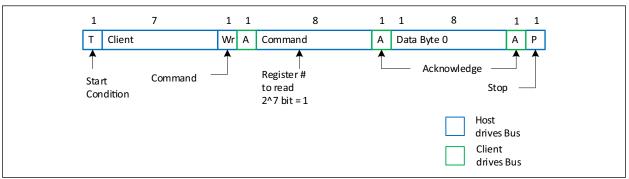

**Read.** The standard byte read is as shown in Figure 2-10. It is an extension of the byte write. The write start condition is repeated then the client device starts sending data and the server acknowledges it until the last byte is sent. The server terminates the transfer with a NAK then a stop condition. For byte operation, the 2^7th bit of the command byte must be set. For block operations, the 2^7th bit must be reset. If the bit is not set, the next byte must be the byte transfer count.

FIGURE 2-10: SMBus Byte Read.

Write. Figure 2-11 illustrates a simple typical byte write. For byte operation the 2^7th bit of the command byte must be set.

FIGURE 2-11: SMBus Byte Write.

#### 2.15 SMBus Block Read/Write

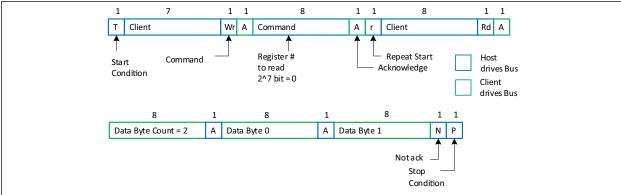

For block operations, the 2^7th bit must be reset. If the bit is not set the next byte must be the byte transfer count. The count can be between 1 and 32. It cannot be zero or exceed 32.

**Read.** After the client address is sent with the R/W condition bit set, the command byte is sent with the MSB = 0. The client Ack's the register index in the command byte. The server sends a repeat start function. After the client Ack's this the client sends the number of bytes. The server Ack's each byte except the last and sends a stop function.

FIGURE 2-12: SMBus Block Read.

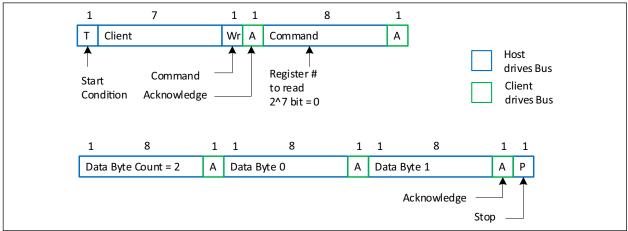

Write. After the client address is sent with the R/W condition bit not set, the command byte is sent with the MSB = 0. The lower seven bits indicate what register to start the transfer at. If the command byte is 00h, the client device will be compatible with existing block mode client devices. The next byte of a write must be the count of bytes that the server will transfer to the client device. The byte count must be greater than zero and less than 33. Following this byte are the data bytes to be transferred to the client device. The client device always acknowledges each byte received. The transfer is terminated after the client sends the Ack and the server sends a stop function.

FIGURE 2-13: SMBus Block Write.

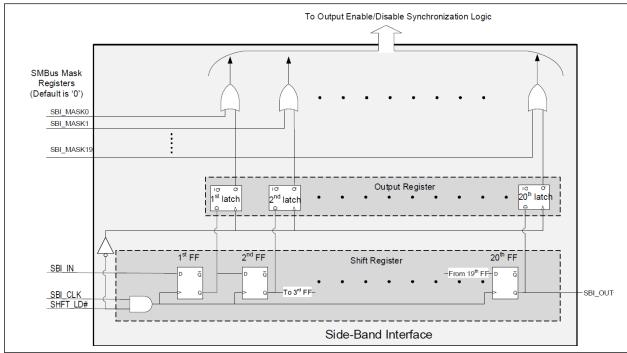

#### 2.16 Programming via Side-Band Interface

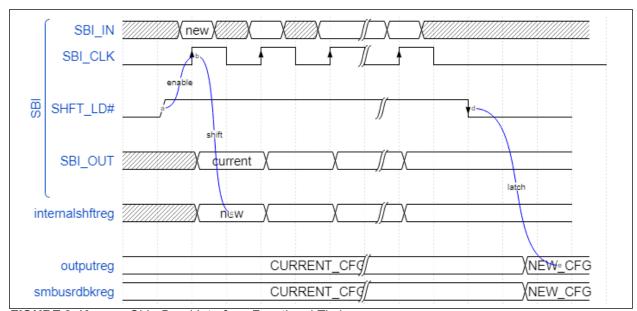

The third output enable/disable method is a simple serial interface referred to as the Side-Band Interface (SBI). In the DB2000QL, this is a 3-wire interface consisting of SBI\_DATA (input), SBI\_CLK, and SHFT\_LD# pins. The CK440Q adds an additional pin: SBI\_OUT. This output is the last stage of the internal 20-bit shift register. The SBI\_DATA pin is renamed to SBI\_IN. When the SHFT\_LD# pin is high, the rising edge of SBI\_CLK can shift DATA into the shift register. After shifting data, the falling edge of SHFT\_LD# loads the shift register contents to the output control register.

Both the SBI and the traditional interface feed common output enable/disable synchronization logic ensuring glitch free enable and disable of outputs, regardless of the method used.

Because the CK440Q has dedicated pins for the SBI, both SBI and the traditional SMBus methods are active at the same time. There are SMBus registers for masking off the disable function of the SBI interface. When set to a one, the mask register forces the SBI for its respective output to indicate 'enabled'. This prevents accidentally disabling critical outputs when using the SBI. Remember that the traditional SMBus enable bits and the OE# pins may still disable an output.

If the application does not use the SBI, the SBI input pins may be tied 'Low'. Figure 2-14 provides a high level functional description of the SBI.

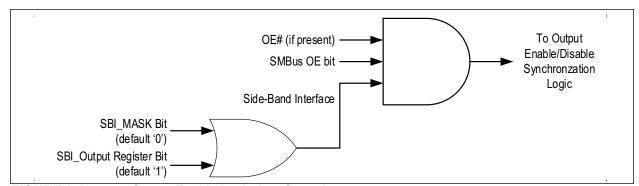

FIGURE 2-14: Side-Band Interface Control Logic – Functional Description.

#### 2.17 Output Enable/Disable Priority

The CK440Q outputs require that outputs be enabled by an 'AND' function of all methods of enabling the output. Figure 2-15 illustrates this. There are three enable/disable paths: OE# pin (if present), a SMBus OE bit, and the Side-Band Interface. All three must indicate 'enable' for the output to be enabled. Conversely, any single enable/disable path can disable an output if it indicates 'disable'.

FIGURE 2-15: Output Enable Logic (per Output).

A closer study of Figure 2-15 shows the following must be true to enable an output:

- · OE# pin (if present) must be 'low'

- · SMBus OE bit must be 'high'

- · Side-Band Interface must be 'high'

Additionally, one can see that the Side-Band Interface indicates a 'high' if the SBI\_Mask\_Bit OR the SBI\_Output Register Bit are 'high'. This means that the SBI\_MASK\_Bit can prevent the SBI interface from disabling an output. Note that the SBI\_MASK\_Bits are SMBus registers.

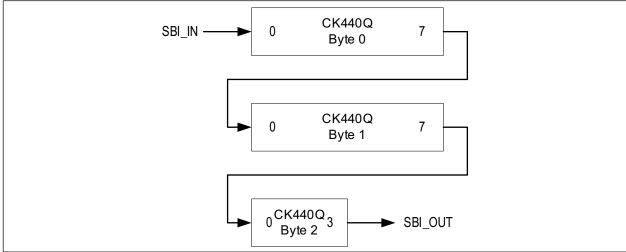

The shift order follows the order of the SMBus enable bits in Byte[2:0] as shown in Figure 2-16. The first bit shifted in would be the output enable for the PFT\_OUT, which is in Byte 2 bit 3. The last bit shifted in would be the output enable for 100M0, which is in Byte 0, bit 0.

FIGURE 2-16: Side-Band Shift Order.

The SMBus registers for the SBI Output and SBI\_Mask follow the same bit order. Note that the SBI Output register contains the value latched from the shift register. Software must apply the SBI Mask bits to this value to get the output of the Side-Band Interface OR gate in Figure 2-15.

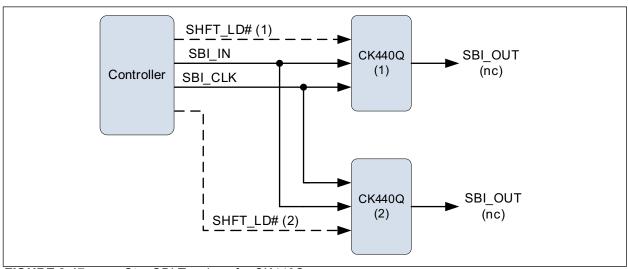

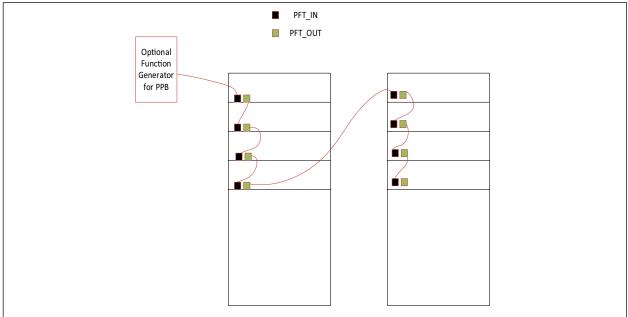

Figure 2-17 illustrates a star topology connection for the CK440Q SBI interface. The star topology allows independent configuration of each device. For CK440Q, this means shifting 20 bits at a time. A disadvantage is that a separate SHFT\_LD# pin is required for each device.

FIGURE 2-17: Star SBI Topology for CK440Q.

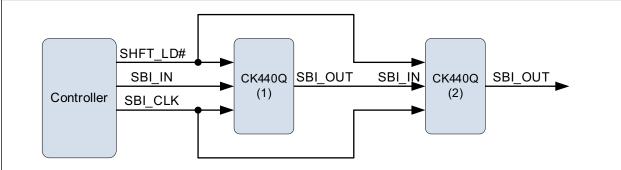

The daisy chain topology allows configuration of any number of devices with only three signals from the SBI controller. It utilizes the SBI\_OUT pin of one device to drive the SBI\_IN pin of the next device in the daisy chain. Users must take care to shift the proper number of bits in this configuration. For the example shown in Figure 2-18, the SBI bit stream consists of 40 bits.

FIGURE 2-18: Daisy-Chain SBI Topology for CK440Q.

#### 2.18 Side-Band Interface Functionality and Detailed Timing

Figure 2-19 shows the basic timing of the side-band interface. The SHFT\_LD# pin goes high to enable the SBI\_CLK input. Next, the rising edge of SBI\_CLK clocks SBI\_IN data into the shift register. After the 20th clock, stop the clock low and drive the SHFT\_LD# pin low. The falling edge of SHFT\_LD# latches the shift register contents to the output control register, enabling or disabling the outputs. Always shift 20 bits of data into the shift register to control the outputs.

FIGURE 2-19: Side-Band Interface Functional Timing.

The SBI interface supports clock rates up to 25 MHz. The CK440Q allows two SBI connection topologies: star and daisy chain. In a star topology, multiple devices may share SBI\_CLK and SBI\_IN pins. In this topology, each CK440Q has a dedicated SHFT\_LD# pin. In a daisy-chain topology, the SBI\_OUT of one device connects to the SBI\_IN device of a downstream device. When using the daisy chain topology, the user must shift a complete set of bits for the combined devices. Two daisy-chained CK440Q devices require shifting of 40 bits. When the SHFT\_LD# pin is low, the SBI interface ignores any activity on the SBI\_CLK and SBI\_IN pins.

#### 2.19 Platform Time (PFT) Phase/Frequency Tracking

PFT\_IN/OUT allows different CK440 devices to frequency lock the 25 MHz clocks to a single time base. The system implementation is shown in Figure 2-20.

FIGURE 2-20: Frequency Lock.

The local 25 MHz frequency locks to the PFT\_IN clock if it is present. If PFT\_IN is not present, the local 25 MHz frequency is sourced from the local crystal.

The output signal PFT\_LOST# asserts if the PFT\_IN clock is not present. If the PFT\_IN clock is lost during operation, PFT\_OUT and all other clocks are continued without timing glitches. If the PFT\_IN clock is applied during operation, the frequency lock occurs according to the PFT filter to ensure a glitchless output of PFT\_OUT.

PFT IN does not replace the need for the local crystal oscillator and may not be used as the oscillator source.

The signed PPM difference between the supplied PFT\_IN clock and the local crystal oscillator can be read in the SMBUS registers. The PPM difference is defined as the number of 1 ns steps that were required in the last 215 clocks, signed for direction.

The platform time tracking must be able to track ±125 ppm difference between the local clock and the PFT\_IN clock. The phase relationship between input PFT\_IN and PFT\_OUT is within (±4 ns). The PTO timing parameters are given in Table 2-5.

TABLE 2-5: PLATFORM TIME TIMING PARAMETERS

| Parameter      | Symbol              | Min. | Тур. | Max. | Units | Conditions   |

|----------------|---------------------|------|------|------|-------|--------------|

| PTO_OUT Period | t <sub>PERIOD</sub> | 38   | 40   | 42   | ns    | Clock period |

| PPM Tracking   | PFT_PPM             | ±125 | _    | _    | ppm   | _            |

#### 3.0 REGISTER MAP

**Note:** When differential outputs are disabled they drive low/low. For example, if 100M0 output is disabled, it will drive low on both 100M0 and 100M0# pins.

TABLE 3-1: BYTE 0: OUTPUT ENABLE CONTROL REGISTER 0

| Bit | Description         | If Bit = 0 | If Bit = 1 | Туре | Default | Output(s)<br>Affected |

|-----|---------------------|------------|------------|------|---------|-----------------------|

| 0   | Output Enable 100M0 | Disabled   | Enabled    | RW   | 1       | 100M0                 |

| 1   | Output Enable 100M1 | Disabled   | Enabled    | RW   | 1       | 100M1                 |

| 2   | Output Enable 100M2 | Disabled   | Enabled    | RW   | 1       | 100M2                 |

| 3   | Output Enable 100M3 | Disabled   | Enabled    | RW   | 1       | 100M3                 |

| 4   | Output Enable 100M4 | Disabled   | Enabled    | RW   | 1       | 100M4                 |

| 5   | Output Enable 100M5 | Disabled   | Enabled    | RW   | 1       | 100M5                 |

| 6   | Output Enable 100M6 | Disabled   | Enabled    | RW   | 1       | 100M6                 |

| 7   | Output Enable MXCK8 | Disabled   | Enabled    | RW   | 1       | MXCK8                 |

TABLE 3-2: BYTE 1: OUTPUT ENABLE CONTROL REGISTER 1

| Bit | Description         | If Bit = 0 | If Bit = 1 | Туре | Default | Output(s)<br>Affected |

|-----|---------------------|------------|------------|------|---------|-----------------------|

| 0   | Output Enable MXCK0 | Disabled   | Enabled    | RW   | 1       | MXCK0                 |

| 1   | Output Enable MXCK1 | Disabled   | Enabled    | RW   | 1       | MXCK1                 |

| 2   | Output Enable MXCK2 | Disabled   | Enabled    | RW   | 1       | MXCK2                 |

| 3   | Output Enable MXCK3 | Disabled   | Enabled    | RW   | 1       | MXCK3                 |

| 4   | Output Enable MXCK4 | Disabled   | Enabled    | RW   | 1       | MXCK4                 |

| 5   | Output Enable MXCK5 | Disabled   | Enabled    | RW   | 1       | MXCK5                 |

| 6   | Output Enable MXCK6 | Disabled   | Enabled    | RW   | 1       | MXCK6                 |

| 7   | Output Enable MXCK7 | Disabled   | Enabled    | RW   | 1       | MXCK7                 |

TABLE 3-3: BYTE 2: OUTPUT ENABLE CONTROL REGISTER 2

| Bit | Description                       | If Bit = 0          | If Bit = 1         | Туре | Default | Output(s)<br>Affected |

|-----|-----------------------------------|---------------------|--------------------|------|---------|-----------------------|

| 0   | Output Enable 25M0                | Disabled            | Enabled            | RW   | 1       | 25M0                  |

| 1   | Output Enable 25M1                | Disabled            | Enabled            | RW   | 1       | 25M1                  |

| 2   | Output Enable 25M2                | Disabled            | Enabled            | RW   | 1       | 25M2                  |

| 3   | Output Enable PFT_OUT             | Disabled            | Enabled            | RW   | 1       | PFT_OUT               |

| 4   | Reserved                          | _                   | _                  | _    | 0       | Reserved              |

| 5   | Realtime Readback of MXCK_SEL pin | 100 MHz<br>Selected | 25 MHz<br>Selected | R    | 0       | MXCK[8:0]             |

| 6   | MXCK_SEL Control (Note 1)         | Pin Control         | Register Control   | RW   | 0       | MXCK[8:0]             |

| 7   | MXCK_SEL                          | 100 MHz             | 25 MHz             | RW   | 0       | MXCK[8:0]             |

Note 1: If MXCK\_SEL Control (bit 6) is set to '0' (default), MXCK[8:0] outputs are controlled with MXCK\_SEL\_100 pin. If MXCK\_SEL Control (bit 6) is set to '1' then MXCK[8:0] outputs are controlled with MXCK\_SEL bit (bit 7). MXCK\_SEL switchover is asynchronous. If the user needs glitch free transition, the outputs shall be disabled first and enabled only after the MXCK\_SEL is changed.

TABLE 3-4: BYTE 3: PFT CONTROL REGISTER

| Bit | Description                                       | If Bit = 0       | If Bit = 1          | Туре | Defualt  | Output(s)<br>Affected |

|-----|---------------------------------------------------|------------------|---------------------|------|----------|-----------------------|

| 0   | Reserved                                          | _                | _                   | _    | 0        | Reserved              |

| 1   | Reserved                                          | _                | _                   | _    | 0        | Reserved              |

| 2   | Reserved                                          | _                | _                   | _    | 0        | Reserved              |

| 3   | Reserved                                          | _                | _                   | _    | 0        | Reserved              |

| 4   | Reserved                                          | _                | _                   | _    | 0        | Reserved              |

| 5   | Clear Delta Frequency Registers<br>(Byte 4 and 5) | _                | All bits reset to 0 | RW   | 0        | Reserved              |

| 6   | Stop Delta Frequency Update<br>(Byte 4 and 5)     | Disabled         | Enabled             | RW   | 0        | Reserved              |

| 7   | Realtime Readback of PFT_LOST#                    | PFT_LOST#<br>low | PFT_LOST#<br>high   | R    | Realtime | PFT_OUT               |

Note 1: Prior to reading the delta frequency between PFT\_IN and the local 25 MHz XO (Bytes 4 and 5), the user should set bit 6 to prevent the case where one of the PFT Frequency Delta Registers is read before and the other after the internal update. This bit should be cleared after the read has been completed.

TABLE 3-5: BYTE 4: PFT FREQUENCY DELTA REGISTER 0 (LEAST SIGNIFICANT BYTE)

| Bit | Description                    | If Bit = 0 | If Bit = 1 | Туре | Default  | Output(s)<br>Affected |

|-----|--------------------------------|------------|------------|------|----------|-----------------------|

| 0   | PFT – 25 MHz XO bit 0          | _          | _          | R    | Realtime | _                     |

| 1   | PFT – 25 MHz XO bit 1          | _          | _          | R    | Realtime | _                     |

| 2   | PFT – 25 MHz XO bit 2          | _          | _          | R    | Realtime | _                     |

| 3   | PFT – 25 MHz XO bit 3          | _          | _          | R    | Realtime | _                     |

| 4   | PFT – 25 MHz XO bit 4 (Note 1) | _          | _          | R    | Realtime | _                     |

| 5   | PFT – 25 MHz XO bit 5          | _          | _          | R    | Realtime | _                     |

| 6   | PFT – 25 MHz XO bit 6          | _          | _          | R    | Realtime | _                     |

| 7   | PFT – 25 MHz XO bit 7          | _          | _          | R    | Realtime | _                     |

Note 1: Byte 4 and 5 contain frequency difference between the PFT clock and the local 25 MHz reference in two's complement format with resolution (step size) of 1 ns \* (25 MHz/2<sup>15</sup>) ≈ 1 ns/1.31 ms = 0.763 ppm. Byte 4 contains the least significant byte.

TABLE 3-6: BYTE 5: PFT FREQUENCY DELTA REGISTER 1 (MOST SIGNIFICANT BYTE)

| Bit | Description                     | If Bit = 0 | If Bit = 1 | Туре | Default  | Output(s)<br>Affected |

|-----|---------------------------------|------------|------------|------|----------|-----------------------|

| 0   | PFT – 25 MHz XO bit 8           | _          | _          | R    | Realtime | _                     |

| 1   | PFT – 25 MHz XO bit 9           | _          | _          | R    | Realtime | _                     |

| 2   | PFT – 25 MHz XO bit 10          | _          | _          | R    | Realtime | _                     |

| 3   | PFT – 25 MHz XO bit 11          | _          | _          | R    | Realtime | _                     |

| 4   | PFT – 25 MHz XO bit 12 (Note 1) | _          | _          | R    | Realtime | _                     |

| 5   | PFT – 25 MHz XO bit 13          | _          | _          | R    | Realtime | _                     |

| 6   | PFT – 25 MHz XO bit 14          | _          | _          | R    | Realtime | _                     |

| 7   | PFT – 25 MHz XO bit 15          | _          | _          | R    | Realtime | _                     |

Note 1: Byte 4 and 5 contain frequency difference between the PFT clock and the local 25 MHz reference in two's complement format with resolution (step size) of 1 ns \* (25 MHz/2<sup>15</sup>) ≈ 1 ns/1.31 ms = 0.763 ppm. Byte 5 contains the most significant byte.

TABLE 3-7: BYTE 6: SSC PLL CONTROL REGISTER

| Bit | Description                 | If Bit = 0                                         | If Bit = 1             | Туре                            | Default                                             | Output(s)<br>Affected                               |

|-----|-----------------------------|----------------------------------------------------|------------------------|---------------------------------|-----------------------------------------------------|-----------------------------------------------------|

| 0   | SSC Select                  | bit1 bit0: SSC 5<br>00: SSC 0<br>01: SSC =         | RW                     | Latch SSC<br>Pin on<br>Power-Up | 100M[6:0] and<br>MXCK[8:0] if<br>MXCK_SEL is<br>low |                                                     |

| 1   | 330 Select                  | 01: SSC = -0.3%<br>10: Reserved<br>11: SSC = -0.5% |                        | RW                              | Latch SSC<br>Pin on<br>Power-Up                     | 100M[6:0] and<br>MXCK[8:0] if<br>MXCK_SEL is<br>low |

| 2   | SSC Pin Control             | Enabled                                            | Disabled               | RW                              | 0                                                   | 100M[6:0] and<br>MXCK[8:0] if<br>MXCK_SEL is<br>low |

| 3   | SSC PLL Input Source        | XTAL                                               | Filter PLL<br>(Note 1) | RW                              | 0                                                   | 100M[6:0] and<br>MXCK[8:0] if<br>MXCK_SEL is<br>low |

| 4   | Readback of SSC ENABLE Pin  | bit1 bit0: SSC \$ 00: SSC 0 01: SSC =              | Off                    | R                               | Realtime                                            | 100M[6:0] and<br>MXCK[8:0] if<br>MXCK_SEL is<br>low |

| 5   | Neadback of OOC_ENABLE FIII | 01: SSC = -0.3%<br>10: Reserved<br>11: SSC = -0.5% |                        | R                               | Realtime                                            | 100M[6:0] and<br>MXCK[8:0] if<br>MXCK_SEL is<br>low |

| 6   | Reserved                    | _                                                  | _                      | _                               | 0                                                   | Reserved                                            |

| 7   | Reserved                    | _                                                  | _                      | _                               | 0                                                   | Reserved                                            |

**Note 1:** When "SSC PLL Input Source" selects the "Filter PLL" option, there's no guarantee the outputs will be synchronized.

TABLE 3-8: BYTE 7: OE# REALTIME READBACK CONTROL REGISTER

| Bit | Description                    | If Bit = 0 | If Bit = 1 | Туре | Default  | Output(s)<br>Affected |

|-----|--------------------------------|------------|------------|------|----------|-----------------------|

| 0   | Realtime Readback of OE_0# pin | OE_0# Low  | OE_0# High | R    | Realtime | 100M0                 |

| 1   | Realtime Readback of OE_1# pin | OE_1# Low  | OE_1# High | R    | Realtime | 100M1                 |

| 2   | Realtime Readback of OE_2# pin | OE_2# Low  | OE_2# High | R    | Realtime | 100M2                 |

| 3   | Realtime Readback of OE_3# pin | OE_3# Low  | OE_3# High | R    | Realtime | 100M3                 |

| 4   | Realtime Readback of OE_4# pin | OE_4# Low  | OE_4# High | R    | Realtime | 100M4                 |

| 5   | Realtime Readback of OE_5# pin | OE_5# Low  | OE_5# High | R    | Realtime | 100M5                 |

| 6   | Realtime Readback of OE_6# pin | OE_6# Low  | OE_6# High | R    | Realtime | 100M6                 |

| 7   | Reserved                       | _          | _          | R    | 0        | _                     |

TABLE 3-9: BYTE 8: VENDOR/REVISION IDENTIFICATION CONTROL REGISTER

| Bit | Description         | If Bit = 0 | If Bit = 1 | Туре | Default | Output(s)<br>Affected |

|-----|---------------------|------------|------------|------|---------|-----------------------|

| 0   | Vendor ID Bit 0     | _          | _          | R    | 1       | _                     |

| 1   | Vendor ID Bit 1     | _          | _          | R    | 1       | _                     |

| 2   | Vendor ID Bit 2     | _          | _          | R    | 0       | _                     |

| 3   | Vendor ID Bit 3     | _          | _          | R    | 0       | _                     |

| 4   | Revision Code Bit 0 | _          | _          | R    | 0       | _                     |

| 5   | Revision Code Bit 1 | _          | _          | R    | 1       | _                     |

| 6   | Revision Code Bit 2 | _          | _          | R    | 0       | _                     |

| 7   | Revision Code Bit 3 | _          | _          | R    | 0       | _                     |

TABLE 3-10: BYTE 9: DEVICE ID CONTROL REGISTER

| Bit | Description       | If Bit = 0 | If Bit = 1 | Туре | Default | Output(s)<br>Affected |

|-----|-------------------|------------|------------|------|---------|-----------------------|

| 0   | Device ID 0       | _          | _          | R    | 1       | _                     |

| 1   | Device ID 1       | _          | _          | R    | 1       | _                     |

| 2   | Device ID 2       | _          | _          | R    | 0       | _                     |

| 3   | Device ID 3       | _          | _          | R    | 1       | _                     |

| 4   | Device ID 4       | _          | _          | R    | 1       | _                     |

| 5   | Device ID 5       | _          | _          | R    | 0       | _                     |

| 6   | Device ID 6       | _          | _          | R    | 1       | _                     |

| 7   | Device ID 7 (MSB) | _          | _          | R    | 0       | _                     |

TABLE 3-11: BYTE 10: BYTE COUNT REGISTER

| Bit | Description                                                                | If Bit = 0 | If Bit = 1 | Туре | Default | Output(s)<br>Affected |

|-----|----------------------------------------------------------------------------|------------|------------|------|---------|-----------------------|

| 0   | BC0 - Writing to this register configures how many bytes will be read back | _          | _          | RW   | 0       | _                     |

| 1   | BC1 - Writing to this register configures how many bytes will be read back | _          | _          | RW   | 0       | _                     |

| 2   | BC2 - Writing to this register configures how many bytes will be read back | _          | _          | RW   | 0       | _                     |

| 3   | BC2 - Writing to this register configures how many bytes will be read back | _          | _          | RW   | 1       | _                     |

| 4   | BC3 - Writing to this register configures how many bytes will be read back | _          | _          | RW   | 0       | _                     |

| 5   | BC4 - Writing to this register configures how many bytes will be read back | _          | _          | RW   | 0       | _                     |

| 6   | Reserved                                                                   | _          | _          |      | 0       |                       |

| 7   | Reserved                                                                   | _          | _          | _    | 0       | _                     |

TABLE 3-12: BYTE 11: SIDE-BAND INTERFACE MASK REGISTER 0

| Bit | Description    | If Bit = 0<br>(Note 1) | If Bit = 1<br>(Note 1) | Туре | Default | Output(s)<br>Affected |

|-----|----------------|------------------------|------------------------|------|---------|-----------------------|

| 0   | SBI Mask 100M0 | Off                    | On                     | RW   | 0       | 100M0                 |

| 1   | SBI Mask 100M1 | Off                    | On                     | RW   | 0       | 100M1                 |

| 2   | SBI Mask 100M2 | Off                    | On                     | RW   | 0       | 100M2                 |

| 3   | SBI Mask 100M3 | Off                    | On                     | RW   | 0       | 100M3                 |

| 4   | SBI Mask 100M4 | Off                    | On                     | RW   | 0       | 100M4                 |

| 5   | SBI Mask 100M5 | Off                    | On                     | RW   | 0       | 100M5                 |

| 6   | SBI Mask 100M6 | Off                    | On                     | RW   | 0       | 100M6                 |

| 7   | SBI Mask MXCK8 | Off                    | On                     | RW   | 0       | MXCK8                 |