# X67BCJ321.L12

## 1 General information

Established in 1979, the Modbus protocol has approved the use of Ethernet with both Modbus TCP and Modbus/UDP. Today, Modbus TCP is an open Internet draft standard introduced by Schneider Automation to the Internet Engineering Task Force (IETF), the organization responsible for Internet standardization. The Modbus services and object model have been preserved since the original version and left unchanged for use with the TCP/IP transmission medium.

Modbus/UDP differs from Modbus TCP in that it uses connectionless communication via UDP/IP. The advantages of faster and easier communication with UDP/IP also brings with it the disadvantage of requiring error detection and correction in the application layer.

This bus controller makes it possible to connect X2X Link I/O nodes to Modbus via Ethernet. The bus controller can be operated on B&R controllers through the use of Automation Studio or on third-party systems with Modbus TCP or -UDP master functionality.

- Fieldbus: Modbus/TCP, Modbus/UDP

- Integrated 2-port switch for efficient cabling

- I/O configuration via the fieldbus

- DHCP-capable

- Response time: <1 to 8 ms (depends on the load on the integrated switch)</li>

- Check validity of command sequences before execution

- 16 digital channels, configurable as inputs or outputs

- M12 connection type

- Integrated connection to local expansions via X2X Link for 250 additional modules

- Configurable I/O cycle (0.5 to 4 ms)

#### Information:

Only the standard function model (see the respective module description) is supported when the bus controller is used together with multi-function modules it has automatically configured itself.

All other function models are supported when configured accordingly in Automation Studio V4.3 or later.

Automation Studio can be downloaded at no cost from the B&R website (<u>www.br-automation.com</u>). The evaluation license is permitted to be used to create complete configurations for fieldbus bus controllers at no cost.

# 2 Order data

| Order number  | Short description                                                                                                                                                                                                                         | Figure |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

|               | Bus controller modules                                                                                                                                                                                                                    |        |

| X67BCJ321.L12 | X67 bus controller, 1 Modbus TCP/UDP interface, X2X Link power supply 15 W, 16 digital channels configurable as inputs or outputs, 24 VDC, 0.5 A, configurable input filter, 2 event counters 50 kHz, M12 connectors, high-density module |        |

Table 1: X67BCJ321.L12 - Order data

| Required accessories                                                                                  |

|-------------------------------------------------------------------------------------------------------|

| See "Required cables and connectors" on page 8.                                                       |

| For a general overview, see section "Accessories - General overview" of the X67 system user's manual. |

# 3 Technical data

| Order number                               | X67BCJ321.L12                                                                                                                  |

|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|

| Short description                          |                                                                                                                                |

| Bus controller                             | Modbus TCP/UDP slave                                                                                                           |

| General information                        |                                                                                                                                |

| Inputs/Outputs                             | 16 digital channels, configurable as inputs or outputs using Automation Studio or data point, inputs with additional functions |

| Insulation voltage between channel and bus | 500 V <sub>eff</sub>                                                                                                           |

| Nominal voltage                            | 24 VDC                                                                                                                         |

| B&R ID code                                |                                                                                                                                |

| Bus controller                             | 0xAD3C                                                                                                                         |

| Internal I/O module                        | 0xBD76                                                                                                                         |

| Sensor/Actuator power supply               | 0.5 A summation current                                                                                                        |

| Status indicators                          | I/O function per channel, supply voltage, bus function                                                                         |

| Diagnostics                                |                                                                                                                                |

| Outputs                                    | Yes, using LED status indicator and software                                                                                   |

| I/O power supply                           | Yes, using LED status indicator and software                                                                                   |

| Connection type                            | , ,                                                                                                                            |

| Fieldbus                                   | M12, D-coded                                                                                                                   |

| X2X Link                                   | M12, B-coded                                                                                                                   |

| Inputs/Outputs                             | 8x M12, A-coded                                                                                                                |

| I/O power supply                           | M8, 4-pin                                                                                                                      |

| Power output                               | 15 W X2X Link power supply for I/O modules                                                                                     |

| Power consumption                          | 10 11 / L.X. Ellik politic cappi) for the missaise                                                                             |

| Fieldbus                                   | 4.2 W                                                                                                                          |

| Internal I/O                               | 2.5 W                                                                                                                          |

| X2X Link power supply                      | 24.3 W at maximum power output for connected I/O modules                                                                       |

| Certifications                             | 2 10 11 at maximum perior curput of commercial in a modulo                                                                     |

| CE                                         | Yes                                                                                                                            |

| ATEX                                       | Zone 2, II 3G Ex nA IIA T5 Gc<br>IP67, Ta = 0 - Max. 60°C<br>TÜV 05 ATEX 7201X                                                 |

| UL                                         | cULus E115267<br>Industrial control equipment                                                                                  |

| HazLoc                                     | cCSAus 244665 Process control equipment for hazardous locations Class I, Division 2, Groups ABCD, T5                           |

| EAC                                        | Yes                                                                                                                            |

| KC                                         | Yes                                                                                                                            |

| Interfaces                                 |                                                                                                                                |

| Fieldbus                                   | Modbus TCP/UDP slave                                                                                                           |

| Variant                                    | 2x M12 interface (switch), 2x female connector on the module                                                                   |

| Cable length                               | Max. 100 m between 2 stations (segment length)                                                                                 |

| Transfer rate                              | 10/100 Mbit/s                                                                                                                  |

Table 2: X67BCJ321.L12 - Technical data

|                                                      | VOTRO 1004 I 40                                                                       |

|------------------------------------------------------|---------------------------------------------------------------------------------------|

| Order number                                         | X67BCJ321.L12                                                                         |

| Transfer                                             | AODACE TIAOODACE TV                                                                   |

| Physical layer                                       | 10BASE-T/100BASE-TX                                                                   |

| Half-duplex                                          | Yes                                                                                   |

| Full-duplex                                          | Yes                                                                                   |

| Autonegotiation                                      | Yes                                                                                   |

| Auto-MDI/MDIX                                        | Yes                                                                                   |

| Min. cycle time 1)                                   |                                                                                       |

| Fieldbus                                             | 1 ms                                                                                  |

| X2X Link                                             | 500 μs                                                                                |

| Synchronization between bus systems possible         | No                                                                                    |

| I/O power supply                                     |                                                                                       |

| Nominal voltage                                      | 24 VDC                                                                                |

| Voltage range                                        | 18 to 30 VDC                                                                          |

| Integrated protection                                | Reverse polarity protection                                                           |

| Power consumption                                    |                                                                                       |

| Sensor/Actuator power supply                         | Max. 12 W <sup>2)</sup>                                                               |

| Sensor/Actuator power supply                         |                                                                                       |

| Voltage                                              | I/O power supply minus voltage drop for short-circuit protection                      |

| Voltage drop for short-circuit protection at 0.5 A   | Max. 2 VDC                                                                            |

| Summation current                                    | Max. 0.5 A                                                                            |

|                                                      |                                                                                       |

| Short-circuit proof                                  | Yes                                                                                   |

| Digital inputs                                       | - :                                                                                   |

| Input characteristics per EN 61131-2                 | Type 1                                                                                |

| Input voltage                                        | 18 to 30 VDC                                                                          |

| Input current at 24 VDC                              | Typ. 4 mA                                                                             |

| Input circuit                                        | Sink                                                                                  |

| Input filter                                         |                                                                                       |

| Hardware                                             | ≤10 µs (channels 1 to 4) / ≤70 µs (channels 5 to 16)                                  |

| Software                                             | Default 0 ms, configurable between 0 and 25 ms in 0.2 ms intervals                    |

| Input resistance                                     | Τγρ. 6 kΩ                                                                             |

| Additional functions                                 | 50 kHz event counting, gate measurement                                               |

| Switching threshold                                  | 30 KHZ event counting, gate measurement                                               |

| -                                                    | 45 VDO                                                                                |

| Low                                                  | <5 VDC                                                                                |

| High                                                 | >15 VDC                                                                               |

| Event counters                                       |                                                                                       |

| Quantity                                             | 2                                                                                     |

| Signal form                                          | Square wave pulse                                                                     |

| Evaluation                                           | Each negative edge, cyclic counter                                                    |

| Input frequency                                      | Max. 50 kHz                                                                           |

| Counter 1                                            | Input 1                                                                               |

| Counter 2                                            | Input 3                                                                               |

| Counter frequency                                    | Max. 50 kHz                                                                           |

| Counter size                                         | 16-bit                                                                                |

| Gate measurement                                     |                                                                                       |

| Quantity                                             | 1                                                                                     |

| Signal form                                          | Square wave pulse                                                                     |

| Evaluation                                           | · · ·                                                                                 |

|                                                      | Positive edge - Negative edge                                                         |

| Counter frequency                                    | (O.M.) (O.M.) (O.T.)                                                                  |

| Internal                                             | 48 MHz, 3 MHz, 187.5 kHz                                                              |

| Counter size                                         | 16-bit                                                                                |

| Length of pause between pulses                       | ≥100 µs                                                                               |

| Pulse length                                         | ≥20 µs                                                                                |

| Supported inputs                                     | Input 2 or input 4                                                                    |

| Digital outputs                                      |                                                                                       |

| Variant                                              | Current-sourcing FET                                                                  |

| Switching voltage                                    | I/O power supply minus residual voltage                                               |

| Nominal output current                               | 0.5 A                                                                                 |

| Total nominal current                                | 8 A                                                                                   |

| Output circuit                                       | Source                                                                                |

| Output circuit Output protection                     | Thermal shutdown in the event of overcurrent or short circuit, integrated protection  |

| Output proteotion                                    | for switching inductive loads, reverse polarity protection of the output power supply |

| Diagnostic status                                    | Output monitoring with 10 ms delay                                                    |

| Leakage current when the output is switched off      |                                                                                       |

| -                                                    | 5 μA                                                                                  |

| Switching on after overload shutdown                 | Approx. 10 ms (depends on the module temperature)                                     |

| Residual voltage                                     | <0.3 V at 0.5 A nominal current                                                       |

| Peak short-circuit current                           | <12 A                                                                                 |

| Switching delay                                      |                                                                                       |

| 0 → 1                                                | <400 μs                                                                               |

| 1 → 0                                                | <400 µs                                                                               |

| Switching frequency                                  | ·                                                                                     |

| Resistive load                                       | Max. 100 Hz                                                                           |

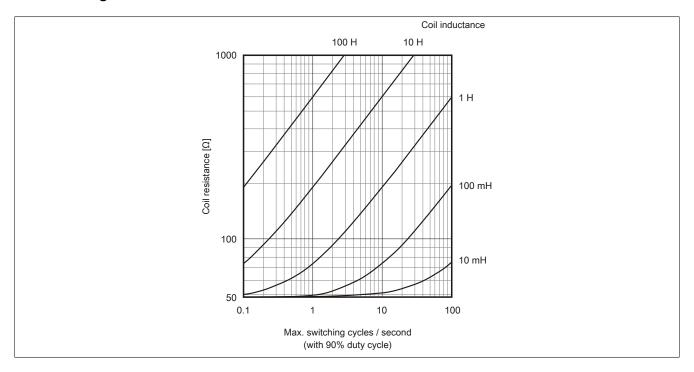

| Inductive load                                       | See section "Switching inductive loads".                                              |

| Braking voltage when switching off inductive loads   | 50 VDC                                                                                |

| 2. a.m.ig voltage which aveitoring on mudelive leads | 00 450                                                                                |

Table 2: X67BCJ321.L12 - Technical data

| Order number                           | X67BCJ321.L12                                                      |

|----------------------------------------|--------------------------------------------------------------------|

| Electrical properties                  |                                                                    |

| Electrical isolation                   | Bus isolated from channel                                          |

|                                        | Modbus not isolated from bus and channel not isolated from channel |

| Operating conditions                   |                                                                    |

| Mounting orientation                   |                                                                    |

| Any                                    | Yes                                                                |

| Installation elevation above sea level |                                                                    |

| 0 to 2000 m                            | No limitation                                                      |

| >2000 m                                | Reduction of ambient temperature by 0.5°C per 100 m                |

| Degree of protection per EN 60529      | IP67                                                               |

| Ambient conditions                     |                                                                    |

| Temperature                            |                                                                    |

| Operation                              | -25 to 60°C                                                        |

| Derating                               | -                                                                  |

| Storage                                | -40 to 85°C                                                        |

| Transport                              | -40 to 85°C                                                        |

| Mechanical properties                  |                                                                    |

| Dimensions                             |                                                                    |

| Width                                  | 53 mm                                                              |

| Height                                 | 155 mm                                                             |

| Depth                                  | 42 mm                                                              |

| Weight                                 | 350 g                                                              |

| Torque for connections                 |                                                                    |

| M8                                     | Max. 0.4 Nm                                                        |

| M12                                    | Max. 0.6 Nm                                                        |

Table 2: X67BCJ321.L12 - Technical data

- The minimum cycle time specifies how far the bus cycle can be reduced without communication errors occurring. The power consumption of the sensors and actuators connected to the module is not permitted to exceed 12 W.

# 4 LED status indicators

| Figure                  | LED             | Color                                                              | Status         | Description                                                                               |  |  |  |  |

|-------------------------|-----------------|--------------------------------------------------------------------|----------------|-------------------------------------------------------------------------------------------|--|--|--|--|

|                         | Status indicato | Status indicator 1: Status indicator for Modbus TCP bus controller |                |                                                                                           |  |  |  |  |

|                         | L/A IF          | Green                                                              | Blinking       | Indicates Ethernet activity on one or both Ethernet interfaces                            |  |  |  |  |

|                         |                 |                                                                    | Permanently    | Indicates an established connection (link) on one or both Ethernet inter-                 |  |  |  |  |

|                         |                 |                                                                    | on             | faces, but no communication is taking place                                               |  |  |  |  |

|                         |                 |                                                                    | Off            | Indicates that no physical Ethernet connection exists                                     |  |  |  |  |

| Status indicator 1:     | S/E1)           | Green                                                              | Permanently    | Indicates that there is at least one client connection                                    |  |  |  |  |

| eft: L/A IF; right: S/E |                 |                                                                    | on             |                                                                                           |  |  |  |  |

| 000                     |                 |                                                                    | 2 pulses       | Indicates that there are no client connections                                            |  |  |  |  |

|                         |                 |                                                                    | 4 pulses       | Indicates that the controller is waiting for an address from the DHCP server              |  |  |  |  |

| 0                       |                 |                                                                    | Blinking       | Initialization of connected I/O modules                                                   |  |  |  |  |

| 1-1   5-1               |                 | Red                                                                | Permanently on | Indicates a major unrecoverable hardware fault                                            |  |  |  |  |

| 3::0                    |                 |                                                                    | 2 pulses       | Watchdog timeout                                                                          |  |  |  |  |

| 2-1 6-1                 |                 |                                                                    | 3 pulses       | Faulty I/O module configuration data                                                      |  |  |  |  |

| <b>3 3</b>              |                 |                                                                    | 4 pulses       | Indicates that the controller has detected an IP address being used twice                 |  |  |  |  |

| 2-2<br>3-1<br>7-1       |                 |                                                                    | 5 pulses       | Indicates a missing, defective or incorrect I/O module                                    |  |  |  |  |

|                         |                 |                                                                    | 6 pulses       | Error reading from or writing to flash memory                                             |  |  |  |  |

| 3-2 7-2<br>4-1 8-1      | VO LEDs         |                                                                    |                |                                                                                           |  |  |  |  |

| (C) 4-2 8-2 (C)         | 1-1 to 8-2      | Orange                                                             | -              | Input/Output status of the corresponding channel                                          |  |  |  |  |

| 15 (D) (A)              | Status indicato | Status indicator 2: Status indicator for module function           |                |                                                                                           |  |  |  |  |

|                         | Left Green      |                                                                    | Off            | No power to module                                                                        |  |  |  |  |

|                         |                 |                                                                    | Single flash   | RESET mode                                                                                |  |  |  |  |

| Status indicator 2:     |                 |                                                                    | Blinking       | PREOPERATIONAL mode                                                                       |  |  |  |  |

| eft: green; Right: red  |                 |                                                                    | On             | RUN mode                                                                                  |  |  |  |  |

|                         | Right           | Red                                                                | Off            | No power to module or everything OK                                                       |  |  |  |  |

|                         |                 |                                                                    | On             | Error or reset status                                                                     |  |  |  |  |

|                         |                 |                                                                    | Single flash   | Warning/Error on an I/O channel. Level monitoring for digital outputs has been triggered. |  |  |  |  |

|                         |                 |                                                                    | Double flash   | Supply voltage not in the valid range                                                     |  |  |  |  |

The Status/Error LED is a green/red dual LED. The LED blinks red several times immediately after startup. This is a boot message, however, and not an error.

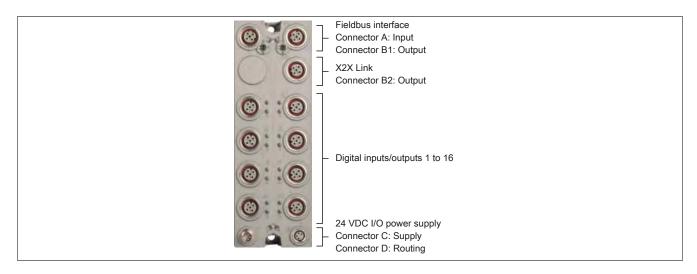

# 5 Operating and connection elements

### 6 Fieldbus interfaces

The module is connected to the network using pre-assembled cables. The connection is made using M12 circular connectors.

| Connection |                                                          | Pinout                                   |                |

|------------|----------------------------------------------------------|------------------------------------------|----------------|

| 2 A        | Pin                                                      | N                                        | lame           |

| 1          | 1                                                        | TXD                                      | Transmit data  |

|            | 2                                                        | RXD                                      | Receive data   |

|            | 3                                                        | TXD\                                     | Transmit data\ |

|            | 4                                                        | RXD\                                     | Receive data\  |

| 4          | Shield connection                                        | n made via threaded insert in the module |                |

| 3          | $A \rightarrow D$ -keyed (fe B1 $\rightarrow$ D-keyed (f | emale), input<br>emale), output          |                |

| 2 B1 1     |                                                          |                                          |                |

# Information:

The color of the wires used in field-assembled cables for connecting to the fieldbus interface may deviate from the standard.

It is extremely important to make sure that the pinout is correct (see X67 section "Accessories - POW-ERLINK cables" in the X67 user's manual).

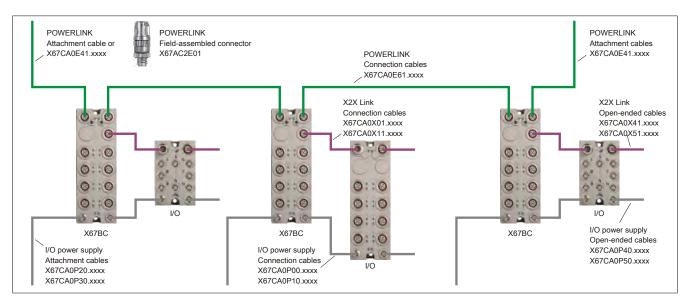

#### 6.1 Cabling guidelines for bus controllers with Ethernet cables

Some X67 system bus controllers are based on Ethernet technology. POWERLINK cables supplied by B&R can be used for wiring.

| Model number   | Connection type                 |

|----------------|---------------------------------|

| X67CA0E41.xxxx | Attachment cables - RJ45 to M12 |

| X67CA0E61.xxxx | Connection cables - M12 to M12  |

The following cabling guidelines must be observed:

- · Use Cat 5 SFTP cables.

- · Observe the minimum cable bend radius (see data sheet for the cable).

# Information:

Using POWERLINK cables supplied by B&R (X67CA0E61.xxxx and X67CA0E41.xxxx) satisfies product standard EN 61131-2.

The customer must implement additional measures in the event of further requirements.

#### 6.2 Modbus TCP network address switches

High Lov

| Switch position | Description                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                              |  |  |  |  |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 0x00            | This switch position is the factory default setting. In this position, the address switches have no effect on system parameters. The bus controller parameters in flash memory are used (IP address or interface number). The bus controller is started with factory default values if valid flash data is not present. |                                                                                                                                                                                                              |  |  |  |  |

| 0x01 to 0x7F    | The last position of the IP address saved in in flash memory is not changed. The interfa                                                                                                                                                                                                                                | flash memory is changed to the address switch value. The IP address saved ace number is read from flash memory.                                                                                              |  |  |  |  |

| 0x80 to 0xEF    |                                                                                                                                                                                                                                                                                                                         | Sets the bus controller to DHCP mode for this range. The DNS server is informed of the current hostname. A hostname is generated according to the setting of the address switch.                             |  |  |  |  |

|                 | Example The generated hostname is in "br" + "mb" + Address sw                                                                                                                                                                                                                                                           | nade up of 3 elements:<br>itch value (3 decimal places)                                                                                                                                                      |  |  |  |  |

|                 | This means, for example, the 215): "brmb215".                                                                                                                                                                                                                                                                           | at the following hostname is generated for address switch setting 0xD7 (dec.                                                                                                                                 |  |  |  |  |

| 0xF0 to 0xFD    | Reserved (same function as position 0xFF)                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                              |  |  |  |  |

| 0xFE            |                                                                                                                                                                                                                                                                                                                         | Initializes all bus controller parameters with default values during booting. No values are read from flash memory. The communication parameters correspond to the values assigned with switch setting 0xFF. |  |  |  |  |

| 0xFF            | Initializes all communication parameters wit<br>ory. Default parameters:                                                                                                                                                                                                                                                |                                                                                                                                                                                                              |  |  |  |  |

|                 | IP address:                                                                                                                                                                                                                                                                                                             | 192.168.100.1                                                                                                                                                                                                |  |  |  |  |

|                 | Subnet mask:                                                                                                                                                                                                                                                                                                            | 255.255.255.0                                                                                                                                                                                                |  |  |  |  |

|                 | Gateway:                                                                                                                                                                                                                                                                                                                | • Gateway: 192,168,100,254                                                                                                                                                                                   |  |  |  |  |

|                 | -                                                                                                                                                                                                                                                                                                                       | i illiary NetBiod Hame.                                                                                                                                                                                      |  |  |  |  |

|                 | _                                                                                                                                                                                                                                                                                                                       | occordary reciproc harne.                                                                                                                                                                                    |  |  |  |  |

|                 | Interface number:                                                                                                                                                                                                                                                                                                       | 502                                                                                                                                                                                                          |  |  |  |  |

|                 | X2X Link configuration:                                                                                                                                                                                                                                                                                                 | 4 ms cycle time                                                                                                                                                                                              |  |  |  |  |

|                 | X2X Link cable length:                                                                                                                                                                                                                                                                                                  | 0 m                                                                                                                                                                                                          |  |  |  |  |

## 6.2.1 Setting the IP address (default value)

Changes to the network address switches are only applied after a restart. If the bus controller is restarted with the address switch value 0xFF, it is initialized with the IP address 192.168.100.1. This address is also the factory default setting. The interface number is set to 502 (reserved for Modbus).

This IP address can be used to establish a connection to the bus controller. The internationally unique MAC address is listed on the housing side of the bus controller. The combination of "br" and the MAC address results in a unique name (primary NetBIOS name) that also makes it possible to access the bus controller.

Example of the primary NetBIOS name:

MAC address: 00-60-65-00-49-02 Resulting NetBIOS name: br006065004902

This means that, without additional parameter changes, either the default IP address 192.168.100.1 or the NetBIOS name "br+MAC" can be used to communicate with the bus controller.

Since NetBIOS is being used, the bus controller can only be accessed via this name if there are no intermediary routers or gateways in the way.

#### 6.2.2 Automatic IP assignment by a DHCP server

If a network address switch setting between 0x80 and 0xEF is configured, the bus controller will attempt to request an IP address from the DHCP server. The assigned IP address can be queried with command "ping" together with the hostname. The bus controller registers this hostname on the DHCP server, which should forward it to a DNS server.

## **Example** The hostname (DNS name) is made up of 3 elements:

"br" + "mb" + Address switch value (3 decimal places)

This means, for example, that the following hostname is generated for address switch setting 0xD7 (dec. 215): "brmb215".

If DNS service is not available on the network, the bus controller's two NetBIOS names can also be used for access. The secondary NetBIOS name is identical to the hostname. If the address switches are set to 0x00, it is identical to the primary NetBIOS name. The bus controller can only be reached via its NetBIOS name if no other routers or gateways are in the way.

### 6.2.3 Changing the IP address with the network address switches

The address switches can be used to change the last byte in the IP address configured on the bus controller. The IP address saved in flash memory is not changed. If the address switches are set to 0x00, the bus controller applies the IP address last saved to flash memory. Switch positions between 0x01 and 0x7F cause the last position of the IP address (the lowest byte) to be overwritten by the value of the address switch. This provides the user a quick and easy way to address a large number of bus controllers. In short, an IP address between 192.168.100.1 and 192.168.100.127 can be selected for a bus controller using the address switches without requiring any additional software configuration.

#### 6.2.4 Saving an IP address to flash memory

The IP parameters in flash memory can be changed via the Modbus protocol, the ModbusTCP Toolbox or the Telnet interface. The ModbusTCP Toolbox can be downloaded from the B&R website.

The IP address, subnet and gateway are all defined in the address range 0x1003 to 0x100E. Each has a length of 4 words. The data is applied by writing constant 0xC1 to address 0x1140 ("Write single register" fc6, addr. 0x1140, data 0xC1). The new settings are applied after the bus controller is restarted.

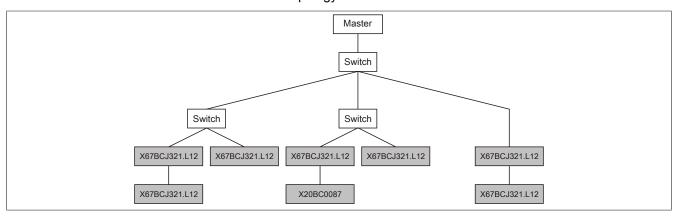

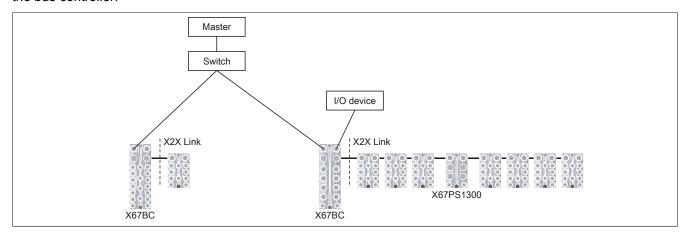

#### 6.3 Integration in a Modbus TCP network

This bus controller can be used in a tree or line topology as follows:

## 6.4 System configuration

A digital mixed module is already integrated in the bus controller. Up to 250 I/O modules can be connected to the bus controller.

#### Information:

15 W are provided by the bus controller for additional X67 modules or other X2X Link-based modules. System supply module X67PS1300 is needed for additional power. This system supply module provides 15 W for additional modules. Each one should be mounted in the middle of the modules that are to be supplied with power.

## 6.5 Required cables and connectors

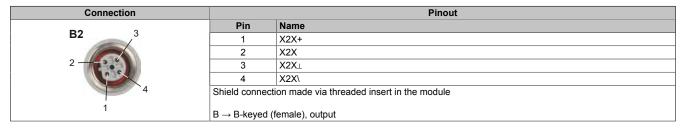

#### 7 X2X Link

Up to 250 additional modules can be connected to the bus controller via X2X Link using pre-assembled cables. The connection is made using an M12 circular connector.

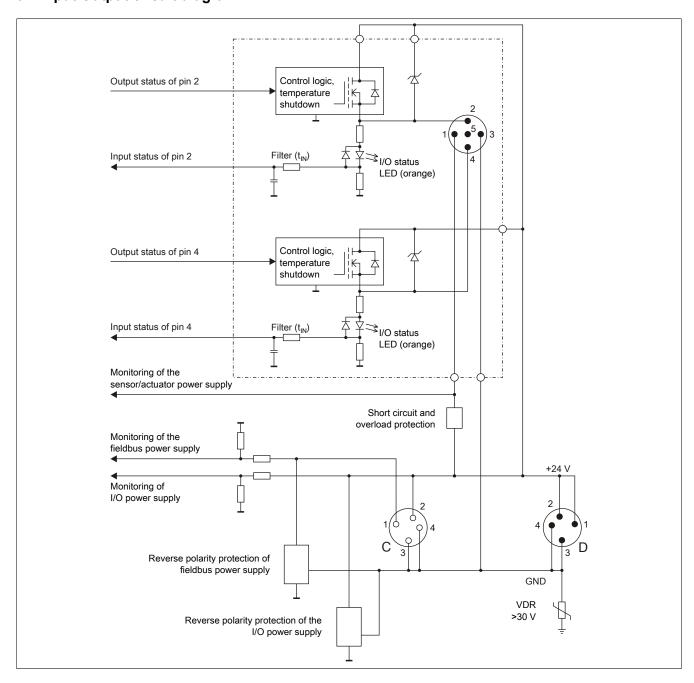

# 8 24 VDC I/O power supply

The I/O power supply is connected via M8 connectors C and D. The power supply is connected via connection C (male). Connector D (female) is used to route the power supply to other modules.

The fieldbus / X2X Link power supply and I/O power supply are supplied separately via pins 1 and 2.

# Information:

The maximum permissible current for the I/O power supply is 8 A (4 A per pin).

| Connection | Pinout                                                    |                                                   |                      |  |

|------------|-----------------------------------------------------------|---------------------------------------------------|----------------------|--|

| 2 C        | Pin                                                       | Connector C (male)                                | Connector D (female) |  |

| 1, /       | 1                                                         | 24 VDC fieldbus / X2X Link                        | 24 VDC I/O           |  |

|            | 2                                                         | 24 VDC I/O                                        | 24 VDC I/O           |  |

| 4          | 3                                                         | GND                                               | GND                  |  |

|            | 4                                                         | GND                                               | GND                  |  |

| 3          | C → Connector (male) in module, feed for I/O power supply |                                                   |                      |  |

|            | D → Connecto                                              | r (female) in module, routing of I/O power supply |                      |  |

| D 2        |                                                           |                                                   |                      |  |

| 4 3        |                                                           |                                                   |                      |  |

# 9 Integrated digital mixed module

1 additional mixed module can be saved by the digital mixed module integrated in the bus controller.

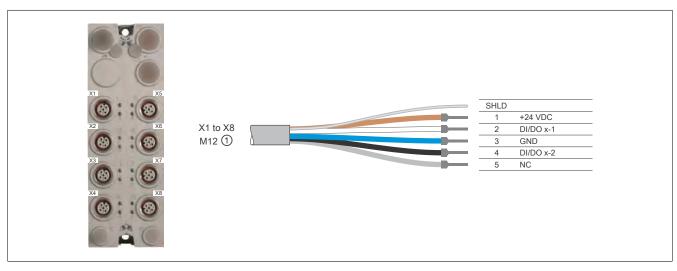

#### 9.1 Pinout

① X67CA0A41.xxxx: M12 sensor cable, straight X67CA0A51.xxxx: M12 sensor cable, angled

# 9.2 Connection X1 to X8

| M12, 5-pin        | Pinout                                                    |                                                |  |

|-------------------|-----------------------------------------------------------|------------------------------------------------|--|

| Connection 1 to 4 | Pin                                                       | Name                                           |  |

| 1                 | 1                                                         | 24 VDC sensor/actuator power supply¹)          |  |

| . 2               | 2                                                         | Input/Output x-1                               |  |

| 5                 | 3                                                         | GND                                            |  |

| 3                 | 4                                                         | Input/Output x-2                               |  |

|                   | 5                                                         | NC                                             |  |

| 4                 | Shield connection made via threaded insert in the module. |                                                |  |

| 3                 | 1) An external                                            | sensor/actuator power supply is not permitted. |  |

| 3                 |                                                           | keyed (female), input/output                   |  |

| Connection 5 to 8 |                                                           |                                                |  |

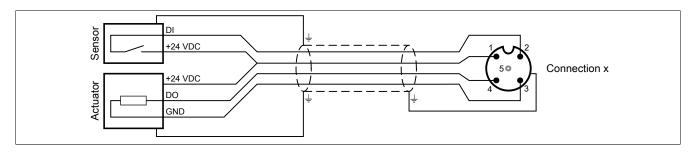

# 9.3 Connection example

# 9.4 Input/Output circuit diagram

# 9.5 Switching inductive loads

# 10 SG3

This module is not supported on SG3 target systems.

# 11 Register description

# 11.1 General data points

In addition to the registers described in the register description, the module has additional general data points. These are not module-specific but contain general information such as serial number and hardware variant.

General data points are described in section "Additional information - General data points" in the X67 system user's manual.

## 11.2 Function model 2 - Standard

| Register      | Name                                       | Data type | R      | ead     | W      | rite    |

|---------------|--------------------------------------------|-----------|--------|---------|--------|---------|

|               |                                            |           | Cyclic | Acyclic | Cyclic | Acyclic |

| Configuration | n                                          |           |        |         |        |         |

| 16            | ConfigIOMask01                             | USINT     |        |         |        | •       |

| 17            | ConfigIOMask02                             | USINT     |        |         |        | •       |

| 18            | ConfigOutput03 (input filter)              | USINT     |        |         |        | •       |

| Communicat    | ion                                        |           |        |         |        |         |

| 0             | Input state of digital inputs 1 to 16      | UINT      | •      |         |        |         |

|               | DigitalInput01                             | Bit 0     |        |         |        |         |

|               |                                            |           |        |         |        |         |

|               | DigitalInput16                             | Bit 15    |        |         |        |         |

| 2             | Switching state of digital outputs 1 to 16 | UINT      |        |         | •      |         |

|               | DigitalOutput01                            | Bit 0     |        |         |        |         |

|               |                                            |           |        |         |        |         |

|               | DigitalOutput16                            | Bit 15    |        |         |        |         |

| 30            | Status of digital outputs 1 to 16          | UINT      | •      |         |        |         |

|               | StatusDigitalOutput01                      | Bit 0     |        |         |        |         |

|               |                                            |           |        |         |        |         |

|               | StatusDigitalOutput16                      | Bit 15    |        |         |        |         |

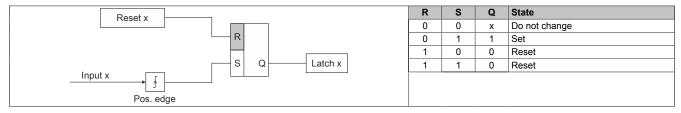

| 26            | Input latch - Rising edges 1 to 8          | USINT     | •      |         |        |         |

|               | InputLatch01                               | Bit 0     |        |         |        |         |

|               |                                            |           |        |         |        |         |

|               | InputLatch08                               | Bit 7     |        |         |        |         |

| 27            | Input latch - Rising edges 9 to 16         | USINT     | •      |         |        |         |

|               | InputLatch09                               | Bit 0     |        |         |        |         |

|               |                                            |           |        |         |        |         |

|               | InputLatch16                               | Bit 7     |        |         |        |         |

| 28            | Acknowledgment - Input latch 1 to 8        | USINT     |        |         | •      |         |

|               | QuitInputLatch01                           | Bit 0     |        |         |        |         |

|               |                                            |           |        |         |        |         |

|               | QuitInputLatch08                           | Bit 7     |        |         |        |         |

| 29            | Acknowledgment - Input latch 9 to 16       | USINT     |        |         | •      |         |

|               | QuitInputLatch09                           | Bit 0     |        | 1       |        |         |

|               |                                            |           |        |         |        |         |

|               | QuitInputLatch16                           | Bit 7     |        |         |        |         |

| 8192          | asy_ModulID                                | UINT      |        | •       |        |         |

| 8196          | asy_SupplyStatus                           | USINT     |        | •       |        |         |

| 8208          | asy_SupplyInput                            | USINT     |        | •       |        |         |

| 8210          | asy_SupplyOutput                           | USINT     |        | •       |        |         |

# 11.3 Function model 1 - Counter

| Register     | Name                                       | Data type | Re     | ead     | Write  |         |

|--------------|--------------------------------------------|-----------|--------|---------|--------|---------|

|              |                                            |           | Cyclic | Acyclic | Cyclic | Acyclic |

| onfiguration | i e                                        |           |        |         |        |         |

| 16           | ConfigIOMask01                             | USINT     |        |         |        | •       |

| 17           | ConfigIOMask02                             | USINT     |        |         |        | •       |

| 20           | ConfigOutput01 (counter channel 1)         | USINT     |        |         |        | •       |

| 22           | ConfigOutput02 (counter channel 2)         | USINT     |        |         |        | •       |

| 18           | ConfigOutput03 (input filter)              | USINT     |        |         |        | •       |

| ommunicati   | on                                         |           |        |         |        |         |

| 0            | Input state of digital inputs 1 to 16      | UINT      | •      |         |        |         |

|              | DigitalInput01                             | Bit 0     |        |         |        |         |

|              |                                            |           |        |         |        |         |

|              | DigitalInput16                             | Bit 15    |        |         |        |         |

| 2            | Switching state of digital outputs 1 to 16 | UINT      |        |         | •      |         |

|              | DigitalOutput01                            | Bit 0     |        |         |        |         |

|              |                                            |           |        |         |        |         |

|              | DigitalOutput16                            | Bit 15    |        |         |        |         |

| 30           | Status of digital outputs 1 to 16          | UINT      | •      |         |        |         |

|              | StatusDigitalOutput01                      | Bit 0     |        |         |        |         |

|              |                                            |           |        |         |        |         |

|              | StatusDigitalOutput16                      | Bit 15    |        |         |        |         |

| 26           | Input latch - Rising edges 1 to 8          | USINT     | •      |         |        |         |

|              | InputLatch01                               | Bit 0     |        |         |        |         |

|              |                                            |           |        |         |        |         |

|              | InputLatch08                               | Bit 7     |        |         |        |         |

| 27           | Input latch - Rising edges 9 to 16         | USINT     | •      |         |        |         |

|              | InputLatch09                               | Bit 0     |        |         |        |         |

|              |                                            |           |        |         |        |         |

|              | InputLatch16                               | Bit 7     |        |         |        |         |

| 28           | Acknowledgment - Input latch 1 to 8        | USINT     |        |         | •      |         |

|              | QuitInputLatch01                           | Bit 0     |        |         |        |         |

|              |                                            |           |        |         |        |         |

|              | QuitInputLatch08                           | Bit 7     |        |         |        |         |

| 29           | Acknowledgment - Input latch 9 to 16       | USINT     |        |         | •      |         |

|              | QuitInputLatch09                           | Bit 0     |        |         |        |         |

|              |                                            |           |        |         |        |         |

|              | QuitInputLatch16                           | Bit 7     |        |         |        |         |

| 4            | Counter01                                  | UINT      | •      |         |        |         |

| 6            | Counter02                                  | UINT      | •      |         |        |         |

| 20           | Reset counter 1                            | USINT     |        |         | •      |         |

|              | ResetCounter01                             | Bit 5     |        |         |        |         |

| 22           | Reset counter 2                            | USINT     |        |         | •      |         |

|              | ResetCounter02                             | Bit 5     |        |         |        |         |

| 8192         | asy_ModulID                                | UINT      |        | •       |        |         |

| 8196         | asy_SupplyStatus                           | USINT     |        | •       |        |         |

| 8208         | asy_SupplyInput                            | USINT     |        | •       |        |         |

| 8210         | asy_SupplyOutput                           | USINT     |        | •       |        |         |

## 11.4 Function model 254 - Bus controller

| Register      | Offset1) | Name                                       | Data type | Read   |         | Write  |         |

|---------------|----------|--------------------------------------------|-----------|--------|---------|--------|---------|

|               |          |                                            |           | Cyclic | Acyclic | Cyclic | Acyclic |

| Configuration |          |                                            |           |        |         |        |         |

| 16            | -        | ConfigIOMask01                             | USINT     |        |         |        | •       |

| 17            | -        | ConfigIOMask02                             | USINT     |        |         |        | •       |

| 20            | -        | ConfigOutput01 (counter channel 1)         | USINT     |        |         |        | •       |

| 22            | -        | ConfigOutput02 (counter channel 2)         | USINT     |        |         |        | •       |

| 18            | -        | ConfigOutput03 (input filter)              | USINT     |        |         |        | •       |

| ommunication  | า        |                                            |           |        |         |        |         |

| 0             | 0        | Input state of digital inputs 1 to 16      | UINT      | •      |         |        |         |

|               |          | DigitalInput01                             | Bit 0     |        |         |        |         |

|               |          |                                            |           |        |         |        |         |

|               |          | DigitalInput16                             | Bit 15    |        |         |        |         |

| 2             | 2        | Switching state of digital outputs 1 to 16 | UINT      |        |         | •      |         |

|               |          | DigitalOutput01                            | Bit 0     |        |         |        |         |

|               |          |                                            |           |        |         |        |         |

|               |          | DigitalOutput16                            | Bit 15    |        |         |        |         |

| 30            | -        | Status of digital outputs 1 to 16          | UINT      | •      |         |        |         |

|               |          | StatusDigitalOutput01                      | Bit 0     |        |         |        |         |

|               |          |                                            |           |        |         |        |         |

|               |          | StatusDigitalOutput16                      | Bit 15    |        |         |        |         |

| 26            | -        | Input latch - Rising edges 1 to 8          | USINT     | •      |         |        |         |

|               |          | InputLatch01                               | Bit 0     |        |         |        |         |

|               |          |                                            |           |        |         |        |         |

|               |          | InputLatch08                               | Bit 7     |        |         |        |         |

| 27            | _        | Input latch - Rising edges 9 to 16         | USINT     | •      |         |        |         |

|               |          | InputLatch09                               | Bit 0     |        |         |        |         |

|               |          |                                            |           |        |         |        |         |

|               |          | InputLatch16                               | Bit 7     |        |         |        |         |

| 28            | _        | Acknowledgment - Input latch 1 to 8        | USINT     |        |         | •      |         |

|               |          | QuitInputLatch01                           | Bit 0     |        |         |        |         |

|               |          |                                            |           |        |         |        |         |

|               |          | QuitInputLatch08                           | Bit 7     |        |         |        |         |

| 29            |          | Acknowledgment - Input latch 9 to 16       | USINT     |        |         | •      |         |

|               |          | QuitInputLatch09                           | Bit 0     |        |         | -      |         |

|               |          |                                            |           |        |         |        |         |

|               |          | QuitInputLatch16                           | Bit 7     |        |         |        |         |

| 4             |          | Counter01                                  | UINT      |        | •       |        |         |

| 6             |          | Counter02                                  | UINT      |        | •       |        |         |

| 20            |          | Reset counter 1                            | USINT     |        | -       | •      |         |

|               |          | ResetCounter01                             | Bit 5     |        |         |        |         |

| 22            |          | Reset counter 2                            | USINT     |        |         | •      |         |

|               |          | ResetCounter02                             | Bit 5     |        |         |        |         |

| 8192          | _        | asy ModulID                                | UINT      |        | •       |        |         |

| 8196          |          | asy_SupplyStatus                           | USINT     |        | •       |        |         |

| 8208          |          | asy_SupplyInput                            | USINT     |        | •       |        |         |

| 8210          | <u> </u> | asy SupplyOutput                           | USINT     |        | •       |        |         |

<sup>1)</sup> The offset specifies the position of the register within the CAN object.

## 11.4.1 Using the module on the bus controller

Function model 254 "Bus controller" is used by default only by non-configurable bus controllers. All other bus controllers can use other registers and functions depending on the fieldbus used.

For detailed information, see section "Additional information - Using I/O modules on the bus controller" in the X67 user's manual (version 3.30 or later).

#### 11.4.2 CAN I/O bus controller

The module occupies 2 digital logical slots on CAN I/O.

# 11.5 Configuration

#### 11.5.1 I/O mask 1 to 8

Name:

ConfigIOMask01

Channels are configured as inputs/outputs in this register. It also determines whether output monitoring or filtering is applied to the channels. Outputs are monitored but not filtered.

# Information:

In counter operation, channels 1 to 4 can only be configured as inputs.

| Data type | Values                 | Bus controller default setting |

|-----------|------------------------|--------------------------------|

| USINT     | See the bit structure. | 0                              |

#### Bit structure:

| Bit | Description                          | Value | Information                                          |

|-----|--------------------------------------|-------|------------------------------------------------------|

| 0   | Channel 1 configured as input/output | 0     | Configured as input (bus controller default setting) |

|     |                                      | 1     | Configured as output                                 |

|     |                                      |       |                                                      |

| 7   | Channel 8 configured as input/output | 0     | Configured as input (bus controller default setting) |

|     |                                      | 1     | Configured as output                                 |

#### 11.5.2 I/O mask 9 to 16

Name:

ConfigIOMask02

Channels are configured as inputs/outputs in this register. It also determines whether output monitoring or filtering is applied to the channels. Outputs are monitored but not filtered.

| Data type | Values                 | Bus controller default setting |

|-----------|------------------------|--------------------------------|

| USINT     | See the bit structure. | 0                              |

#### Bit structure:

| Bit | Description                           | Value | Information                                          |

|-----|---------------------------------------|-------|------------------------------------------------------|

| 0   | Channel 9 configured as input/output  | 0     | Configured as input (bus controller default setting) |

|     |                                       | 1     | Configured as output                                 |

|     |                                       |       |                                                      |

| 7   | Channel 16 configured as input/output | 0     | Configured as input (bus controller default setting) |

|     |                                       | 1     | Configured as output                                 |

## 11.5.3 Input filter

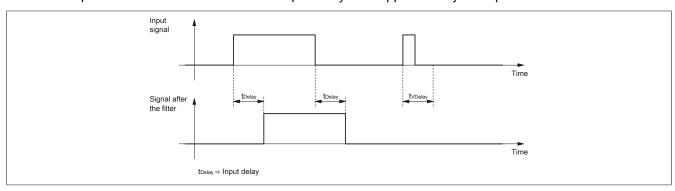

An input filter is available for each input. The input delay can be set using register "ConfigOutput03" on page 17. Disturbance pulses which are shorter than the input delay are suppressed by the input filter.

#### 11.5.3.1 Digital input filter

Name:

ConfigOutput03

This register can be used to specify the filter value for all digital inputs.

The filter value can be configured in steps of 100  $\mu$ s. It makes sense to enter values in steps of 2, however, since the input signals are sampled every 200  $\mu$ s.

| Data type | Value                                                 | Filter                                          |

|-----------|-------------------------------------------------------|-------------------------------------------------|

| USINT     | 0 No software filter (bus controller default setting) |                                                 |

|           | 2                                                     | 0.2 ms                                          |

|           |                                                       |                                                 |

|           | 250                                                   | 25 ms - Higher values are limited to this value |

#### 11.5.4 Configuration of Counter Channels 1 and 2

Name:

ConfigOutput01 to ConfigOutput02

ResetCounter01 to ResetCounter02

Counter channels 1 and 2 are configured in this register.

| Data type | Values                 | Bus controller default setting |

|-----------|------------------------|--------------------------------|

| USINT     | See the bit structure. | 0                              |

#### Bit structure:

| Bit   | Description                                                 | Value      | Information                                                 |

|-------|-------------------------------------------------------------|------------|-------------------------------------------------------------|

| 0 - 2 | Configuration of the counter frequency (only with gate mea- | 000        | Counter frequency = 48 MHz (bus controller default setting) |

|       | surement)                                                   | 001 C      | Counter frequency = 3 MHz                                   |

|       |                                                             | 010        | Counter frequency = 187.5 kHz                               |

|       |                                                             | 011 to 111 | Reserved                                                    |

| 3 - 4 | Reserved                                                    | 0          |                                                             |

| 5     | ResetCounter0x                                              | 0          | No affect on counter (bus controller default setting)       |

|       |                                                             | 1          | Delete counter                                              |

| 6 - 7 | Configuration of the operating mode                         | 0          | Event counter operation (Bus controller default setting)    |

|       |                                                             | 1          | Gate measurement                                            |

#### **Event counter operation**

The falling edges are registered on the counter input.

The counter status is collected with a fixed offset to the network cycle and transferred in the same cycle.

#### **Gate measurement**

## Information:

Only one of the counter channels at a time can be used for gate measurement.

The time of rising to falling edges for the gate input is registered using an internal frequency. The result is checked for overflow (0xFFFF).

The recovery time between measurements must be >100 µs.

The measurement result is transferred with the falling edge to the result memory.

#### 11.6 Communication