# PSoC™ Automotive Multitouch generation 6L slider

#### **Features**

- Automotive Electronics Council (AEC)-Q100 qualified

- Multitouch capacitive slider controller

- 32-bit Arm® Cortex® CPU

- Register-configurable

- Noise-suppression technologies for EMI

- Effective 20-V drive for higher signal-to-noise ratio (SNR)<sup>[1]</sup>

- · Auto armor technology improves both electromagnetic emissions and immunity

- Water rejection and wet-finger tracking using dual sense capability

- Multitouch glove with automatic mode switching

- Ten fingers with thin glove (≤ 1 mm thick)

- Two fingers with thick glove (≤5 mm thick)

- Up to 3 TX configuration supported

- Large object rejection

- Supports 1 TX single layer configuration

- Automatic baseline tracking to environmental changes

- Low-power look-for-touch mode

- Field upgrades via bootloader

- Infineon Manufacturing Test Kit (MTK)

- Slider sensor self-test

- Low-power CAPSENSE™ wake-up button with power consumption of 50 μA

- System performance (configuration dependent)

- Up to 48 sense pins, 135 intersections (45 RX and 3TX)

- Swipe speed of up to 1000 mm/s

- Reports up to ten fingers

- Small finger support down to 4 mm

- Support up to 10 capacitive sensing buttons

- Refresh rate up to 250 Hz; other rates configurable

- TX frequency up to 350 kHz

#### Note

1. Effective voltage when using 17 multi-phase TX and 5-V V<sub>CCTX</sub> supply.

#### **Features**

- Power (configuration-dependent)

- 1.71 V to 1.95 V and 3.0 V to 5.5 V logic and digital I/Os supply

- 3.0 V to 5.5 V analog supply

- 9 mW average power

- 11 μW typical Deep Sleep power

- Sensor and system design (configuration-dependent)

- Supports a variety of slider sensors and stackups

- Manhattan, diamond

- Plastic (PET) and glass-sensor substrates

- Metal mesh

- · Communication interface

- I<sup>2</sup>C slave at 100 and 400 kbps

- SPI slave bit rates up to 8 Mbps

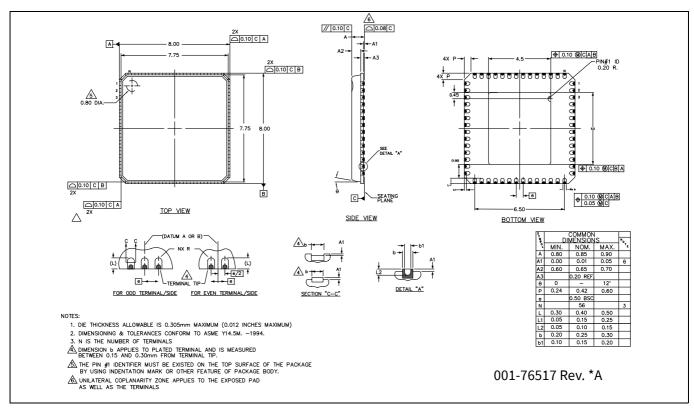

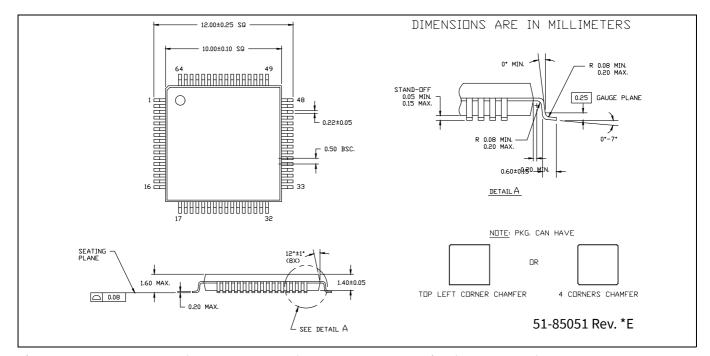

- Package

- 56-lead QFN wettable flank, 8 × 8 × 1 mm, 0.5 mm pin-pitch

- 64-lead TQFP 10 × 10 × 1.4 mm, 0.5 mm pin-pitch

- Ambient temperature range

- Automotive-A: -40°C to 85°C

- Automotive-S: -40°C to 105°C

Table of contents

### Table of contents

| Features                                              | •••••          |

|-------------------------------------------------------|----------------|

| Table of contents                                     | •••••          |

| 1 Slider system overview                              |                |

| 2 CYAT6165X overview                                  |                |

| 3 Features overview                                   |                |

| 3.1 Auto armor technology                             |                |

| 3.2 Water rejection                                   |                |

| 3.3 Wet-finger tracking                               |                |

| 3.4 Glove                                             |                |

| 3.5 Automatic mode switching                          |                |

| 3.6 Large finger tracking                             |                |

| 3.7 Large object detection and rejection              |                |

| 3.8 Look-for-Touch                                    |                |

| 4 Slider system specifications                        |                |

| 4.1 System performance specifications                 |                |

| 5 System design options                               |                |

| 5.1 CAPSENSE™ button/FPC support                      |                |

| 5.2 Sensors                                           |                |

| 6 Power supply information                            |                |

| 6.1 Required external components                      |                |

| 6.2 Voltage coefficient                               |                |

| 7 Power states summary                                |                |

| 8 Pin information                                     |                |

| 9 Electrical Specifications                           |                |

| 9.1 Absolute maximum ratings                          |                |

| 9.2 Operating temperature                             |                |

| 9.3 DC specifications                                 |                |

| 9.3.1 Flash specifications                            |                |

| 9.3.2 Chip-level DC specifications                    |                |

| 9.3.3 I/O port 0 (P0[0:1]) DC specifications          |                |

| 9.3.4 I/O port 1 (P1[0:3]) and XRES DC specifications |                |

| 9.4 AC specifications                                 | 2              |

| 9.4.1 SWD interface AC specifications                 |                |

| 9.4.2 Chip-level AC specifications                    |                |

| 9.4.3 I2C specifications                              | 2              |

| 9.4.4 SPI specifications                              | 3              |

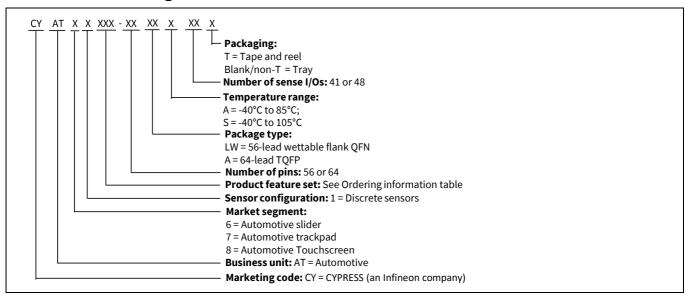

| 10 Packaging information                              | 3              |

| 10.1 Thermal impedance and moisture sensitivity       | 3              |

| 10.2 Solder reflow specifications                     | 3              |

| 11 Ordering information                               | 3              |

| 11.1 Ordering code definitions                        | 3              |

| 12 Acronyms                                           | 3              |

| 13 Reference documents                                | 30             |

| 14 Document conventions                               | 3 <sup>-</sup> |

| 14.1 Units of measure                                 |                |

| 14.2 Port nomenclature                                |                |

|                                                       |                |

| 15 Glossary                                           | 3              |

2024-07-30

Slider system overview

# 1 Slider system overview

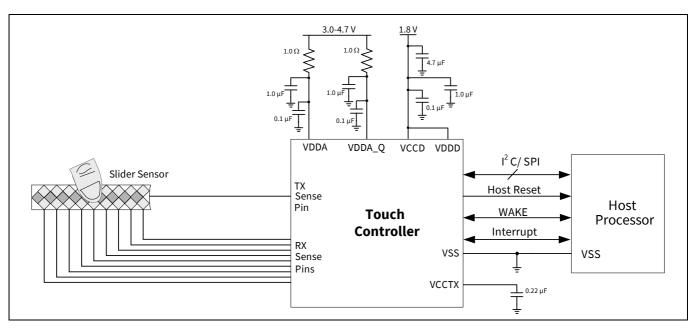

Figure 1 CYAT6165X typical system diagram

**PSoC™** Automotive Multitouch generation 6L slider

2 CYAT6165X overview

A capacitive slider detects changes in capacitance to determine the location of one or more fingers on the surface of the slider. A typical slider system consists of a capacitive slider sensor, an FPC bonded to the sensor, and the slider controller mounted on the FPC. The FPC connects the slider controller to the host processor. Users can interact with the user interface through finger movements and gestures on the surface of the slider.

CYAT6165X is a capacitive slider controller with the sensing and processing technology to resolve the locations and report the positions of up to ten fingers on the slider. The slider controller converts an array of sensor capacitances into an array of digital values, which are processed by touch-detection and position-resolution algorithms in the controller. These algorithms determine the location and signal magnitude of each finger on the slider.

Infineon provides:

CYAT6165X overview

- Application firmware

- · Design guidance for the sensor and FPC

- Slider sensor MTK

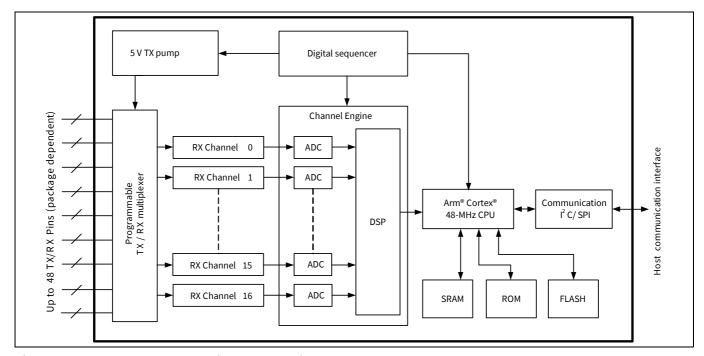

The CYAT6165X functional block diagram is shown in Figure 2. This device contains a high-performance Arm® 32-bit CPU with an integrated hardware multiply unit. This CPU controls all sensing and processing of measured capacitance results to allow tracking and reporting touches. The controller is optimized for low power and fast response time, with built-in support for manufacturing test. The slider controller communicates with a host through an I<sup>2</sup>C slave interface at up to 400 kbps or an SPI interface at up to 8 Mbps.

CYAT6165X collects the slider sensor information using the touch subsystem. This touch subsystem consists of a 5 V TX pump, TX drivers, RX channels, and a programmable transmit/receive (TX/RX) multiplexer. The multiplexer electrically connects the analog front end of each RX channel and TX driver to the appropriate row and column electrodes of the slider sensor.

The controller TX/RX multiplexer allows flexibility of chip placement on the FPC. All pins connecting to the slider sensor are programmable as either TX or RX.

Infineon reference documents are available under NDA through your local Infineon sales representative or write to automotive@infineon.com.

Figure 2 CYAT6165X functional block diagram

infineon

Features overview

#### 3 Features overview

#### 3.1 Auto armor technology

The auto armor technology improves both electromagnetic emissions and immunity. It ensures no false finger touches when CYAT6165X is exposed to electromagnetic waves.

#### 3.2 Water rejection

The water droplets can cause false touches to be reported. However, CYAT6165X continues to operate in the presence of water droplets or condensation. CYAT6165X enables water rejection using dual sense, Infineon's patented self- and mutual-capacitance sensing ability.

#### 3.3 Wet-finger tracking

In a slider system, moisture on fingers can cause false touches to be reported and make tracking of fingers across the slider difficult. CYAT6165X can detect and track fingers that are wet and enable more robust functionality of the slider, using dual sense. This includes sweaty fingers touching the slider or fingers moving across a mist-covered slider.

#### 3.4 Glove

CYAT6165X detects and tracks gloved fingers. Glove support allows navigating the slider without having to remove gloves or without the use of expensive conductive gloves. Tracking of gloved fingers is supported by automatic mode switching, which automatically transitions between tracking gloved fingers and other touch-tracking modes. Ten-finger glove-touch is supported for thin gloves ( $\leq 1$  mm thick) and two-finger operation is supported for thick gloves ( $\leq 5$  mm thick).

#### 3.5 Automatic mode switching

CYAT6165X supports automatic mode switching which detects and tracks a new touch object type without requiring manual selection of the touch type from the user. Automatic mode switching allows an uninterrupted user experience when switching between a bare finger, gloved finger, fingernail, or wet finger.

#### 3.6 Large finger tracking

A well-designed slider system must correctly report a large finger or thumb as only a single touch. If this is not supported, a large finger can incorrectly be reported as two or more touches, hampering the user experience. When an object, such as a thumb, is pressed against the slider sensor, CYAT6165X ensures that only one touch is reported at the center of the object.

### 3.7 Large object detection and rejection

It is important to be able to detect the presence of a large object on the slider sensor. CYAT6165X can determine the presence of a large object, such as a fist or palm, from the slider data. This presence may either be rejected or reported to the host.

#### 3.8 Look-for-touch

The look-for-touch is a low-power and fast-wakeup mode, in which the slider sensor is measured for an increase in self-capacitance. An increase in self-capacitance indicates that a touch is present. Because it is only necessary to detect a finger's presence, and not location, the sensing can be done at a much lower SNR, requiring less time and power. Look-for-touch sensing is used to implement multiple functions, including wake-on-touch and fast first-touch response.

#### PSoC™ Automotive Multitouch generation 6L slider

infineon

Slider system specifications

### 4 Slider system specifications

This section specifies the slider system performance delivered by CYAT6165X. For definitions, justification of parameters, and test methodologies, refer to the Infineon specification **PSoC™ Automotive Multitouch touchscreen controller user interface performance definitions (001-49389)**<sup>[2]</sup>.

#### 4.1 System performance specifications

The system performance specifications in **Table 1**<sup>[3]</sup> and **Table 2**<sup>[4]</sup> are valid under these conditions:  $-40^{\circ}\text{C} \leq \text{T}_{A} \leq 85^{\circ}\text{C}^{[5]}$  for Grade-A devices,  $-40^{\circ}\text{C} \leq \text{T}_{A} \leq 105^{\circ}\text{C}^{[5]}$  for Grade-S devices;  $1.71 \text{ V} \leq \text{V}_{\text{DDD}} \leq 1.95 \text{ V}$  or  $3.0 \text{ V} \leq \text{V}_{\text{DDD}} \leq 5.5 \text{ V}$ ,  $1.71 \text{ V} \leq \text{V}_{\text{CCD}} \leq 1.95 \text{ V}$ ,  $3.0 \text{ V} \leq \text{V}_{\text{DDA}} \leq 5.5 \text{ V}$ , unless otherwise noted. Typical values are specified at  $\text{T}_{A} = 25^{\circ}\text{C}$ ,  $\text{V}_{\text{DDD}} = \text{V}_{\text{CCD}} = 1.8 \text{ V}$ , core low dropout regulator (LDO) disabled, and  $\text{V}_{\text{DDA}} = 3 \text{ V}$ , unless otherwise noted. Data is validated using 1 TX configuration, 5-mm electrode pitch. Contact the local Infineon sales representative for information on the system performance conditions to guarantee the specifications in **Table 1**. The performance conditions and specifications are valid only for sensors approved by Infineon for use with CYAT6165X and produced by qualified Infineon partners.

Contact automotive@infineon.com to discuss any deviations.

Table 1 Typical system performance specifications (Configuration dependent)

| Category | Conditions               | Core | Unit |

|----------|--------------------------|------|------|

| Accuracy | 6–12 mm diameter finger  | 0.5  |      |

|          | Glove (≤1 mm thick)      | 2    | mm   |

|          | Glove (1 < thick ≤ 5 mm) | 4    |      |

#### **Notes**

- 2. Infineon reference documents are available under NDA through your local Infineon sales representative. You can also direct your requests to **automotive@infineon.com**.

- 3. Typical, as represented by 85% of the sample data measured. Accuracy is measured at points across the entire panel at 1.1 mm intervals.

- 4. Typical, as represented by the average values from the Infineon specification, PSoC™ Automotive Multitouch touchscreen controller user interface performance definitions (001-49389).

- 5. System performance specifications are dependent on the combination of slider controller, display, slider, and environment noise and temperature. Infine on guarantees the performance of the touch controller over this temperature range, but system performance may be impacted by the response of these other elements.

Slider system specifications

Table 2

System performance specifications (Configuration dependent)

| Category                       | Description                                            | Conditions                                                                                        | Min     | Тур | Max                | Unit |

|--------------------------------|--------------------------------------------------------|---------------------------------------------------------------------------------------------------|---------|-----|--------------------|------|

| Jitter                         | Delta in reported X, Y position, for non-moving finger | 5–12 mm diameter finger                                                                           | -       | 0.5 | -                  | mm   |

| Refresh rate                   | -                                                      | One finger on panel                                                                               | 60      | 200 | 250 <sup>[6]</sup> | Hz   |

| Response<br>time               | Active response time                                   | First finger down                                                                                 | _       | -   | 30                 | ms   |

| Swipe speed                    | -                                                      | _                                                                                                 | -       | 300 | 1000               | mm/s |

| Low power<br>wake-up<br>button | Power consumption                                      | 3.3 V, 100 ms scan rate                                                                           | -       | 50  | -                  | μΑ   |

|                                | In Active state                                        | 1 finger, 60 Hz refresh rate                                                                      | - 0.5 - | 180 |                    |      |

| Power                          | In Active look-for-touch state                         | -                                                                                                 | _       | -   | 30                 | mW   |

|                                | Average power <sup>[7]</sup>                           | Active state for 25% of<br>touch activity and in<br>Deep Sleep state for<br>75% of touch activity | _       | 9   | -                  |      |

|                                | In Deep Sleep state                                    | -                                                                                                 | -       | 11  | -                  | μW   |

#### **Notes**

<sup>6.</sup> Requires setting TX pulses for mutual-cap and self-cap to 8 and no noise in the environment.

<sup>7.</sup> See "Power states summary" on page 15 for power state transition details and refresh interval configuration for each state. Average power is the power consumed during the active and Deep Sleep states, and is calculated using this equation: (0.25 × 120 mW) + (0.75 × 0.030 mW) = 30 mW.

System design options

### 5 System design options

### **5.1** CAPSENSE™ button/FPC support

The CYAT6165X controller supports a maximum of 10 physical CAPSENSE™ buttons.

Detailed FPC development guidelines, including EMI shielding, are available in the **PSoC™ Automotive**Multitouch touchscreen controller module design best practices (001-50467).

#### 5.2 Sensors

Infineon supports the following sensor patterns:

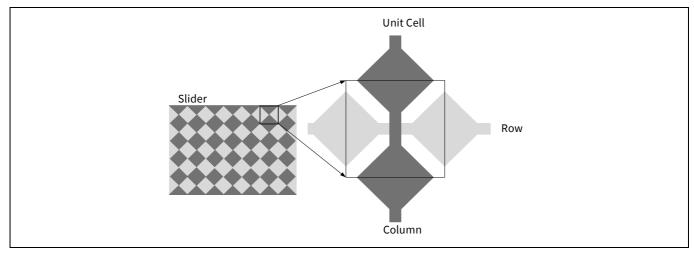

- Single-solid diamond (SSD)

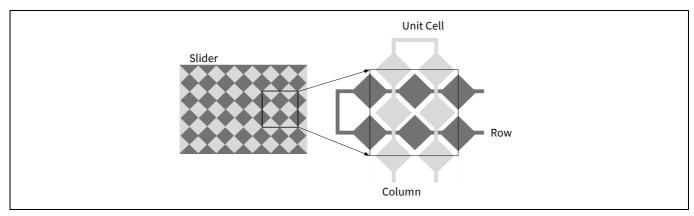

- Dual-solid diamond (DSD)

- Manhattan-3 (MH3)

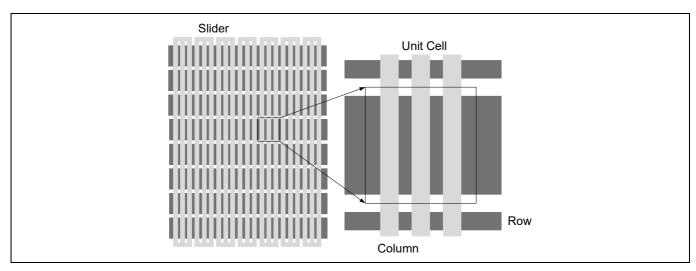

Figure 3 through Figure 5 show examples of SSD, DSD, and MH3 sensor patterns and unit cells.

Figure 3 Single-solid diamond pattern and unit cell

Figure 4 Dual-solid diamond unit cell

infineon

System design options

Figure 5 Manhattan-3 pattern and unit cell

Infineon continues to develop additional patterns and materials to increase performance and decrease system cost.

The specific sensor pattern used varies based on the mechanical, electrical, optical, and cost constraints; all of these factors must be considered for an optimal solution.

Following is an example:

• Overlays/lens thickness < 1 mm should not use SSD due to large signal disparity (SD).

To learn more about how to design sensors using stackups and materials, see the **PSoC™ Automotive Multitouch touchscreen controller module design best practices (001-50467)**.

infineon

Power supply information

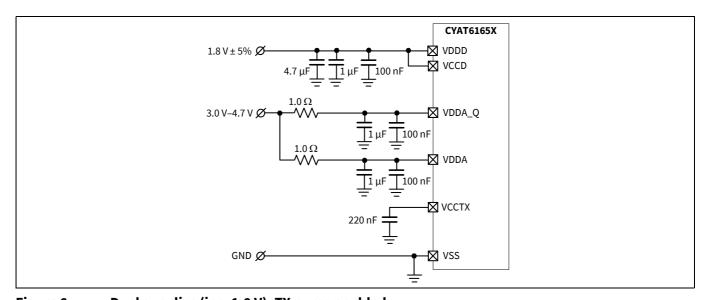

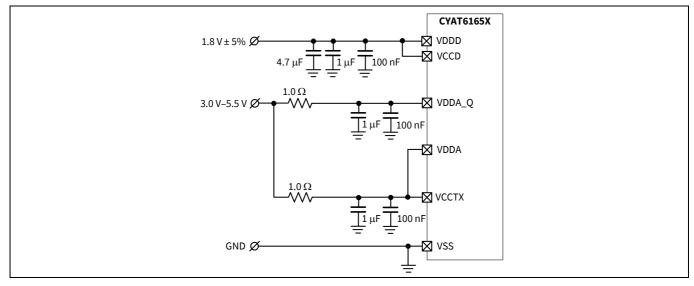

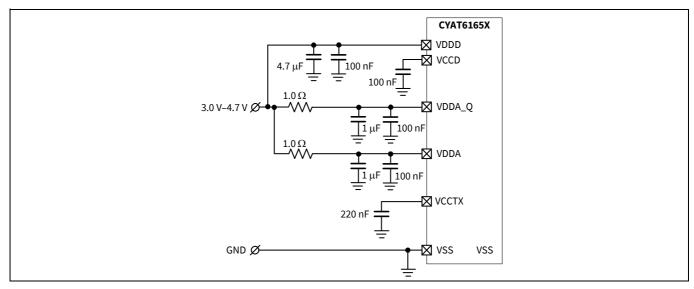

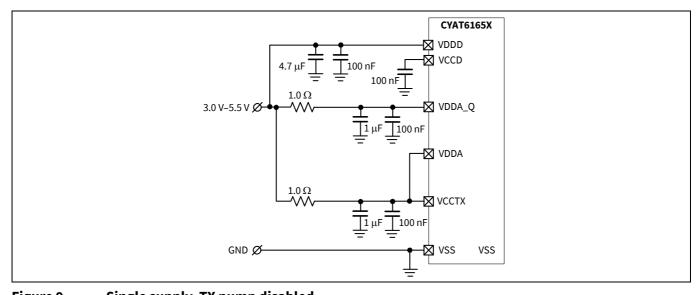

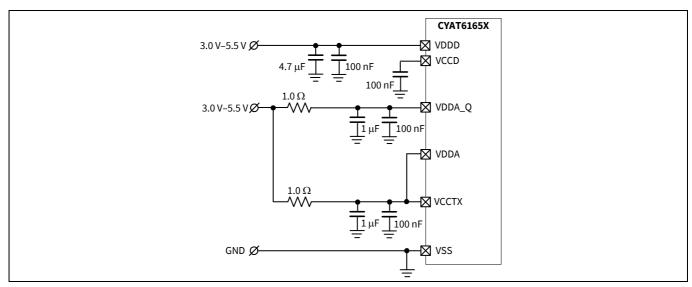

### **6** Power supply information

CYAT6165X contains four power pins: VDDA, VDDA\_Q, VDDD, and VCCD. VDDA supplies power to the chip's analog circuitry, TX pump, and drivers. VDDA\_Q supplies power to the RX analog circuitry. VDDD supplies power to the digital I/Os, core LDO regulator, supply monitors, and external reset circuitry (XRES). VCCD supplies power to the CPU core, and may be configured as an input or output, depending on if a 1.71 V–1.95 V V<sub>DDD</sub> supply is used.

#### 6.1 Required external components

The touch controller requires external components for proper device operation. Quantities are dependent on the power supply configuration used. External capacitors require an X5R dielectric characteristic or better. It is recommended to use an X7R dielectric characteristic or better for high-frequency  $0.1 \,\mu\text{F}/0.22 \,\mu\text{F}$  capacitors.

#### VDDA:

- 1.0 Ω, 5% tolerance resistor

- 0.1 μF capacitor

- 1 μF capacitor (2.2 μF in high low-frequency noise)

#### VDDA Q:

- 1.0 Ω, 5% tolerance resistor

- 0.1 μF capacitor

- 1 μF capacitor (2.2-μF in high low-frequency noise)

#### VDDD:

- 0.1 μF capacitor

- 4.7 μF capacitor

#### VCCD:

• 0.1 μF capacitor

#### **VCCTX:**

• 0.22 μF capacitor (configurations with the VCCTX pump enabled)

Power supply information

#### 6.2 Voltage coefficient

The actual capacitance of external capacitors may be reduced with higher bias voltage. Check the capacitor datasheet for the voltage coefficient. Capacitors used for power supply decoupling or filtering are operated under a continuous DC-bias. Many capacitors used with DC power across them provide less than their target capacitance, and their capacitance is not constant across their working voltage range. When selecting capacitors for use with this device verify that the selected components provide the required capacitance under the specific operating conditions of temperature and voltage used in your design. While the temperature ratings of a capacitor are normally found as part of its catalog part number (for example, X7R, C0G, Y5V), the matching voltage coefficient may only be available on the component datasheet or direct from the manufacturer. Use of components that do not provide the required capacitance under the actual operating conditions may cause the device to perform to less than the datasheet specifications.

The available power configurations, with the TX pump enabled, are shown in **Figure 6** and **Figure 8**. **Figure 7**, **Figure 9**, and **Figure 10** show power supply configurations with the TX pump disabled.

Figure 6 Dual supplies (inc. 1.8 V), TX pump enabled

Figure 7 Dual supplies (inc. 1.8 V), TX pump disabled

Power supply information

Figure 8 Single supply, TX pump enabled

Figure 9 Single supply, TX pump disabled

Power supply information

Figure 10 Dual supplies (no 1.8 V), TX pump disabled

Power states summary

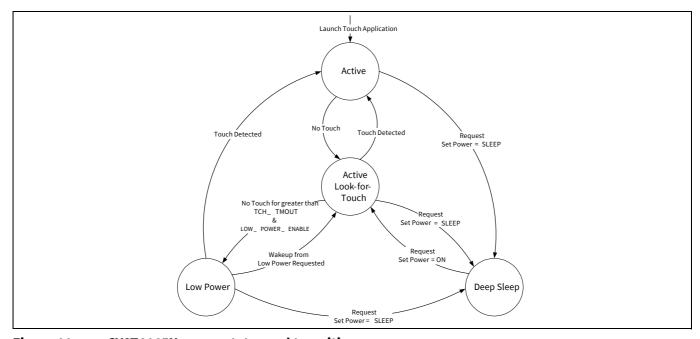

### 7 Power states summary

The CYAT6165X controller has four power states, illustrated in Figure 11:

- Active, where the slider is actively scanned to determine the presence of a touch and identify the touch coordinates.

- Active look-for-touch, where the device performs a fast self-capacitive scan to determine if a touch exists.

- Low-power, where the slider is scanned for touch presence at a much slower rate.

- Deep Sleep, where the slider is not scanned and CYAT6165X is in a Low-power state with no processing.

The CYAT6165X controller automatically manages transitions between three power states (Active, Active Look-for-touch, and Low Power). The host can force transition in and out of the fourth power state (Deepsleep).

The Active state emphasizes low refresh time for accurate finger tracking, the active look-for-touch state allows fast first-touch response, and the low power state enables low power consumption during periods of no touch activity. In all three states, the CYAT6165X controller periodically scans the panel to determine the presence of a touch. If a touch is present, the controller either enters or remains in the active state where it identifies the touch coordinates. These tasks occur at different rates in the three states and the detection of touches affects transitions between the states. Transition from Active to Active look-for-touch occurs when no touch is detected.

The host can request to disable low-power thus forcing CYAT61X controller to stay out of the Low-power state at all times for the fastest response to the first touch on the panel.

The following parameters configure power states, which can be configured by the host:

- Refresh Interval (register ACT\_INTRVL) sets the minimum time between the start of subsequent slider scans in the active state.

- Active Look-for-touch Interval (register ACT\_LFT\_INTRVL) sets the minimum refresh time in the active look-for-touch state.

- Active Mode Timeout (register TCH\_TMOUT) sets the period of time in which no touch is detected during the

active look-for-touch state before transitioning to the low power state.

- Low-Power Interval (register LP\_INTRVL) sets the time in the Low-power state between slider scans.

- Deep Sleep is entered via a command from the host to move the device into the Deep Sleep state. Automatic entry into the Low-power state is enabled by setting the LOW\_POWER\_ENABLE parameter.

Figure 11 CYAT6165X power states and transitions

#### PSoC™ Automotive Multitouch generation 6L slider

infineon

Pin information

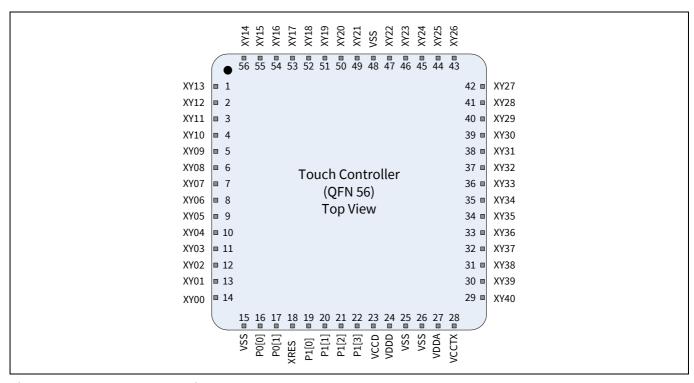

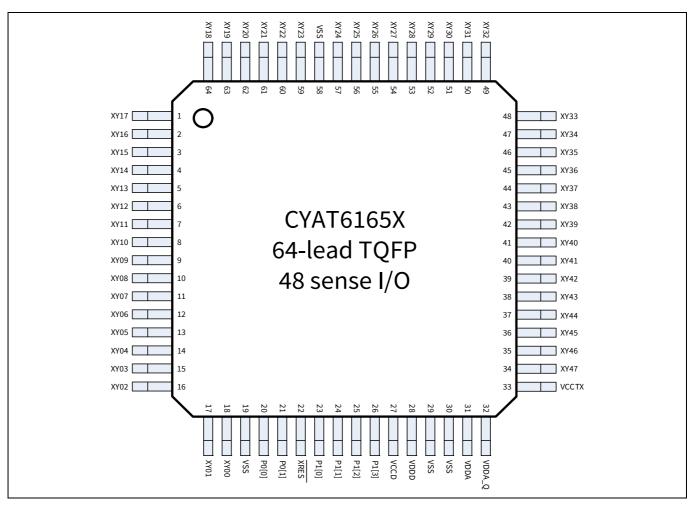

#### **8** Pin information

CYAT6165X is available in a 56-lead QFN wettable flank package and 64-lead TQFP package. This section lists pin names, descriptions, and mappings to the physical package. Input and output pins may have more than one possible configuration. Guidance for each configuration option is provided below:

XY: XY pins may be configured as either transmit (TX) drive or receive (RX) sense, allowing each design to be optimized based on the sensor pattern and layout. See PSoC™ Automotive Multitouch touchscreen controller module design best practices (001-50467), for guidelines. To configure the device for lowest power, leave unused XY pins unconnected. TX and RX pins are tied to VSS internally during the Deepsleep power state.

**P1:** Unused port 1 pin should be left unconnected.

**External Reset (XRES):** If the XRES pin is unused, it must be connected to V<sub>DDD</sub> (either directly or through an external resistor).

**SWD:** Serial wire debug (SWD) is the recommended programming mode for all designs. If SWD is not used on the target board, use the bootloader to upgrade firmware.

**COMM\_INT:** The COMM\_INT pin is required. This interrupt pin is used for the host communication. If resistive mode is used, note that all I/Os are Hi-Z during chip initialization (after XRES or bootloader exit), so an additional external resistor is recommended.

**P1[0] (WAKE):** Wake pin indicates the status of the low power wake up button.

**P1[1] (HOST RESET):** The Host reset pin is used to send a reset pulse to the host controller on specific predefined conditions.

**Pin configurations:** Multiple pin configurations are supported using the Touch Tuning Host Emulator (TTHE) software. Pins are configured using the TTHE pin configuration wizard.

infineon

Table 3 56-lead QFN pin list

| Table 3 | 30-0  | eau QFN piii | เมอเ   |                                                         |

|---------|-------|--------------|--------|---------------------------------------------------------|

| Pin     | Name  | Type         |        | Description                                             |

|         |       | Digital      | Analog | •                                                       |

| 1       | XY13  | -            | I/O    | TX/RX sense pin 13, RX channel 0                        |

| 2       | XY12  | _            | I/O    | TX/RX sense pin 12, RX channel 8                        |

| 3       | XY11  | -            | I/O    | TX/RX sense pin 11, RX channel 7                        |

| 4       | XY10  | -            | I/O    | TX/RX sense pin 10, RX channel 6                        |

| 5       | XY09  | _            | I/O    | TX/RX sense pin 09, RX channel 5                        |

| 6       | XY08  | _            | I/O    | TX/RX sense pin 08, RX channel 4                        |

| 7       | XY07  | _            | I/O    | TX/RX sense pin 07, RX channel 3                        |

| 8       | XY06  | _            | I/O    | TX/RX sense pin 06, RX channel 2                        |

| 9       | XY05  | _            | I/O    | TX/RX sense pin 05, RX channel 1                        |

| 10      | XY04  | _            | I/O    | TX/RX sense pin 04, RX channel 0                        |

| 11      | XY03  | _            | I/O    | TX/RX sense pin 03, RX channel 8                        |

| 12      | XY02  | _            | I/O    | TX/RX sense pin 02, RX channel 7                        |

| 13      | XY01  | -            | I/O    | TX/RX sense pin 01, RX channel 6                        |

| 14      | XY00  | -            | I/O    | TX/RX sense pin 00, RX channel 5                        |

| 15      | VSS   | Power        |        | Connect to ground                                       |

| 16      | P0[0] | I/O          | _      | I2C SCL / SPI SCLK                                      |

| 17      | P0[1] | I/O          | _      | I2C SDA / SPI MOSI                                      |

| 18      | XRES  | I            | _      | External active LOW reset, no internal pull-up          |

| 19      | P1[0] | I/O          | _      | SWDCLK / SPI MISO / EXT_START / WAKE                    |

| 20      | P1[1] | I/O          | _      | SWDIO / SPI SS / EXT_SYNC / HOST_RESET                  |

| 21      | P1[2] | I/O          | _      | ERROR - Set high when internal error is detected        |

| 22      | P1[3] | I/O          | _      | COMM_INT                                                |

| 23      | VCCD  | Power        |        | Digital core power supply input/output                  |

| 24      | VDDD  | Power        |        | Digital power supply input                              |

| 25      | VSS   | Power        |        | Connect to ground                                       |

| 26      | VSS   | Power        |        | Connect to ground                                       |

| 27      | VDDA  | Power        |        | Tx/Rx power supply input                                |

| 28      | VCCTX | Power        |        | TX pump reservoir and filter capacitor connection point |

| 29      | XY40  | _            | I/O    | TX/RX sense pin 40, RX channel 13                       |

| 30      | XY39  | -            | I/O    | TX/RX sense pin 39, RX channel 12                       |

| 31      | XY38  | _            | I/O    | TX/RX sense pin 38, RX channel 11                       |

| 32      | XY37  | _            | I/O    | TX/RX sense pin 37, RX channel 10                       |

| 33      | XY36  | _            | I/O    | TX/RX sense pin 36, RX channel 9                        |

| 34      | XY35  | _            | I/O    | TX/RX sense pin 35, RX channel 16                       |

| 35      | XY34  | _            | I/O    | TX/RX sense pin 34, RX channel 15                       |

| 36      | XY33  | _            | I/O    | TX/RX sense pin 33, RX channel 14                       |

| 37      | XY32  | _            | I/O    | TX/RX sense pin 32, RX channel 13                       |

| 38      | XY31  | _            | I/O    | TX/RX sense pin 31, RX channel 12                       |

|         | 1     |              | 1.     |                                                         |

Table 3 56-lead QFN pin list (continued)

| Din | Nama | Туре    |        | Description                       |

|-----|------|---------|--------|-----------------------------------|

| Pin | Name | Digital | Analog | <b>Description</b>                |

| 39  | XY30 | -       | I/O    | TX/RX sense pin 30, RX channel 11 |

| 40  | XY29 | _       | I/O    | TX/RX sense pin 29, RX channel 16 |

| 41  | XY28 | _       | I/O    | TX/RX sense pin 28, RX channel 15 |

| 42  | XY27 | _       | I/O    | TX/RX sense pin 27, RX channel 14 |

| 43  | XY26 | _       | I/O    | TX/RX sense pin 26, RX channel 13 |

| 44  | XY25 | _       | I/O    | TX/RX sense pin 25, RX channel 12 |

| 45  | XY24 | _       | I/O    | TX/RX sense pin 24, RX channel 11 |

| 46  | XY23 | _       | I/O    | TX/RX sense pin 23, RX channel 10 |

| 47  | XY22 | _       | I/O    | TX/RX sense pin 22, RX channel 9  |

| 48  | VSS  | Power   |        | Connect to ground                 |

| 49  | XY21 | _       | I/O    | TX/RX sense pin 21, RX channel 8  |

| 50  | XY20 | _       | I/O    | TX/RX sense pin 20, RX channel 7  |

| 51  | XY19 | _       | I/O    | TX/RX sense pin 19, RX channel 6  |

| 52  | XY18 | _       | I/O    | TX/RX sense pin 18, RX channel 5  |

| 53  | XY17 | -       | I/O    | TX/RX sense pin 17, RX channel 4  |

| 54  | XY16 | -       | I/O    | TX/RX sense pin 16, RX channel 3  |

| 55  | XY15 | -       | I/O    | TX/RX sense pin 15, RX channel 2  |

| 56  | XY14 | _       | I/O    | TX/RX sense pin 14, RX channel 1  |

Figure 12 56-lead QFN pinout

64-lead TQFP pin list Table 4

| Table 4 | 04-le   | 1       |        |                                                         |

|---------|---------|---------|--------|---------------------------------------------------------|

| Pin No. | Name    | Туре    |        | Description                                             |

|         | Italiic | Digital | Analog | Bescription                                             |

| 1       | XY17    | _       | I/O    | TX/RX sense pin 17, Rx channel 2                        |

| 2       | XY16    | _       | I/O    | TX/RX sense pin 16, Rx channel 1                        |

| 3       | XY15    | _       | I/O    | TX/RX sense pin 15, Rx channel 0                        |

| 4       | XY14    | _       | I/O    | TX/RX sense pin 14, Rx channel 8                        |

| 5       | XY13    | -       | I/O    | TX/RX sense pin 13, Rx channel 7                        |

| 6       | XY12    | _       | I/O    | TX/RX sense pin 12, Rx channel 6                        |

| 7       | XY11    | _       | I/O    | TX/RX sense pin 11, Rx channel 5                        |

| 8       | XY10    | _       | I/O    | TX/RX sense pin 10, Rx channel 4                        |

| 9       | XY09    | _       | I/O    | TX/RX sense pin 09, Rx channel 3                        |

| 10      | XY08    | _       | I/O    | TX/RX sense pin 08, Rx channel 2                        |

| 11      | XY07    | _       | I/O    | TX/RX sense pin 07, Rx channel 1                        |

| 12      | XY06    | -       | I/O    | TX/RX sense pin 06, Rx channel 0                        |

| 13      | XY05    | -       | I/O    | TX/RX sense pin 05, Rx channel 8                        |

| 14      | XY04    | -       | I/O    | TX/RX sense pin 04, Rx channel 7                        |

| 15      | XY03    | _       | I/O    | TX/RX sense pin 03, Rx channel 6                        |

| 16      | XY02    | _       | I/O    | TX/RX sense pin 02, Rx channel 5                        |

| 17      | XY01    | -       | I/O    | TX/RX sense pin 01, Rx channel 4                        |

| 18      | XY00    | _       | I/O    | TX/RX sense pin 00, Rx channel 3                        |

| 19      | VSS     | Power   |        | Connect to ground                                       |

| 20      | P0[0]   | I/O     | _      | I2C SCL / SPI SCLK                                      |

| 21      | P0[1]   | I/O     | _      | I2C SDA / SPI MOSI                                      |

| 22      | XRES    | 1       | _      | External active LOW reset, no internal pull-up          |

| 23      | P1[0]   | I/O     | _      | SWDCLK / SPI MISO / EXT_START /WAKE                     |

| 24      | P1[1]   | I/O     | _      | SWDIO / SPI SS / EXT_SYNC / HOST_RESET                  |

| 25      | P1[2]   | I/O     | _      | ERROR - Set high when internal error is detected        |

| 26      | P1[3]   | I/O     | _      | COMM_INT                                                |

| 27      | VCCD    | Power   |        | Digital core power supply input/output                  |

| 28      | VDDD    | Power   |        | Digital power supply input                              |

| 29      | VSS     | Power   |        | Connect to ground                                       |

| 30      | VSS     | Power   |        | Connect to ground                                       |

| 31      | VDDA    | Power   |        | Tx/Rx power supply input                                |

| 32      | VDDA_Q  | Power   |        | Tx/Rx power supply input                                |

| 33      | VCCTX   | Power   |        | TX pump reservoir and filter capacitor connection point |

| 34      | XY47    | _       | I/O    | TX/RX sense pin 47, Rx channel 16                       |

| 35      | XY46    | _       | I/O    | TX/RX sense pin 46, Rx channel 15                       |

| 36      | XY45    | _       | I/O    | TX/RX sense pin 45, Rx channel 14                       |

| 37      | XY44    | _       | I/O    | TX/RX sense pin 44, Rx channel 13                       |

| 38      | XY43    | _       | I/O    | TX/RX sense pin 43, Rx channel 12                       |

|         |         |         |        | ' ' '                                                   |

64-lead TQFP pin list (continued) Table 4

| Din No  | Nama | Туре    |        | Description                       |

|---------|------|---------|--------|-----------------------------------|

| Pin No. | Name | Digital | Analog | Description                       |

| 39      | XY42 | _       | I/O    | TX/RX sense pin 42, Rx channel 11 |

| 40      | XY41 | -       | I/O    | TX/RX sense pin 41, Rx channel 10 |

| 41      | XY40 | -       | I/O    | TX/RX sense pin 40, Rx channel 09 |

| 42      | XY39 | _       | I/O    | TX/RX sense pin 39, Rx channel 16 |

| 43      | XY38 | -       | I/O    | TX/RX sense pin 38, Rx channel 15 |

| 44      | XY37 | -       | I/O    | TX/RX sense pin 37, Rx channel 14 |

| 45      | XY36 | -       | I/O    | TX/RX sense pin 36, Rx channel 13 |

| 46      | XY35 | -       | I/O    | TX/RX sense pin 35, Rx channel 12 |

| 47      | XY34 | _       | I/O    | TX/RX sense pin 34, Rx channel 11 |

| 48      | XY33 | -       | I/O    | TX/RX sense pin 33, Rx channel 10 |

| 49      | XY32 | -       | I/O    | TX/RX sense pin 32, Rx channel 09 |

| 50      | XY31 | -       | I/O    | TX/RX sense pin 31, Rx channel 16 |

| 51      | XY30 | -       | I/O    | TX/RX sense pin 30, Rx channel 15 |

| 52      | XY29 | _       | I/O    | TX/RX sense pin 29, Rx channel 14 |

| 53      | XY28 | _       | I/O    | TX/RX sense pin 28, Rx channel 13 |

| 54      | XY27 | _       | I/O    | TX/RX sense pin 27, Rx channel 12 |

| 55      | XY26 | _       | I/O    | TX/RX sense pin 26, Rx channel 11 |

| 56      | XY25 | _       | I/O    | TX/RX sense pin 25, Rx channel 10 |

| 57      | XY24 | _       | I/O    | TX/RX sense pin 24, Rx channel 09 |

| 58      | VSS  | Power   |        | Connect to ground                 |

| 59      | XY23 | _       | I/O    | TX/RX sense pin 23, Rx channel 8  |

| 60      | XY22 | _       | I/O    | TX/RX sense pin 22, Rx channel 7  |

| 61      | XY21 | _       | I/O    | TX/RX sense pin 21, Rx channel 6  |

| 62      | XY20 | -       | I/O    | TX/RX sense pin 20, Rx channel 5  |

| 63      | XY19 | -       | I/O    | TX/RX sense pin 19, Rx channel 4  |

| 64      | XY18 | _       | I/O    | TX/RX sense pin 18, Rx channel 3  |

Figure 13 64-lead TQFP pinout

infineon

**Electrical Specifications**

### 9 Electrical Specifications

This section lists CYAT6165X DC and AC electrical specifications.

### 9.1 Absolute maximum ratings

Table 5 Absolute maximum ratings

|                                  |                                                                                                                      | 0-                               |                       |     |                                                  |                                       |

|----------------------------------|----------------------------------------------------------------------------------------------------------------------|----------------------------------|-----------------------|-----|--------------------------------------------------|---------------------------------------|

| Symbol                           | Description                                                                                                          | Conditions                       | Min                   | Тур | Max                                              | Unit                                  |

| T <sub>STG</sub>                 | Storage temperature                                                                                                  | -                                | -55                   | 25  | 125                                              | °C                                    |

| V <sub>DDD</sub>                 | Digital supply voltage                                                                                               | -                                | V <sub>SS</sub> – 0.5 | _   | 6                                                | V                                     |

| V <sub>DDA</sub>                 | Analog supply voltage                                                                                                | -                                | V <sub>SS</sub> – 0.5 | _   | 6                                                | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ |

| V <sub>DDDR</sub>                | Amplitude (V <sub>PP</sub> ) of digital (V <sub>DDD</sub> ) supply ripple riding on the DC voltage                   | DC to 20 MHz                     | -                     | _   | 100                                              |                                       |

|                                  | Amplitude (V <sub>PP</sub> ) of analog (V <sub>DDA</sub> ) supply ripple riding on the DC voltage (TX pump enabled)  | DC to 20 MHz                     | _                     | _   | 100                                              | mV                                    |

| V <sub>DDAR</sub> <sup>[8]</sup> | Amplitude (V <sub>PP</sub> ) of analog (V <sub>DDA</sub> ) supply ripple riding on the DC voltage (TX pump disabled) | DC to 150 kHz <sup>[9]</sup>     | -                     | -   | 15                                               |                                       |

|                                  |                                                                                                                      | 150 kHz <sup>[9]</sup> to 20 MHz | -                     | -   | 15 +<br>20 dB/decade<br>> 150 kHz <sup>[9]</sup> |                                       |

| V <sub>CCD</sub>                 | Core supply voltage                                                                                                  | -                                | V <sub>SS</sub> – 0.5 | -   | 2.3                                              |                                       |

|                                  | Port 0 pin voltage                                                                                                   | Driver enabled                   | V <sub>SS</sub> – 0.5 | _   | 6                                                | V                                     |

| $V_{GPIO}$                       | Port 0 pin voltage                                                                                                   | Driver disabled                  | V <sub>SS</sub> – 0.5 | _   | 7                                                | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ |

|                                  | Port 1 pin voltage                                                                                                   | -                                | V <sub>SS</sub> – 0.5 | _   | V <sub>DDD</sub> + 0.5                           |                                       |

| I <sub>IO</sub>                  | Current into I/O pin                                                                                                 | -                                | -25                   | _   | 50                                               | mA                                    |

| ESD <sub>CDM</sub>               | Electrostatic discharge voltage                                                                                      | Charge device model              | 1500                  | -   | _                                                | V                                     |

| ESD <sub>HBM</sub>               | Electrostatic discharge voltage                                                                                      | Human body model                 | 5000                  | _   | _                                                | v                                     |

### 9.2 Operating temperature

Table 6 Operating temperature

| Symbol         | Description                   | Conditions | Min | Тур | Max | Unit |

|----------------|-------------------------------|------------|-----|-----|-----|------|

| T <sub>A</sub> | Ambient temperature (A-grade) | -          | -40 | _   | 85  | °C   |

| T <sub>A</sub> | Ambient temperature (S-grade) | -          | -40 | _   | 105 |      |

#### Notes

<sup>8.</sup> Analog supply ripple specifications are valid for the supply presented to the external resistor (for example, label "V" in **Figure 6**), not at the device VDDA and VDDA\_Q pin.

<sup>9.</sup> If a 2.2-μF capacitor is used in place of a 1-μF capacitor, the threshold is 80 kHz.

infineon

**Electrical Specifications**

#### 9.3 DC specifications

The specifications in this section are valid under these conditions:  $-40^{\circ}\text{C} \le T_{\text{A}} \le 85^{\circ}\text{C}$  for Grade-A devices,  $-40^{\circ}\text{C} \le T_{\text{A}} \le 105^{\circ}\text{C}$  for Grade-S devices.

#### 9.3.1 Flash specifications

The specifications in **Table 7** are valid under these conditions:  $1.71 \text{ V} \le \text{V}_{\text{DDD}} \le 1.95 \text{ V}$  or  $3.0 \text{ V} \le \text{V}_{\text{DDD}} \le 5.5 \text{ V}$ ,  $1.71 \text{ V} \le \text{V}_{\text{CCD}} \le 1.95 \text{ V}$ , and  $3.0 \text{ V} \le \text{V}_{\text{DDA}} \le 5.5 \text{ V}$ . Typical values are specified at  $\text{T}_{\text{A}} = 25^{\circ}\text{C}$ ,  $\text{V}_{\text{DDD}} = \text{V}_{\text{CCD}} = 1.8 \text{ V}$ , core LDO disabled, and  $\text{V}_{\text{DDA}} = 3.0 \text{ V}$ .

Table 7 Flash specifications

| Symbol                | Description           | Conditions                                                                           | Min                | Тур | Max | Unit   |

|-----------------------|-----------------------|--------------------------------------------------------------------------------------|--------------------|-----|-----|--------|

| Flash <sub>ENPB</sub> | Flash write endurance | Erase/write cycles per<br>block                                                      | 10,000             | -   | -   | cycles |

| Flash <sub>DR</sub>   | Flash data retention  | Following maximum Flash write cycles (Flash <sub>ENPB</sub> ), T <sub>A</sub> ≤ 55°C | 20 <sup>[10]</sup> | _   | -   | Voars  |

|                       |                       | Following maximum Flash write cycles (Flash <sub>ENPB</sub> ), T <sub>A</sub> > 55°C | 10 <sup>[10]</sup> | -   | -   | years  |

#### Note

10. Storing programmed devices at or above the ambient temperature specified by Flash DR may reduce flash data retention time. Infineon provides a retention calculator to calculate the retention lifetime based on customer's individual temperature profiles for operation over the ambient temperature range for the device's temperature rating. For more information, contact the support team at support@infineon.com.

infineon

**Electrical Specifications**

### 9.3.2 Chip-level DC specifications

The specifications in **Table 8** are valid under these conditions:  $1.71 \text{ V} \le \text{V}_{DDD} \le 1.95 \text{ V}$  or  $3.0 \text{ V} \le \text{V}_{DDD} \le 5.5 \text{ V}$ ,  $1.71 \text{ V} \le \text{V}_{CCD} \le 1.95 \text{ V}$ , and  $3.0 \text{ V} \le \text{V}_{DDA} \le 5.5 \text{ V}$ . Typical values are specified at  $\text{T}_{A} = 25^{\circ}\text{C}$ ,  $\text{V}_{DDD} = \text{V}_{CCD} = 1.8 \text{ V}$ , core LDO disabled, and  $\text{V}_{DDA} = 3.0 \text{ V}$ .

Table 8 Chip-level DC specifications

| Symbol                           | Description                                                 | Conditions                                                                  | Min               | Тур | Max  | Unit |

|----------------------------------|-------------------------------------------------------------|-----------------------------------------------------------------------------|-------------------|-----|------|------|

| V                                | Digital supply voltage                                      | Core LDO enabled (V <sub>CCD</sub> output)                                  | 3.0               | -   | 5.5  |      |

| $V_{DDD}$                        | Digital supply voltage                                      | Core LDO disabled (V <sub>CCD</sub> input) <sup>[11]</sup>                  | 1.71              | 1.8 | 1.95 |      |

| V <sub>CCD</sub>                 | Digital core supply voltage                                 | Core LDO enabled (V <sub>CCD</sub> output)                                  | _                 | 1.8 | -    |      |

| *CCD                             | Digital core supply voltage                                 | Core LDO disabled (V <sub>CCD</sub> input) <sup>[11]</sup>                  | 1.71              | 1.8 | 1.95 | V    |

| V <sub>DDA</sub> <sup>[11]</sup> | Analog supply voltage                                       | TX pump enabled                                                             | 3.0               | _   | 4.7  |      |

| V DDA -                          | Analog supply voltage                                       | TX pump disabled                                                            | 3.0               | -   | 5.5  |      |

| V <sub>CCTX</sub>                | V <sub>CCTX</sub> supply operating voltage range            | Input to external low-pass filter, external V <sub>CCTX</sub> configuration | 3.0               | -   | 5.5  |      |

| PSA <sub>RAMP</sub>              | V <sub>DDA</sub> ramp rate from ground to minimum voltage   | _                                                                           | _                 | _   | 100  |      |

| PSD <sub>RAMP</sub>              | V <sub>DDD</sub> ramp rate from ground to minimum voltage   | -                                                                           | 1 <sup>[12]</sup> | _   | 40   | V/ms |

| PSD <sub>RAMPDOWN</sub>          | V <sub>DDD</sub> ramp down rate from 1.5 V to 1.0 V         | -                                                                           | 1 <sup>[12]</sup> | -   | 40   |      |

| I <sub>DDD_ACT</sub>             | V <sub>DDD</sub> active current                             | -                                                                           | -                 | 20  | 50   | m A  |

| I <sub>DDA_ACT</sub>             | V <sub>DDA</sub> active current                             | -                                                                           | -                 | 15  | 20   | mA   |

| I <sub>DDD_DS</sub>              | V <sub>DDD</sub> deep sleep current                         | -                                                                           | _                 | 3   | -    |      |

| I <sub>DDA_DS</sub>              | V <sub>DDA</sub> deep sleep current                         | -                                                                           | _                 | 2   | -    |      |

| ı                                | $V_{DDD}$ current, $\overline{XRES} = LOW$                  | $1.71 \text{ V} \le \text{V}_{DDD} \le 1.95 \text{ V}$                      | _                 | 5   | -    | μΑ   |

| I <sub>DDD_XR</sub>              | VDDD current, ARES - LOW                                    | $3.0 \text{ V} \leq \text{V}_{\text{DDD}} \leq 5.5 \text{ V}$               | _                 | 1   | -    |      |

| I <sub>DDA_XR</sub>              | $V_{DDA}$ current, $\overline{XRES} = LOW$                  | -                                                                           | -                 | 25  | -    |      |

| I <sub>DDD_P</sub>               | V <sub>DDD</sub> flash programming and flash verify current |                                                                             | _                 | 5   | 25   | mA   |

#### **Notes**

<sup>11.</sup>These Min and Max limits are inclusive of noise. For proper operation, V<sub>DDA</sub> or V<sub>DDD</sub> with combined noise cannot go below or above the specified min or max limits.

<sup>12.</sup>If minimum ramp rate cannot be met, XRES should be asserted during voltage ramp (1.5 V >  $V_{DDD}$  >1.0 V for ramp-down or until voltage is stable for ramp-up). Note that a glitch on the I<sup>2</sup>C bus could occur during voltage ramp in this case.

infineon

**Electrical Specifications**

### 9.3.3 I/O port 0 (P0[0:1]) DC specifications

The port 0 specifications in **Table 9** are valid under these conditions:  $1.71 \text{ V} \le \text{V}_{DDD} \le 1.95 \text{ V}$  or  $3.0 \text{ V} \le \text{V}_{DDD} \le 5.5 \text{ V}$ ,  $1.71 \text{ V} \le \text{V}_{CCD} \le 1.95 \text{ V}$ , and  $3.0 \text{ V} \le \text{V}_{DDA} \le 5.5 \text{ V}$ . Typical values are specified at  $\text{T}_A = 25^{\circ}\text{C}$ ,  $\text{V}_{DDD} = \text{V}_{CCD} = 1.8 \text{ V}$ , core LDO disabled, and  $\text{V}_{DDA} = 3.0 \text{ V}$ .

Table 9 I/O port 0 (P0[0:1]) DC specifications

| Symbol               | Description                                | Conditions                                                                                                                               | Min                    | Тур | Max                    | Unit |

|----------------------|--------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-----|------------------------|------|

|                      |                                            | CMOS mode                                                                                                                                | $0.7 \times V_{DDD}$   | _   | -                      |      |

| $V_{IH}$             | Input high voltage                         | 1.8-V mode, $V_{EXT}^{[14]} = 1.8 \text{ V},$<br>3.0 V $\leq$ V <sub>DDD</sub> $\leq$ 5.5 V                                              | $0.7 \times V_{EXT}$   | -   | -                      |      |

|                      |                                            | CMOS mode                                                                                                                                | _                      | _   | $0.3 \times V_{DDD}$   |      |

| $V_{IL}$             | Input low voltage                          | 1.8-V mode, $V_{EXT}^{[14]} = 1.8 \text{ V}$ ,<br>3.0 V $\leq$ V <sub>DDD</sub> $\leq$ 5.5 V                                             | -                      | -   | 0.3 × V <sub>EXT</sub> |      |

| V                    | High output voltage                        | Reference to $V_{DDD}$ , $I_{OH} = 1$ mA, $V_{DDD} = 1.8 \text{ V}$                                                                      | V <sub>DDD</sub> – 0.5 | -   | -                      | V    |

| V <sub>OH</sub>      | riigii output voltage                      | Reference to $V_{DDD}$ , $I_{OH} = 4$ mA,<br>$V_{DDD} = 3.0 \text{ V}$                                                                   | V <sub>DDD</sub> - 0.6 | _   | -                      |      |

| V <sub>OL</sub>      | Low output voltage                         | $V_{DDD} \ge 1.71 \text{ V, } I_{OL} = 10 \text{ mA}$                                                                                    | _                      | _   | 0.6                    |      |

| VOL                  | Low output voltage                         | $V_{DDD} \ge 1.71 \text{ V, } I_{OL} = 3 \text{ mA}$                                                                                     | _                      | _   | 0.4                    |      |

| V <sub>H</sub>       | Input hysteresis                           | -                                                                                                                                        | $0.1 \times V_{DDD}$   | _   | -                      |      |

| _                    | Output rise time Fast-Strong               | 25 pF load,<br>10%–90% V <sub>DDD</sub> = 3.3 V                                                                                          | 2                      | _   | 12                     |      |

| T <sub>RISE_OV</sub> | Output rise time<br>Slow-Strong            | 25 pF load,<br>10%–90% V <sub>DDD</sub> = 3.3 V                                                                                          | 10                     | -   | 60                     | nc   |

| т                    | Output fall time Fast-Strong               | 25 pF load,<br>10%–90% V <sub>DDD</sub> = 3.3 V                                                                                          | 1.5                    | -   | 12                     | ns   |

| T <sub>FALL_OV</sub> | Output fall time Slow-Strong               | 25 pF load,<br>10%–90% V <sub>DDD</sub> = 3.3 V                                                                                          | 10                     | -   | 60                     |      |

| I <sub>IL</sub> [13] | Input leakage current                      | $T_A = 25^{\circ}C, V_{DDD} = 3.0 \text{ V}$                                                                                             | -                      | _   | 14                     | nA   |

| III.                 | (absolute value)                           | $T_A = 25^{\circ}C, V_{DDD} = 0.0 V$                                                                                                     | _                      | _   | 10                     | μΑ   |

| C <sub>IN</sub>      | Input pin capacitance                      | Package and pin dependent T <sub>A</sub> = 25°C                                                                                          | -                      | -   | 7                      | nΓ   |

| C <sub>OUT</sub>     | Output pin capacitance                     | Package and pin dependent T <sub>A</sub> = 25°C                                                                                          | -                      | -   | 7                      | pF   |

| R <sub>INT</sub>     | Internal pull-up / pull-down<br>resistance | Pin configured for internal pull-up or pull-down; note that all I/Os are Hi-Z during chip initialization (after XRES or bootloader exit) | 3.5                    | 5.6 | 8.5                    | kΩ   |

#### Notes

<sup>13.</sup> Gang tested with all I/Os to 1  $\mu$ A.

<sup>14.</sup>V<sub>EXT</sub> is the external supply used to bias the pull-up resistor when used on an I<sup>2</sup>C bus.

infineon

**Electrical Specifications**

### 9.3.4 I/O port 1 (P1[0:3]) and XRES DC specifications

The specifications in **Table 10** are valid under these conditions:  $1.71 \text{ V} \le \text{V}_{DDD} \le 1.95 \text{ V}$  or  $3.0 \text{ V} \le \text{V}_{DDD} \le 5.5 \text{ V}$ ,  $1.71 \text{ V} \le \text{V}_{CCD} \le 1.95 \text{ V}$ , and  $3.0 \text{ V} \le \text{V}_{DDA} \le 5.5 \text{ V}$ . Typical values are specified at  $\text{T}_A = 25^{\circ}\text{C}$ ,  $\text{V}_{DDD} = \text{V}_{CCD} = 1.8 \text{ V}$ , core LDO disabled, and  $\text{V}_{DDA} = 3.0 \text{ V}$ .

Table 10 I/O port 1 (P1[0:3]) and XRES DC specifications

| Symbol                           | Description Conditions N              |                                                  | Min                    | Тур | Max                  | Unit |

|----------------------------------|---------------------------------------|--------------------------------------------------|------------------------|-----|----------------------|------|

|                                  |                                       | 1.8 V configuration                              | 1.26                   | _   | -                    |      |

| $V_{IH}$                         | Input voltage high threshold          | CMOS configuration                               | $0.7 \times V_{DDD}$   | _   | -                    |      |

|                                  |                                       | XRES                                             | 1.35                   | _   | -                    |      |

|                                  |                                       | 1.8 V configuration                              | _                      | _   | 0.54                 |      |

| $V_{IL}$                         | Input voltage low threshold           | CMOS configuration                               | _                      | _   | 0.3×V <sub>DDD</sub> |      |

|                                  |                                       | XRES                                             | _                      | _   | 0.45                 | ٧    |

| V                                | High output voltage                   | $I_{OH} = 4 \text{ mA}, V_{DDD} = 3.0 \text{ V}$ | V <sub>DDD</sub> - 0.6 | _   | -                    |      |

| $V_{OH}$                         | nigii output voitage                  | I <sub>OH</sub> = 1 mA, V <sub>DDD</sub> = 1.8 V | V <sub>DDD</sub> - 0.5 | _   | -                    |      |

| V                                | Low Output Voltage                    | $I_{OL} = 8 \text{ mA}, V_{DDD} = 3.3 \text{ V}$ | _                      | _   | 0.6                  |      |

| $V_{OL}$                         | Low Output voltage                    | I <sub>OL</sub> = 4 mA, V <sub>DDD</sub> = 1.8 V | _                      | _   | 0.6                  |      |

| $V_{H}$                          | Input hysteresis voltage              | -                                                | $0.1 \times V_{DDD}$   | _   | _                    |      |

| <b>T</b>                         | Output rise time Fast-Strong          | 25 pF load,<br>10%–90% V <sub>DDD</sub> = 3.3 V  | 2                      | _   | 12                   |      |

| T <sub>RISE_G</sub>              | Output rise time<br>Slow-Strong       | 25 pF load,<br>10%–90% V <sub>DDD</sub> = 3.3 V  | -                      | _   | 60                   | -    |

| <b>-</b>                         | Output fall time Fast-Strong          | 25 pF load,<br>10%–90% V <sub>DDD</sub> = 3.3 V  | 2                      | -   | 12                   | ns   |

| T <sub>FALL_G</sub>              | Output fall time<br>Slow-Strong       | 25 pF load,<br>10%–90% V <sub>DDD</sub> = 3.3 V  | -                      | -   | 60                   |      |

| I <sub>IL</sub> <sup>[15]</sup>  | Input leakage (absolute value)        | _                                                | -                      | -   | 2                    | nA   |

| C <sub>IN</sub>                  | Input pin capacitance                 | Package and pin dependent T <sub>A</sub> = 25°C  | -                      | -   | 7                    |      |

| C <sub>OUT</sub>                 | Output pin capacitance                | Package and pin dependent T <sub>A</sub> = 25°C  | -                      | -   | 7                    | pF   |

| R <sub>INT</sub> <sup>[16]</sup> | Internal pull-up/pull-down resistance | Pin configured for internal pull-up or pull-down | 3.5                    | 5.6 | 8.5                  | kΩ   |

#### Notes

16.XRES is input only with no internal pull-up or pull-down resistor.

<sup>15.</sup> Gang tested with all I/Os to 1  $\mu$ A.

infineon

**Electrical Specifications**

#### 9.4 AC specifications

The specifications in this section are valid under these conditions:  $-40^{\circ}\text{C} \le T_{A} \le 85^{\circ}\text{C}$  for Grade-A devices,  $-40^{\circ}\text{C} \le T_{A} \le 105^{\circ}\text{C}$  for Grade-S devices.

### 9.4.1 SWD interface AC specifications

The specifications in **Table 11** are valid under these conditions:  $1.71 \text{ V} \le \text{V}_{DDD} \le 1.95 \text{ V}$  or  $3.0 \text{ V} \le \text{V}_{DDD} \le 5.5 \text{ V}$ ,  $1.71 \text{ V} \le \text{V}_{CCD} \le 1.95 \text{ V}$ ,  $3.0 \text{ V} \le \text{V}_{DDA} \le 5.5 \text{ V}$ , and  $\text{C}_{LOAD} = 25 \text{ pF}$ . Typical values are specified at  $\text{T}_A = 25^{\circ}\text{C}$ ,  $\text{V}_{DDD} = \text{V}_{CCD} = 1.8 \text{ V}$ , core LDO disabled, and  $\text{V}_{DDA} = 3.0 \text{ V}$ .

Table 11 SWD interface AC specifications

| Symbol                  | Description                             | Conditions                                                   | Min   | Тур | Max | Unit   |

|-------------------------|-----------------------------------------|--------------------------------------------------------------|-------|-----|-----|--------|

| t                       | SWDCLK frequency                        | $3.3 \text{ V} \leq \text{V}_{\text{DDD}} \leq 5 \text{ V}$  | -     | -   | 14  | MHz    |

| <sup>†</sup> SWDCLK     | SWDCLK frequency                        | $1.71 \text{ V} \le \text{V}_{\text{DDD}} \le 3.3 \text{ V}$ | -     | _   | 8   | IVITIZ |

| T <sub>SWDI_SETUP</sub> | SWDIO input setup before<br>SWDCLK HIGH | T = 1 / f <sub>SWDCLK</sub>                                  | T / 4 | -   | -   |        |

| T <sub>SWDI_HOLD</sub>  | SWDIO input hold after<br>SWDCLK HIGH   | $T = 1 / f_{SWDCLK}$                                         | T / 4 | -   | -   | nc     |

| T <sub>SWDO_VALID</sub> | SWDCLK HIGH to SWDIO output valid       | $T = 1 / f_{SWDCLK}$                                         | -     | -   | T/2 | ns     |

| T <sub>SWDO_HOLD</sub>  | SWDIO output hold after<br>SWDCLK HIGH  | T = 1 / f <sub>SWDCLK</sub>                                  | 1     | -   | _   |        |

**Electrical Specifications**

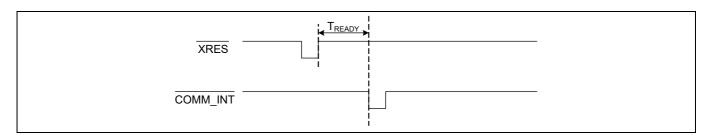

# 9.4.2 Chip-level AC specifications

The specifications in **Table 12** are valid under these conditions:  $1.71 \text{ V} \le \text{V}_{DDD} \le 1.95 \text{ V}$  or  $3.0 \text{ V} \le \text{V}_{DDD} \le 5.5 \text{ V}$ ,  $1.71 \text{ V} \le \text{V}_{CCD} \le 1.95 \text{ V}$ , and  $3.0 \text{ V} \le \text{V}_{DDA} \le 5.5 \text{ V}$ . Typical values are specified at  $\text{T}_A = 25^{\circ}\text{C}$ ,  $\text{V}_{DDD} = \text{V}_{CCD} = 1.8 \text{ V}$ , core LDO disabled, and  $\text{V}_{DDA} = 3.0 \text{ V}$ .

Table 12 Chip-level AC specifications

| Symbol                     | Description                                                       | Conditions                                 | Min | Тур | Max  | Unit |

|----------------------------|-------------------------------------------------------------------|--------------------------------------------|-----|-----|------|------|

| T <sub>XRST</sub>          | External reset<br>(XRES) pulse width                              | After V <sub>DDD</sub> is valid            | 10  | -   | _    | μs   |

| T <sub>READY</sub>         | Time from deassertion of XRES to COMM_INT                         | _                                          | -   | -   | 35   | ms   |

| T <sub>CAL</sub>           | Calibration routine execution time                                | -                                          | _   | _   | 2000 |      |

| F <sub>IMOTOL1</sub>       | Frequency<br>variation at 37 MHz<br>and 48 MHz                    | _                                          | -   | -   | ±2   | %    |

| T <sub>COMM_EXIT_CRC</sub> | Time from EXIT BTLDR command (with CRC checking) to SYS INFO MODE | POST_SHORT_OPEN_CTRL - "Disabled All" [17] | -   | 40  | -    | ms   |

Figure 14 COMM\_INT timing diagram

#### Note

17.For POST\_SHORT\_OPEN\_CTRL - "Enabled All", there will be an additional 100 ms during startup.

**Electrical Specifications**

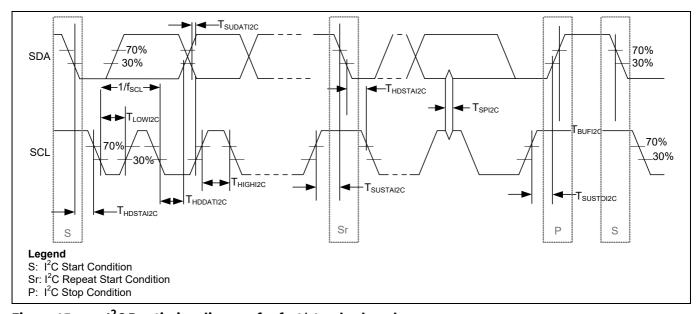

### 9.4.3 I<sup>2</sup>C specifications

The specifications in **Table 13** are valid under these conditions:  $1.71 \text{ V} \leq \text{V}_{DDD} \leq 1.95 \text{ V}$  or  $3.0 \text{ V} \leq \text{V}_{DDD} \leq 5.5 \text{ V}$ ,  $1.71 \text{ V} \leq \text{V}_{CCD} \leq 1.95 \text{ V}$ , and  $3.0 \text{ V} \leq \text{V}_{DDA} \leq 5.5 \text{ V}$ . Typical values are specified at  $\text{T}_A = 25^{\circ}\text{C}$ ,  $\text{V}_{DDD} = \text{V}_{CCD} = 1.8 \text{ V}$ , core LDO disabled, and  $\text{V}_{DDA} = 3.0 \text{ V}$ . CYAT6165X does not require a clock-stretch capable host, but is fully compatible with systems that perform clock-stretching.

To ensure proper I<sup>2</sup>C functionality in extreme bus conditions, refer to Infineon's application note **Using CY8CTMA4/5XX** I<sup>2</sup>C in systems with slow clock edges (001-81514)<sup>[18]</sup>.

**Note:** The P0[0] and P0[1] pins have I/O cells optimized for use on multi-drop buses. When the touch device is powered off, the pin drivers do not load the attached bus, such that other devices attached to them may continue to communicate.

Figure 15 I<sup>2</sup>C Bus timing diagram for fast/standard mode

#### Note

18.Extreme bus conditions are considered to be a combination of the following conditions: High-capacitive bus load, slow SCL fall time, and fast SDA rise/fall time. Infineon reference documents are available under NDA through the local Infineon sales representative. Direct any requests to **automotive@infineon.com**.

**Electrical Specifications**

AC characteristics of the I<sup>2</sup>C SDA and SCL pins Table 13

| Cumbal                | Description                                                                                              | Standard             | mode                 | Fast mode            | Unit                 |      |  |

|-----------------------|----------------------------------------------------------------------------------------------------------|----------------------|----------------------|----------------------|----------------------|------|--|

| Symbol                | Description                                                                                              | Min                  | Max                  | Min                  | Мах                  | Unit |  |

| f <sub>SCLI2C</sub>   | SCL clock frequency                                                                                      | 0                    | 100                  | 0                    | 400                  | kHz  |  |

| T <sub>HDSTAI2C</sub> | Hold time (repeated) start condition. After this period, the first clock pulse is generated.             |                      | -                    | 0.6                  | -                    |      |  |

| T <sub>LOWI2C</sub>   | LOW period of SCL clock                                                                                  | 4.7                  | _                    | 1.3                  | _                    |      |  |

| T <sub>HIGHI2C</sub>  | HIGH period of SCL clock                                                                                 | 4                    | _                    | 0.6                  | _                    | μs   |  |

| T <sub>SUSTAI2C</sub> | Setup time for repeated start condition                                                                  | 4.7                  | _                    | 0.6                  | _                    |      |  |

| T <sub>HDDATI2C</sub> | Data hold time                                                                                           | 0                    | _                    | 0                    | _                    |      |  |

| T <sub>SUDATI2C</sub> | Data setup time                                                                                          | 250                  | _                    | 100                  | _                    | ns   |  |

| T <sub>VDDATI2C</sub> | Data valid time                                                                                          | -                    | 3.45                 | -                    | 0.9                  |      |  |

| T <sub>VDACKI2C</sub> |                                                                                                          |                      | 3.45                 | _                    | 0.9                  | μs   |  |

| T <sub>SUSTOI2C</sub> | Setup time for stop condition                                                                            | 4                    | _                    | 0.6                  | _                    |      |  |

| V <sub>HH</sub>       | Input hysteresis high voltage,<br>1.71 V ≤ V <sub>DDD</sub> ≤ 1.95 V or 3.0 V ≤ V <sub>DDD</sub> ≤ 5.5 V | 0.1×V <sub>DDD</sub> | -                    | 0.1×V <sub>DDD</sub> | _                    | ٧    |  |

| T <sub>BUFI2C</sub>   | Bus free time between a stop and start condition                                                         | 4.7                  | _                    | 1.3                  | _                    | μs   |  |

| T <sub>SPI2C</sub>    | Pulse width of spikes that are suppressed by input filter                                                | -                    | -                    | 50                   | -                    | ns   |  |

| C <sub>BUS</sub>      | Capacitance load for SDA or SCL                                                                          | _                    | 400                  | _                    | 400                  | pF   |  |

| V <sub>IL_I2C</sub>   | Input low voltage                                                                                        | -0.5                 | $0.3 \times V_{DDD}$ | -0.5                 | $0.3 \times V_{DDD}$ |      |  |

| V <sub>IH_I2C</sub>   | Input high voltage                                                                                       | $0.7 \times V_{DDD}$ | _                    | $0.7 \times V_{DDD}$ | _                    | V    |  |

| V <sub>OL_I2C_L</sub> | Output low voltage (V <sub>DDD</sub> ≤ 2 V, 3 mA sink)                                                   | _                    | $0.2 \times V_{DDD}$ | _                    | $0.2 \times V_{DDD}$ | ľ    |  |

| V <sub>OL_I2C_H</sub> | Output low voltage (V <sub>DDD</sub> > 3 V, 3 mA sink)                                                   | _                    | 0.4                  | _                    | 0.4                  |      |  |

|                       | Output low current                                                                                       | _                    | 3                    | _                    | 3                    | mΛ   |  |

| I <sub>OL_I2C</sub>   | Output low current V <sub>OL</sub> = 0.6 V                                                               | _                    | _                    | _                    | 6                    | mA   |  |

| V <sub>H_I2C</sub>    | Input hysteresis                                                                                         | $0.1 \times V_{DDD}$ | -                    | $0.1 \times V_{DDD}$ | _                    | m۷   |  |

**Electrical Specifications**

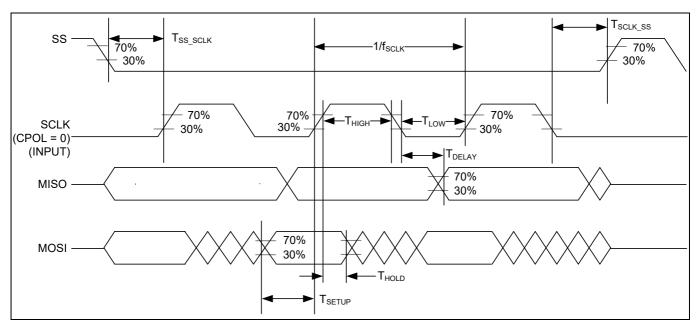

#### **SPI specifications** 9.4.4

The specifications listed in **Table 14** are valid under these conditions:  $1.71 \text{ V} \le \text{V}_{DDD} \le 1.95 \text{ V}$  or  $3.0 \text{ V} \le \text{V}_{DDD} \le 5.5 \text{ V}$ ,  $1.71 \text{ V} \le \text{V}_{CCD} \le 1.95 \text{ V}$ ,  $3.0 \text{ V} \le \text{V}_{DDA} \le 5.5 \text{ V}$ , and  $\text{C}_{LOAD} = 25 \text{ pF}$ . Typical values are specified at  $\text{T}_A = 25 ^{\circ}\text{C}$ ,  $\text{V}_{DDD} = \text{V}_{CCD} = 1.8 \text{ V}$ , core LDO disabled, and  $\text{V}_{DDA} = 3.0 \text{ V}$ .

Figure 16 **SPI timing diagram**

Table 14 **AC characteristics of SPI pins**

| Parameter            | Description                                                                                                  | Conditions                | Min | Тур | Max | Unit |

|----------------------|--------------------------------------------------------------------------------------------------------------|---------------------------|-----|-----|-----|------|

| f <sub>SCLK</sub>    | SCLK clock frequency                                                                                         | -                         | -   | -   | 8   | MHz  |

| 1/f <sub>SCLK</sub>  | SPI SCLK cycle time (period)                                                                                 | _                         | 125 | -   | _   | ns   |

| SDR <sub>SPI</sub>   | Sustained data rate for SPI transaction                                                                      | -                         | -   | -   | 8   | Mbps |

| T <sub>IDLESPI</sub> | Time between consecutive SPI transactions (duration between SS deactivation and the following SS activation) | -                         | 125 | -   | -   |      |