## Automotive single channel pyro-fuse driver

## Features

- AEC-Q100 grade 1 qualified

- Full ISO26262 compliant, ASIL-D systems ready

- Very low power consumption:

- Less than 10  $\mu$ A in deep-sleep mode (only trigger detection enabled)

- Less than 4 mA in low-power mode (trigger detection enabled, ER boost recharge active, cyclic diagnostics every 100 ms)

- Boost regulator to charge Energy Reserve (ER) with bang-bang control to reduce consumption

- FENH/FENL digital input triggers, compatible to level or PWM signals (16 kHz and 125 kHz), with line integrity check feature

- Autonomous cyclic diagnostic routine to ensure detection of all failures which may prevent safe deployment and/or cause inadvertent deployment

- Programmable deployment profile: current value and time duration can be adapted to different pyro-fuse igniters

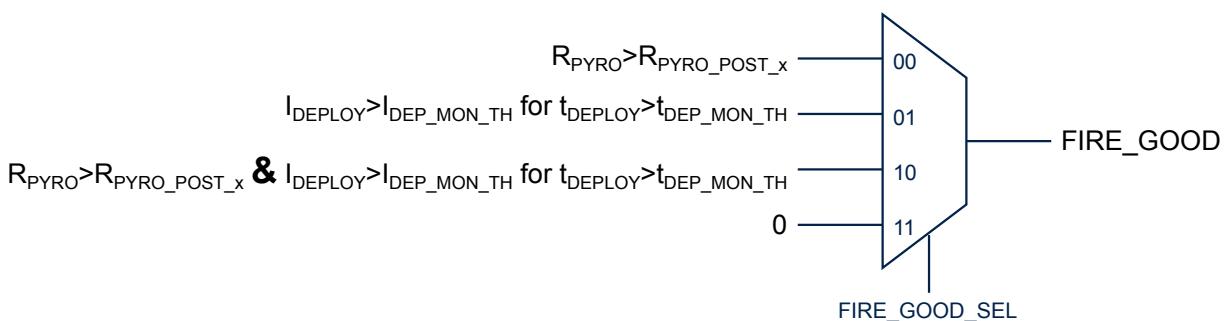

- Firing strategy supporting multiple retry attempts based on user-selectable FIRE\_GOOD signal

- Embedded NVM for configuration parameters storage and runtime configuration integrity check

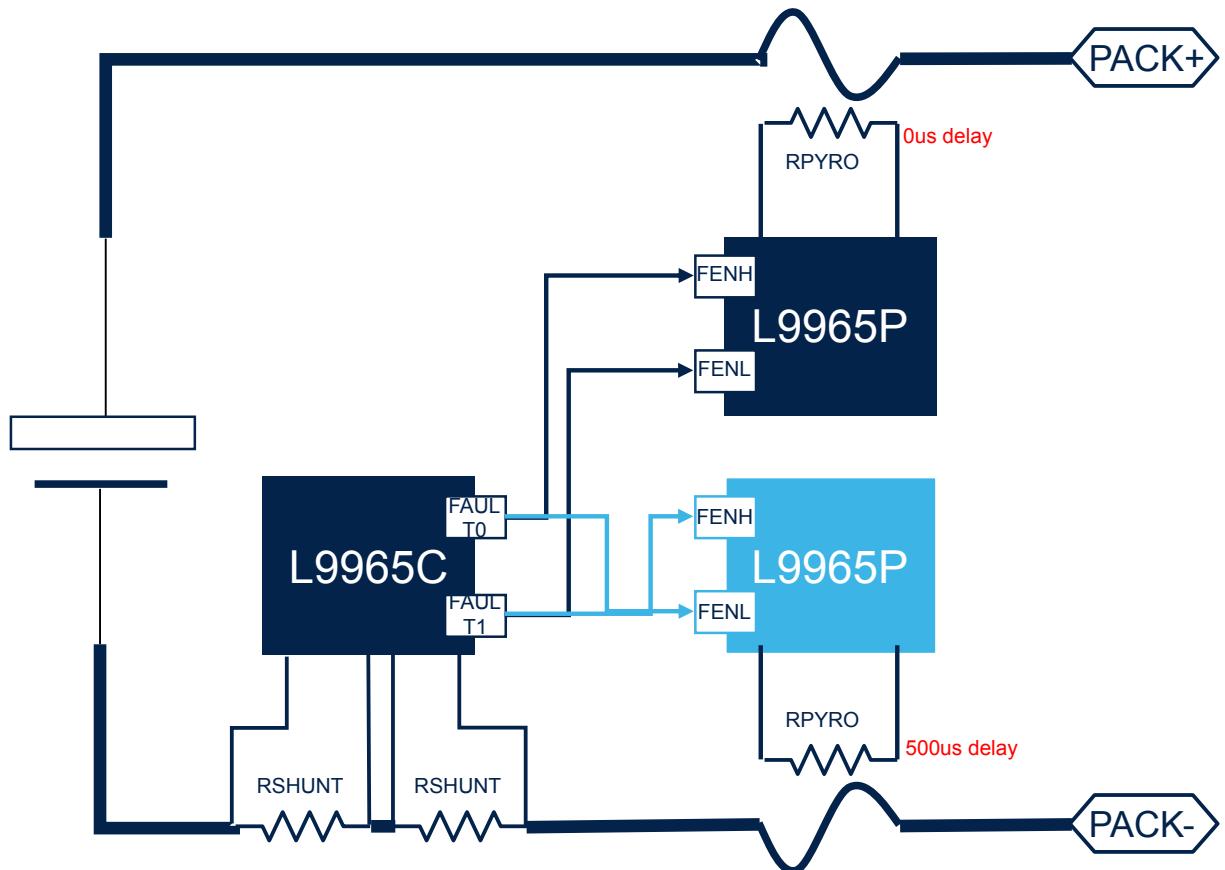

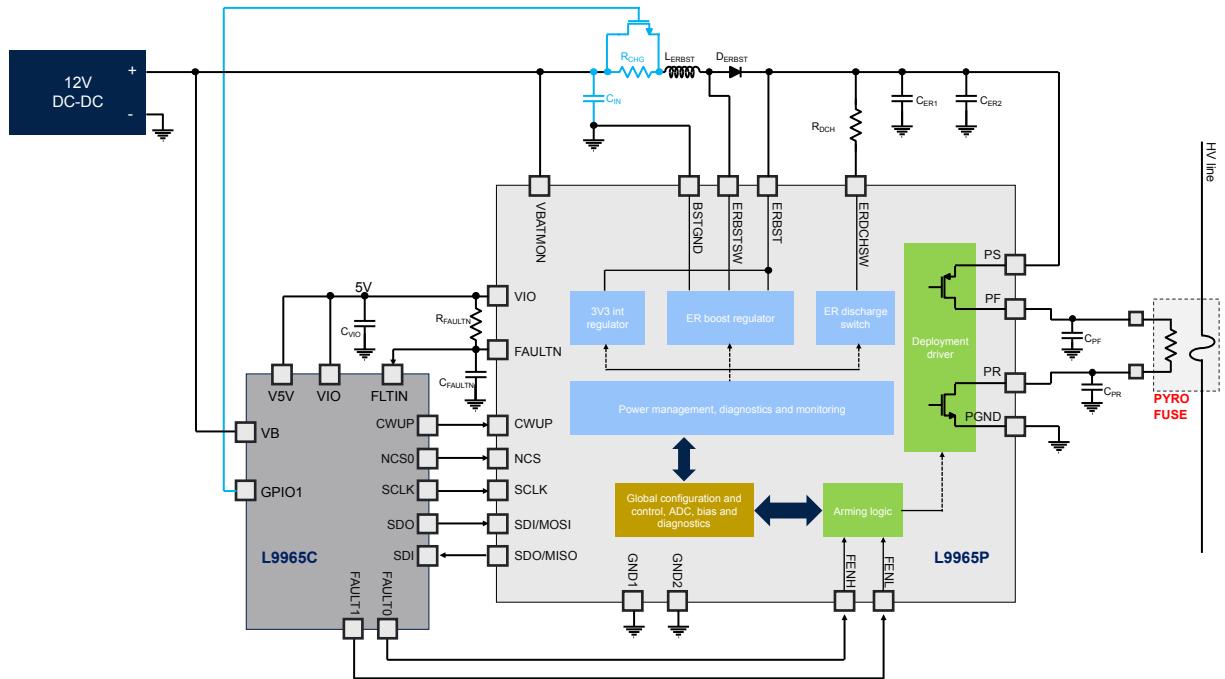

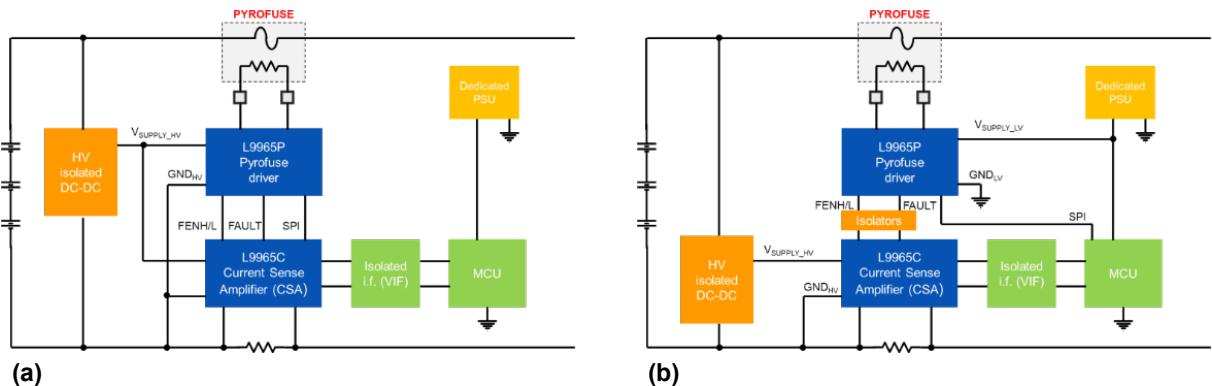

- Easy integration with L9965C companion CSA, implementing many of the safety mechanisms needed to achieve ASIL targets, thus allowing easy L9965P plug and play in the system

- Pyro-fuse deployment available down to a minimum operating battery voltage of 6 V

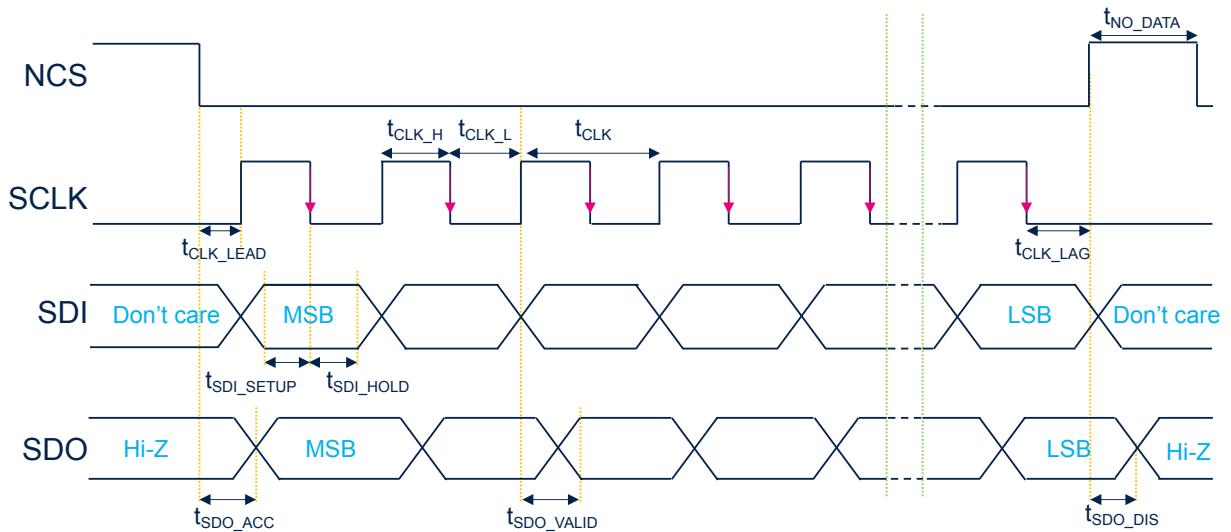

- 24-bit peripheral SPI for direct MCU/L9965C interface

- Compatible with pyro-fuses certified according LV-16 and USCAR-28

## Product status link

[L9965P](#)

## Product summary

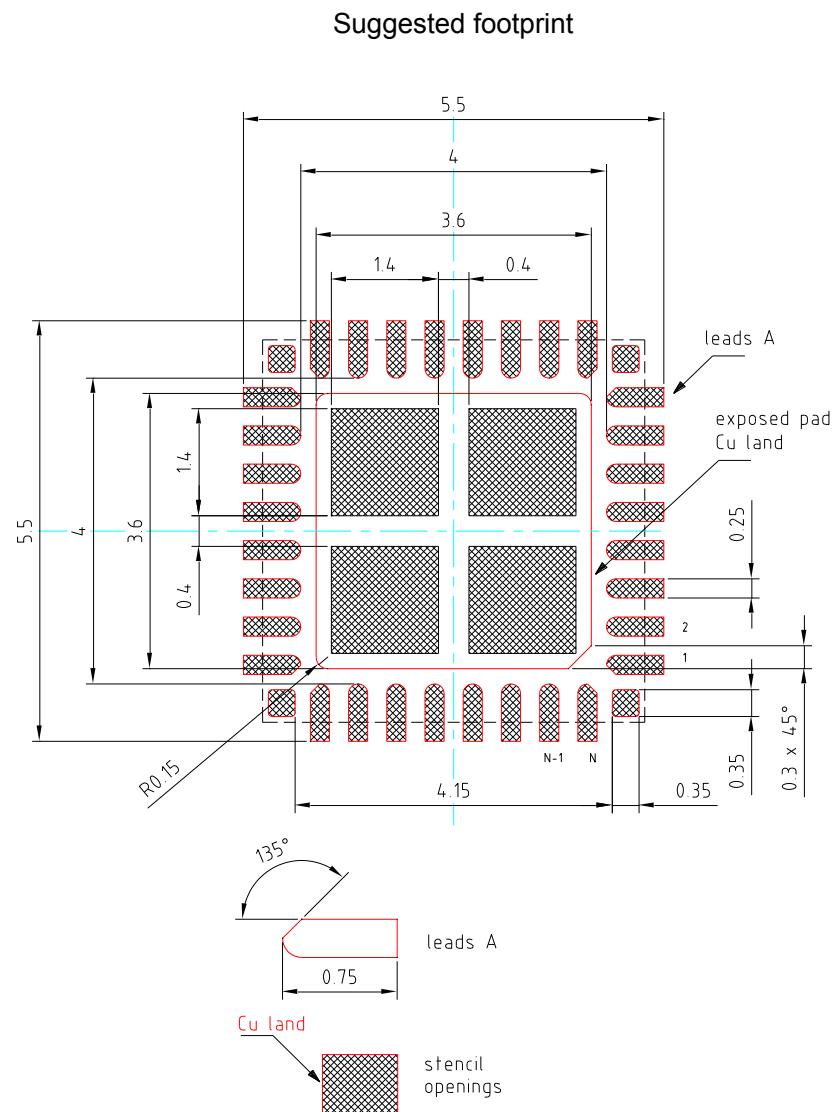

| Order code   | Package | Packing       |

|--------------|---------|---------------|

| L9965P-FN    |         | Tray          |

| L9965P-FN-TR | VFQFN32 | Tape and reel |

| L9965P-FP    |         | Tray          |

| L9965P-FP-TR | TQFP32L | Tape and reel |

## Product labels

## Application

- High voltage battery packs for BEVs and PHEVs

- Backup energy storage systems and UPS

## Description

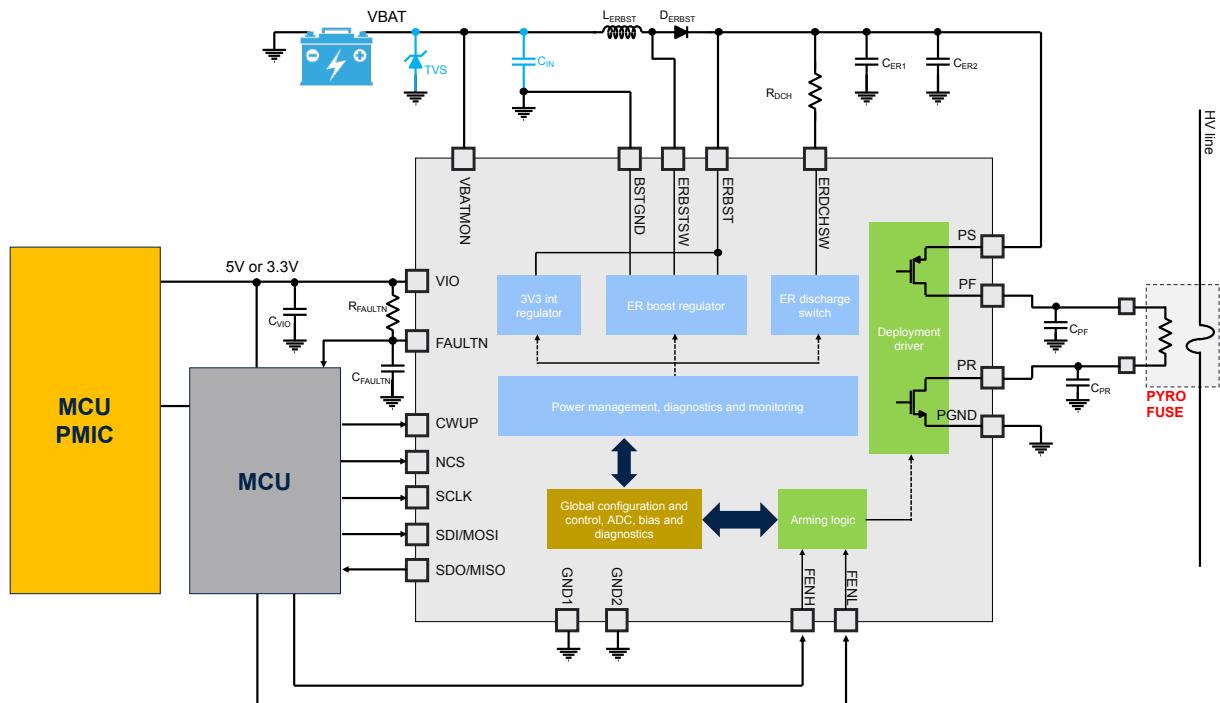

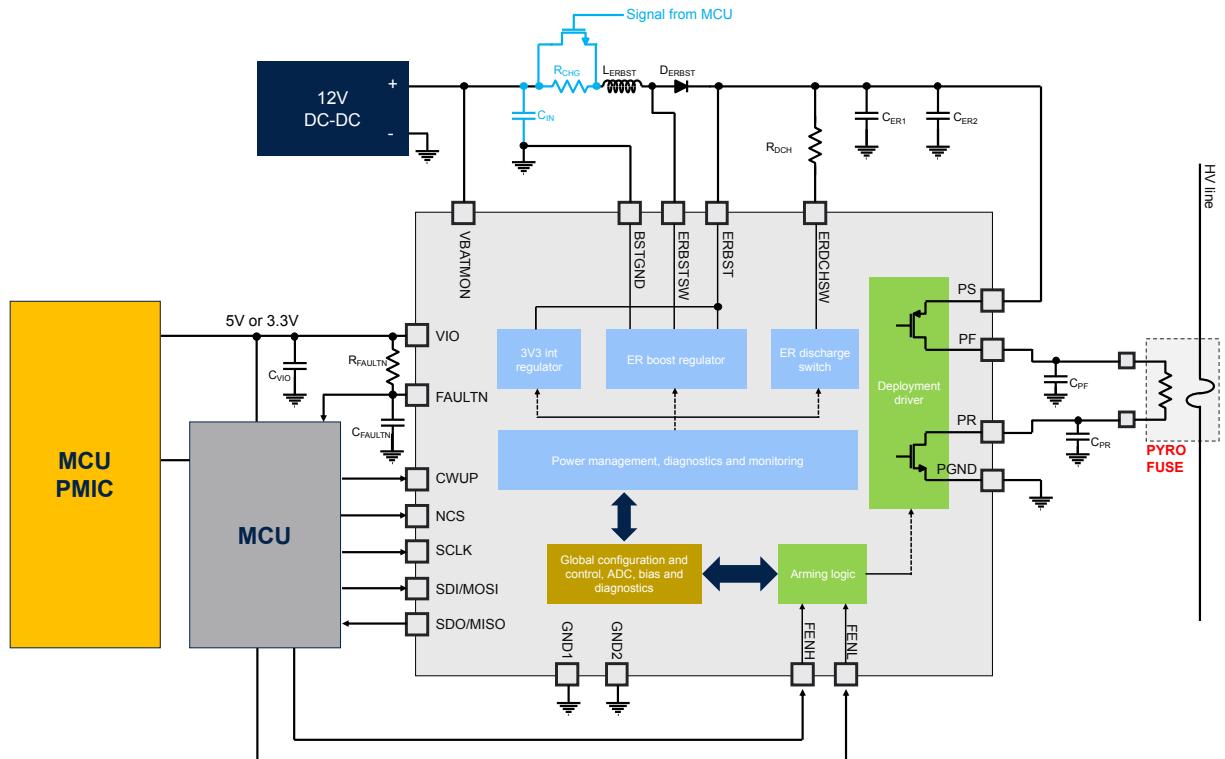

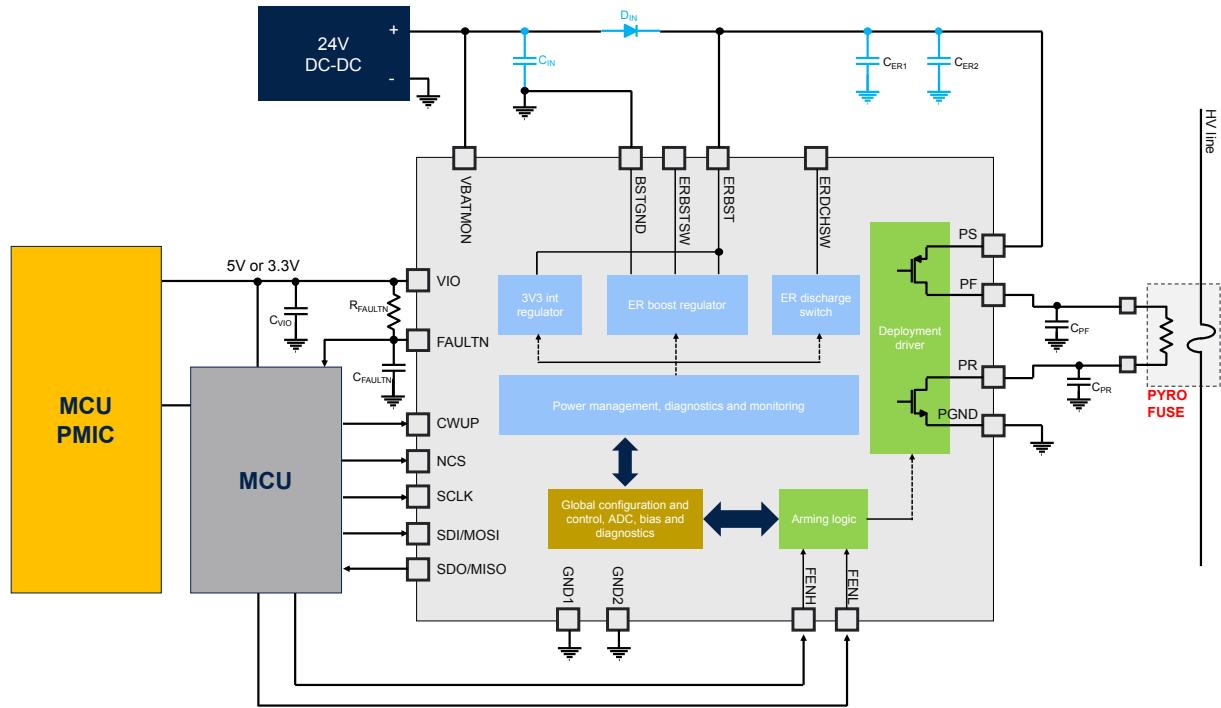

L9965P is an automotive-grade single channel pyro-fuse driver capable to break high voltage battery line quickly and reliably in case of short circuit or car crash.

To accomplish this function, the device features a dual FET output stage made of a HS and a LS powerMOS. The stage is equipped with a closed loop current feedback and can be configured to deliver controlled firing profiles programming both current value and time duration.

Moreover, the power stage is able to perform a defined number of auto-retry attempts based on the success or not of the deployment.

The device embeds a programmable firing logic allowing to generate the trigger signal from two SPI commands or from two digital inputs (FENH/FENL).

The digital input triggers are compatible with both level and PWM encoding, supporting 16 kHz and 125 kHz encoded signals.

The device supports the charging of an external capacitor to be used as tank capacitor or as energy reserve (ER) in case of battery loss. An internal boost regulator can be used to control the ER cap voltage around a programmable setpoint. Boosting the input battery voltage allows using smaller ER capacitor values to store the energy needed for firing, even in case of ECU battery loss.

The device has been designed to deliver maximum safety and performance while still being energy efficient. A low-power operation strategy allows minimizing the idle consumption, keeping the device in an ultra low power state while still performing all the diagnostic sweeps needed for achieving the ASIL targets. The periodicity of the diagnostic sweeps can be programmed in order to comply with any FTI. During such ultra low power state, the device is still sensitive to wake-up/trigger sources in order to be ready to fire.

Operation in conjunction with L9965C companion chip allows simplifying the software development, as many safety mechanisms are already implemented by L9965C.

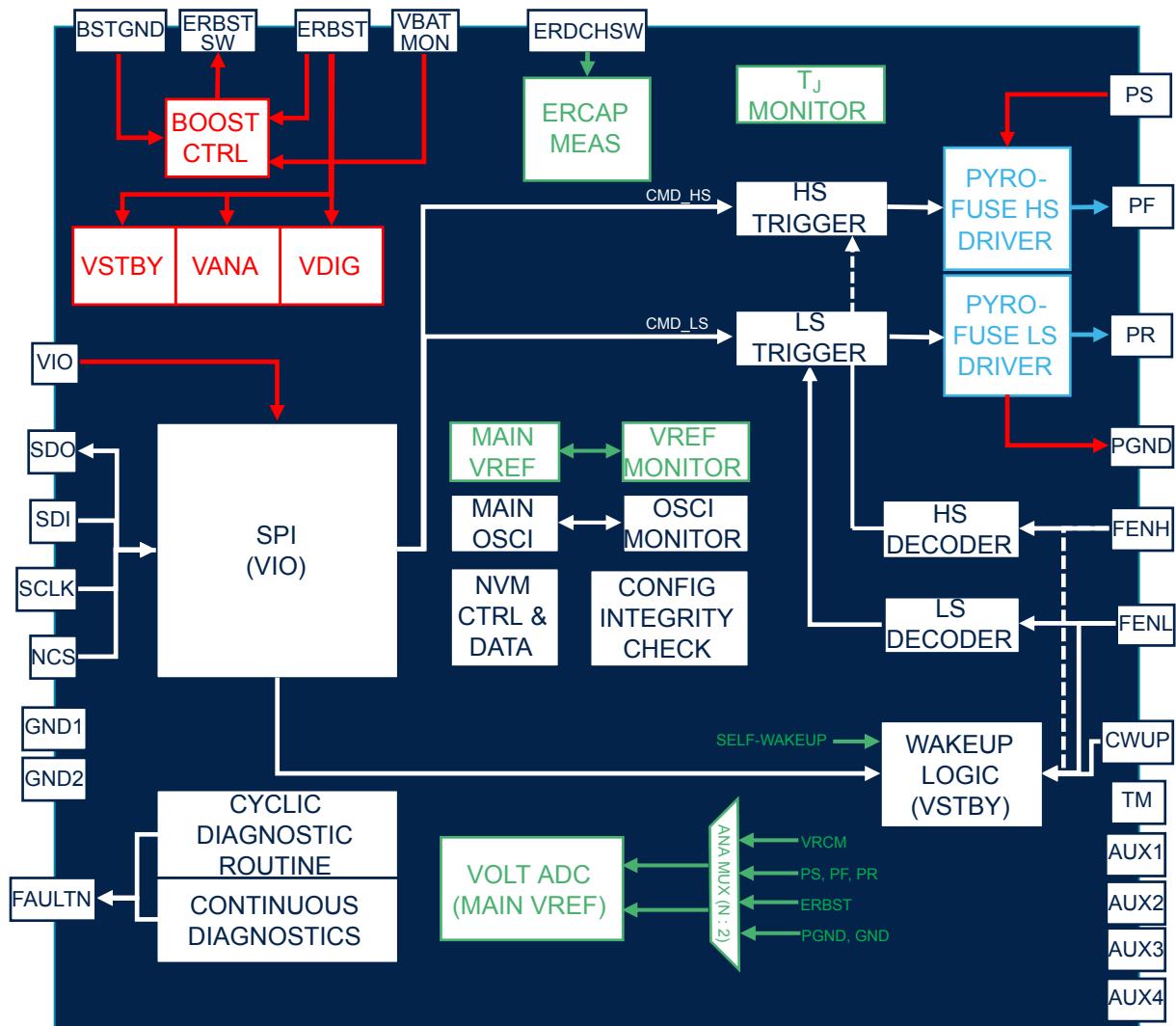

# 1 Block diagram and pin description

## 1.1 Block diagram

Figure 1. Block diagram

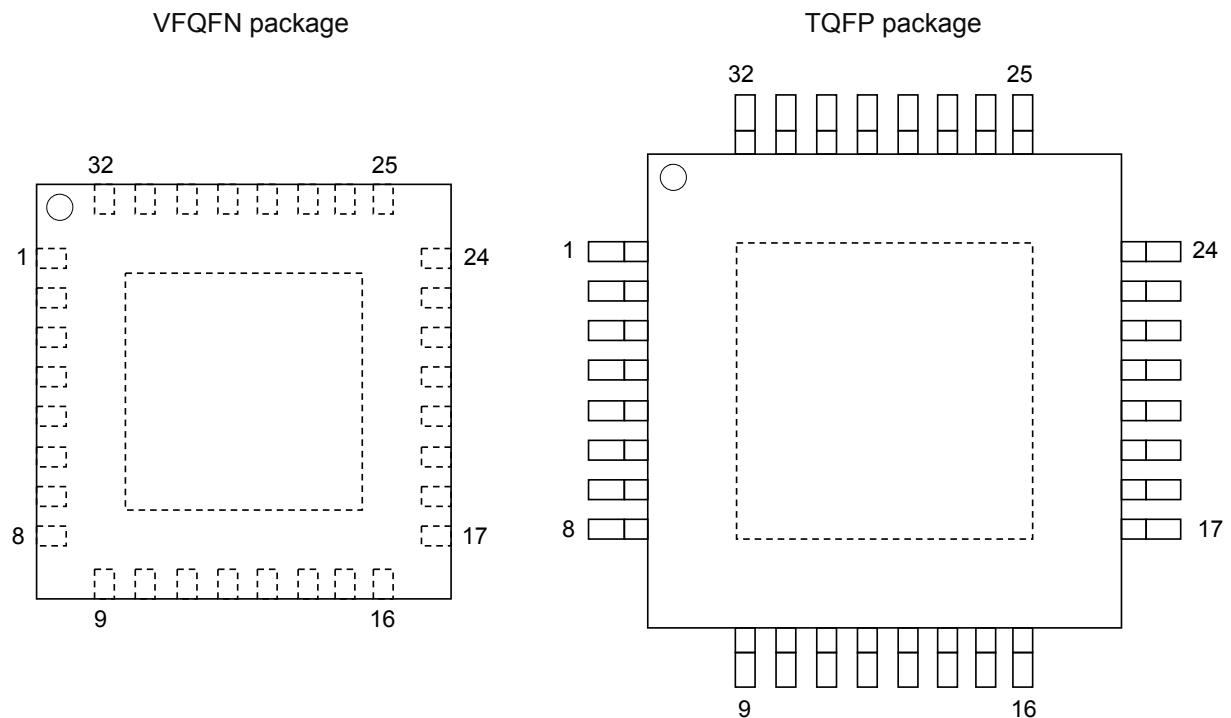

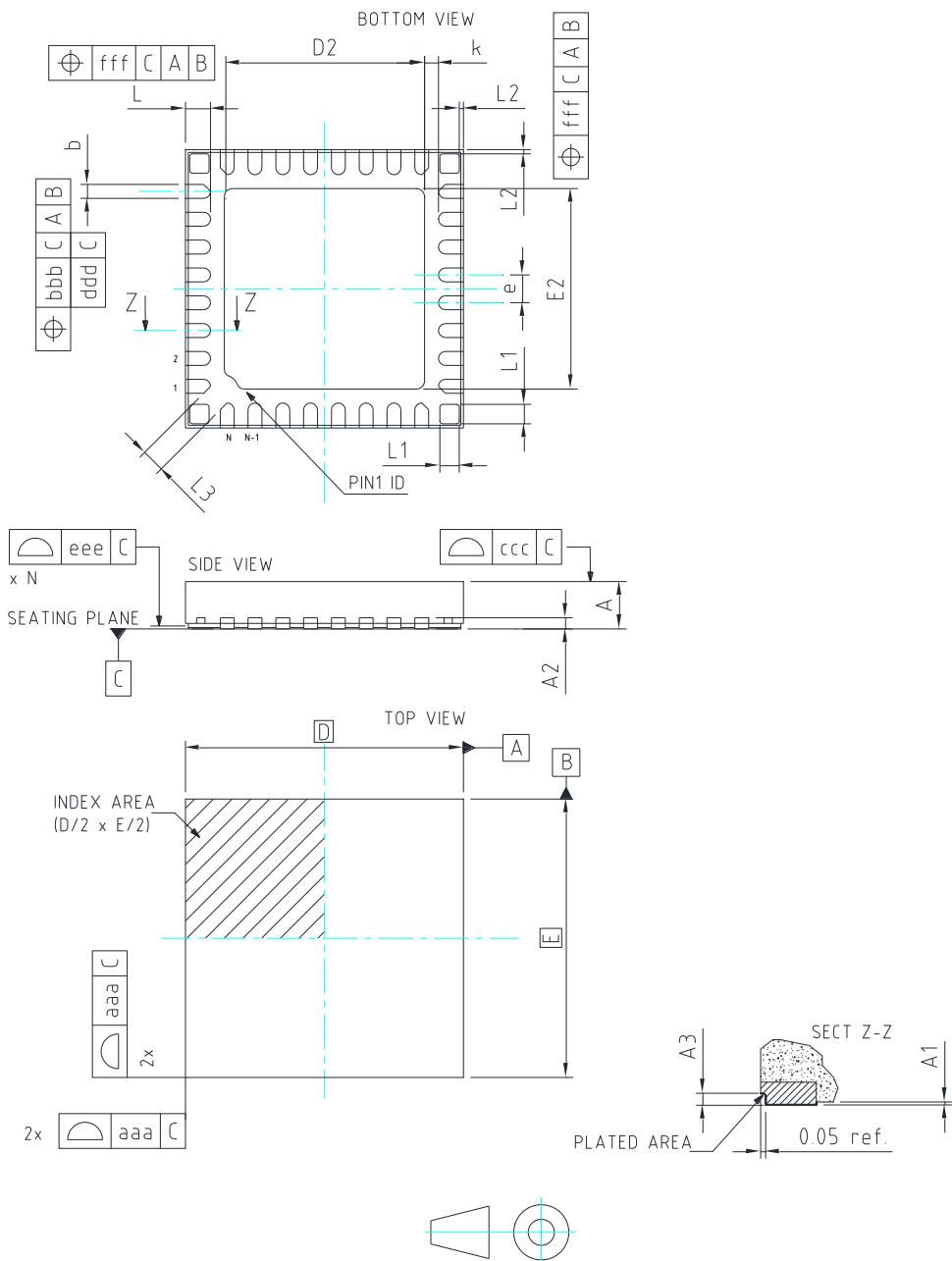

## 1.2 Pin description

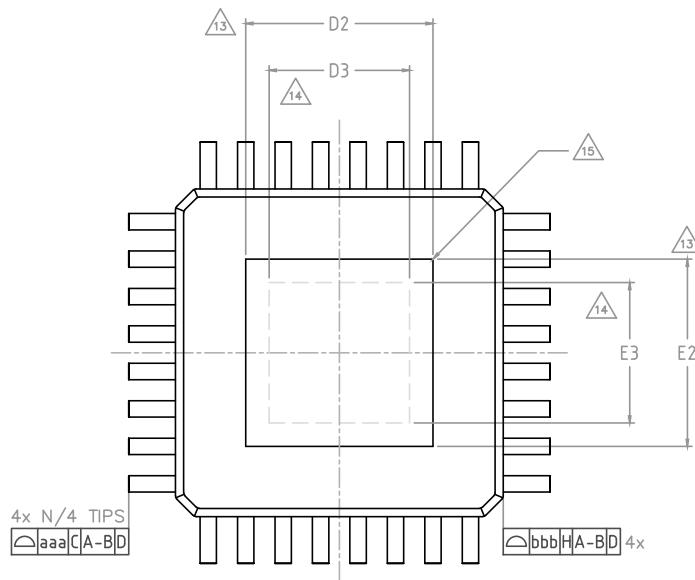

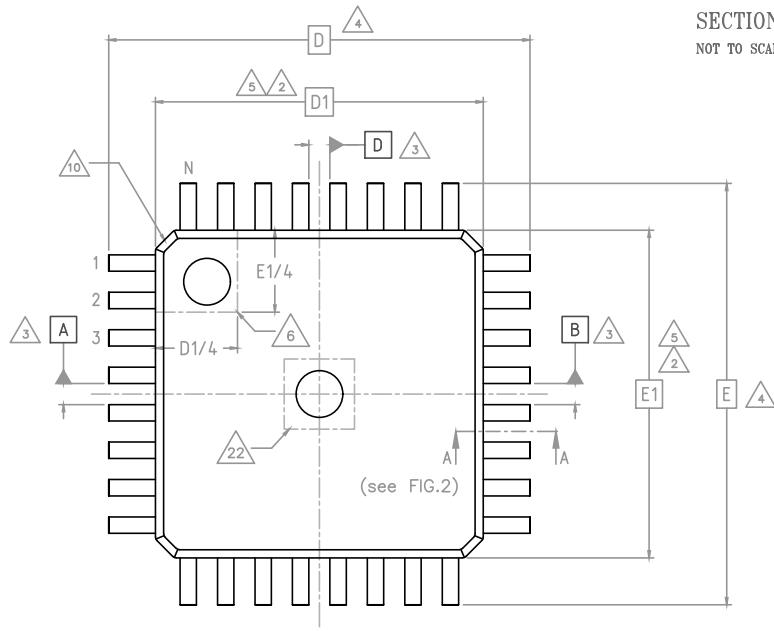

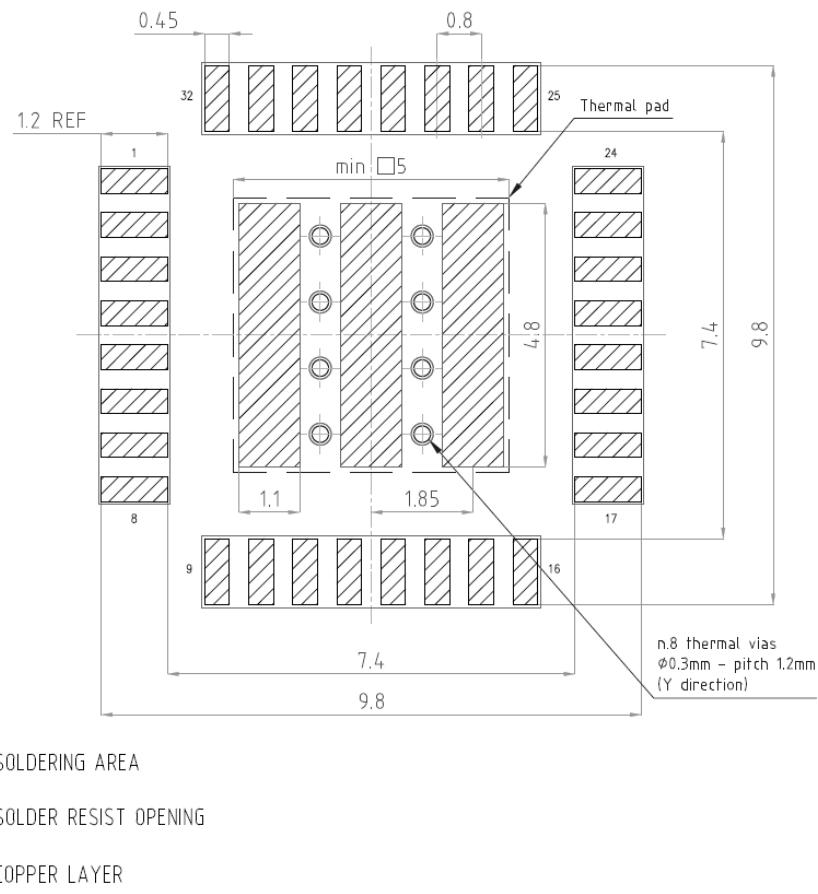

**Figure 2. Pinout (top view)**

**Table 1. Pin function**

| #  | Name    | Function                                         | Internal PU/PD       | Type   |

|----|---------|--------------------------------------------------|----------------------|--------|

| 1  | CWUP    | Cyclic wake-up input                             | PD                   | Local  |

| 2  | GND2    | Ground pin                                       | -                    | Global |

| 3  | FAULTN  | Open-drain fault output pin                      | -                    | Local  |

| 4  | AUX1    | Short to ground in application                   | -                    | Local  |

| 5  | NCS     | SPI chip select                                  | PU                   | Local  |

| 6  | SCLK    | SPI clock                                        | PD                   | Local  |

| 7  | SDI     | SPI data in (MOSI)                               | PD                   | Local  |

| 8  | SDO     | SPI data out (MISO)                              | -                    | Local  |

| 9  | VIO     | Digital output buffer supply input               | -                    | Local  |

| 10 | AUX2    | Short to ground in application                   | -                    | Local  |

| 11 | TM      | ST test mode pin, short to ground in application | PD                   | Local  |

| 12 | GND1    | Ground pin                                       | -                    | Global |

| 13 | AUX3    | Open in application                              | PD                   | Local  |

| 14 | FENH    | Fire enable high-side                            | PU/PD (configurable) | Local  |

| 15 | AUX4    | Open in application                              | PD                   | Local  |

| 16 | FENL    | Fire enable low-side                             | PU/PD (configurable) | Local  |

| 17 | PGND    | Pyro-fuse driver low-side ground                 | -                    | Local  |

| 18 | NC      | No connection                                    | -                    | Local  |

| 19 | PR      | Pyro-fuse driver low-side output                 | -                    | Global |

| 20 | NC      | No connection                                    | -                    | Local  |

| 21 | PF      | Pyro-fuse driver high-side output                | -                    | Global |

| 22 | NC      | No connection                                    | -                    | Local  |

| 23 | PS      | Pyro-fuse driver high-side supply                | -                    | Global |

| 24 | NC      | No connection                                    | -                    | Local  |

| 25 | ERDCHSW | Energy reserve discharge switch                  | -                    | Local  |

| 26 | NC      | No connection                                    | -                    | Local  |

| 27 | ERBST   | Main supply/energy reserve boost output          | -                    | Global |

| 28 | NC      | No connection                                    | -                    | Local  |

| 29 | BSTGND  | Energy reserve boost ground                      | -                    | Local  |

| 30 | ERBSTSW | Energy reserve boost switching node              | -                    | Local  |

| 31 | NC      | No connection                                    | -                    | Local  |

| 32 | VBATMON | Input battery monitor pin                        | -                    | Global |

| 33 | EP      | Exposed pad: connect to GND                      | -                    | -      |

## 2 Product ratings

### 2.1 Thermal ratings

Table 2. Thermal ratings

| Symbol            | Parameter                                               | Test condition                       | Min | Typ  | Max | Unit |

|-------------------|---------------------------------------------------------|--------------------------------------|-----|------|-----|------|

| $T_{AMB}$         | Operating and testing temperature                       |                                      | -40 | -    | 125 | °C   |

| $T_J$             | Junction temperature for all parameters                 |                                      | -40 | -    | 150 | °C   |

| $T_{STG}$         | Storage temperature                                     |                                      | -40 | -    | 150 | °C   |

| $R_{TH\_ja,TQFP}$ | Junction to ambient thermal resistance, TQFP32 package  | According JEDEC standard on 2s2p PCB | -   | 29.4 | -   | °C/W |

| $R_{TH\_ja,QFN}$  | Junction to ambient thermal resistance, VFQFN32 package | According JEDEC standard on 2s2p PCB | -   | 35   | -   | °C/W |

### 2.2 Electrical ratings

The following section describes the different operational ranges.

For each device pin:

- **Operating range (OR):** within this range functions operate as specified and without parameter deviations. All the device electrical parameters are tested and guaranteed in this range and are valid in the whole  $T_J$  operating range, unless otherwise specified.

- **Absolute maximum rating range (AMR):** within this range functions may not operate properly. However, the IC will not be damaged. Exposure to AMR conditions for extended periods may affect device reliability. Exceeding any AMR may cause permanent damage to the integrated circuit.

Note:

- *Currents are noted with a positive sign when flowing into a pin.*

- *Integrated protections and diagnostics are designed to prevent device destruction under the fault conditions described in the specification. Fault conditions are considered to be out of normal operating range. Protection functions are not designed for continuous repetitive operation.*

**Table 3. Pin electrical ratings**

| Parameter            | Description              | Test condition | AMR <sub>MIN</sub> | OR <sub>MIN</sub> | OR <sub>MAX</sub>                        | AMR <sub>MAX</sub>    | Unit | Note               |

|----------------------|--------------------------|----------------|--------------------|-------------------|------------------------------------------|-----------------------|------|--------------------|

| <b>Power supply</b>  |                          |                |                    |                   |                                          |                       |      |                    |

| V <sub>VIO</sub>     | VIO: voltage range       | vs. GNDx       | -0.3               | 3                 | 5.5                                      | 20                    | V    | -                  |

| V <sub>ERBST</sub>   | ERBST: voltage range     | vs. GNDx       | -0.3               | 6                 | 26                                       | 40                    | V    | -                  |

| V <sub>ERBSTSW</sub> | ERBSTSW: voltage range   | vs. GNDx       | -0.3               | 0                 | V <sub>ERBST_111</sub> +V <sub>DFW</sub> | 40                    | V    | Only if ERBST used |

| V <sub>ERDCHSW</sub> | ERDCHSW: voltage range   | vs. GNDx       | -0.3               | 6                 | V <sub>ERBST</sub>                       | 40                    | V    | -                  |

| V <sub>PS</sub>      | PS: voltage range        | vs. GNDx       | -0.3               | 6                 | 26                                       | 40                    | V    | -                  |

| V <sub>VBATMON</sub> | VBATMON: voltage range   | vs. GNDx       | -0.3               | 6                 | 26                                       | 40                    | V    | -                  |

| <b>Ground</b>        |                          |                |                    |                   |                                          |                       |      |                    |

| V <sub>BSTGND</sub>  | BSTGND: voltage range    | vs. GNDx       | -0.3               | -0.1              | 0.1                                      | 0.6                   | V    | -                  |

| V <sub>PGND</sub>    | PGND: voltage range      | vs. GNDx       | -0.3               | -0.1              | 0.1                                      | 0.6                   | V    | -                  |

| <b>SPI</b>           |                          |                |                    |                   |                                          |                       |      |                    |

| V <sub>NCS</sub>     | NCS: voltage range       | vs. GNDx       | -0.3               | 0                 | V <sub>VIO</sub>                         | 20                    | V    | -                  |

| V <sub>SCLK</sub>    | SCLK: voltage range      | vs. GNDx       | -0.3               | 0                 | V <sub>VIO</sub>                         | 20                    | V    | -                  |

| V <sub>SDI</sub>     | SDI: voltage range       | vs. GNDx       | -0.3               | 0                 | V <sub>VIO</sub>                         | 20                    | V    | -                  |

| V <sub>SDO</sub>     | SDO: voltage range       | vs. GNDx       | -0.3               | 0                 | V <sub>VIO</sub>                         | V <sub>VIO</sub> +0.3 | V    | -                  |

| <b>Pyro-fuse</b>     |                          |                |                    |                   |                                          |                       |      |                    |

| V <sub>FENx</sub>    | FENH,FENL: voltage range | vs. GNDx       | -0.3               | 0                 | V <sub>VIO</sub>                         | 20                    | V    | -                  |

| V <sub>PF</sub>      | PF: voltage range        | vs. GNDx       | -1                 | 0                 | V <sub>PS</sub>                          | V <sub>PS</sub> +0.3  | V    | -                  |

| V <sub>PR</sub>      | PR: voltage range        | vs. GNDx       | -0.3               | 0                 | V <sub>PS</sub>                          | 35                    | V    | -                  |

| <b>Wake-up</b>       |                          |                |                    |                   |                                          |                       |      |                    |

| V <sub>CWUP</sub>    | CWUP: voltage range      | vs. GNDx       | -0.3               | 0                 | V <sub>VIO</sub>                         | 20                    | V    | -                  |

| <b>Fault</b>         |                          |                |                    |                   |                                          |                       |      |                    |

| V <sub>FAULTN</sub>  | FAULTN: voltage range    | vs. GNDx       | -0.3               | 0                 | V <sub>VIO</sub>                         | 20                    | V    | -                  |

## 2.2.1 Absolute maximum ratings

Table 4. Absolute maximum ratings

| Symbol  | Test condition                          | Min  | Typ | Max           | Unit |

|---------|-----------------------------------------|------|-----|---------------|------|

| CWUP    |                                         | -0.3 | -   | 20            | V    |

| GND2    | GND1, GND2 and EP in short to substrate | -    | 0   | -             | V    |

| FAULTN  |                                         | -0.3 | -   | 20            | V    |

| AUX1    |                                         | -0.3 | -   | 20            | V    |

| NCS     |                                         | -0.3 | -   | 20            | V    |

| SCLK    |                                         | -0.3 | -   | 20            | V    |

| SDI     |                                         | -0.3 | -   | 20            | V    |

| SDO     |                                         | -0.3 | -   | $V_{VIO}+0.3$ | V    |

| VIO     |                                         | -0.3 | -   | 20            | V    |

| AUX2    |                                         | -0.3 | -   | 20            | V    |

| TM      |                                         | -0.3 | -   | 20            | V    |

| GND1    | GND1, GND2 and EP in short to substrate | -    | 0   | -             | V    |

| AUX3    |                                         | -0.3 | -   | 20            | V    |

| FENH    |                                         | -0.3 | -   | 20            | V    |

| AUX4    |                                         | -0.3 | -   | 20            | V    |

| FENL    |                                         | -0.3 | -   | 20            | V    |

| PGND    |                                         | -0.3 | -   | 0.6           | V    |

| NC      |                                         | -    | -   | -             |      |

| PR      |                                         | -0.3 | -   | 35            | V    |

| PF      |                                         | -1   | -   | $V_{PS}+0.3$  | V    |

| PS      |                                         | -0.3 | -   | 40            | V    |

| ERDCHSW |                                         | -0.3 | -   | 40            | V    |

| ERBST   |                                         | -0.3 | -   | 40            | V    |

| BSTGND  |                                         | -0.3 | -   | 0.6           | V    |

| ERBSTSW |                                         | -0.3 | -   | 40            | V    |

| VBATMON |                                         | -0.3 | -   | 40            | V    |

| EP      | GND1, GND2 and EP in short to substrate | -    | 0   | -             | V    |

## 2.3 ESD ratings

Table 5. ESD ratings

| Symbol                  | Parameter                            | Test condition                                                                                                          | Min  | Typ | Max | Unit | Notes    |

|-------------------------|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------|------|-----|-----|------|----------|

| $V_{ESD\_HBM\_GLOBAL}$  | Human body model                     | Global pins are connected at ground_all except global pin under test (ground_all = all ground pins connected together). | -4   | -   | 4   | kV   | -        |

| $V_{ESD\_HBM\_LOCAL}$   | Human body model                     | Local pins, test done according to AEC-Q100-002.                                                                        | -2   | -   | 2   | kV   | Class C2 |

| $V_{ESD\_CDM\_LATERAL}$ | Charged device model                 | Test done according to AEC-Q100-011                                                                                     | -500 | -   | 500 | V    | Class C3 |

| $V_{ESD\_CDM\_CORNER}$  | Charged device model for corner pins | Test done according to AEC-Q100-011                                                                                     | -750 | -   | 750 | V    | Class C4 |

| $I_{LATCH\_UP}$         | Latch up current test                | Test done according to AEC-Q100-004                                                                                     | -100 | -   | 100 | mA   | -        |

### 3 Functional description

In the following paragraphs all the bits in **bold** are located in the NVM and are protected by lock to avoid unwanted modification (see the [Section 3.15: Configuration Lock](#)).

#### 3.1 Device functional states (FSM)

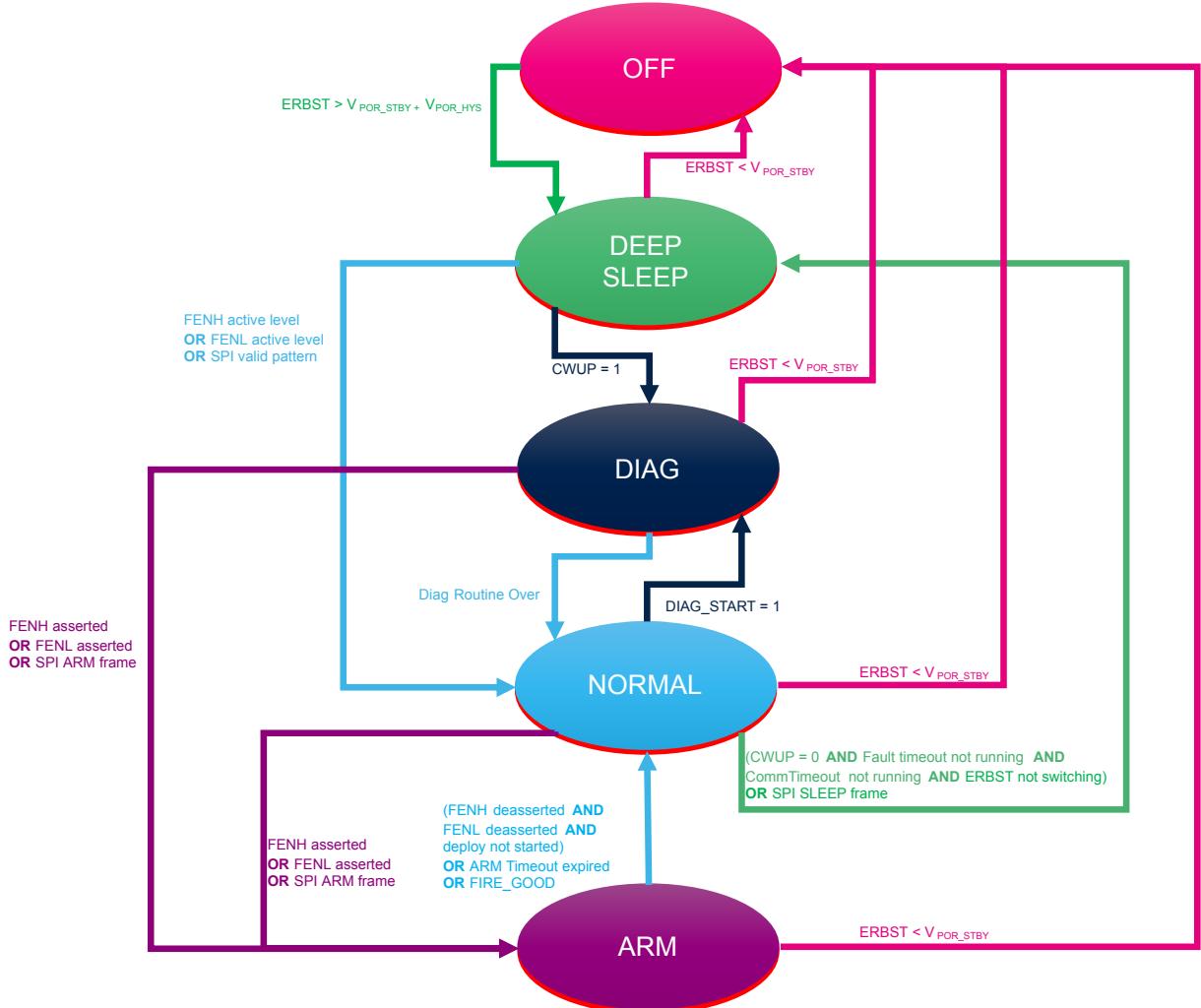

The L9965P operates according to the FSM shown in the [Figure 3](#).

**Figure 3. Device FSM**

The [Table 6](#) summarizes the FSM behavior, describing the transitions and the resources active in each operating state.

**Table 6. Device FSM**

| State      | Purpose                                                                                        | Reached from   | Condition                                                                                                                                                                                                                       | Active resources                                                                                                    |

|------------|------------------------------------------------------------------------------------------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| OFF        | Device OFF                                                                                     | Any state      | When the ERBST voltage falls below the $V_{POR\_TH}$ threshold                                                                                                                                                                  | None                                                                                                                |

| DEEP-SLEEP | Ultralow power state for managing long inactivity periods or implementing low-power strategies | NORMAL         | When CWUP is low, fault timeout ( $t_{FAULT\_HANDLING\_TIMEOUT}$ ) is expired, the SPI communication timeout ( $t_{SPI\_COMM\_TIMEOUT}$ ) is expired and ERBST is not working (ER CAP charged)<br><b>OR</b><br>SPI SLEEP frames | Wake-up from cyclic wake-up pin (CWUP)<br>Wake-up via peripheral SPI<br>Wake-up from fire enable inputs (FENH/FENL) |

|            |                                                                                                |                | OFF                                                                                                                                                                                                                             | Wake-up from cyclic wake-up pin (CWUP)<br>Wake-up via peripheral SPI                                                |

| DIAG       | Diagnostic state                                                                               | DEEP-SLEEP     | When CWUP is asserted                                                                                                                                                                                                           | All resources are active in NORMAL<br>Additionally, all the resources needed to perform the diagnostic routine      |

|            |                                                                                                | NORMAL         | When commanded via SPI                                                                                                                                                                                                          |                                                                                                                     |

| NORMAL     | Normal operating state                                                                         | DEEP-SLEEP     | Wake-up from any of the enabled sources (FENH or FENL or SPI valid pattern)                                                                                                                                                     | All resources are active, except the ones needed to perform the diagnostic routine                                  |

|            |                                                                                                | ARM            | All the enabled deploy conditions (FENH and FENL) are deasserted<br><b>OR</b><br>Arming timeout (corresponding to deployment time) expired<br><b>OR</b><br>FIRE_GOOD                                                            |                                                                                                                     |

|            |                                                                                                | DIAG           | Diagnostic routine over                                                                                                                                                                                                         |                                                                                                                     |

| ARM        | Prepare to deploy                                                                              | NORMAL or DIAG | At least one deploy condition asserted between FENH, FENL or SPI ARM frame                                                                                                                                                      | All resources active in NORMAL, except the ones needed to perform the diagnostic routine                            |

### 3.1.1 SPI SLEEP commands

To force the device to go in a DEEP-SLEEP state, the following procedure shall be implemented:

1. MCU writes 0x77 into the SPECIAL\_KEY register to enter partial go-to-sleep;

2. MCU writes 0xCC into the SPECIAL\_KEY register to confirm go-to-sleep.

### 3.1.2 Diagnostics summary

This section describes in detail the enable/masking of all the diagnostic features implemented in the device, according to the functional state.

**Note:** *Many diagnostics may be subject to user-defined configurations and/or enable. The following table assumes that all diagnostics have been enabled in the device configuration.*

**Table 7. Diagnostics summary**

| State      | ERBST OV | PS UV/OV | FENx decoder diag | Deployment autoretry | Diag routine | Oscillator monitor | Reference monitor | GND loss | Config integrity check |

|------------|----------|----------|-------------------|----------------------|--------------|--------------------|-------------------|----------|------------------------|

| OFF        | OFF      | OFF      | OFF               | OFF                  | OFF          | OFF                | OFF               | OFF      | OFF                    |

| DEEP-SLEEP | OFF      | OFF      | OFF               | OFF                  | OFF          | OFF                | OFF               | OFF      | OFF                    |

| DIAG       | AON      | AON      | AON               | OFF                  | OD/CYC       | AON                | AON               | AON      | AON                    |

| NORMAL     | AON      | AON      | AON               | OFF                  | OFF          | AON                | AON               | AON      | AON                    |

| ARM        | AON      | AON      | AON               | AON                  | OFF          | AON                | AON               | AON      | AON                    |

**Note:**

- *AON* → *Diagnostic always-on and running*

- *OD* → *Diagnostic available on-demand*

- *CYC* → *Diagnostic cyclically activated by internal timer*

- *OFF* → *Diagnostic disabled/masked*

## 3.2 Power management

The IC is supplied by ERBST pin, which is then used to generate all the internal regulated supplies.

The IC is usually supplied by an isolated DC/DC converter feeding from the 12 V LV supply (reinforced isolation); alternatively by an isolated DC/DC converter from the HV battery pack.

### 3.2.1 Power management electrical parameters

All parameters are tested and guaranteed in the following conditions, unless otherwise noted: all supplies according to the [Table 3](#);  $T_J$  according to the [Table 2](#).

Table 8. Device current consumption

| Symbol                                    | Parameter                                                                                                                        | Test condition                                                                                                                                | Min | Typ | Max  | Unit          |

|-------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|------|---------------|

| $V_{POR\_TH}$                             | POR threshold (sensed on ERBST pin)                                                                                              |                                                                                                                                               | -   | -   | 4.7  | V             |

| $I_{BASE\_SLP0}$                          | Base current consumption of the device in DEEP-SLEEP state (from VBATMON, ERBSTSW, ERBST, ERDCHSW and PS)                        | $-40^{\circ}\text{C} \leq T_{\text{amb}} \leq +85^{\circ}\text{C}$<br>DEEP-SLEEP                                                              | -   | -   | 10   | $\mu\text{A}$ |

| $I_{BASE\_SLP1}$                          | Base current consumption of the device in DEEP-SLEEP state (from VBATMON, ERBSTSW, ERBST, ERDCHSW and PS)                        | $+85^{\circ}\text{C} \leq T_{\text{amb}} \leq +125^{\circ}\text{C}$<br>$+85^{\circ}\text{C} \leq T_J \leq +125^{\circ}\text{C}$<br>DEEP-SLEEP | -   | -   | 15   | $\mu\text{A}$ |

| $I_{BASE\_NORM}$                          | Base current consumption of the device in NORMAL state with all resources enabled (from VBATMON, ERBSTSW, ERBST, ERDCHSW and PS) | NORMAL                                                                                                                                        | -   | -   | 2.4  | mA            |

| $I_{BASE\_DIAG}$                          | Base current consumption of the device in DIAG state with all resources enabled (from VBATMON, ERBSTSW, ERBST, ERDCHSW and PS)   | DIAG with no diagnostics active                                                                                                               | -   | -   | 2.4  | mA            |

| $I_{\Delta\text{ELTA\_BOOST}}$            | Delta current when the boost controller is in the duty-phase                                                                     | NORMAL, DIAG, ARM, boost charging the ER cap (excluding boost charging current)                                                               | -   | -   | 7.5  | mA            |

| $I_{\Delta\text{ELTA\_ADC}}$              | Delta current when the voltage ADC is enabled and continuously converting                                                        | NORMAL, ADC continuously converting for on-demand conversions                                                                                 | -   | -   | 3.5  | mA            |

| $I_{\Delta\text{ELTA\_ACT\_PD\_PR}}$      | Delta current when the PR active pull-down is enabled                                                                            | NORMAL, PR pull-down enabled                                                                                                                  | -   | -   | 0.2  | mA            |

| $I_{\Delta\text{ELTA\_SS}}$               | Delta current when the spread spectrum is enabled                                                                                | NORMAL, spread spectrum enabled                                                                                                               | -   | -   | 0.06 | mA            |

| $I_{\Delta\text{ELTA\_NVM}}$              | Delta current when the NVM is downloaded                                                                                         | NORMAL, NVM download                                                                                                                          | -   | -   | 1    | mA            |

| $I_{\Delta\text{ELTA\_ABIST}}$            | Delta current when the ABIST is running                                                                                          | DIAG, ABIST continuously running                                                                                                              | -   | -   | 0.6  | mA            |

| $I_{\Delta\text{ELTA\_HWSC}}$             | Delta current from ERBST when the HWSC is running                                                                                | DIAG, HSWC continuously running                                                                                                               | -   | -   | 3.5  | mA            |

| $I_{\Delta\text{ELTA\_VRCM\_CHECK}}$      | Delta current when the VRCM check is running                                                                                     | DIAG, VRCM check continuously running (excluding diagnostic currents)                                                                         | -   | -   | 4.2  | mA            |

| $I_{\Delta\text{ELTA\_PYRO\_LEAK\_TEST}}$ | Delta current when the pyro outputs leakage test is running                                                                      | DIAG, pyro outputs leakage test continuously running                                                                                          | -   | -   | 3.5  | mA            |

| $I_{\Delta\text{ELTA\_RES\_MEAS}}$        | Delta current when the pyro igniter resistance measurement is running                                                            | DIAG, Pyro igniter resistance measurement continuously running (excluding diagnostic currents)                                                | -   | -   | 4.5  | mA            |

| $I_{\Delta\text{ELTA\_FET\_TEST}}$        | Delta current when the FETs test is running                                                                                      | DIAG, Pyro deployment FETs test continuously running (excluding diagnostic currents)                                                          | -   | -   | 3.5  | mA            |

| $I_{\Delta\text{ELTA\_ER\_CAP\_DIAG}}$    | Delta current when the ER capacitor diagnostic is running                                                                        | DIAG, ER capacitor diagnostic continuously running (excluding diagnostic current sunk from ERDCHSW)                                           | -   | -   | 2.5  | mA            |

| $I_{\text{VIO\_BASE}}$                    | Base current consumption from VIO pin                                                                                            | DEEP-SLEEP, SDO in HiZ                                                                                                                        | -   | -   | 1    | $\mu\text{A}$ |

| $I_{\text{VIO\_DELTA}}$                   | Delta current consumption from VIO pin with activity on FAULTN and SDO                                                           | NORMAL, DIAG, ARM                                                                                                                             | -   | -   | 500  | $\mu\text{A}$ |

### 3.3 Power supply section

#### 3.3.1 Main supply (ERBST)

The ERBST pin is the main supply. This line:

- Feeds the internal VANA LDO used for biasing the analog circuitry.

- Feeds the internal VDIG LDO used for biasing the digital circuitry.

- Feeds the internal VSTBY LDO used for biasing the circuitry in DEEP-SLEEP.

The boost regulator is disabled by default and can be enabled via NVM setting the **ERBST\_EN** bit to 1. Once the boost regulator is enabled via NVM, it can be turned-off via the **ERBST\_DIS** bit.

Once  $V_{ERBST} > V_{VBATMON} - V_{ERBST\_DIS}$  for  $t > t_{ERBST\_READY\_FLT}$ , the initial charge phase is over, the **ERBST\_RDY** bit in the ERBOOST register is set to 1 and the switching operation starts. This ensures the presence of the external diode between **VBATMON** pin and **ERBST** pin. If  $V_{ERBST} < V_{VBATMON} - V_{ERBST\_DIS}$  after  $t_{ERBST\_READY\_FLT}$ , the ERBST regulator is turned-off and the **ERBST\_RDY** bit is set to 0.

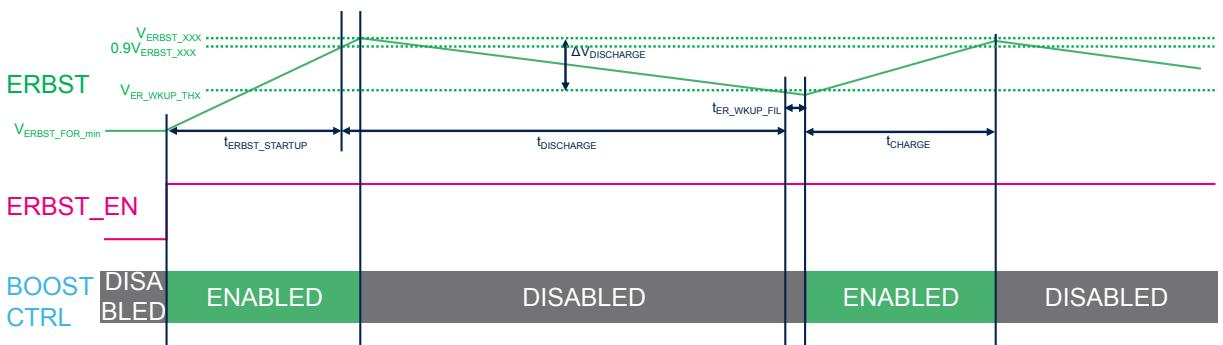

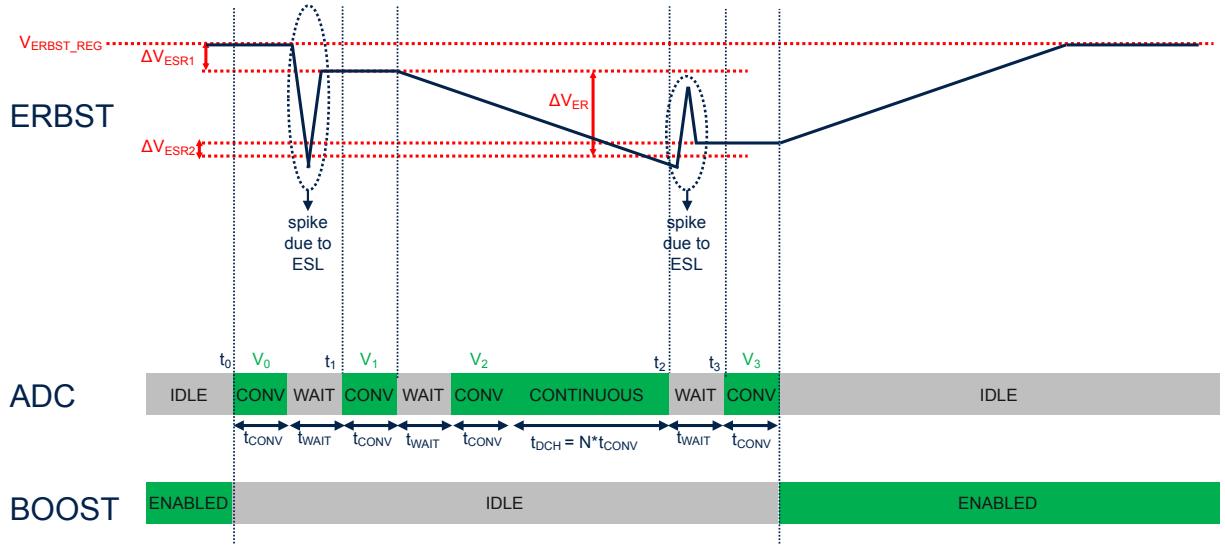

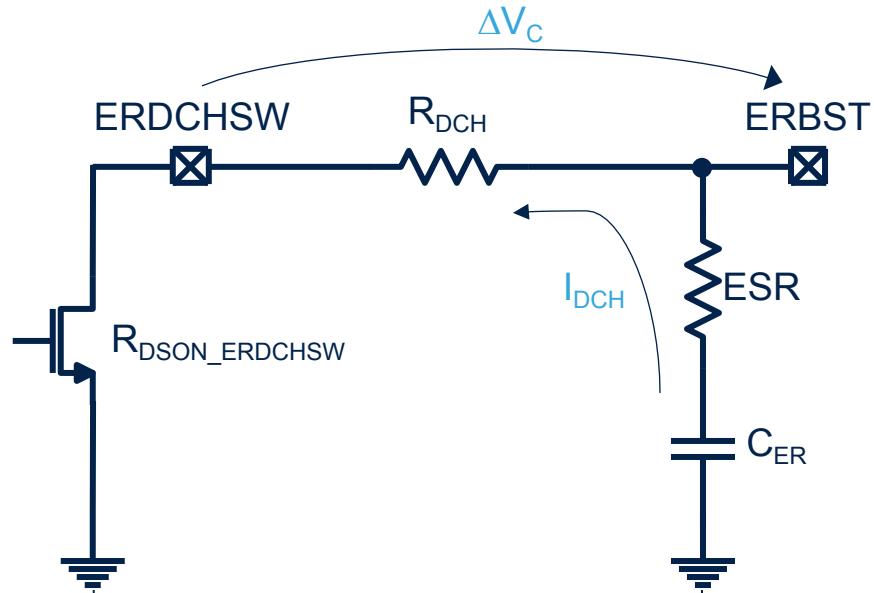

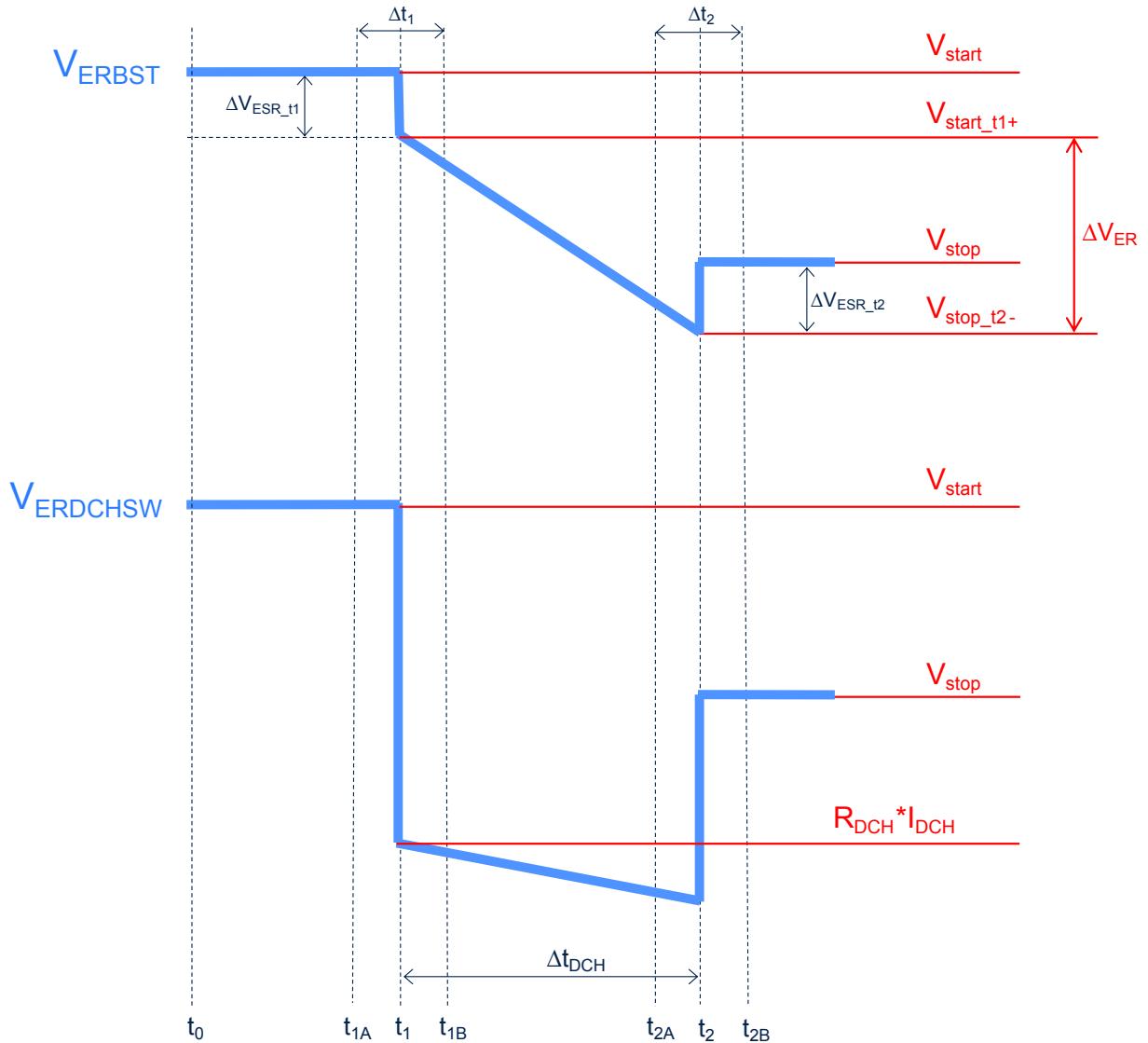

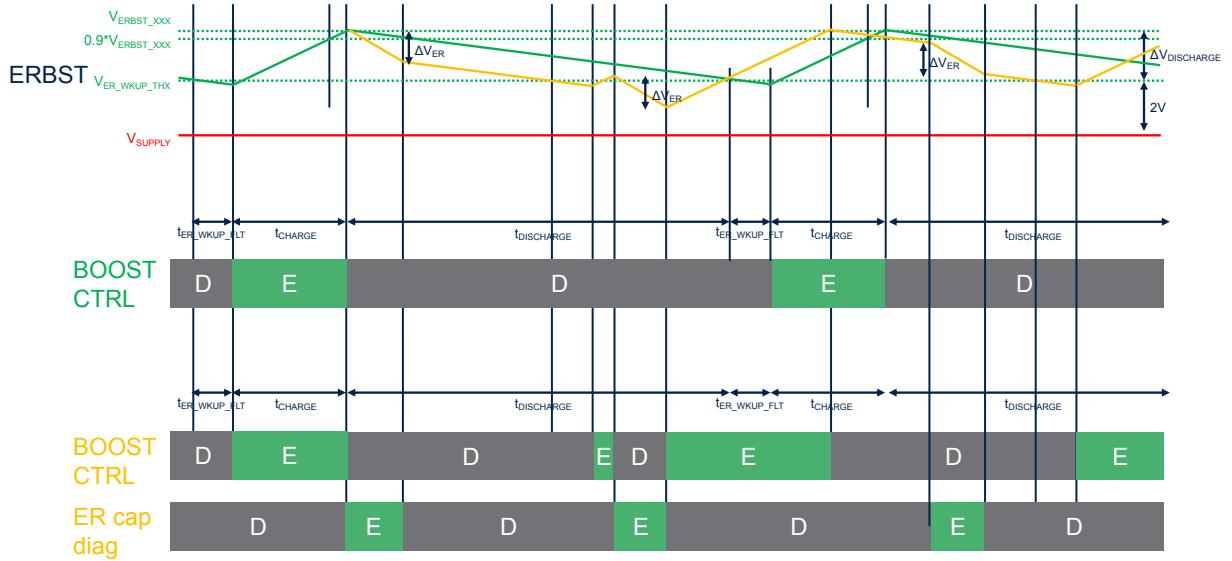

Once started, the boost operates according to a bang-bang strategy, as shown in the Figure 4:

- The controller is enabled and boosts the battery voltage whenever  $V_{ERBST}$  falls below the  $V_{ER\_WKUP\_THX}$  voltage programmed in the **VER\_WKUP\_TH** bit field for an interval longer than  $t_{ER\_WKUP\_FLT}$ . While in the duty phase, the IC is kept in NORMAL and any transition to DEEP-SLEEP is delayed until the setpoint has been reached.

- The controller is disabled whenever  $V_{ERBST}$  reaches the target  $V_{ERBST\_XXX}$  setpoint.

This strategy guarantees high energy efficiency meantime the ER cap voltage is always charged for firing the pyro-fuse. In fact, considering the typical range for  $C_{ERBST}$  capacitor, the boost controller spends most of the time in the disabled state.

Figure 4. ERBST controller working principle

To allow quick charging of the ER cap at every system startup, the boost controller has been designed to guarantee a maximum  $t_{ERBST\_STARTUP}$  startup time in the worst-case application scenario.

Moreover, the controller has been designed to limit the maximum power consumption to  $P_{IN\_ERBST}$ . It is possible to enable this function through the **PIN\_LIMIT** bit in NVM.

Note:

*In applications where the power limitation is required, to limit the initial inrush current it is possible to mount the resistor  $R_{CHG}$  between the **VBATMON** pin and the **ERBST** inductor  $L_{ERBST}$ . Once the initial charge phase has finished ( $V_{ERBST} > V_{VBATMON} - V_{ERBST\_DIS}$ ), the **ERBST\_RDY** bit is set to 1. The MCU can read this flag and drive a GPIO to short the resistor  $R_{CHG}$ .*

It is possible to keep disabled the ERBST regulator setting **ERBST\_DIS=1** in the ERBOOST register.

### 3.3.1.1 ERBST diagnostics

**Table 9. ERBST diagnostics**

| Fault type       | Assertion condition                                                                                                                                                        | IC reaction to assertion                                                                                                                                                         | Release condition                                                                                                          | IC reaction to flag clear                                   | Maskable                                                                                                                                     |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| ERBST UV         | If the $V_{ERBST}$ voltage falls below $V_{ERBST\_UV\_TH}$ for an interval longer than $t_{ERBST\_UV\_FLT}$ the ERBST UV fault is acknowledged                             | The ERBST_UV flag is set<br>FAULTN line is asserted<br>The "fire inhibit" signal is set                                                                                          | If the $V_{ERBST}$ voltage rises above $V_{ERBST\_UV\_TH} + V_{ERBST\_UV\_HYS}$ , the fault flag can be cleared by MCU     | FAULTN line is released<br>Pyro-fuse fire is possible again | Non-maskable                                                                                                                                 |

| ERBST OV         | If the $V_{ERBST}$ voltage rises above $V_{ERBST\_OV\_TH}$ for an interval longer than $t_{ERBST\_OV\_FLT}$ the ERBST OV fault is acknowledged                             | The ERBST_OV flag is set<br>FAULTN line is asserted<br>The ERBST is turned OFF<br>The "fire inhibit" signal is set                                                               | If the $V_{ERBST}$ voltage drops below $V_{ERBST\_OV\_TH} - V_{ERBST\_OV\_HYS}$ , the fault flag can be cleared by MCU     | FAULTN line is released<br>Pyro-fuse fire is possible again | <b>ERBST_OV_FAULTN_MSK</b> masks fault redirection on FAULTN pin<br><b>ERBST_OV_FIRE_MSK</b> masks the inhibition of pyro-fuse fire commands |

| ERBTSW OC        | If the ERBTSW current raises above $I_{ERBTSW\_OC}$ for $N_{ERBTSW\_OC\_COUNT}$ times the ERBST OC fault is acknowledged                                                   | The ERBST_OC flag is set<br>FAULTN line is asserted<br>The ERBST is turned OFF                                                                                                   | Power cycle (CWUP toggle) is needed to restart again                                                                       | None                                                        | <b>ERBTSW_OC_FAULTN_MSK</b> masks fault redirection on FAULTN pin                                                                            |

| ERBTSW OT        | If the ERSBTSW driver temperature exceeds $T_{ERBTSW\_SD}$ for an interval longer than $t_{ERBTSW\_SD\_FLT}$ the ERBST OT fault is acknowledged                            | The ERBST_OT flag is set<br>FAULTN line is asserted<br>The ERBST is turned OFF                                                                                                   | If the ERBTSW driver temperature drops below $T_{ERBTSW\_SD} - T_{ERBTSW\_SD\_HYS}$ , the fault flag can be cleared by MCU | ERBST re-enabled<br>FAULTN line is released                 | <b>ERBTSW_OT_FAULTN_MSK</b> masks fault redirection on FAULTN pin                                                                            |

| ERBST diode loss | If $V_{ERBTSW} - V_{ERBST}$ voltage rises above the $V_{ERBST\_DLOSS\_TH}$ threshold for $N_{ERBTSW\_DLOSS\_COUNT}$ times, the external diode loss failure is acknowledged | The ERBST_DLOSS flag is set<br>FAULTN line is asserted<br>The ERBST is turned OFF<br>The ERBTSW clamping voltage is activated, limiting the voltage value to $V_{ERBTSW\_CLAMP}$ | Power cycle (CWUP toggle) is needed to restart again                                                                       | None                                                        | <b>ERBTSW_DLOSS_FAULTN_MSK</b> masks fault redirection on FAULTN pin                                                                         |

| BSTGND loss      | See the Section 3.13: Ground loss monitor (GNDMON)                                                                                                                         | See the Section 3.13: Ground loss monitor (GNDMON)                                                                                                                               | See the Section 3.13: Ground loss monitor (GNDMON)                                                                         | See the Section 3.13: Ground loss monitor (GNDMON)          | See the Section 3.13: Ground loss monitor (GNDMON)                                                                                           |

### 3.3.1.2 ERBST electrical parameters

All parameters are tested and guaranteed in the following conditions, unless otherwise noted: all supplies according to the Table 3;  $T_J$  according to the Table 2.

**Table 10. ERBST supply electrical parameters**

| Symbol               | Parameter                      | Test condition                                                   | Min  | Typ | Max  | Unit | Pin   |

|----------------------|--------------------------------|------------------------------------------------------------------|------|-----|------|------|-------|

| $V_{ERBST\_UV\_TH}$  | ERBST undervoltage threshold   | Max slew rate = 2.3 V/ms                                         | 4.7  | -   | 5.3  | V    | ERBST |

| $V_{ERBST\_UV\_HYS}$ | ERBST undervoltage hysteresis  | Max slew rate = 2.3 V/ms                                         | 50   | -   | 150  | mV   | ERBST |

| $t_{ERBST\_UV\_FLT}$ | ERBST undervoltage filter time | Tested by SCAN                                                   | 7    | 9   | 11   | us   | ERBST |

| $V_{ERBST\_OV\_TH}$  | ERBST overvoltage threshold    | Considering max nom value of 26 V + 5%, max slew rate = 2.3 V/ms | 27.4 | -   | 31.1 | V    | ERBST |

| Symbol                 | Parameter                                                                  | Test condition                                                                                             | Min   | Typ | Max   | Unit | Pin            |

|------------------------|----------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|-------|-----|-------|------|----------------|

| $V_{ERBST\_OV\_HYS}$   | ERBST overvoltage hysteresis                                               | Max slew rate = 2.3 V/ms                                                                                   | 150   | -   | 250   | mV   | ERBST          |

| $t_{ERBST\_OV\_FLT}$   | ERBST overvoltage filter time                                              | Tested by SCAN                                                                                             | 17    | 20  | 21    | us   | ERBST          |

| $V_{ERBST\_000}$       | ERBST regulated voltage                                                    | $ERBST\_SET = 000$<br>All operating lines and loads                                                        | 16.92 | 18  | 19.08 | V    | ERBST          |

| $V_{ERBST\_001}$       |                                                                            | $ERBST\_SET = 001$<br>All operating lines and loads                                                        | 17.86 | 19  | 20.14 | V    | ERBST          |

| $V_{ERBST\_010}$       |                                                                            | $ERBST\_SET = 010$<br>All operating lines and loads                                                        | 18.80 | 20  | 21.20 | V    | ERBST          |

| $V_{ERBST\_011}$       |                                                                            | $ERBST\_SET = 011$<br>All operating lines and loads                                                        | 19.74 | 21  | 22.26 | V    | ERBST          |

| $V_{ERBST\_100}$       |                                                                            | $ERBST\_SET = 100$<br>All operating lines and loads                                                        | 20.68 | 22  | 23.32 | V    | ERBST          |

| $V_{ERBST\_101}$       |                                                                            | $ERBST\_SET = 101$<br>All operating lines and loads                                                        | 21.62 | 23  | 24.38 | V    | ERBST          |

| $V_{ERBST\_110}$       |                                                                            | $ERBST\_SET = 110$<br>All operating lines and loads                                                        | 22.56 | 24  | 25.44 | V    | ERBST          |

| $V_{ERBST\_111}$       |                                                                            | $ERBST\_SET = 111$<br>All operating lines and loads                                                        | NA    | NA  | NA    | V    | ERBST          |

| $V_{ER\_WKUP\_TH0}$    | ERBST cap discharge threshold (in tracking with $V_{ERBST\_XXX}$ setpoint) | $VER\_WKUP\_TH = 000$                                                                                      | 15.04 | 16  | 16.96 | V    | ERBST          |

| $V_{ER\_WKUP\_TH1}$    |                                                                            | $VER\_WKUP\_TH = 001$                                                                                      | 15.98 | 17  | 18.02 | V    | ERBST          |

| $V_{ER\_WKUP\_TH2}$    |                                                                            | $VER\_WKUP\_TH = 010$                                                                                      | 16.92 | 18  | 19.08 | V    | ERBST          |

| $V_{ER\_WKUP\_TH3}$    |                                                                            | $VER\_WKUP\_TH = 011$                                                                                      | 17.86 | 19  | 20.14 | V    | ERBST          |

| $V_{ER\_WKUP\_TH4}$    |                                                                            | $VER\_WKUP\_TH = 100$                                                                                      | 18.80 | 20  | 21.20 | V    | ERBST          |

| $V_{ER\_WKUP\_TH5}$    |                                                                            | $VER\_WKUP\_TH = 101$                                                                                      | 19.74 | 21  | 22.26 | V    | ERBST          |

| $V_{ER\_WKUP\_TH6}$    |                                                                            | $VER\_WKUP\_TH = 110$                                                                                      | 20.68 | 22  | 23.32 | V    | ERBST          |

| $V_{ER\_WKUP\_TH7}$    |                                                                            | $VER\_WKUP\_TH = 111$                                                                                      | NA    | NA  | NA    | V    | ERBST          |

| $t_{ERBST\_WKUP\_FLT}$ | ERBST discharge comparator deglitch                                        | Guaranteed by SCAN                                                                                         | 17    | 20  | 21    | μs   | ERBST          |

| $P_{IN\_ERBST}$        | Boost input peak power                                                     | Input power limitation to guarantee $t_{ERBST\_STARTUP}$ in $V_{IN} = 6 \text{ V}$ to $18 \text{ V}$ range | 1.8   | -   | 2.6   | W    | ERBST          |

| $\eta_{ERBST}$         | Boost efficiency                                                           | $P_{IN\_ERBST} = P_{IN\_ERBST\max}$<br>$V_{IN} = 6 \text{ V}$<br>Guaranteed by design                      | 0.6   | -   | -     | W/W  | ERBST, ERBSTSW |

| $f_{ERBST}$            | Switching frequency                                                        | Design info, taking in consideration temperature and external competent variations                         | 1.6   | -   | 2.4   | MHz  | ERBST          |

| $t_{ERBST\_ON\_MIN}$   | Minimum ON-time                                                            | Design info                                                                                                |       | 80  | -     | ns   | ERBSTSW        |

| $C_{ERBST}$            | External output capacitor                                                  | Application info, including component tolerance                                                            | 0.1   | -   | 1.2   | mF   | ERBST          |

| $C_{ERBST\_ESR}$       | External output capacitor ESR                                              | Application info, including component tolerance                                                            | 100   | -   | 500   | mΩ   | ERBST          |

| Symbol                    | Parameter                               | Test condition                                                                                      | Min  | Typ | Max  | Unit | Pin            |

|---------------------------|-----------------------------------------|-----------------------------------------------------------------------------------------------------|------|-----|------|------|----------------|

| $L_{ERBST}$               | External output inductor                | $I_{SAT} \gg I_{ERBST\_PEAK\_LIM}$<br>Application info                                              | -20% | 33  | +20% | μH   | ERBST          |

| $L_{ERBST\_DCR}$          | External inductor DCR                   | Application info                                                                                    |      | -   | 1.5  | Ω    | ERBST          |

| $V_{DFW}$                 | External diode forward voltage          | Application info                                                                                    |      | -   | 1.2  | V    | ERBST          |

| $V_{ERBST\_DIS}$          | ERBST disable threshold during power-up | Voltage difference between VBATMON pin and ERBST pin                                                | 1.5  | 2.2 | 2.7  | V    | VBATMON, ERBST |

| $t_{ERBST\_READY\_FLT}$   | ERBST ready filter time                 | Tested by SCAN                                                                                      | 10   | 20  | 25   | μs   | VBATMON, ERBST |

| $t_{ERBST\_STARTUP}$      | ERBST startup time                      | From $V_{ERBST} = 5.3$ V to 90% of $V_{ERBST\_110}$<br>$C_{ERBST} = C_{ERBSTmax}$<br>$V_{IN} = 6$ V |      | -   | 220  | ms   | ERBST          |

| $T_{ERBTSW\_SD}$          | Thermal shutdown threshold              | Guaranteed by design                                                                                | 150  | -   | 190  | °C   | ERBST          |

| $T_{ERBTSW\_SD\_HYS}$     | Thermal shutdown threshold hysteresis   | Guaranteed by design                                                                                | 5    | -   | 15   | °C   | ERBST          |

| $t_{ERBST\_SD\_FLT}$      | Thermal shutdown filter time            | Guaranteed by design                                                                                | 7    | 8.5 | 10   | μs   | ERBST          |

| $I_{ERBST\_PEAK\_LIM\_0}$ | ERBTSW peak current limitation          | <b>PIN_LIMIT = 0</b>                                                                                | 330  | -   | 480  | mA   | ERBTSW         |

| $I_{ERBST\_PEAK\_LIM\_1}$ | ERBTSW peak current limitation          | <b>PIN_LIMIT = 1</b><br>$V_{IN} = 6$ V                                                              | 300  | -   | 440  | mA   | ERBTSW         |

| $I_{ERBST\_OC}$           | ERBTSW overcurrent threshold            |                                                                                                     | 460  | -   | 700  | mA   | ERBTSW         |

| $N_{ERBST\_OC\_COUNT}$    | Number of counts before turn-off        | Overcurrent events                                                                                  | -    | 5   | -    | #    | ERBTSW         |

| $R_{DSON\_ERBTSW}$        | Boost switch ON resistance              |                                                                                                     | -    | -   | 1    | Ω    | ERBTSW         |

| $V_{ERBST\_DLOSS\_TH}$    | ERBST diode loss detection threshold    | Voltage difference between ERBTSW pin and ERBST pin                                                 | 2.3  | 3.3 | 4.0  | V    | ERBST, ERBTSW  |

| $V_{ERBTSW\_CLAMP}$       | ERBTSW pin clamping voltage             | Diode loss                                                                                          | 33   | -   | 40   | V    | ERBTSW         |

| $N_{ERBST\_DLOSS\_COUNT}$ | Number of counts before turn-off        | Diode loss clamping events                                                                          | -    | 3   | -    | #    | ERBTSW         |

| $t_{RISE\_ERBTSW}$        | ERBTSW rise time                        | From 10% to 90% of $V_{ERBTSW\_max}$<br>Min $I_{ERDCHSW}$ peak current<br>Application info          | -    | -   | 15   | ns   | ERBTSW         |

| $t_{FALL\_ERBTSW}$        | ERBTSW fall time                        | From 90% to 10% of $V_{ERBTSW\_max}$<br>Max $I_{ERDCHSW}$ peak current<br>Application info          | -    | -   | 20   | ns   | ERBTSW         |

### 3.3.2 Power stage supply (PS)

The PS pin is the power stage supply input. This line:

- Feeds the level shifters between the **signal stage** and the **power stage**.

- Feeds the HS circuitry of the **power stage**.

#### 3.3.2.1 PS diagnostics

**Table 11. PS diagnostics**

| Fault type | Assertion condition                                                                    | IC reaction to assertion                                                             | Release condition                                                                                             | IC reaction to flag clear                                   | Maskable                                                                                                                               |

|------------|----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| PS UV      | If the $V_{PS}$ voltage falls below $V_{PS\_UV\_TH}$ , the PS_UV fault is acknowledged | The PS_UV flag is set<br>FAULTN line is asserted<br>The “fire inhibit” signal is set | If the $V_{PS}$ voltage rises above $V_{PS\_UV\_TH} + V_{PS\_UV\_HYS}$ , the PS_UV flag can be cleared by MCU | FAULTN line is released<br>Pyro-fuse fire is possible again | Non-maskable                                                                                                                           |

| PS OV      | If the $V_{PS}$ voltage rises above $V_{PS\_OV\_TH}$ , the PS_OV fault is acknowledged | The PS_OV flag is set<br>FAULTN line is asserted<br>The “fire inhibit” signal is set | If the $V_{PS}$ voltage drops below $V_{PS\_OV\_TH} - V_{PS\_OV\_HYS}$ , the PS_OV flag can be cleared by MCU | FAULTN line is released<br>Pyro-fuse fire is possible again | <b>PS_OV_FAULTN_MSK</b> masks fault redirection on FAULTN pin<br><b>PS_OV_FIRE_MSK</b> masks the inhibition of pyro-fuse fire commands |

#### 3.3.2.2 PS electrical parameters

All parameters are tested and guaranteed in the following conditions, unless otherwise noted: all supplies according to the [Table 3](#);  $T_J$  according to the [Table 2](#).

**Table 12. PS supply electrical parameters**

| Symbol            | Parameter                   | Test condition                                                     | Min  | Typ | Max  | Unit | Pin |

|-------------------|-----------------------------|--------------------------------------------------------------------|------|-----|------|------|-----|

| $V_{PS\_UV\_TH}$  | PS undervoltage threshold   | Max slew rate = 2.3 V/ms                                           | 4.7  | -   | 5.3  | V    | PS  |

| $V_{PS\_UV\_HYS}$ | PS undervoltage hysteresis  | Max slew rate = 2.3 V/ms                                           | 150  | -   | 250  | mV   | PS  |

| $t_{PS\_UV\_FLT}$ | PS undervoltage filter time | Tested by SCAN                                                     | 17   | 20  | 21   | μs   | PS  |

| $V_{PS\_OV\_TH}$  | PS overvoltage threshold    | Considering max nom value of 26 V + 5%<br>Max slew rate = 2.3 V/ms | 27.4 | -   | 31.1 | V    | PS  |

| $V_{PS\_OV\_HYS}$ | PS overvoltage hysteresis   | Max slew rate = 2.3 V/ms                                           | 150  | -   | 250  | mV   | PS  |

| $t_{PS\_OV\_FLT}$ | PS overvoltage filter time  | Tested by SCAN                                                     | 17   | 20  | 21   | μs   | PS  |

### 3.3.3 IO output buffer supply (VIO)

The VIO pin is the digital output buffer supply. This line feeds the SDO output buffer. It is suggested to add a bypass ceramic capacitor near the VIO pin.

The VIO shall be supplied externally and it enables compatibility with both 3.3 V and 5 V controllers.

There is no diagnostic on the VIO supply.

## 3.4 Wake-up sources

The following section lists the available wake-up sources and their behavior.

Whenever a wake-up source is validated, the wake-up sequence is initiated and shall successfully end within  $t_{WAKEUP\_TIMEOUT}$ . Otherwise, the IC returns to the previously held low power state.

**Table 13. Wake-up sources electrical parameters**

| Symbol                | Parameter                                   | Test condition | Min | Typ | Max | Unit | Pin                   |

|-----------------------|---------------------------------------------|----------------|-----|-----|-----|------|-----------------------|

| $t_{WAKEUP\_TIMEOUT}$ | Timeout for completing the wake-up sequence | Tested by SCAN | 20  | -   | 25  | ms   | CWUP, FENH, FENL, SPI |

### 3.4.1 Wake-up from cyclic wake-up pin (CWUP)

The CWUP pin can be used by the host controller for the following purposes:

- Triggering cyclic wakeups and diagnostics in low-power strategies.

- Keep the device constantly in NORMAL state in full-power strategies.

When the CWUP pin is set high for longer than  $t_{CWUP\_POWERUP\_PULSE}$  ( $t_{CWUP\_FLT}$  filter time is applied), a wake-up condition is acknowledged and latched in the CWUP\_WAKEUP bit in INTERNAL\_STATUS register. The IC completes the power-up phase after  $t_{CWUP\_POWERUP\_TIME}$  since the CWUP signal is set high.

This wake-up source is always available.

#### 3.4.1.1 CWUP electrical parameters

All parameters are tested and guaranteed in the following conditions, unless otherwise noted: all supplies according to the [Table 3](#);  $T_J$  according to the [Table 2](#).

**Table 14. CWUP electrical parameters**

| Symbol                     | Parameter                              | Test condition                                                                               | Min | Typ | Max | Unit | Pin  |

|----------------------------|----------------------------------------|----------------------------------------------------------------------------------------------|-----|-----|-----|------|------|

| $t_{CWUP\_FLT}$            | CWUP filter time                       | Input filter time, guaranteed by design                                                      | 250 | -   | 800 | ns   | CWUP |

| $t_{CWUP\_POWERUP\_PULSE}$ | CWUP min input pulse to start power-up | Minimum time to guarantee a correct power-up (starting from the CWUP low to high transition) | 100 | -   | -   | μs   | CWUP |

| $t_{CWUP\_POWERUP\_TIME}$  | IC wake-up latency                     | From the CWUP low to high transition to the IC in DIAG (full download of NVM)                | -   | -   | 1   | ms   | CWUP |

### 3.4.2 Wake-up from fire enable inputs (FENH/FENL)

In DEEP-SLEEP state the IC is still responsive to FENH/FENL inputs in order to quickly wake-up and be ready to fire when required.

When either FENH/FENL pin holds the active level for longer than  $t_{FENx\_FLT}$ , a wake-up condition is acknowledged and latched in the FENX\_WAKEUP bit in the INTERNAL\_STATUS register.

If active level of FENH and FENL pins disappears after wake-up trigger, the IC remains in NORMAL state for  $t_{FENx\_WAKEUP\_WAIT}$  before returning in DEEP-SLEEP state.

These wake-up sources can be enabled setting **FENH\_EN** = 1 and **FENL\_EN** = 1 in NVM.

The active levels can also be programmed through **FENH\_LEVEL** and **FENL\_LEVEL**.

*Note:*

*In order to speed up the wake-up procedure, when the device is awakened by FENH/FENL pin, NVM operations are locked (neither download nor upload). A transition to DEEP-SLEEP is needed to unlock NVM.*

#### 3.4.2.1 FENH/FENL wake-up electrical parameters

All parameters are tested and guaranteed in the following conditions, unless otherwise noted: all supplies according to the Table 3;  $T_J$  according to the Table 2.

**Table 15. Wake-up sources electrical parameters**

| Symbol                   | Parameter               | Test condition                                                        | Min | Typ | Max | Unit | Pin        |

|--------------------------|-------------------------|-----------------------------------------------------------------------|-----|-----|-----|------|------------|

| $t_{FENx\_FLT}$          | FENH, FENL input filter | Analog filter, guaranteed by design                                   | 250 | -   | 800 | ns   | FENH, FENL |

| $t_{FENx\_WAKEUP\_TIME}$ | IC wake-up latency      | From the FENH/FENL assertion to the IC in ARM state (no NVM download) | -   | -   | 400 | μs   | FENH, FENL |

| $t_{FENx\_WAKEUP\_WAIT}$ | IC wake-up wait         | From the FENH/FENL assertion to the IC return in DEEP-SLEEP state     | 1.8 | 2   | 2.1 | ms   | FENH, FENL |

### 3.4.3 Wake-up via peripheral SPI

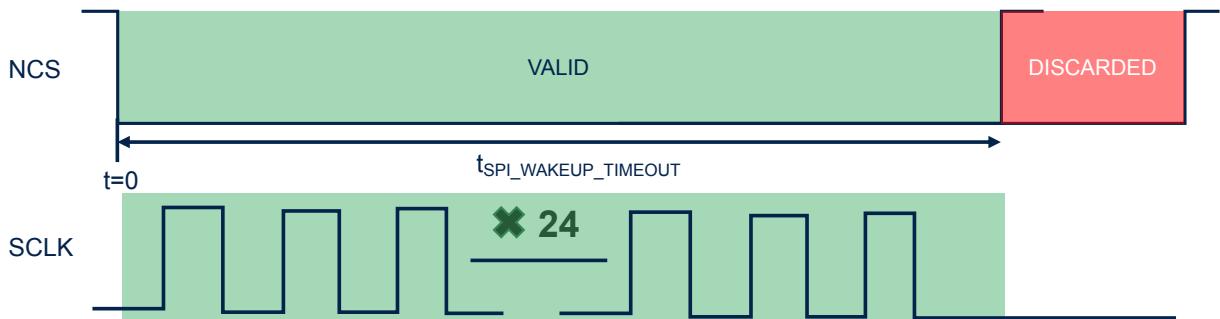

The IC can be woken up by any valid SPI frame. A wake-up condition is acknowledged when the following pattern is received:

1. A NCS high to low transition

2. 24 SCK pulses

3. A NCS low to high transition

To prevent the logic being stuck in the wake-up detection state upon incomplete patterns, the  $t_{SPI\_WAKEUP\_TIMEOUT}$  is started upon every NCS assertion, and the wake-up pattern shall end before timeout expiration, otherwise it is discarded.

Wake-up frames are not decoded, so their content may be arbitrary.

**Note:**

*It is strongly recommended to send READ commands to avoid inadvertent write operations in case the device is already awake.*

When a correct wake-up sequence is acknowledged, the event is latched in the SPI\_WAKEUP bit located in the INTERNAL\_STATUS register. The latch-set pulse also triggers the start of the  $t_{SPI\_COMM\_TIMEOUT}$  communication timeout. Such a timer is intended to avoid the IC being left unintendedly in a high consumption power state in case the controller is unresponsive:

- The  $t_{SPI\_COMM\_TIMEOUT}$  is reset and restarted in case a valid frame is received (no CRC error and correct number of SCK pulses).

- The  $t_{SPI\_COMM\_TIMEOUT}$  is reset and stopped in case a high level is detected on CWUP. From that moment on, moving the device to a low power state requires setting CWUP low.

**Figure 5. Wake-up condition by peripheral SPI**

#### 3.4.3.1 SPI wake-up electrical parameters

All parameters are tested and guaranteed in the following conditions, unless otherwise noted: all supplies according to the Table 3;  $T_J$  according to the Table 2.

**Table 16. SPI electrical parameters**

| Symbol                     | Parameter                                                           | Test condition                                                              | Min | Typ | Max | Unit | Pin                 |

|----------------------------|---------------------------------------------------------------------|-----------------------------------------------------------------------------|-----|-----|-----|------|---------------------|

| $t_{SPI\_WAKEUP\_TIMEOUT}$ | Timeout for receive of wake-up frame                                | Guaranteed by SCAN                                                          | 0.4 | -   | 2   | ms   | NCS, SDI, SDO, SCLK |

| $t_{SPI\_COMM\_TIMEOUT}$   | Communication timeout started in case of wake-up via peripheral SPI | Guaranteed by SCAN                                                          | -   | 2   | -   | s    | NCS, SDI, SDO, SCLK |

| $t_{SPI\_WAKEUP\_TIME}$    | IC wake-up latency                                                  | From the NCS low to high transition to the IC in NORMAL (full NVM download) | -   | -   | 1   | ms   | NCS, SDI, SDO, SCLK |

## 3.5

**Fault notification (FAULTN)**

Detected faults are reported via SPI by the FAULTN\_ECHO bit of the GSW. The FAULTN\_ECHO bit being set to '1' indicates the IC has not detected a failure.

Additionally, the fault status can also be reported by the FAULTN output, which can be disabled by setting **FAULTN\_DIS** = 1 in NVM.

Whenever a fault condition is detected, the open-drain FAULTN output is asserted low. The output is released when every latched fault has been cleared.

Depending on the IC configuration, some diagnostics can be masked and their redirection onto FAULTN line can also be masked. Refer to the diagnostic tables for the specific masking conditions.

Whenever a fault is asserted and the CWUP input level is low, the  $t_{FAULT\_HANDLING\_TIMEOUT}$  is released and runs in background. The timeout is reset by the CWUP high level: if the host controller does not raise CWUP before the timeout expires, the IC moves back to DEEP-SLEEP. If a fault occurs when the CWUP input level is high and it is still present when the CWUP input level is set low, the  $t_{FAULT\_HANDLING\_TIMEOUT}$  does not start.

## 3.5.1

**FAULTN integrity check**

To enable reaching the ASIL targets at system level, the IC provides a means to periodically verify the integrity of the FAULTN line. Depending on the power management strategy, different configurations may apply, as reported in the [Table 17](#).

**Table 17. FAULTN configuration according to different power management strategies**

| Power management strategy | L9965C state | L9965P state                                            | CWUP                                         | FAULTN                                      | Configuration                                           | Note                                                                                                                |

|---------------------------|--------------|---------------------------------------------------------|----------------------------------------------|---------------------------------------------|---------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| Full power                | NORMAL       | NORMAL                                                  | Static high                                  | Pulse generation every $t_{FAULTN\_PERIOD}$ | <b>FAULTN_DIS</b> = 0<br><b>FAULTN_CYCLIC_PULSE</b> = 1 | The FAULTN path is continuously checked, allowing quick detection of line stuck failures                            |

| Full power                | NORMAL       | NORMAL                                                  | Static high                                  | Level mode                                  | <b>FAULTN_DIS</b> = 0<br><b>FAULTN_CYCLIC_PULSE</b> = 0 | The FAULTN output integrity can only be verified manually using the <b>FAULTN_FORCE</b> command                     |

| Low power                 | NORMAL       | CYCLIC WAKEUP (alternation between DEEP-SLEEP and DIAG) | Cyclic high pulse generated by L9965C or MCU | Pulse generation every $t_{CWUP\_PERIOD}$   | <b>FAULTN_DIS</b> = 0<br><b>FAULTN_CYCLIC_PULSE</b> = 0 | The FAULTN path is checked at each cyclic wake-up event: FAULTN low pulses are synchronized to received CWUP pulses |

FAULTN\_FORCE should be used only with FAULTN\_CYCLIC\_PULSE = 0. If used with FAULTN\_CYCLIC\_PULSE = 1, it is a fault injection.

When enabled, the integrity check can be executed:

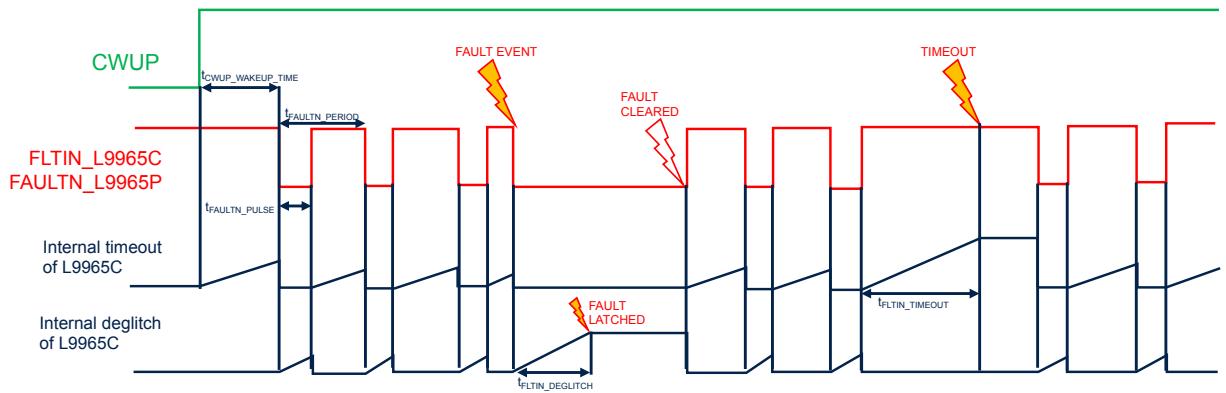

- Continuously in full power mode (refer to the [Figure 6](#))

- This diagnostic requires FAULTN\_CYCLIC\_PULSE = 1. Pulse generation starts  $t_{FAULTN\_PERIOD}$  after such a bit is written high (see the [Figure 7](#)).

- If a failure occurs and FAULTN is held active low for fault signaling, the  $t_{FAULTN\_PERIOD}$  timer is kept under reset. It restarts once all faults have been cleared and FAULTN returns to its inactive high state.

- Manually

- Setting FAULTN\_FORCE = 1 forces the FAULTN output low, instead setting FAULTN\_FORCE = 0 releases the output. The FAULTN\_FORCE command overrides any other FAULTN output buffer driving signal.

- This strategy is recommended when multiple L9965P are present in the system and their FAULTN outputs are connected in wired-OR.

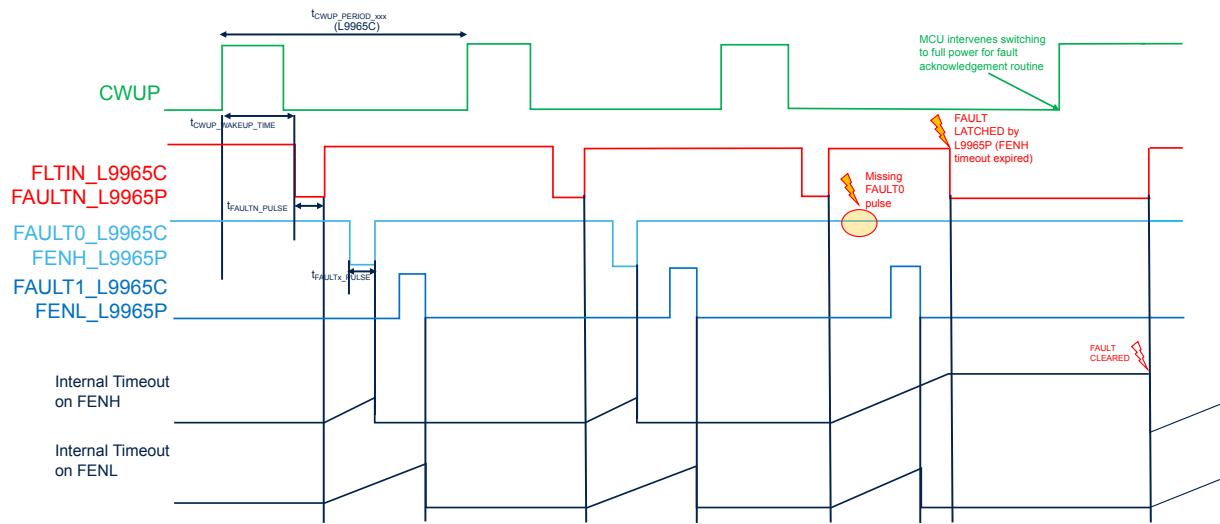

- Once per cycle in low power mode (refer to the [Figure 8](#) and [Figure 9](#))

- At each CWUP rising edge, the L9965P starts its cyclic wake-up.

- Once awake, the L9965P generates a negative pulse lasting  $t_{FAULTN\_PULSE}$  on the FAULTN output line.

- This diagnostic does not require the use of the FAULTN\_CYCLIC\_PULSE bit since the FAULTN pin is automatically checked at each wake-up cycle.

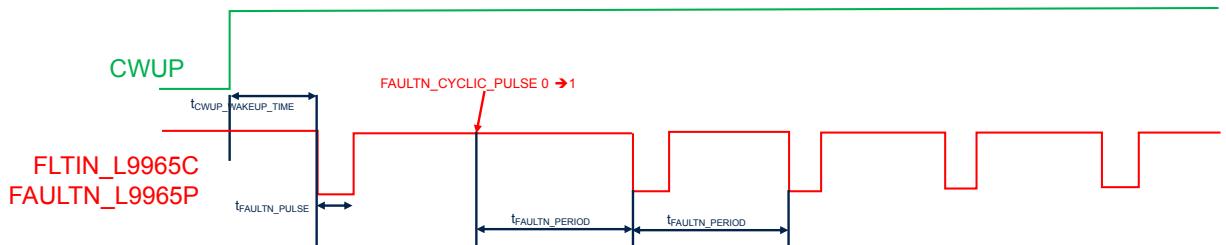

**Figure 6. FAULTN integrity check in full power mode**

**Figure 7. FAULTN cyclic pulse generation start**

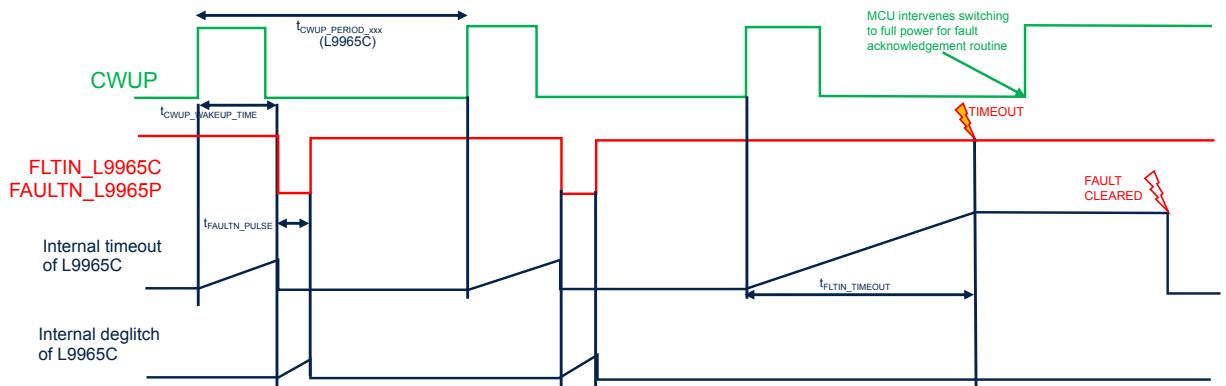

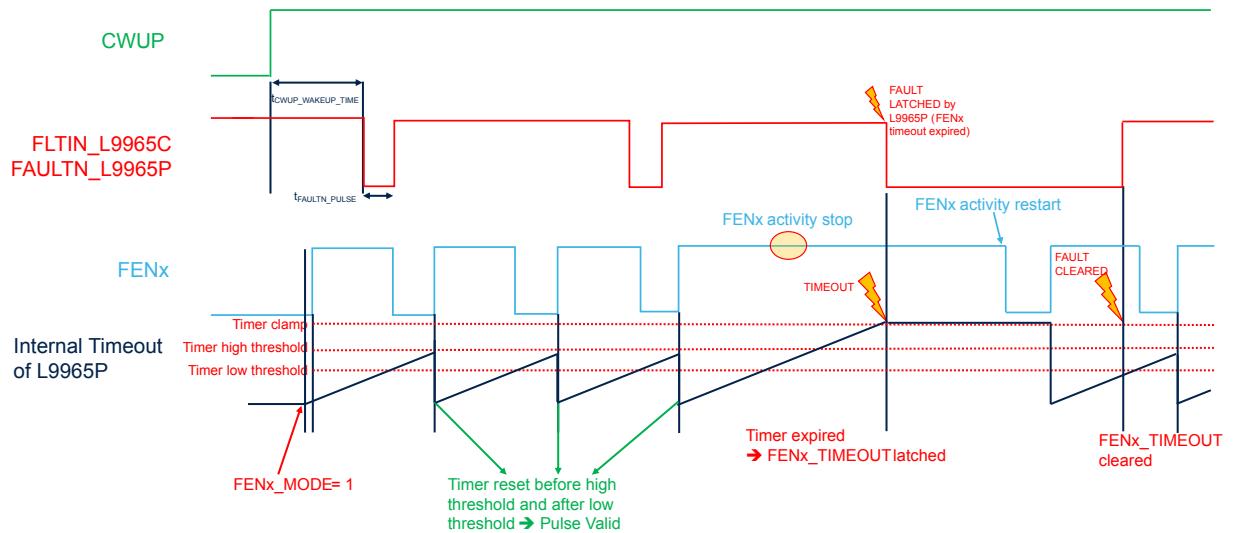

**Figure 8. FAULTN integrity check in low power mode (example of timeout detected by L9965C)**

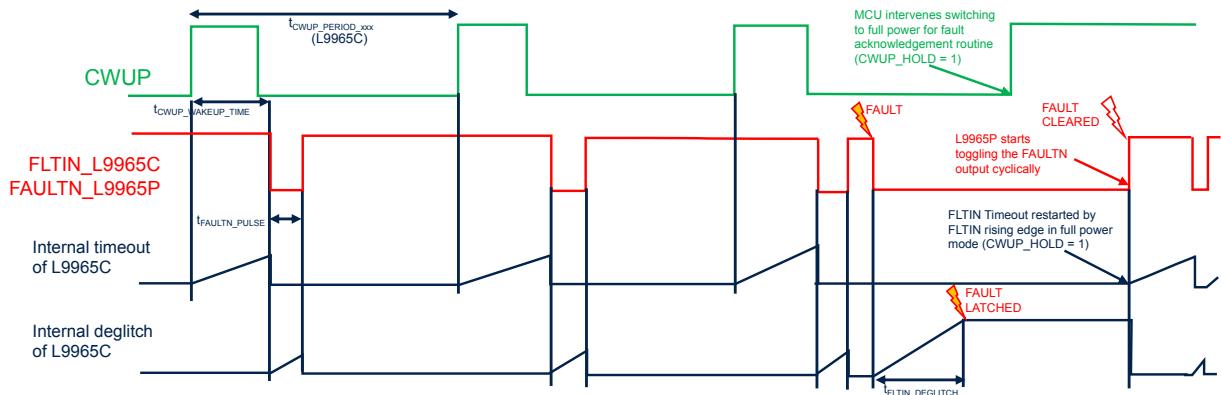

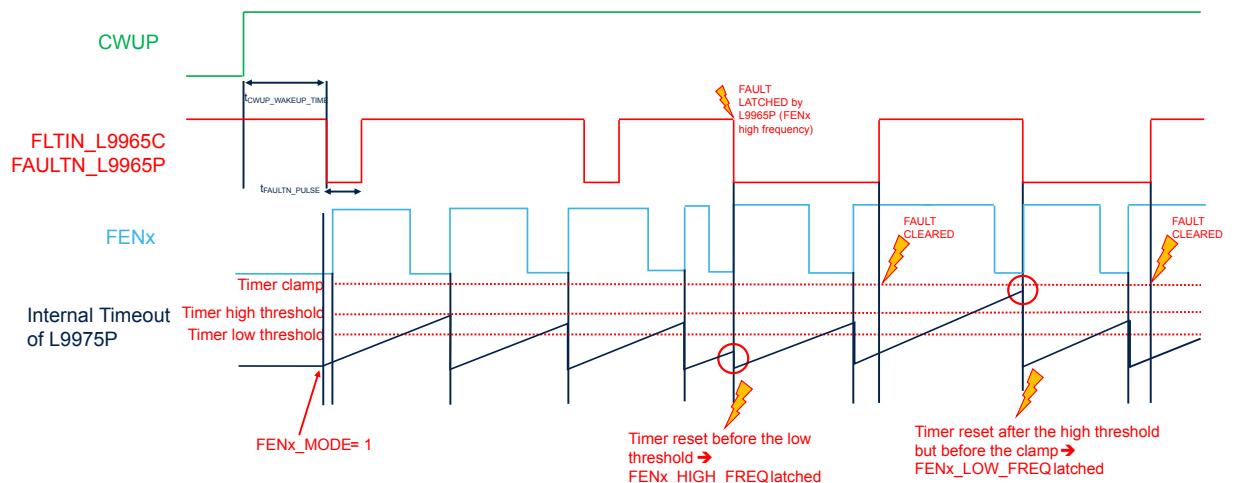

Figure 9. FAULTN integrity check in low power mode (example of fault detected by L9965P)

### 3.5.2 FAULTN electrical parameters

All parameters are tested and guaranteed in the following conditions, unless otherwise noted: all supplies according to the Table 3;  $T_J$  according to the Table 2.

Table 18. FAULTN electrical parameters

| Symbol                         | Parameter                            | Test condition     | Min | Typ | Max  | Unit    | Pin    |

|--------------------------------|--------------------------------------|--------------------|-----|-----|------|---------|--------|

| $t_{FAULTN\_PERIOD}$           | FAULTN line integrity pulse period   | Guaranteed by SCAN | 5.5 | -   | 14.5 | ms      | FAULTN |

| $t_{FAULTN\_PULSE}$            | FAULTN line integrity pulse duration | Guaranteed by SCAN | -   | 10  | -    | $\mu$ s | FAULTN |

| $t_{FAULT\_HANDLING\_TIMEOUT}$ | Fault handling timeout               | Guaranteed by SCAN | 1.8 | 2   | 2.1  | s       | FAULTN |

## 3.6

## Pyro-fuse deployment stage

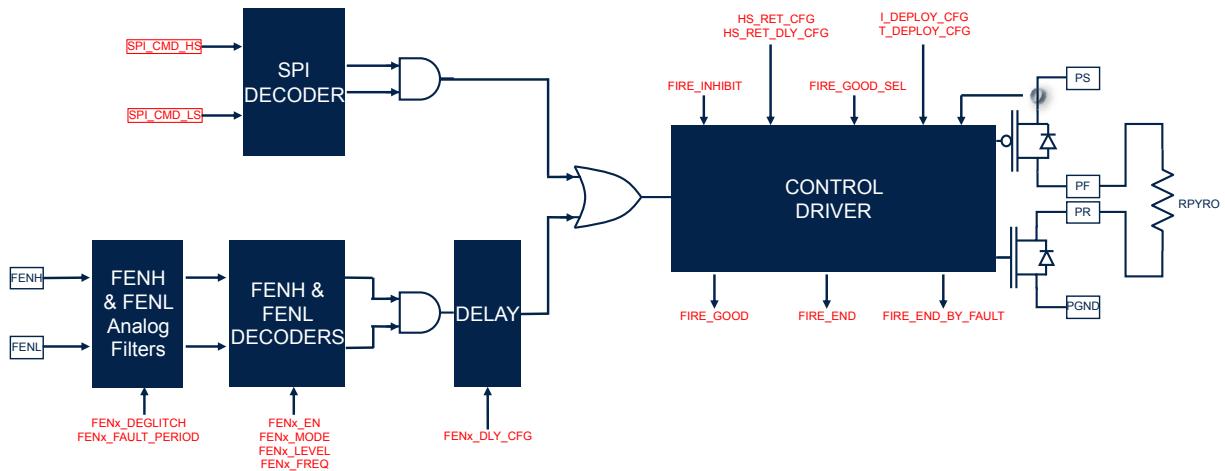

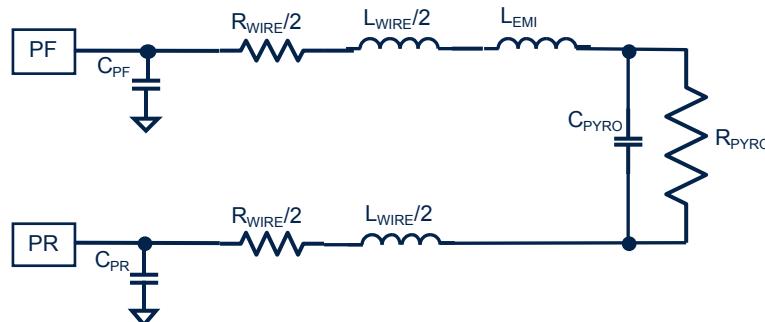

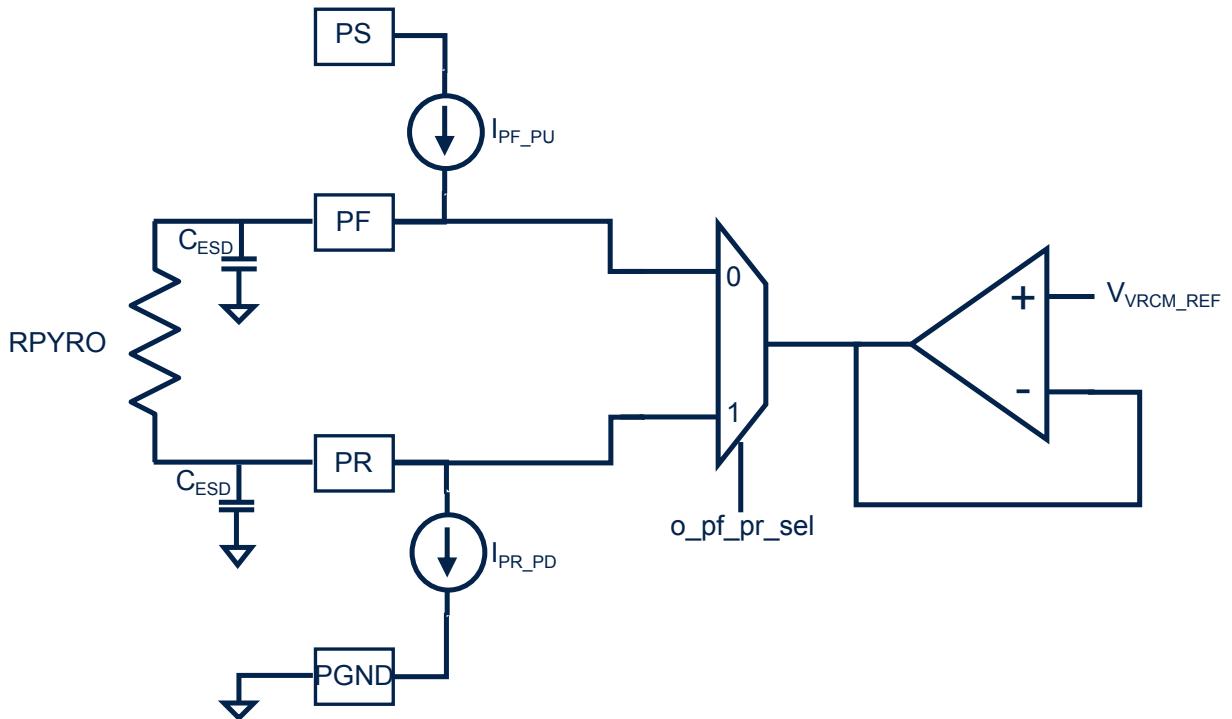

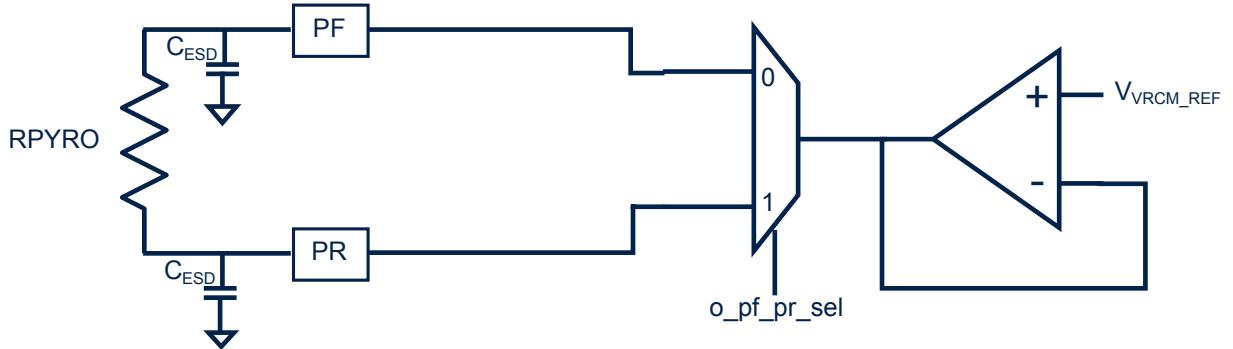

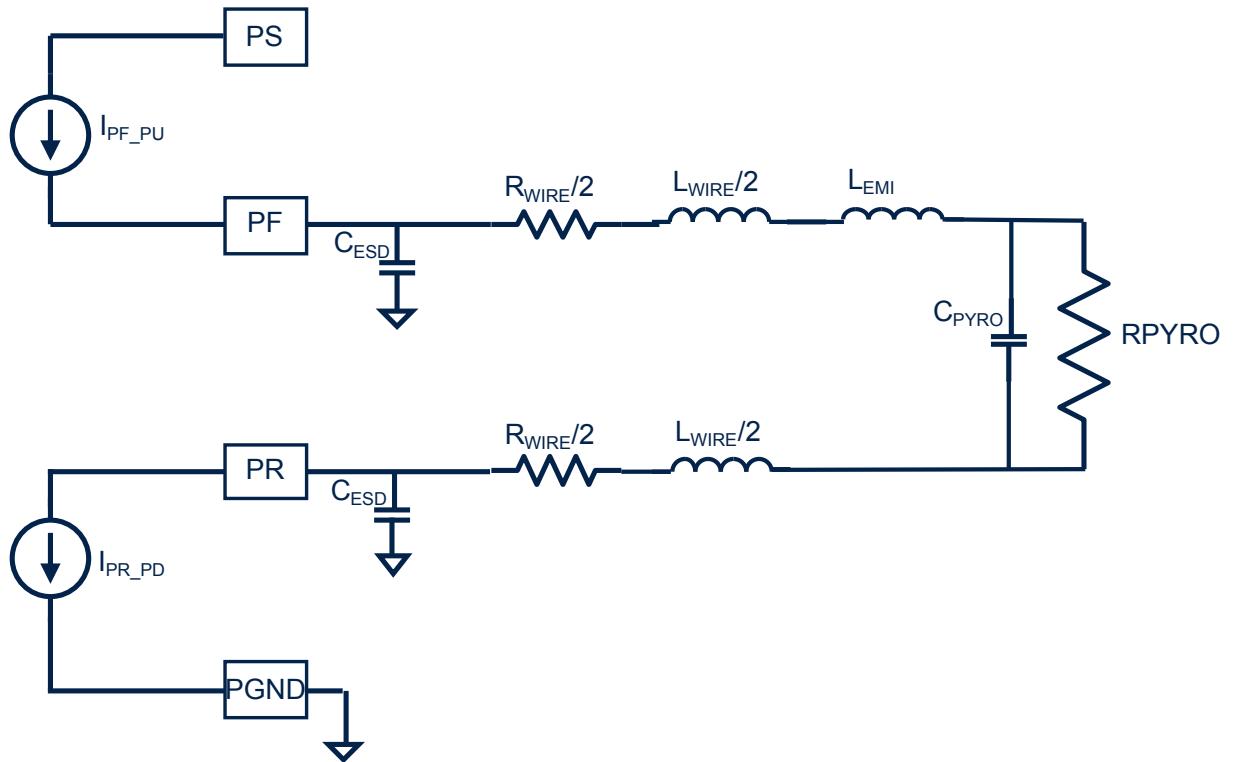

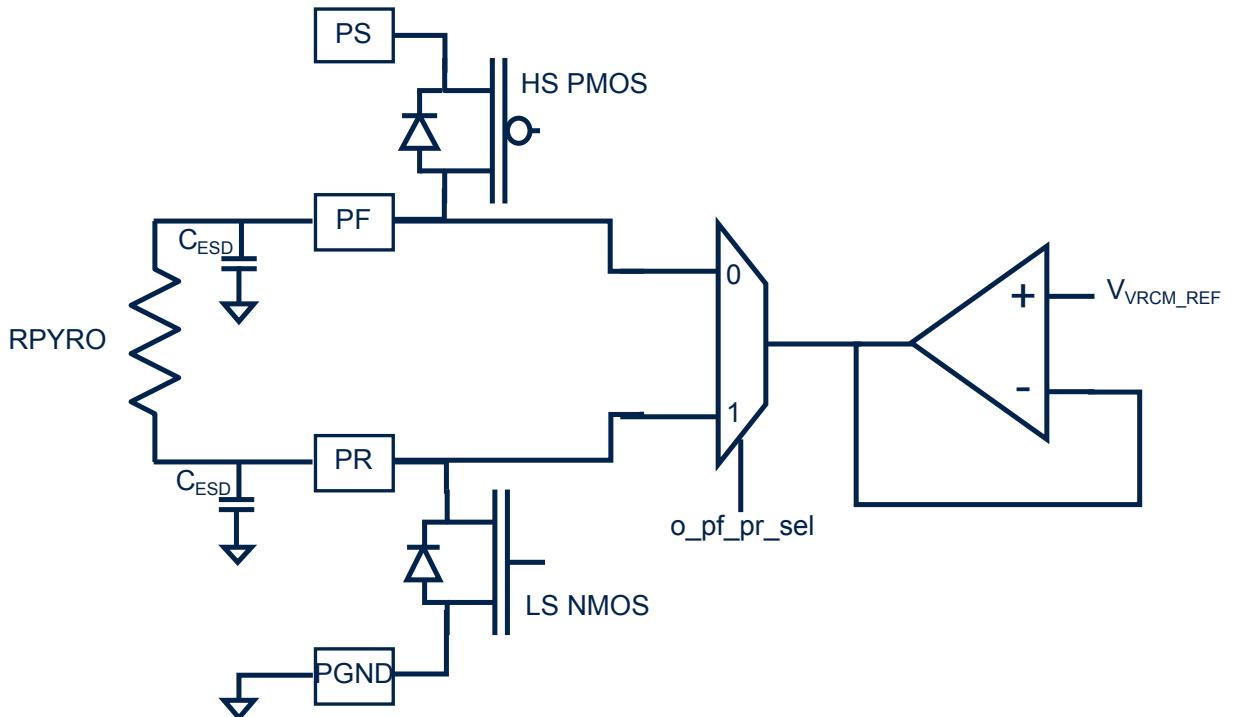

The Figure 10 shows the pyro-fuse deployment stage architecture.

Figure 10. Pyro-fuse deployment stage architecture

Two independent paths are implemented to drive the HS and LS output switches:

- One via hardware through FENH and FENL pins.

- One via software through two SPI commands.

Three substages are present:

- Signal stage

- The FENH and FENL signals decoders are configured via SPI registers and their configuration is stored into NVM.

- A delay stage on the FENx path enables fine-tuning of the trigger output propagation delay for applications where several L9965P pyro-fuse drivers need to be phase-shifted.

- A parallel decoder stage for SPI arming commands is available.

- Control driver

- The control driver translates the signal stage outputs into suitable commands for the power-stage output domain.

- Power stage

- The LS and HS are turned on by a latch whose reset occurs whenever the fire attempt ends successfully or the deploy timer expires.

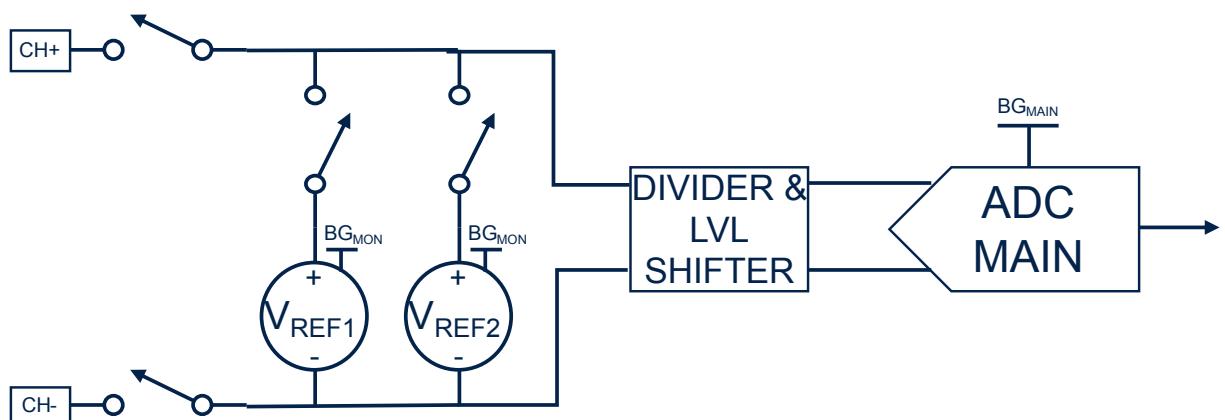

- A HS current sensing is implemented to deploy the pyro-fuse with the programmed current profile and manage the deployment autoretry.

- The power stage is inhibited by a “fire inhibit” signal in case a fault occurs.

### 3.6.1 Signal stage (FENH/FENL/SPI)

The IC has two digital inputs, FENH and FENL, whose signals are treated by two different decoders to generate the driving stimulus for the HS and LS switches.

Additionally, the switches can be triggered by dedicated SPI commands.

The FENH/FENL/SPI decoders are only available in DIAG, NORMAL and ARM states, while in DEEP-SLEEP they are disabled, since FENH/FENL/SPI may only be used as wake-up sources.

#### 3.6.1.1 FENH/FENL decoders configuration

The two decoders can be individually enabled by setting **FENH\_EN** = 1 and **FENL\_EN** = 1. When disabled, their output is always in the inactive state (no trigger).

Before being input to the digital decoders, the FENH/FENL inputs are always pre-filtered by an analog stage ( $t_{FENx\_FLT}$ ) to prevent noise from altering the decoding process.

Each decoder can be configured in different modes:

- **FENH\_MODE/FENL\_MODE** = 0 sets the level-based decoding

- A programmable deglitch filter  $t_{FENx\_DEGLITCH}$  helps to filter out unwanted spikes on the trigger inputs. The deglitch value is valid for both FENH and FENL inputs.

- When the FENL/FENH deglitched signal holds the active level, an arming condition is acknowledged on the corresponding branch.

- **FENH\_MODE/FENL\_MODE** = 1 sets the PWM-based decoding. The PWM-based encoding allows the L9965P continuously monitoring the status of the trigger lines, being capable of detecting frequency drifts and stuck-at faults in real-time, as described in the [Section 3.6.1.2: FENH/FENL integrity check](#).

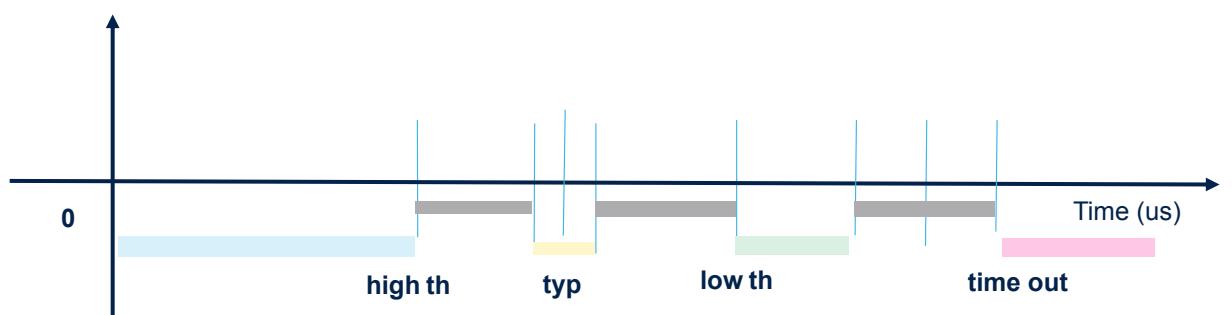

The decoder frequency can be selected between two options:

- **FENH\_FREQ/FENL\_FREQ** = 0 sets the 125 kHz option

- **FENH\_FREQ/FENL\_FREQ** = 1 sets the 16 kHz option

The programmable  $N_{FENx\_FAULT\_PERIOD}$  up/down counter is used to deglitch the PWM periods. The counter value is valid for both FENH and FENL inputs. The counter output behaves as follows:

- In case it reaches the programmed threshold, it saturates and an arming condition is acknowledged on the corresponding branch.

- In case the output value is less than the programmed threshold, the arming is released.

The FENH/FENL active state is configured through **FENH\_LEVEL/FENL\_LEVEL** bits:

- **FENH\_LEVEL = FENL\_LEVEL** = 0 sets the active state to:

- Low level in case of level-based decoding ( $FENx\_MODE$  = 0)