# X20DC4395

Data sheet 3.30 (October 2024)

#### **Publishing information**

B&R Industrial Automation GmbH B&R Strasse 1 5142 Eggelsberg Austria

Telephone: +43 7748 6586-0

Fax: +43 7748 6586-26

office@br-automation.com

#### Disclaimer

All information in this document is current as of its creation. The contents of this document are subject to change without notice. B&R Industrial Automation GmbH assumes unlimited liability in particular for technical or editorial errors in this document only (i) in the event of gross negligence or (ii) for culpably inflicted personal injury. Beyond that, liability is excluded to the extent permitted by law. Liability in cases in which the law stipulates mandatory unlimited liability (such as product liability) remains unaffected. Liability for indirect damage, consequential damage, business interruption, loss of profit or loss of information and data is excluded, in particular for damage that is directly or indirectly attributable to the delivery, performance and use of this material.

B&R Industrial Automation GmbH notes that the software and hardware designations and brand names of the respective companies used in this document are subject to general trademark, brand or patent protection.

Hardware and software from third-party suppliers referenced in this document is subject exclusively to the respective terms of use of these third-party providers. B&R Industrial Automation GmbH assumes no liability in this regard. Any recommendations made by B&R Industrial Automation GmbH are not contractual content, but merely non-binding information for which no liability is assumed. When using hardware and software from third-party suppliers, the relevant user documentation of these third-party suppliers must additionally be consulted and, in particular, the safety guidelines and technical specifications contained therein must be observed. The compatibility of the products from B&R Industrial Automation GmbH described in this document with hardware and software from third-party suppliers is not contractual content unless this has been separately agreed in individual cases; in this respect, warranty for such compatibility is excluded in any case, and it is the sole responsibility of the customer to verify this compatibility in advance.

#### **Version history**

B&R makes every effort to keep documents as current as possible. The most current versions are available for download on the B&R website (www.br-automation.com).

# 1 General information

# 1.1 Other applicable documents

For additional and supplementary information, see the following documents.

# Other applicable documents

| Document name | Title                    |

|---------------|--------------------------|

| MAX20         | X20 System user's manual |

# 1.2 Order data

| Order number | Short description                                                                                                                                                                                  | Figure |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

|              | Counter functions                                                                                                                                                                                  |        |

| X20DC4395    | X20 digital counter module, 2 SSI absolute encoders, 24 V, 2<br>ABR incremental encoders, 24 V, 4 AB incremental encoders,<br>24 V, 8 event counters or 4 PWM, local time measurement<br>functions | 562    |

|              | Required accessories                                                                                                                                                                               | X20 D  |

|              | Bus modules                                                                                                                                                                                        |        |

| X20BM11      | X20 bus module, 24 VDC keyed, internal I/O power supply connected through                                                                                                                          |        |

| X20BM15      | X20 bus module, with node number switch, 24 VDC keyed, internal I/O power supply connected through                                                                                                 |        |

|              | Terminal blocks                                                                                                                                                                                    |        |

| X20TB12      | X20 terminal block, 12-pin, 24 VDC keyed                                                                                                                                                           |        |

Table 1: X20DC4395 - Order data

# 1.3 Module description

This module is a multifunctional counter module. It can be connected to two SSI encoders, two ABR encoders, four AB encoders or eight event counters. Four outputs are available for pulse width modulation. The functions can also be mixed.

#### **Functions:**

- Digital inputs and outputs

- · Counters and encoders

- SSI encoder interface

- PWM Pulse width modulation

- Time measurement function

- Controlling the LED status indicators

- Monitoring the encoder power supply

# Digital inputs and outputs

This module is equipped with 8 digital channels. All channels are used as inputs, 4 channels are also configurable as outputs. The inputs can be compared with predefined states and used to generate events. In addition to being controlled from the application, the setting or clearing of outputs can also be controlled by events.

#### **Counters and encoders**

The module provides counter functions for each channel. These can be configured for different counter or encoder functions depending on the channel. These include:

- · AB encoder

- ABR encoders

- Up/Down counter

- · Event counters

#### SSI absolute encoder

The module provides 2 SSI absolute encoders that are directly supported by the hardware.

#### PWM - Pulse width modulation

The module provides 4 PWM functions that are directly supported by the hardware.

#### Time measurement function

The module has a time measurement function for each I/O channel. It can be configured separately for rising and falling edges on each channel.

#### **Controlling LED status indicators**

The module LED status indicators can be controlled by the application. This allows blink signals to be output or the states of physical inputs and outputs to be displayed.

#### Monitoring the supply voltage

The encoder power supply voltage is monitored.

# 2 Technical description

# 2.1 Technical data

| Order number                                                     | X20DC4395                                                                                                                                                                          |

|------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Short description                                                |                                                                                                                                                                                    |

| I/O module                                                       | 2 SSI absolute encoders 24 V, 2 ABR incremental encoders 24 V, 4 AB incremental encoders 24 V, 8x event counter or 4x pulse width modulation, time measurement, relative timestamp |

| General information                                              | ETT, OX CTORE COURTED OF TAX pulse Wilder Historia Grant Head a circle, relative circlestamp                                                                                       |

| Input voltage                                                    | 24 VDC -15% / +20%                                                                                                                                                                 |

| B&R ID code                                                      | 0x1CC5                                                                                                                                                                             |

| Status indicators                                                | I/O function per channel, operating state, module status                                                                                                                           |

| Diagnostics                                                      | 17 o Tanction per chainer, operating state, module status                                                                                                                          |

| Module run/error                                                 | Yes, using LED status indicator and software                                                                                                                                       |

| Outputs                                                          | Yes, using LED status indicator and software (output state)                                                                                                                        |

| Power consumption                                                | res, using LED status indicator and software (output state)                                                                                                                        |

| Bus                                                              | 0.01 W                                                                                                                                                                             |

| Internal I/O                                                     | 1.5 W                                                                                                                                                                              |

| Additional power dissipation caused by actuators (resistive) [W] | -<br>-                                                                                                                                                                             |

| Type of signal lines                                             | Shielded lines must be used for all signal lines.                                                                                                                                  |

| Certifications                                                   |                                                                                                                                                                                    |

| CE                                                               | Yes                                                                                                                                                                                |

| UKCA                                                             | Yes                                                                                                                                                                                |

| ATEX                                                             | Zone 2, II 3G Ex nA nC IIA T5 Gc                                                                                                                                                   |

| ALEX                                                             | IP20, Ta (see X20 user's manual)<br>FTZÚ 09 ATEX 0083X                                                                                                                             |

| UL                                                               | cULus E115267                                                                                                                                                                      |

|                                                                  | Industrial control equipment                                                                                                                                                       |

| HazLoc                                                           | cCSAus 244665                                                                                                                                                                      |

|                                                                  | Process control equipment                                                                                                                                                          |

|                                                                  | for hazardous locations                                                                                                                                                            |

| DNIV                                                             | Class I, Division 2, Groups ABCD, T5                                                                                                                                               |

| DNV                                                              | Temperature: <b>B</b> (0 to 55°C)<br>Humidity: <b>B</b> (up to 100%)                                                                                                               |

|                                                                  | Vibration: <b>B</b> (4 g)                                                                                                                                                          |

|                                                                  | EMC: <b>B</b> (bridge and open deck)                                                                                                                                               |

| CCS                                                              | Yes                                                                                                                                                                                |

| LR                                                               | ENV1                                                                                                                                                                               |

| KR                                                               | Yes                                                                                                                                                                                |

| ABS                                                              | Yes                                                                                                                                                                                |

| BV                                                               | EC33B                                                                                                                                                                              |

|                                                                  | Temperature: 5 - 55°C                                                                                                                                                              |

|                                                                  | Vibration: 4 g                                                                                                                                                                     |

|                                                                  | EMC: Bridge and open deck                                                                                                                                                          |

| KC                                                               | Yes                                                                                                                                                                                |

| Incremental encoders                                             |                                                                                                                                                                                    |

| Quantity                                                         | 4                                                                                                                                                                                  |

| Encoder inputs                                                   | 24 V, asymmetrical                                                                                                                                                                 |

| Counter size                                                     | 16/32-bit                                                                                                                                                                          |

| Input frequency                                                  | Max. 100 kHz                                                                                                                                                                       |

| Evaluation                                                       | 4x                                                                                                                                                                                 |

| Encoder power supply                                             | Module-internal, max. 600 mA                                                                                                                                                       |

| Overload characteristics of encoder power sup-                   | Short-circuit proof, overload-proof                                                                                                                                                |

| ply                                                              |                                                                                                                                                                                    |

| SSI absolute encoder                                             |                                                                                                                                                                                    |

| Quantity                                                         | 2                                                                                                                                                                                  |

| Encoder inputs                                                   | 24 V, asymmetrical                                                                                                                                                                 |

| Counter size                                                     | 32-bit                                                                                                                                                                             |

| Max. transfer rate                                               | 125 kbit/s                                                                                                                                                                         |

| Encoder power supply                                             | Module-internal, max. 600 mA                                                                                                                                                       |

| Coding                                                           | Gray/Binary                                                                                                                                                                        |

| CLK: Output current                                              | Max. 100 mA                                                                                                                                                                        |

| Overload characteristics of encoder power sup-                   | Short-circuit proof, overload-proof                                                                                                                                                |

| ply                                                              |                                                                                                                                                                                    |

| Event counters                                                   |                                                                                                                                                                                    |

| Quantity                                                         | 8                                                                                                                                                                                  |

|                                                                  |                                                                                                                                                                                    |

| Nominal voltage                                                  | 24 VDC                                                                                                                                                                             |

Table 2: X20DC4395 - Technical data

# **Technical description**

| Order number                                    | X20DC4395                                                                                                                |

|-------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|

| Evaluation                                      | Each edge, cyclic counter                                                                                                |

| Input frequency                                 | Max. 100 kHz                                                                                                             |

| Input current at 24 VDC                         | Approx. 1.3 mA                                                                                                           |

| Input resistance                                | 18.4 kΩ                                                                                                                  |

| Insulation voltage between channel and bus      | 500 V <sub>eff</sub>                                                                                                     |

| Counter frequency                               | 200 kHz                                                                                                                  |

| Counter size                                    | 16/32-bit                                                                                                                |

| Input filter                                    | 10/02 810                                                                                                                |

| Hardware                                        | ≤2 µs                                                                                                                    |

| Software                                        | pv                                                                                                                       |

| Switching threshold                             |                                                                                                                          |

| Low                                             | <5 VDC                                                                                                                   |

| High                                            | >15 VDC                                                                                                                  |

| Edge detection / Time measurement               | 15100                                                                                                                    |

| Possible measurements                           | Gate time, period duration, edge offset for various channels                                                             |

| Measurements per module                         | Up to 9                                                                                                                  |

| Measurements per channel                        | Up to 2                                                                                                                  |

| Signal form                                     | Square wave pulse                                                                                                        |

| Counter size                                    | 16-bit                                                                                                                   |

| Counter frequency                               | 10-DIL                                                                                                                   |

| Internal                                        | 8 MHz, 4 MHz, 2 MHz, 1 MHz, 500 kHz, 250 kHz, 125 kHz, 62.5 kHz                                                          |

| Measurement type                                | 8 MHz, 4 MHz, 2 MHz, 1 MHz, 500 KHz, 250 KHz, 125 KHz, 62.5 KHz  Continuous or triggered                                 |

| Digital outputs                                 | Continuous of triggered                                                                                                  |

| Quantity                                        | 4                                                                                                                        |

| Variant                                         | Push / Pull / Push-Pull                                                                                                  |

|                                                 | 24 VDC                                                                                                                   |

| Nominal voltage Switching voltage               | 24 VDC -15% / +20%                                                                                                       |

| 5 5                                             | ·                                                                                                                        |

| Nominal output current Total nominal current    | 0.1 A<br>0.4 A                                                                                                           |

|                                                 |                                                                                                                          |

| Output circuit                                  | Sink or source                                                                                                           |

| Output protection                               | Thermal shutdown in the event of overcurrent or short cir-<br>cuit, integrated protection for switching inductive loads  |

| Pulse width modulation 1)                       |                                                                                                                          |

| Period duration                                 | 41.6 μs to 1.36 s                                                                                                        |

| Factor for period duration                      | n/48000 s, n = 2 to 65535                                                                                                |

| Pulse duration                                  | 0 to 100%                                                                                                                |

| Resolution for pulse duration                   | 0.1%                                                                                                                     |

| Actuator power supply                           | Module-internal, max. 600 mA                                                                                             |

| Diagnostic status                               | Output monitoring                                                                                                        |

| Leakage current when the output is switched off | Max. 25 μA                                                                                                               |

| Residual voltage                                | <0.9 V at 0.1 A nominal current                                                                                          |

| Peak short-circuit current                      | <10 A                                                                                                                    |

| Switch-on in the event of overload shutdown or  | Approx. 10 ms (depends on the module temperature)                                                                        |

| short-circuit shutdown                          |                                                                                                                          |

| Switching delay                                 |                                                                                                                          |

| 0 → 1                                           | <2 µs                                                                                                                    |

| 1 → 0                                           | <2 µs                                                                                                                    |

| Switching frequency                             |                                                                                                                          |

| Resistive load                                  | Max. 24 kHz                                                                                                              |

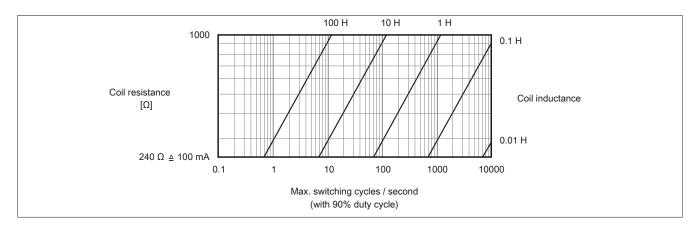

| Inductive load                                  | See section "Switching inductive loads".                                                                                 |

| Braking voltage when switching off inductive    | Switching voltage + 0.6 VDC                                                                                              |

| loads                                           | 500 V                                                                                                                    |

| Insulation voltage between channel and bus      | 500 V <sub>eff</sub>                                                                                                     |

| Electrical properties                           | Burgles I de la                                                                      |

| Electrical isolation                            | Bus isolated from encoder and output<br>Output not isolated from output and encoder<br>Encoder not isolated from encoder |

| Operating conditions                            |                                                                                                                          |

| Mounting orientation                            |                                                                                                                          |

| Horizontal                                      | Yes                                                                                                                      |

| Vertical                                        | Yes                                                                                                                      |

| Installation elevation above sea level          |                                                                                                                          |

| 0 to 2000 m                                     | No limitation                                                                                                            |

| >2000 m                                         | Reduction of ambient temperature by 0.5°C per 100 m                                                                      |

| Degree of protection per EN 60529               | IP20                                                                                                                     |

|                                                 |                                                                                                                          |

Table 2: X20DC4395 - Technical data

| Order number                    | X20DC4395                                   |

|---------------------------------|---------------------------------------------|

| Ambient conditions              |                                             |

| Temperature                     |                                             |

| Operation                       |                                             |

| Horizontal mounting orientation | -25 to 60°C                                 |

| Vertical mounting orientation   | -25 to 50°C                                 |

| Derating                        | -                                           |

| Storage                         | -40 to 85°C                                 |

| Transport                       | -40 to 85°C                                 |

| Relative humidity               |                                             |

| Operation                       | 5 to 95%, non-condensing                    |

| Storage                         | 5 to 95%, non-condensing                    |

| Transport                       | 5 to 95%, non-condensing                    |

| Mechanical properties           |                                             |

| Note                            | Order 1x terminal block X20TB12 separately. |

|                                 | Order 1x bus module X20BM11 separately.     |

| Pitch                           | 12.5 <sup>+0.2</sup> mm                     |

Table 2: X20DC4395 - Technical data

# 2.2 LED status indicators

For a description of the various operating modes, see section "Additional information - Diagnostic LEDs" in the X20 System user's manual.

| Figure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | LED | Color | Status       | Description                                      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|--------------|--------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | r   | Green | Off          | No power to module                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |       | Single flash | RESET mode                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |       | Double flash | BOOT mode (during firmware update) <sup>1)</sup> |

| ြက္ ေ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |       | Blinking     | PREOPERATIONAL mode                              |

| DC 439                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |       | On           | RUN mode                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | е   | Red   | Off          | No power to module or everything OK              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |       | On           | Error or reset status                            |

| (20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1-8 | Green |              | Status of the corresponding digital signal       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |       |              |                                                  |

| THE RESERVE OF THE PERSON NAMED IN COLUMN TWO IS NOT THE PERSON NAMED IN COLUMN TWO IS NAMED IN COLUMN TW |     |       |              |                                                  |

Depending on the configuration, a firmware update can take up to several minutes.

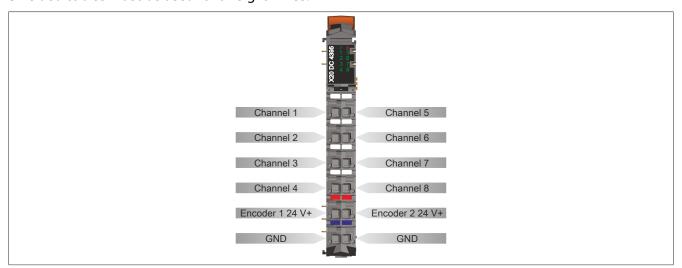

## 2.3 Pinout

Shielded cables must be used for all signal lines.

<sup>1)</sup> Dead time when switching between push and pull: Max. 1.5 μs.

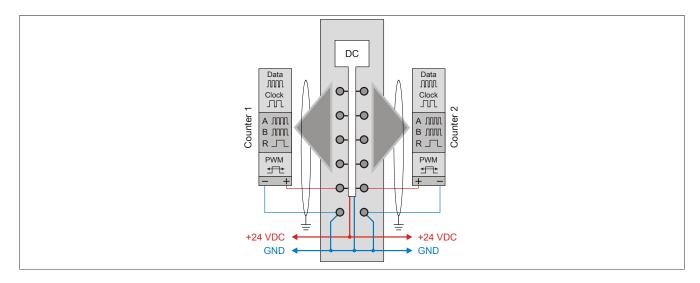

# 2.4 Connection example

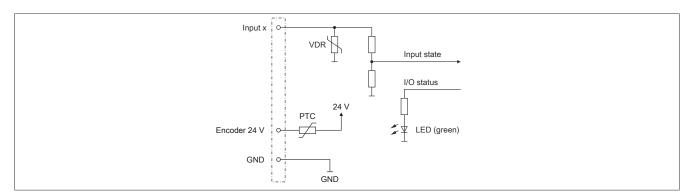

# 2.5 Input circuit diagram

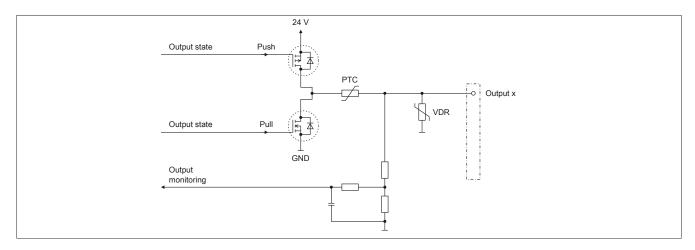

# 2.6 Output circuit diagram

# 2.7 Switching inductive loads

# **3 Function description**

#### 3.1 Hardware channel functions

The following functions can be configured on the module. However, these cannot all be operated simultaneously due to the multiple use of the hardware channels and the cyclical data length limitation:

- 8 digital channels, 4 of which are configurable as outputs

- 8 event counters with adjustable counting direction and optional referencing via digital input

- 4 PWM outputs

- 4 up/down counters, each with optional latch inputs and comparator output

- 4 AB encoders, each with optional latch inputs and comparator output

- 2 ABR encoder with adjustable reference pulse edge and reference position, optional reference enable input, latch input and comparator output

- · 2 SSI encoder, each with optional latch input and comparator output

- 2 Edge-triggered time measurement functions for each channel with selectable start edge regardless of the configuration setting

#### Information:

This module is a multifunctional module. Some bus controllers only support the default function model.

#### **Default function model:**

- 1x ABR incremental encoder (24 V)

- 1x SSI absolute encoder (24 V)

- 1x event counter (24 V)

- 2x PWM output (24 V)

10

# 3.1.1 Connecting options

# Channels 1 to 8 can be connected as follows:

| Channel | Function |               |   |                  |           |     |

|---------|----------|---------------|---|------------------|-----------|-----|

| 1       | 1        | Event counter | Α | A                | SSI data  |     |

| 2       | 1/0      | Event counter | В | В                | SSI cycle | PWM |

| 3       | I        | Event counter | Α | R                |           |     |

| 4       | 1/0      | Event counter | В | Enable reference |           | PWM |

| 5       | I        | Event counter | Α | A                | SSI data  |     |

| 6       | 1/0      | Event counter | В | В                | SSI cycle | PWM |

| 7       | I        | Event counter | Α | R                |           |     |

| 8       | 1/0      | Event counter | В | Enable reference |           | PWM |

# The functions can also be mixed. For example:

| Example 1 |               |  |

|-----------|---------------|--|

| Channel   | Function      |  |

| 1         | SSI data      |  |

| 2         | SSI cycle     |  |

| 3         | Event counter |  |

| 4         | PWM           |  |

| 5         | A             |  |

| 6         | В             |  |

| 7         | Event counter |  |

| 8         | PWM           |  |

| Example 2 |               |  |

|-----------|---------------|--|

| Channel   | Function      |  |

| 1         | SSI data      |  |

| 2         | SSI cycle     |  |

| 3         | A             |  |

| 4         | В             |  |

| 5         | Event counter |  |

| 6         | Event counter |  |

| 7         | Event counter |  |

| 8         | Event counter |  |

| Example 3 |               |  |

|-----------|---------------|--|

| Channel   | Function      |  |

| 1         | Event counter |  |

| 2         | PWM           |  |

| 3         | Event counter |  |

| 4         | PWM           |  |

| 5         | SSI data      |  |

| 6         | SSI cycle     |  |

| 7         | Α             |  |

| 8         | В             |  |

| Example 4 |                  |  |

|-----------|------------------|--|

| Channel   | Function         |  |

| 1         | Α                |  |

| 2         | В                |  |

| 3         | R                |  |

| 4         | Enable reference |  |

| 5         | Α                |  |

| 6         | В                |  |

| 7         | R                |  |

| 8         | Enable reference |  |

| Example 5 |               |  |

|-----------|---------------|--|

| Channel   | Function      |  |

| 1         | Α             |  |

| 2         | В             |  |

| 3         | Event counter |  |

| 4         | PWM           |  |

| 5         | A             |  |

| 6         | В             |  |

| 7         | Event counter |  |

| 8         | Event counter |  |

| Example 6 |               |  |  |

|-----------|---------------|--|--|

| Channel   | Function      |  |  |

| 1         | Event counter |  |  |

| 2         | Event counter |  |  |

| 3         | Event counter |  |  |

| 4         | PWM           |  |  |

| 5         | SSI data      |  |  |

| 6         | SSI cycle     |  |  |

| 7         | A             |  |  |

| 8         | В             |  |  |

# 3.1.2 Description of channel assignments

The functions listed here are directly assigned to the respective hardware channels and cannot be changed.

| Channel | Signal connections                                                         |

|---------|----------------------------------------------------------------------------|

| 1       | Digital input 1                                                            |

|         | Event counter 1                                                            |

|         | AB encoder 1 - signal line A                                               |

|         | Up/down counter 1 - frequency                                              |

|         | SSI encoder 1, data line                                                   |

|         | ABR encoder 1 - signal line A                                              |

| 2       | Digital input 2                                                            |

|         | Digital output 2                                                           |

|         | Event counter 2                                                            |

|         | PWM output 2                                                               |

|         | AB encoder 1 - signal line B                                               |

|         | Up/down counter 1 - direction                                              |

|         | SSI encoder 1, clock line                                                  |

|         | ABR encoder 1 - signal line B                                              |

| 3       | Digital input 3                                                            |

|         | Event counter 3                                                            |

|         | AB encoder 2 - signal line A                                               |

|         | Up/down counter 2 - frequency                                              |

|         | ABR encoder 1 - signal line R                                              |

| 4       | Digital input 4                                                            |

|         | Digital output 4                                                           |

|         | Event counter 4                                                            |

|         | PWM output 4                                                               |

|         | AB encoder 2 - signal line B                                               |

|         | Up/down counter 2 - direction                                              |

|         | ABR encoder 1 - reference enable input                                     |

| 5       | Digital input 5                                                            |

|         | Event counter 5                                                            |

|         | AB encoder 3 - signal line A                                               |

|         | Up/down counter 3 - frequency                                              |

|         | SSI encoder 2, data line                                                   |

|         | ABR encoder 2 - signal line A                                              |

| 6       | Digital input 6                                                            |

|         | Digital output 6                                                           |

|         | Event counter 6                                                            |

|         | PWM output 6                                                               |

|         | AB encoder 3 - signal line B                                               |

|         | Up/down counter 3 - direction                                              |

|         | SSI encoder 2, clock line                                                  |

|         | ABR encoder 2 - signal line B                                              |

| 7       | Digital input 7                                                            |

| '       | Event counter 7                                                            |

|         | AB encoder 4 - signal line A                                               |

|         | Up/down counter 4 - frequency                                              |

|         | ABR encoder 2 - signal line R                                              |

| 8       | Digital input 8                                                            |

|         | Digital injut 8      Digital output 8                                      |

|         | Event counter 8                                                            |

|         |                                                                            |

|         |                                                                            |

|         | AB encoder 4 - signal line B      Un/down counter 4 - direction            |

|         | Up/down counter 4 - direction  ARD an addar 3, reference and be insulated. |

|         | ABR encoder 2 - reference enable input                                     |

Options available in addition to these basic functions, such as comparator outputs or latch inputs, can be configured freely to unused input/output channels.

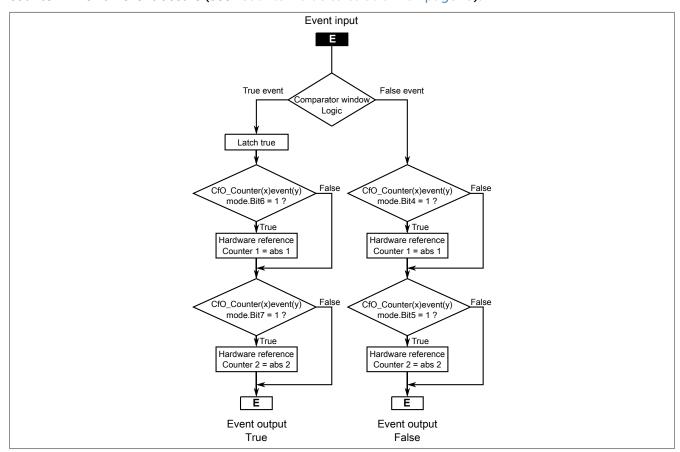

#### 3.2 Event functions

The module provides configurable event functions. An event function can be connected to physical I/O and the values derived from them (e.g. counters) or be purely used for internal processing.

Each event function has event inputs and outputs. Event functions can also only have event inputs or outputs. Each event output has a unique event ID. It is possible to configure when an event is generated on an event output. The effect of the arrival of an event is specified by the event function.

Event functions can also be linked to one another. The link takes place using the event input. Every event input has a 16-bit register to which the event number of the linked event output is written.

#### Information:

The module functions that can be configured in the Automation Studio I/O configuration are primarily based on these event functions and their links. Changes in the Automation Studio I/O configuration have multiple effects on event functions and their links.

The module functions cover the following areas:

- Edge events

- · Direct input functions

- Direct output functions

- · Counter event functions

- SSI event functions

#### 3.2.1 List of event IDs

Various hardware and software functions send event IDs or require event IDs in order to start. The following table shows all of the IDs available to configure the module.

| Event ID                | Description                           |                         |  |  |

|-------------------------|---------------------------------------|-------------------------|--|--|

| Direct event inputs     |                                       |                         |  |  |

| 512                     | Comparator condition 1                | FALSE                   |  |  |

| 513                     |                                       | TRUE                    |  |  |

| 544                     | Comparator condition 2                | FALSE                   |  |  |

| 545                     |                                       | TRUE                    |  |  |

| 576                     | Comparator condition 3                | FALSE                   |  |  |

| 577                     |                                       | TRUE                    |  |  |

| 608                     | Comparator condition 4                | FALSE                   |  |  |

| 609                     |                                       | TRUE                    |  |  |

| Counter event functions |                                       |                         |  |  |

| 2,112                   | Counter function 1                    | Event function 1; FALSE |  |  |

| 2,113                   |                                       | Event function 1; TRUE  |  |  |

| 2,144                   |                                       | Event function 2; FALSE |  |  |

| 2,145                   |                                       | Event function 2; TRUE  |  |  |

| 2,368                   | Counter function 2                    | Event function 1; FALSE |  |  |

| 2,369                   |                                       | Event function 1; TRUE  |  |  |

| 2,400                   |                                       | Event function 2; FALSE |  |  |

| 2,401                   |                                       | Event function 2; TRUE  |  |  |

| 2,624                   | Counter function 3                    | Event function 1; FALSE |  |  |

| 2,625                   |                                       | Event function 1; TRUE  |  |  |

| 2,656                   |                                       | Event function 2; FALSE |  |  |

| 2,657                   |                                       | Event function 2; TRUE  |  |  |

| 2,880                   | Counter function 4                    | Event function 1; FALSE |  |  |

| 2,881                   |                                       | Event function 1; TRUE  |  |  |

| 2,912                   |                                       | Event function 2; FALSE |  |  |

| 2,913                   |                                       | Event function 2; TRUE  |  |  |

| Edge events             |                                       |                         |  |  |

| 4,096                   | Falling edge on I/O channel           | Channel 1               |  |  |

|                         |                                       |                         |  |  |

| 4,103                   |                                       | Channel 8               |  |  |

| 4,112                   | Rising edge on I/O channel            | Channel 1               |  |  |

|                         |                                       |                         |  |  |

| 4,119                   |                                       | Channel 8               |  |  |

| 4,128                   | Rising or falling edge on I/O channel | Channel 1               |  |  |

|                         |                                       |                         |  |  |

| 4,135                   |                                       | Channel 8               |  |  |

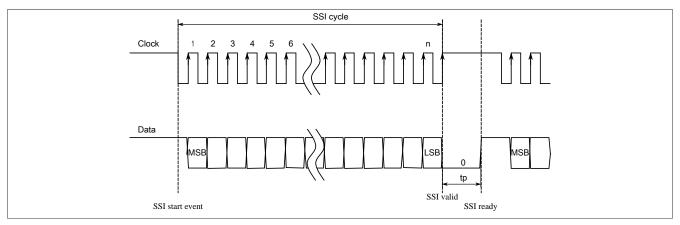

| SSI counter events      |                                       |                         |  |  |

| 7,168                   | SSI 1                                 | SSI valid               |  |  |

| 7,169                   |                                       | SSI ready               |  |  |

#### **Function description**

| Event ID              | Description                                                 |           |  |

|-----------------------|-------------------------------------------------------------|-----------|--|

| 7,424                 | SSI 2                                                       | SSI valid |  |

| 7,425                 |                                                             | SSI ready |  |

| SSI comparator events |                                                             |           |  |

| 7,232                 | SSI 1 comparator condition                                  | FALSE     |  |

| 7,233                 |                                                             | TRUE      |  |

| 7,488                 | SSI 2 comparator condition                                  | FALSE     |  |

| 7,489                 |                                                             | TRUE      |  |

| Timerevents           |                                                             |           |  |

| 208                   | Timer1                                                      | 50 μs     |  |

| 209                   | Timer2                                                      | 100 μs    |  |

| 210                   | Timer3                                                      | 200 μs    |  |

| 211                   | Timer4                                                      | 400 μs    |  |

| 212                   | Timer5                                                      | 800 μs    |  |

| 213                   | Timer6                                                      | 1600 μs   |  |

| 214                   | Timer7                                                      | 3200 μs   |  |

| 215                   | Timer8 3200 μs (time offset to timer 7)                     |           |  |

| Network functions     |                                                             |           |  |

| 224                   | SOAISOP (Synchronous Out Asynchronous In Start Of Protocol) |           |  |

| 225                   | AOSISOP (Asynchronous Out Synchronous In Start Of Protocol) |           |  |

| 226                   | SOAIEOP (Synchronous Out Asynchronous In End Of Protocol)   |           |  |

| 227                   | AOSIEOP (Asynchronous Out Synchronous In End Of Protocol)   |           |  |

| Idle event            |                                                             |           |  |