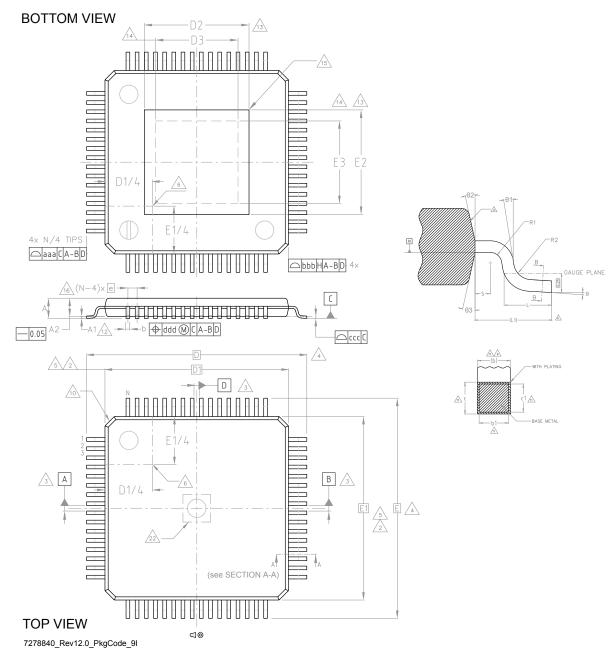

## Automotive Multicell battery monitoring and balancing IC

## TQFP 10x10 64L exposed pad down

#### **Features**

- AEC-Q100 qualified

- Measures 4 to 14 cells in series, with 0 µs desynchronization delay between samples. Supports also busbar connection without altering cell results

- Coulomb counter supporting pack overcurrent detection in both ignition on and off states. Fully synchronized current and voltage samples

- 16-bit voltage ADC with maximum error of ±2 mV in the [0.5 4.3] V range, after soldering, in [-40; +105] °C Tj range

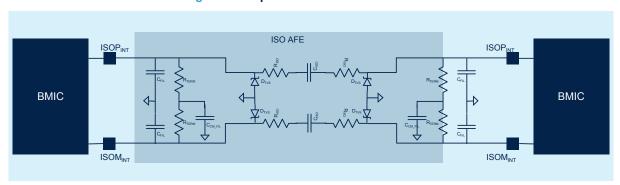

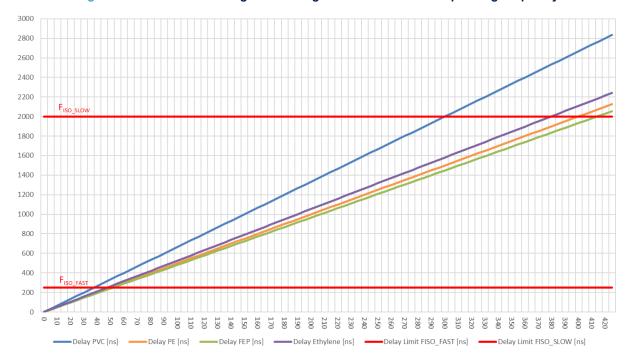

- 2.66 Mbps isolated serial communication with regenerative buffer, supporting

dual access ring. Less than 4 us latency between start of conversion of the 1st

and the 31st device in a chain. Less than 4 ms to convert and read 96 cells in a

system using 8 L9963E and L9963T transceiver. Less than 8 ms to convert and

read 210 cells in a system using 15 L9963E and L9963T transceiver. Less than

16 ms to convert and read 434 cells in a system using 31 L9963E and L9963T

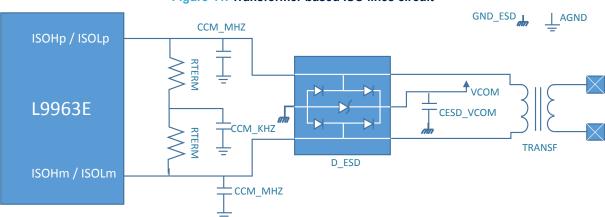

transceiver. Supports both XFMR and CAP based isolation

- 200 mA passive internal balancing current for each cell in both normal and silent-balancing mode. Possibility of executing cyclic wake up measurements. Manual/Timed balancing, on multiple channels simultaneously; Internal/External balancing

- Fully redundant cell measurement path, with ADC Swap, for enhanced safety and limp home functionality

- Intelligent diagnostic routine providing automatic failure validation. Redundant fault notification through both SPI Global Status Word (GSW) and dedicated FAULT line

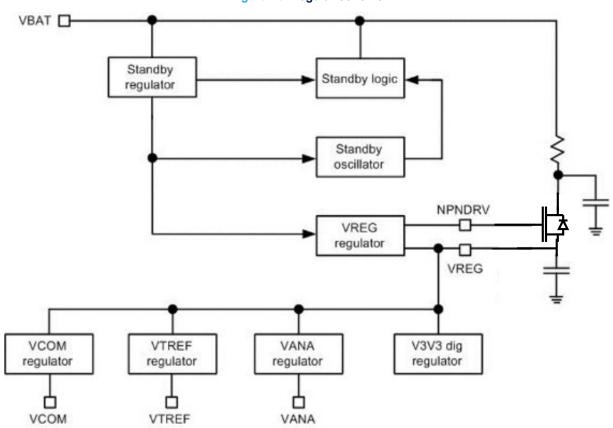

- Two 5 V regulators supporting external load connection with 25 mA (VCOM) and 50 mA (VTREF) current capability

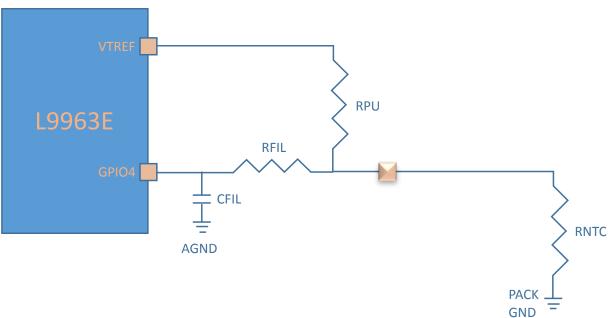

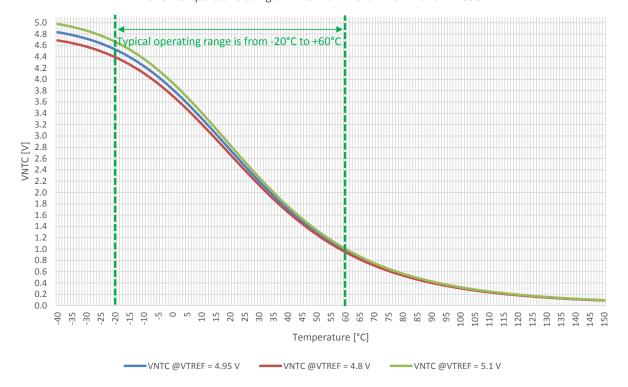

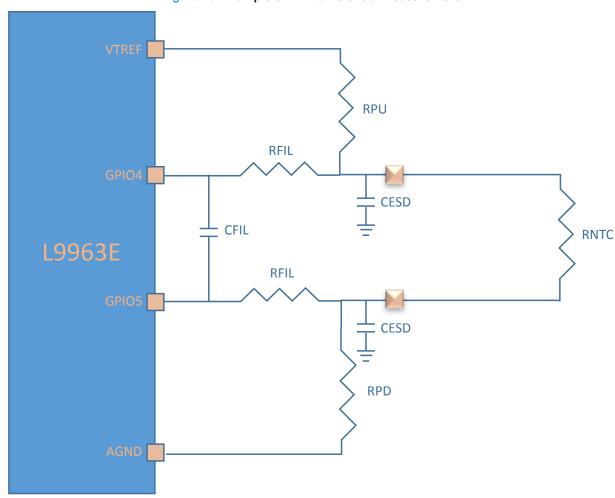

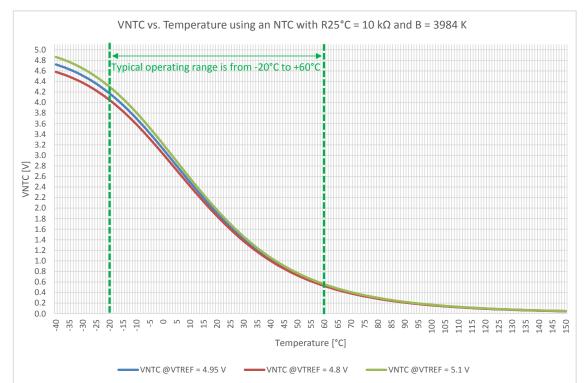

- 9 GPIOs, with up to 7 analog inputs for NTC sensing

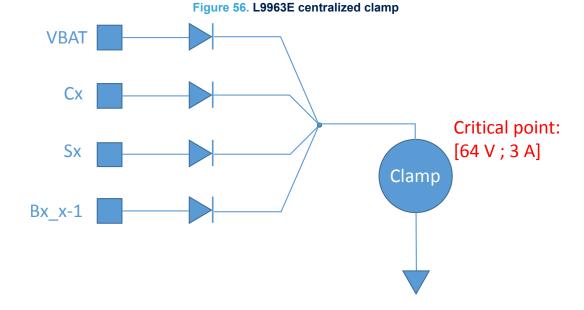

- Robust hot-plug performance. No Zeners needed in parallel to each cell

- Full ISO26262 compliant, ASIL-D systems ready

### Product status link

L9963E

| Product summary |                  |                  |  |  |  |  |

|-----------------|------------------|------------------|--|--|--|--|

| Order code      | der code Package |                  |  |  |  |  |

| L9963E          |                  | Tray             |  |  |  |  |

| L9963E-TR       | TQFP64EP         | Tape and<br>Reel |  |  |  |  |

### **Application**

- · Automotive: 48 V and high-voltage battery packs

- · Backup energy storage systems and UPS

- · E-bikes, e-scooters

- · Portable and semi-portable equipment

### **Description**

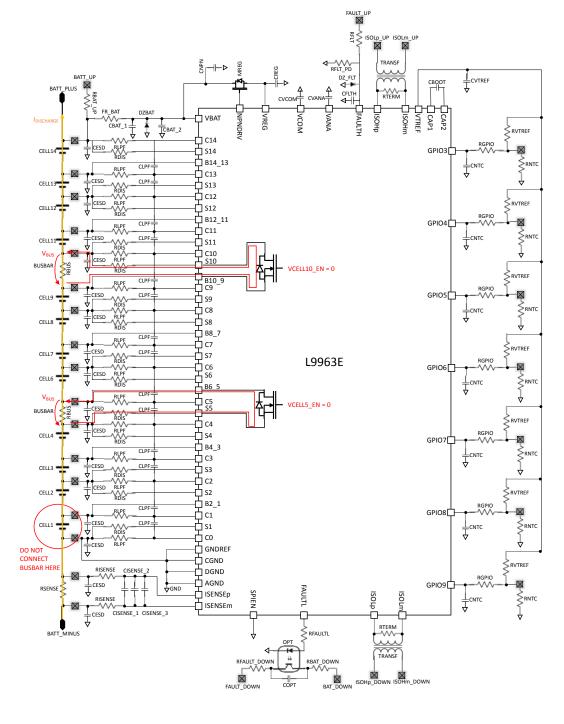

The L9963E is a Li-ion battery monitoring and protecting chip for high-reliability automotive applications and energy storage systems. Up to 14 stacked battery cells can be monitored to meet the requirements of 48 V and higher voltage systems.

Each cell voltage is measured with high accuracy, as well as the current for the on-chip coulomb counting. The device can monitor up to 7 NTCs. The information is transmitted through SPI communication or isolated interface.

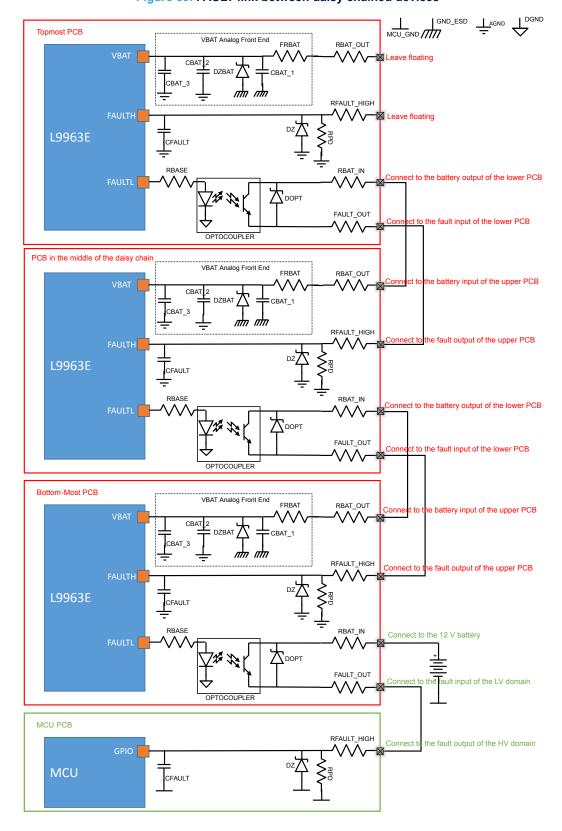

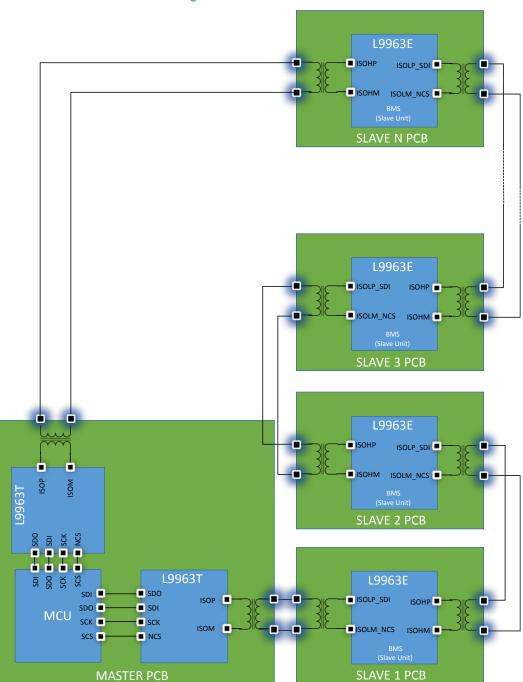

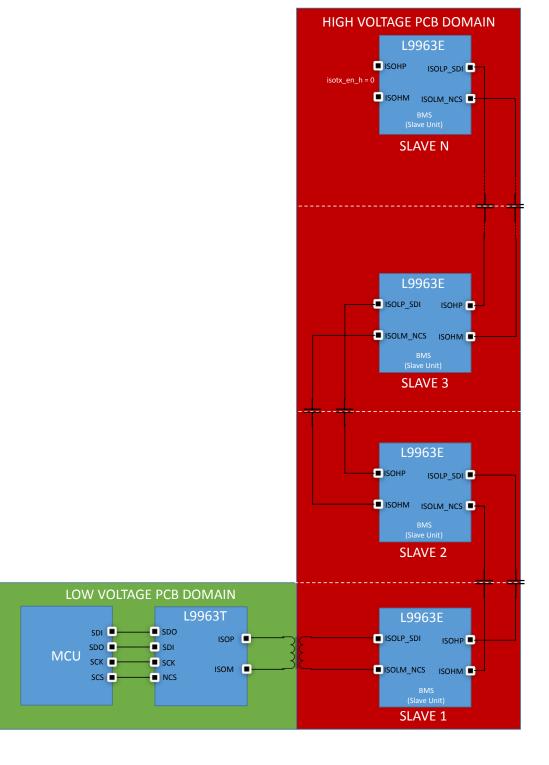

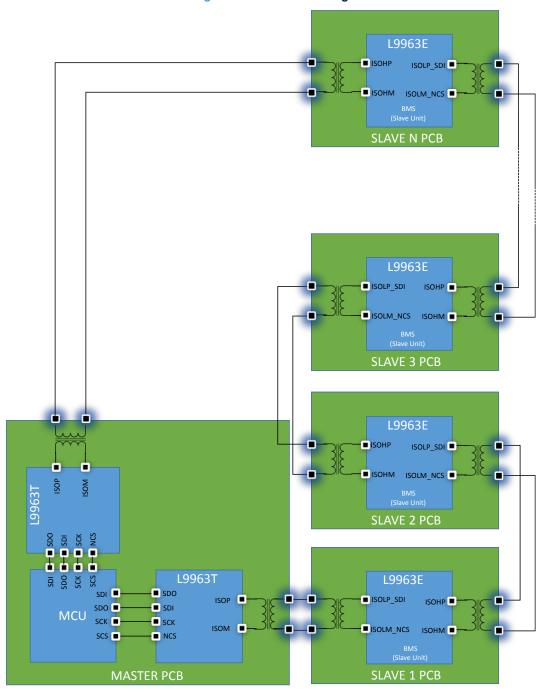

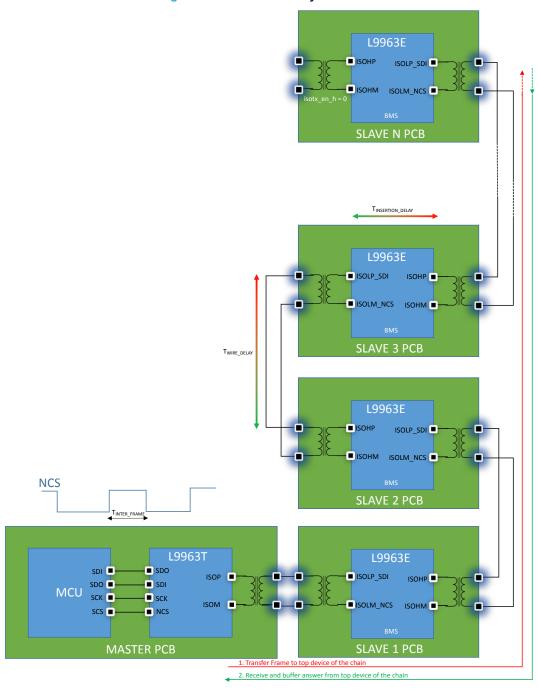

Multiple L9963E can be connected in a daisy chain and communicate with one host processor via the transformer isolated interfaces, featuring high-speed, low EMI, long distance, and reliable data transmission.

Passive balancing with programmable channel selection is offered in both normal and low power mode (silent balance). The balancing can be terminated automatically based on internal timer interrupt. Nine GPIOs are integrated for external monitoring and controlling. The L9963E features a comprehensive set of fault detection and notification functions to meet the safety standard requirements.

DS13636 - Rev 2 page 2/184

### 1 Device introduction

The L9963E is intended for operation in both hybrid (HE) and full electric (FE) vehicles using lithium battery packs. The IC embeds all the features needed to perform battery management. A single device can monitor from 4 up to 14 cells. Several devices can be stacked in a vertical arrangement in order to monitor up to 31 battery packs for a total of 434 series cells.

The device can be supplied with the same battery it monitors, and generates stable internal references by means of a voltage regulator and a bootstrap. Both unit need to be surrounded by external components to be functional. It also features two internal bandgaps that are constantly monitored by internal circuitry to guarantee measurement precision. The microcontroller can also monitor the precision of the bandgap by reading the conversion of an internally generated voltage reference (VTREF).

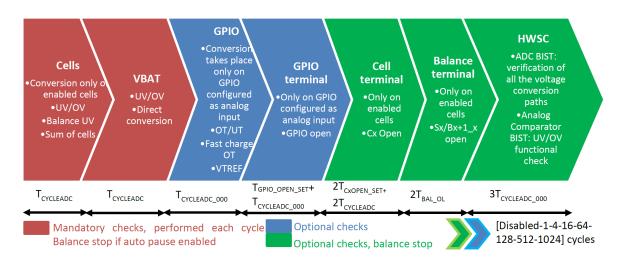

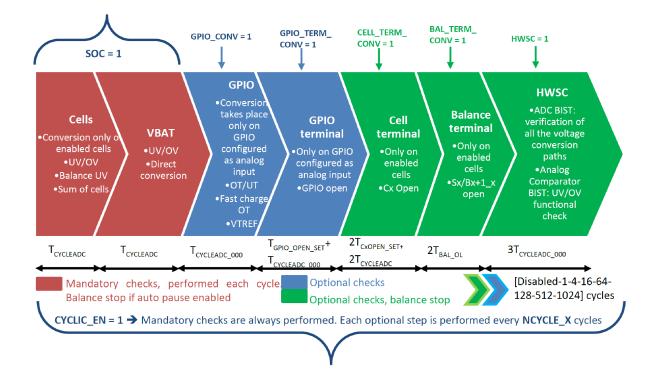

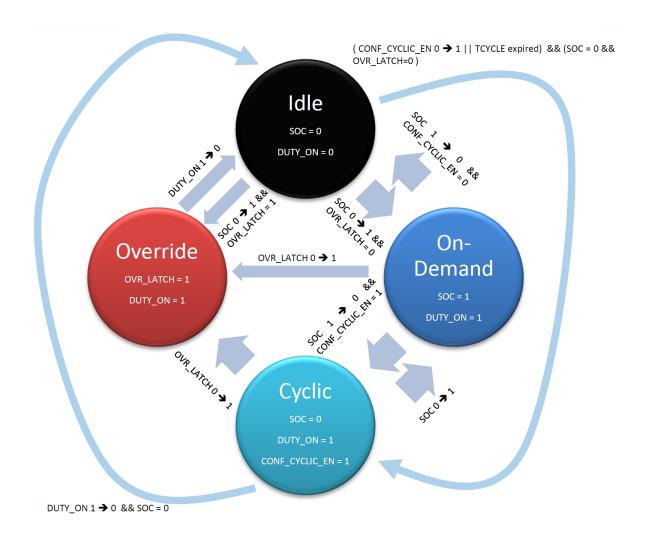

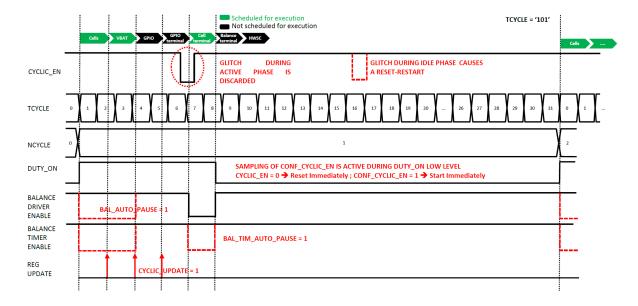

L9963E main activity consists in monitoring cells and battery pack status through stack voltage measurement, cell voltage measurement, temperature measurement and coulomb counting. Measurement and diagnostic tasks can be executed either on demand or periodically, with a programmable cycle interval. Measurement data is available for an external microcontroller to perform charge balancing and to compute the State Of Health (SOH) and State Of Charge (SOC). In a typical use, the IC works in normal mode performing measurement conversions, diagnostics and communication; the device can also be put into a cyclic wake up state, in order to reduce the current consumption from the battery: while in this state, the main functions are activated periodically.

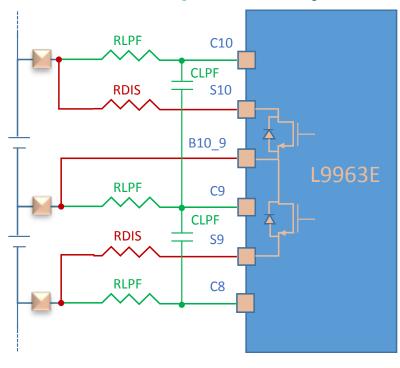

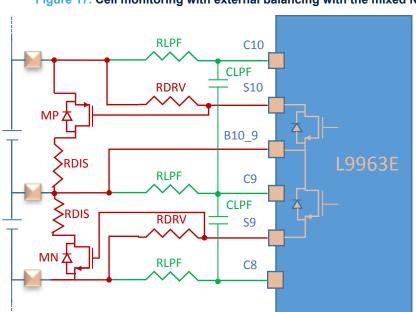

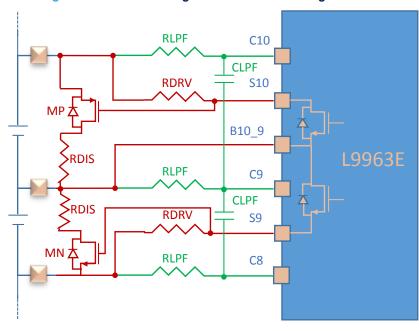

Passive cell balancing can be performed either via internal discharge path or via external MOSFETs. The controller can either manually control the balancing drivers or start a balancing task with a fixed duration. In the second case, the balancing may be programmed to continue also when the IC enters a low power mode called Silent Balancing, in order to avoiding unnecessary current absorption from the battery pack.

Thanks to the GPIOs, the device also offers the possibility to operate a distributed cell temperature sensing via external NTCs resistances. In general, the GPIOs can be used to perform both absolute and differential voltage conversions. They can also be configured as digital inputs/outputs. The IC supports up to 7 NTCs.

The external microcontroller can communicate with L9963E via SPI protocol, depending on the status of one pin at the startup (SPIEN pin). The physical layer can be either a classical 4-wire based SPI or a 2-wire, transformer/capacitive based, isolated interface through a dedicated isolated transceiver device. L9963E, in fact, can be used as a transceiver, acting as a bridge between the two physical layers. In case of multiple L9963E vertically arrayed, each L9963E communicates with the others by means of a vertical isolated interface. The microcontroller can either address a single device of the chain or send broadcast commands.

L9963E has been engineered to perform automatic validation of any failure involving the cells or the whole battery pack. The device is able to detect the loss of the connection to a cell or GPIO terminal. Moreover it features an HardWare Self Check (HWSC) that verifies the correct functionality of the internal analog comparators and the ADCs. All these checks are automatically performed in case a failure involving both cells or the battery pack is detected, in order to provide always a reliable information to the external microcontroller. The current sensing interface used for coulomb counting is also capable of detecting failures such as open wires and overcurrent in sleep mode. Conversions for coulomb counting are validated by built in self-test of the precision and detecting any counter overflow. The cell balancing terminals can detect any short/open fault and the internal powerMOS are protected against overcurrent.

The stack voltage is monitored for OV/UV by three parallel and independent system. They have been engineered to protect the IC against AMR violation, to detect any overvoltage event as per LV 148 and to provide the possibility to trim the OV/UV levels according to the application and the total number of cells. Moreover, all internal voltage regulators are equipped with UV/OV detection circuitry, that is also self-validated upon failure detection via HWSC. Ground loss detection has also been implemented. In case of overtemperature, thermal shutdown protects the IC. GPIOs are capable of detecting 'stuck @' faults when used as digital outputs. Communication integrity is guaranteed by CRC check, while trimming and calibration data is continuously checked against corruption. Protocol errors such as incorrect address, inconsistent frame and communication interruption will be detected.

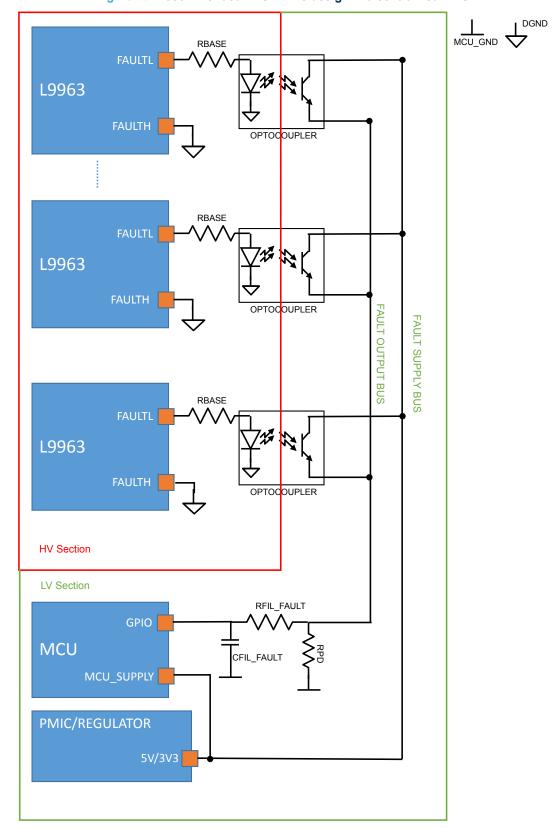

Critical failure modes will trigger the assertion of a dedicated FAULT line (implemented via two GPIOs), propagating through the L9963E chain via external optocouplers and reaching the microcontroller. L9963E can quarantee the FAULT line integrity via a heartbeat routine.

DS13636 - Rev 2 page 3/184

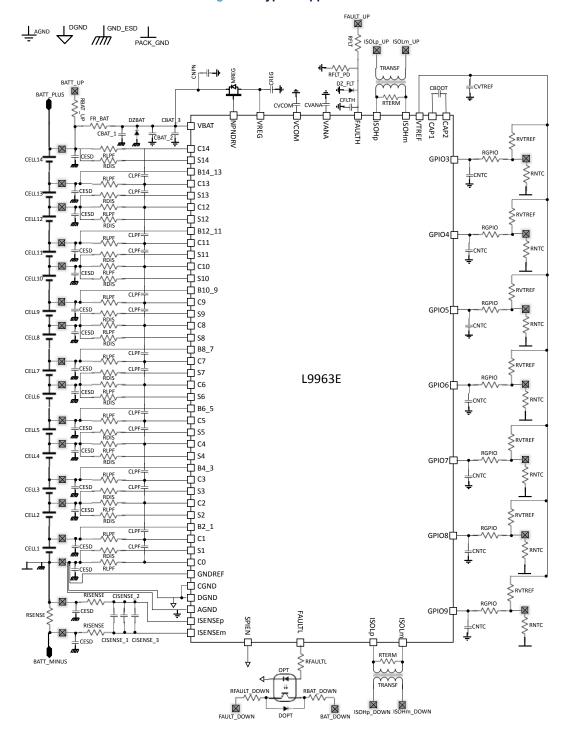

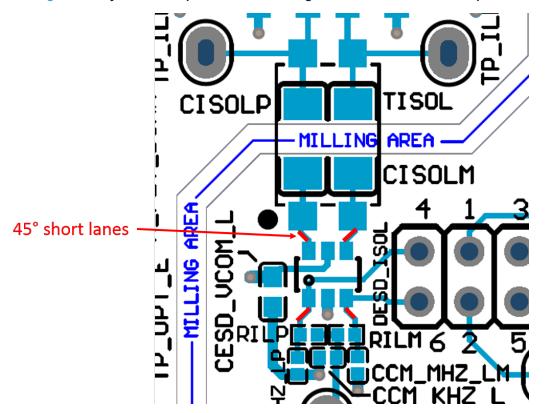

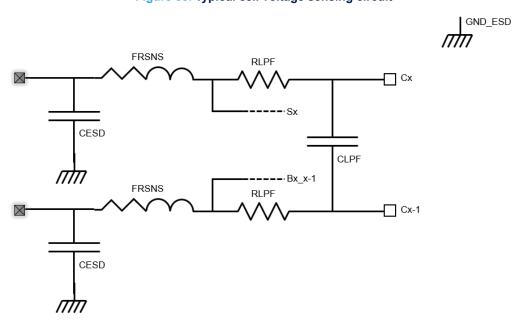

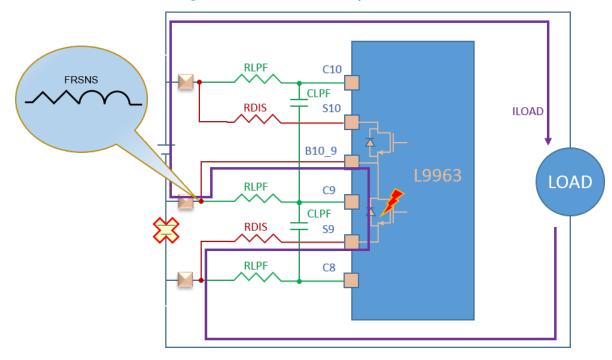

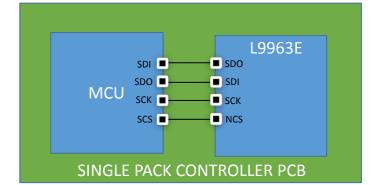

Figure 1. Typical application

DS13636 - Rev 2 page 4/184

# Block diagram and pin description

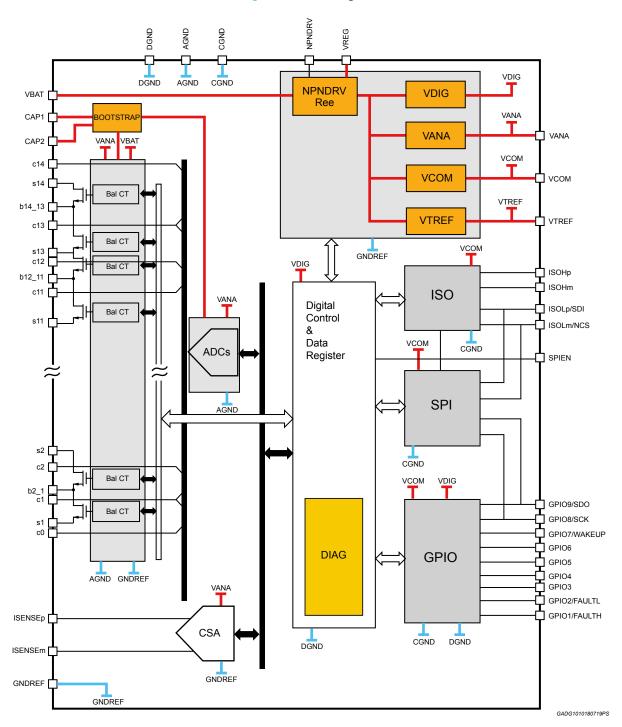

### 2.1 Block diagram

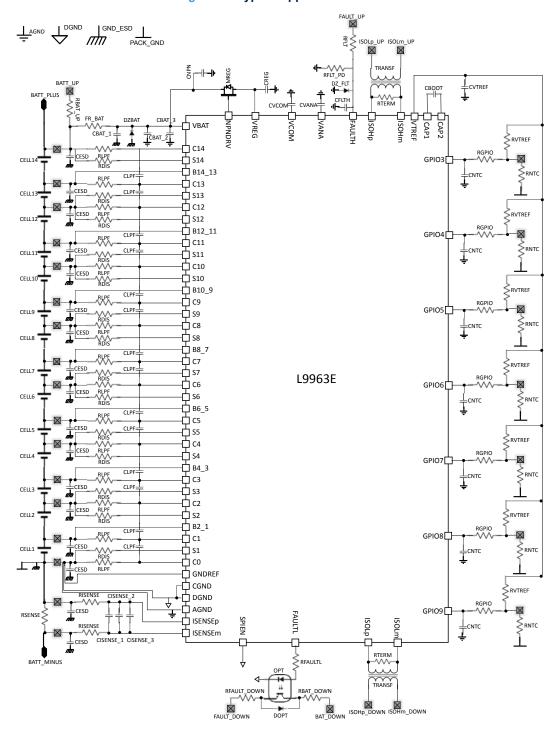

Figure 2. Block diagram

DS13636 - Rev 2 page 5/184

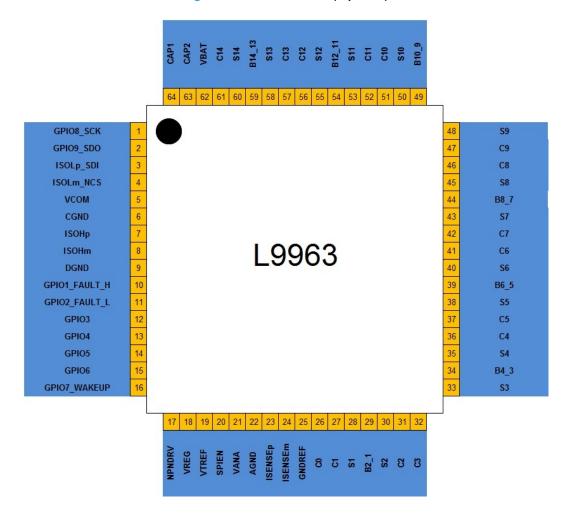

## 2.2 Pin description

Figure 3. Pin connections (top view)

**Table 1. Pin function**

| Pin# | Pin name                                                                                                                                                                                                                                                              | Description                                                                                                                                                                                                                                                                                          | I/O type <sup>(1)</sup> |  |  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|--|--|

| 1    | GPIO8_SCK                                                                                                                                                                                                                                                             | General-purpose I/O / Serial clock input (SPI). Its configuration is locked to Digital Input in case SPIEN = 1. Refer to Section 4.9 General purpose I/O: GPIOs. Generally used to sense NTCs when not configured as SPI. Refer to Section 6.9 NTC analog front end.                                 | DO/DI/AI                |  |  |

| 2    | General-purpose I/O / Serial data output (SPI). Its configuration is locked to Digital Output in case SPIEN = 1. Refer to Section 4.9 General purpose I/O: GPIOs. Generally used to sense NTCs when not configured as SPI. Refer to Section 6.9 NTC analog front end. |                                                                                                                                                                                                                                                                                                      |                         |  |  |

| 3    | ISOLp_SDI                                                                                                                                                                                                                                                             | Non-inverting, low-side isolated serial communication port (isolated SPI) / Serial data input (SPI). Its configuration is locked to Digital Input in case SPIEN = 1. Refer to Section 4.2 Serial communication interface. When used as isolated SPI, refer to Section 6.8 ISO lines circuit.         | DI/AIO                  |  |  |

| 4    | ISOLm_NCS                                                                                                                                                                                                                                                             | Inverting, low-side isolated serial communication port (isolated SPI) / Active low, Chip-Select input (SPI). Its configuration is locked to Digital Input in case SPIEN = 1. Refer to Section 4.2 Serial communication interface. When used as isolated SPI, refer to Section 6.8 ISO lines circuit. | DI/AIO                  |  |  |

DS13636 - Rev 2 page 6/184

| Pin# | Pin name      | Description                                                                                                                                                                                                                                                                | I/O type <sup>(1)</sup> |  |

|------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|--|

| 5    | VCOM          | Regulated power supply used for communication interfaces. Connect a tank capacitor as indicated in Table 73. Can be used to supply external loads with a maximum I <sub>VCOM_ext</sub> current budget.                                                                     | Р                       |  |

| 6    | CGND          | Communication ground. Connect to DGND on top.                                                                                                                                                                                                                              | G                       |  |

| 7    | ISOHp         | Non-inverting, high-side isolated serial communication port. Refer to Section 4.2.3 Isolated Serial Peripheral Interface. Refer to Section 6.8 ISO lines circuit.                                                                                                          | AIO                     |  |

| 8    | ISOHm         | Inverting, high-side isolated serial communication port. Refer to Section 4.2.3 Isolated Serial Peripheral Interface. Refer to Section 6.8 ISO lines circuit.                                                                                                              | AIO                     |  |

| 9    | DGND          | Digital ground. Connect to AGND on top.                                                                                                                                                                                                                                    | G                       |  |

| 10   | GPIO1_ FAULTH | Digital input used for FAULTH receiver. Refer to Section 4.3 FAULT line.                                                                                                                                                                                                   | DI                      |  |

| 11   | GPIO2_FAULTL  | Digital output used for FAULTL transmitter. Refer to Section 4.3 FAULT line.                                                                                                                                                                                               | DO                      |  |

| 12   | GPIO3         |                                                                                                                                                                                                                                                                            | AI/DI/DO                |  |

| 13   | GPIO4         | General-purpose I/O. Refer to Section 4.9 General purpose I/O: GPIOs. Generally                                                                                                                                                                                            | AI/DI/DO                |  |

| 14   | GPIO5         | used to sense NTCs. Refer to Section 6.9 NTC analog front end.                                                                                                                                                                                                             | AI/DI/DO                |  |

| 15   | GPIO6         |                                                                                                                                                                                                                                                                            | AI/DI/DO                |  |

| 16   | GPIO7_WAKEUP  | General-purpose I/O. Refer to Section 4.9 General purpose I/O: GPIOs. Generally used to sense NTCs. Refer to Section 6.9 NTC analog front end. Can be configured to act as wake up input. Refer to Section 4.9.4 GPIO7: wake up feature.                                   | AI/DI/DO                |  |

| 17   | NPNDRV        | Internal voltage regulator controller output. Connect to the base of the external NPN transistor.                                                                                                                                                                          | AO                      |  |

| 18   | VREG          | Regulated analog power supply for core circuitry. Connect a tank capacitor as indicated in Table 73. It is disabled in low power modes (Silent Balancing, Sleep and during the OFF phase of Cyclic Wakeup). VCOM, VANA and VTREF regulators are fed by pre-regulated VREG. | Р                       |  |

| 19   | VTREF         | Buffered, precise analog reference voltage for driving multiple NTCs. Connect a tank capacitor as indicated in Table 73. It has a maximum IVTREF_ext current budget.                                                                                                       | Р                       |  |

| 20   | SPIEN         | At first power up, after VCOM is out of undervoltage, this pin is sampled to determine port L configuration. Connect to VCOM to configure SPI mode. Connect to AGND to select isolated SPI communication.                                                                  | DI                      |  |

| 04   | \/ANIA        | If left floating, this pin has a 100KΩ internal Pull down, forcing isolated SPI mode.                                                                                                                                                                                      |                         |  |

| 21   | VANA          | Precise ADC analog supply. Connect a tank capacitor as indicated in Table 73.                                                                                                                                                                                              | Р                       |  |

| 22   | AGND          | Analog/ESD ground. Ground supply of chip.                                                                                                                                                                                                                                  | G                       |  |

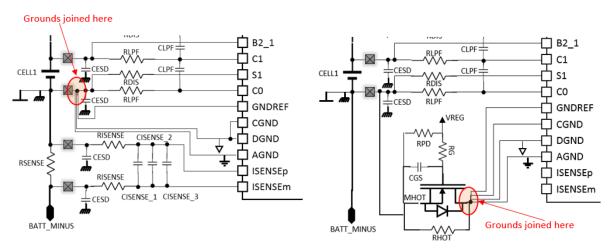

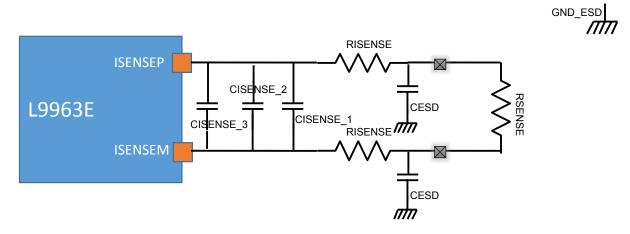

| 23   | ISENSEp       | Non-inverting input of current measurement. Refer to Table 73.                                                                                                                                                                                                             | Al                      |  |

| 24   | ISENSEM       | Inverting input of current measurement. Refer to Table 73.                                                                                                                                                                                                                 | Al                      |  |

| 25   | GNDREF        | Analog/reference GND. Connect to AGND on top                                                                                                                                                                                                                               | G                       |  |

| 26   | C0            | Connect to the negative terminal of 1st cell.                                                                                                                                                                                                                              | Al                      |  |

| 27   | C1            | Cell voltage input. Connect to the positive terminal of 1st cell.                                                                                                                                                                                                          | Al                      |  |

| 28   | S1            | Cell balancing FET control output for 1st cell.                                                                                                                                                                                                                            | AO                      |  |

| 29   | B2_1          | Common terminal for cell balancing S1 and S2.                                                                                                                                                                                                                              | AO                      |  |

| 30   | S2            | Cell balancing FET control output for 2nd cell.                                                                                                                                                                                                                            |                         |  |

| 31   | C2            | Cell voltage input. Connect to the positive terminal of 2nd cell.                                                                                                                                                                                                          |                         |  |

| 32   | C3            | Cell voltage input. Connect to the positive terminal of 3rd cell.                                                                                                                                                                                                          |                         |  |

| 33   | S3            | Cell balancing FET control output for 3rd cell.                                                                                                                                                                                                                            | AO                      |  |

| 34   | B4_3          | Common terminal for cell balancing S3 and S4.                                                                                                                                                                                                                              | AO                      |  |

| 35   | S4            | Cell balancing FET control output for 4th cell.                                                                                                                                                                                                                            | AO                      |  |

DS13636 - Rev 2 page 7/184

| Pin# | Pin name | Description                                                                                                 | I/O type <sup>(1)</sup> |  |  |  |  |

|------|----------|-------------------------------------------------------------------------------------------------------------|-------------------------|--|--|--|--|

| 36   | C4       | Cell voltage input. Connect to the positive terminal of 4th cell.                                           | Al                      |  |  |  |  |

| 37   | C5       | Cell voltage input. Connect to the positive terminal of 5th cell.                                           |                         |  |  |  |  |

| 38   | S5       |                                                                                                             |                         |  |  |  |  |

| 39   | B6_5     |                                                                                                             |                         |  |  |  |  |

| 40   | S6       | Common terminal for cell balancing S5 and S6.  Cell balancing FET control output for 6th cell.              |                         |  |  |  |  |

| 41   | C6       | Cell voltage input. Connect to the positive terminal of 6th cell.                                           | Al                      |  |  |  |  |

| 42   | C7       | Cell voltage input. Connect to the positive terminal of 7th cell.                                           | Al                      |  |  |  |  |

| 43   | S7       | Cell balancing FET control output for 7th cell.                                                             | AO                      |  |  |  |  |

| 44   | B8_7     | Common terminal for cell balancing S7 and S8.                                                               | AO                      |  |  |  |  |

| 45   | S8       | Cell balancing FET control output for 8th cell.                                                             | AO                      |  |  |  |  |

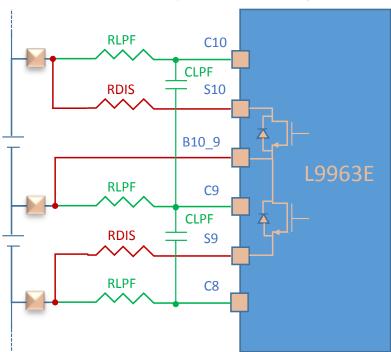

| 46   | C8       | Cell voltage input. Connect to the positive terminal of 8th cell.                                           | Al                      |  |  |  |  |

| 47   | C9       | Cell voltage input. Connect to the positive terminal of 9th cell.                                           | Al                      |  |  |  |  |

| 48   | S9       | Cell balancing FET control output for 9th cell.                                                             | AO                      |  |  |  |  |

| 49   | B10_9    | Common terminal for cell balancing S9 and S10.                                                              | AO                      |  |  |  |  |

| 50   | S10      | Cell balancing FET control output for 10th cell.                                                            | AO                      |  |  |  |  |

| 51   | C10      | Cell voltage input. Connect to the positive terminal of 10th cell.                                          | Al                      |  |  |  |  |

| 52   | C11      | Cell voltage input. Connect to the positive terminal of 11th cell.                                          | Al                      |  |  |  |  |

| 53   | S11      | Cell balancing FET control output for 11th cell.                                                            | AO                      |  |  |  |  |

| 54   | B12_11   | Common terminal for cell balancing S11 and S12.                                                             | AO                      |  |  |  |  |

| 55   | S12      | Cell balancing FET control output for 12th cell.                                                            | AO                      |  |  |  |  |

| 56   | C12      | Cell voltage input. Connect to the positive terminal of 12th cell.                                          | Al                      |  |  |  |  |

| 57   | C13      | Cell voltage input. Connect to the positive terminal of 13th cell.                                          | Al                      |  |  |  |  |

| 58   | S13      | Cell balancing FET control output for 13th cell.                                                            | AO                      |  |  |  |  |

| 59   | B14_13   | Common terminal for cell balancing S13 and S14.                                                             | AO                      |  |  |  |  |

| 60   | S14      | Cell balancing FET control output for 14th cell.                                                            | AO                      |  |  |  |  |

| 61   | C14      | Cell voltage input. Connect to the positive terminal of 14th cell.                                          | Al                      |  |  |  |  |

| 62   | VBAT     | Power supply of chip. This pin is also sensed by internal ADC through a voltage divider. Refer to Table 73. | Р                       |  |  |  |  |

| 63   | CAP2     | Pin2 external bootstrap capacitance. Refer to Table 73.                                                     | Al                      |  |  |  |  |

| 64   | CAP1     | Pin1 external bootstrap capacitance. Refer to Table 73.                                                     | Al                      |  |  |  |  |

| -    | GNDEP    | Ground terminal, connect to AGND plane                                                                      | G                       |  |  |  |  |

<sup>1.</sup> I/O type legend: AI = Analog Input; AO = Analog Output; AIO = Analog I/O; DI = Digital Input; DO = DigitalOutput; DIO = Digital I/O; P = Power; G = Ground; NC = Not Connect.

DS13636 - Rev 2 page 8/184

## 3 Product electrical ratings

### 3.1 Operating range

Within the operating range the part operates as specified and without parameter deviations. The device may not operate properly if maximum operating conditions are exceeded.

Once taken beyond the operative ratings and returned back within, the part will recover with no damage or degradation, unless the AMR are exceeded.

Additional supply voltage and temperature conditions are given separately at the beginning of each electrical specification table.

All voltages are related to the potential at substrate ground AGND, unless otherwise noted.

**Table 2. Operating ranges**

| Symbol                                              | Parameter | Test conditions                                                                    | Min.     | Тур. | Max.        | Unit |

|-----------------------------------------------------|-----------|------------------------------------------------------------------------------------|----------|------|-------------|------|

|                                                     |           | Supply voltage                                                                     | 9.6      |      | 64          | V    |

| VBAT                                                | Global    | Transient operation, 40 ms pulse, repetitive as per VDA320 E48-02 test.            | 64       |      | 70          | V    |

| VBAT, VREG, VCOM, VTREF                             |           | Supply voltage in case of transceiver use only (see Section 6.12 Transceiver mode) | 4.6      | 5    | 5.4         | V    |

| C0                                                  | Global    | Lower Cell Terminal Voltage                                                        | -0.3     |      | 0.3         | V    |

| B(n,n-1); Sn                                        | Global    | Cell Terminal Voltage                                                              | 0        |      | VBAT        | V    |

| C(n) for n=1 to 9                                   | Global    | Cell Terminal Voltage                                                              | 0        |      | VBAT – 4.5  | V    |

| C(n) for n=10 to 14                                 | Global    | Cell Terminal Voltage                                                              | 3        |      | VBAT + 0.3  | V    |

| C(n)-C(n-1) for n=1 to 14                           |           | Cell Terminal Differential Voltage                                                 | 0        |      | 4.7         | V    |

| S(n+1)-B(n+1,n); B(n+1,n)-S(n)<br>for n=1 to 13 odd |           | Cell Balance Terminal Differential Voltage                                         | 0        |      | 4.7         | V    |

| C(n)-S(n) for n=1 to 14                             |           | Cell Terminal Differential Voltage                                                 | 0        |      | 4.7         | V    |

| VBAT – C(14)                                        |           | Battery / high Terminal Differential Voltage                                       | -0.3     |      | 61          | V    |

| ISOHP/M, ISOLP/M                                    | Global    |                                                                                    | -0.3     |      | VCOM        | V    |

| GPIOn                                               | Local     |                                                                                    | -0.3     |      | VCOM        | V    |

| SPIEN                                               | Local     |                                                                                    | -0.3     |      | VCOM        | V    |

| VTREF                                               | Local     |                                                                                    |          | 5    |             | V    |

| ISENSEP - ISENSEM                                   | Local     | CSA Input Differential Mode<br>Range                                               | -0.15    |      | 0.15        | V    |

| ISENSEP + ISENSEM  / 2                              | Local     | CSA Input Common Mode Range (Referenced to GNDREF)                                 | -0.225   |      | 0.225       | V    |

| VCOM                                                | Local     |                                                                                    |          | 5    |             | V    |

| VANA                                                | Local     | Info only                                                                          |          | 3.3  |             | V    |

| VREG                                                | Local     |                                                                                    |          | 6.5  |             | V    |

| NPNDRV                                              | Local     |                                                                                    | VREG-0.3 |      | VREG + 1.5  | V    |

| CAP1                                                | Local     |                                                                                    | 0        |      | VBAT        | V    |

| CAP2                                                | Local     |                                                                                    | VREG     |      | VBAT + VREG | V    |

DS13636 - Rev 2 page 9/184

### 3.1.1 Supply voltage ranges

The device operates up to 14 cells of battery for hybrid and electric vehicles. The device can cover the voltage range of the main automotive Lithium batteries, up to a maximum of 4.6 V per cell in operating conditions. The IC has been engineered to sustain transient OV events as per LV 148

All operative ranges are listed in picture below.

If the stand by V3V3 regulator goes in POR, the device is put in reset.

Critical **Normal** Critical **AMR** AMR OV UV Op **Violation** Violation Params Permanent Permanent may damage damage deviate Permanent Permanent • All parameter parameter functions deviation deviation available 4.6 V 72 V **VBAT** 9

Umage: Control of the 12 70 V ٧٥. .4 \

Figure 4. Device operation in the VBAT supply voltage ranges

### 3.2 Absolute maximum ratings

Exceeding any Absolute Maximum Rating (AMR) may cause permanent damage to the integrated circuit. All voltages are related to the potential at substrate ground AGND.

| Symbol                                             | Parameter | Test conditions                                                                                                                                                              | Min. | Тур. | Max.                   | Unit |

|----------------------------------------------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------------------------|------|

| VBAT, C14                                          | -         |                                                                                                                                                                              | -0.3 | -    | 72                     | V    |

| C0                                                 | -         |                                                                                                                                                                              | -0.3 | -    | 0.3                    | V    |

| C(n); B(n,n-1); Sn                                 | -         |                                                                                                                                                                              | -0.3 | -    | 72                     | V    |

| C(n)-C(n-1) for n=1 to 14                          | -         | In this range, the device is not damaged, but leakage from pins may exceed I <sub>CELL_LEAK</sub> (see Table 39) if ADCs are enabled; it doesn't exceed if ADCs are disabled | -72  | -    | 72                     | V    |

| C(n)-C(n-1) for n=1 to 14                          | -         | In this range, the leakage from pins I <sub>CELL_LEAK</sub> is guaranteed (see Section 6.10.5 Busbar connection) if ADCs are enabled or disabled                             | -6   | -    | 6                      | V    |

| S(n+1)-B(n+1,n) B(n+1,n)-S(n)<br>for n=1 to 13 odd | -         |                                                                                                                                                                              | -0.3 | -    | V <sub>BAL_CLAMP</sub> | V    |

| C(n)-S(n) for n=1 to 14                            | -         | Vreg < 2 V                                                                                                                                                                   | -72  | -    | 72                     | V    |

| VBAT-C14                                           | -         |                                                                                                                                                                              | -72  | -    | 72                     | V    |

| ISOHP/M, ISOLP/M                                   | -         |                                                                                                                                                                              | -0.3 | -    | 6                      | V    |

| GPIOn                                              | -         |                                                                                                                                                                              | -0.3 | -    | 5.5                    | V    |

| SPIEN                                              | -         |                                                                                                                                                                              | -0.3 | -    | 12                     | V    |

| VTREF                                              | -         |                                                                                                                                                                              | -0.3 | -    | 6                      | V    |

**Table 3. Absolute Maximum Rating**

DS13636 - Rev 2 page 10/184

| Symbol                 | Parameter | Test conditions | Min.        | Тур. | Max.        | Unit |

|------------------------|-----------|-----------------|-------------|------|-------------|------|

| ISENSEP/M              | -         |                 | -0.3        | -    | 4.5         | V    |

| VCOM                   | -         |                 | -0.3        | -    | 6           | V    |

| VANA                   | -         |                 | -0.3        | -    | 4.5         | V    |

| VREG                   | -         |                 | -0.3        | -    | 12          | V    |

| NPNDRV                 | -         |                 | -0.3        | -    | 12          | V    |

| CAP1                   | -         |                 | -0.3        | -    | VBAT + 0.3V | V    |

| CAP2                   | -         |                 | VREG - 0.3V | -    | VBAT + 7V   | V    |

| DGND, CGND             | -         |                 | -0.3        | -    | + 0.3       | V    |

| GNDREF shorted to AGND | -         |                 |             | -    |             |      |

**Table 4. ESD protection**

| Item                                                                                                 | Parameter | Test conditions         | Min. | Тур. | Max. | Unit |

|------------------------------------------------------------------------------------------------------|-----------|-------------------------|------|------|------|------|

| All pins Except Isolated<br>Communication Terminals and<br>Global pins <sup>(1)</sup>                | _         | HBM <sup>(2)</sup>      | -2   | -    | 2    | kV   |

| Isolated Communication<br>Terminals <sup>(1)(2)</sup> and Global pins<br>versus all GND+EP connected | _         |                         | -4   | -    | 4    | kV   |

| All pins except Corner Pins                                                                          | _         | CDM <sup>(3)</sup>      | -500 | -    | 500  | V    |

| Corner Pins                                                                                          | _         |                         | -750 | -    | 750  | V    |

| All pins                                                                                             | -         | Latch up <sup>(4)</sup> | -100 | -    | 100  | mA   |

- 1. Tested per AEC-Q100-002.

- 2. Isolated Communication Terminals: ISOHP, ISOHM, ISOLP\_SDI, ISOLM\_NCS.

- 3. Tested per AEC-Q100-011.

- 4. Tested per AEC-Q100-004, Class-2, Level-A.

Pins are all GND connected together.

## 3.3 Temperature ranges and thermal data

Table 5. Temperature ranges and thermal data

| Symbol               | Parameter                                             | Test conditions | Min | Max | Unit |

|----------------------|-------------------------------------------------------|-----------------|-----|-----|------|

| T <sub>amb</sub>     | Operating and testing temperature (ECU environment)   | -               | -40 | 105 | °C   |

| TJ                   | Junction temperature for all parameters               | -               | -40 | 125 | °C   |

| T <sub>stg</sub>     | Storage temperature                                   | -               | -65 | 150 | °C   |

| T <sub>ot</sub>      | Thermal shut-down temperature (junction)              | -               | 175 | 200 | °C   |

| T <sub>ot</sub>      | Temperature ADC accuracy                              | -               | -10 | +10 | °C   |

| O <sub>Thys</sub>    | Thermal shut-down temperature hysteresis              | -               | 5   | 15  | °C   |

| R <sub>Thj-amb</sub> | Thermal resistance junction-to-ambient <sup>(1)</sup> | -               |     | 22  | °C/W |

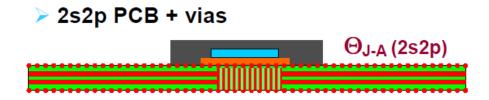

In "2s2p", the "s" suffix stands for "Signal" and the number before indicates how many PCB layers are dedicated to signal wires. The "p" suffix stands for "Power" and the number before indicates how many PCB layers are dedicated to power planes.

DS13636 - Rev 2 page 11/184

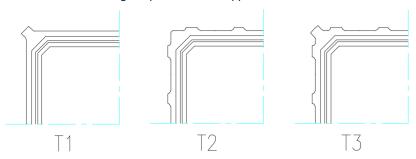

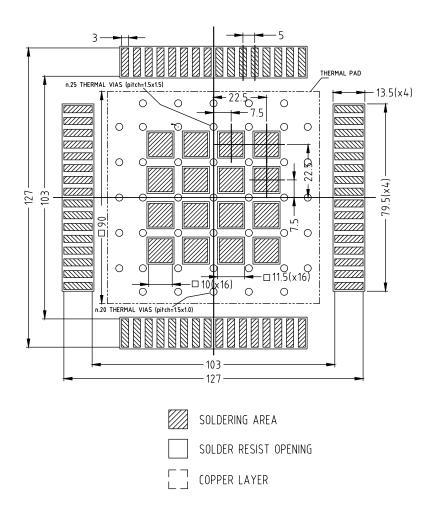

Figure 5. Sketch of a 2s2p PCB with thermal vias

## 3.4 Power management

All parameters are tested and guaranteed in the following conditions, unless otherwise noted: 9.6 V < VBAT < 64 V; -40  $^{\circ}$ C < Tambient < 105  $^{\circ}$ C

**Table 6. Power Management**

| Symbol                                                                                    | Parameter | Test conditions                                                                                                                                                                                                                                                       | Min. | Тур. | Max. | Unit |

|-------------------------------------------------------------------------------------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| I <sub>BAT_NORM</sub> , Total Supply Current in Normal Mode from VBAT pin                 | -         | Normal state (refer to Section 4.1 Device functional state); no load on VTREF; the chip performs continuously data transmission via isolated communication interfaces to higher and lower sides in a stack daisy chain.                                               | 1    |      | 2.5  | mA   |

| ·                                                                                         |           | Application info: IBAT is not affected by communication. Current needed for COM interfaces is drawn out of VREG regulator.                                                                                                                                            |      |      |      |      |

| I <sub>BAT_NORM_ADC</sub> , Total Supply<br>Current in Normal Mode from<br>VBAT pin       | -         | Normal state; No load on VTREF; no communication; The chip performs continuously sampling and converting.                                                                                                                                                             | 5.5  |      | 9    | mA   |

| I <sub>REG_NORM_CSEN1</sub> , Total Supply<br>Current in Normal Mode from<br>VREG MOS     | -         | Normal state; No load on VTREF; no communication; no ADC conversion; Curr sense. Enabled by coulombcounter_en = 1                                                                                                                                                     |      |      | 21   | mA   |

| I <sub>REG_NORM_CSEN0</sub> , Total Supply<br>Current in Normal Mode from<br>VREG MOS     | -         | Normal state; No load on VTREF; no communication; no ADC conversion; Curr sense Disabled by coulombcounter_en = 0                                                                                                                                                     |      |      | 20   | mA   |

| I <sub>REG_NORM_ADC_CSEN1</sub> , Total<br>Supply Current in Normal Mode<br>from VREG MOS | -         | Normal state; No load on VTREF; no communication; The chip performs continuously sampling and converting. Curr sense Enabled by coulombcounter_en = 1                                                                                                                 |      |      | 38   | mA   |

| I <sub>REG_NORM_ADC_CSEN0</sub> , Total<br>Supply Current in Normal Mode<br>from VREG MOS | -         | Normal state; No load on VTREF; no communication; The chip performs continuously sampling and converting. Curr sense Disabled by coulombcounter_en = 0                                                                                                                |      |      | 37   | mA   |

| I <sub>REG_NORM_COMM</sub> , Additional supply current drawn from VREG for communication  | -         | Normal state; No load on VTREF; The chip performs continuously data transmission via isolated communication interfaces to higher and lower sides in a stack daisy chain. (measured with out_res_tx_isoh/l = 11, highest differential amplitude, highest consumption). | 8    | 10.8 | 13   | mA   |

| I <sub>BAT_SLP</sub> , Supply Current in Sleep<br>Mode                                    | -         | Lowest power state; Both internal oscillator and external wakeup detection on.                                                                                                                                                                                        | 10   |      | 50   | μA   |

| BAT_SLP_BAL_CONF                                                                          | -         | Supply Current in Silent Balance Mode (enabled only regulators necessary to bias balance preregulators, refer to Section 4.1 Device functional state).                                                                                                                | 1.2  | 2    | 2.8  | mA   |

| IBAT_BALANCE                                                                              | -         | Delta current when the balancing of all 14 cells are act ivated.                                                                                                                                                                                                      | 0.4  | 0.55 | 0.7  | mA   |

DS13636 - Rev 2 page 12/184

| Symbol           | Parameter | Test conditions                                                     | Min. | Тур. | Max. | Unit |  |

|------------------|-----------|---------------------------------------------------------------------|------|------|------|------|--|

| IREG_GPIO_DIGOUT | -         | Delta current from VREG pin needed to use 1 GPIO as digital output. | 0.4  | 0.8  | 1.2  | mA   |  |

Average DC current consumption in application can be estimated according to the following equations: **Estimation of the average DC current consumption in application**

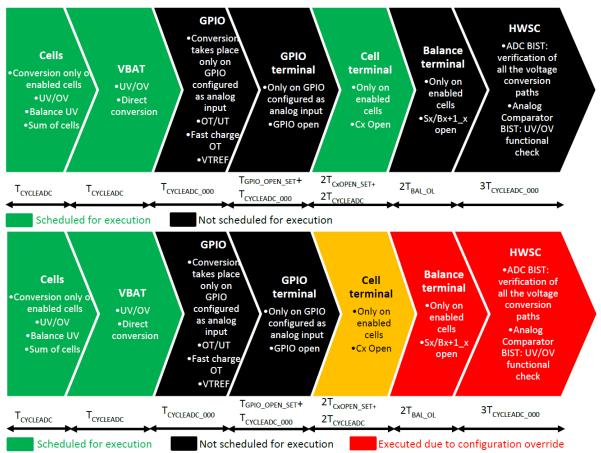

$$\begin{split} I_{AVG} &= \left( I_{BAT_{NORM}ADC} + I_{REG_{NORM}ADC} + \frac{N_{BAL}}{14} I_{BAT_{BALANCE}} + I_{REG_{GPIO_{DIGOUT}}} N_{DIGOUT} \right) \times W_{CONV} \\ &+ \left( I_{BAT_{NORM}} + I_{REG_{NORM}} + \frac{N_{BAL}}{14} I_{BAT_{BALANCE}} + I_{REG_{GPIO_{DIGOUT}}} N_{DIGOUT} \right) \times W_{BAL_{CL}} + I_{LP} \times W_{LP} \\ W_{CONV} &= \frac{2T_{CYCLEADC_{SLEEP}}}{T_{PERIOD}} + \frac{T_{CYCLEADC_{000}}}{N_{CYCLE_{GPIO}} N_{PERIOD}} + \frac{T_{GPIO_{DEN_{SET}}} + T_{CYCLEADC_{000}}}{N_{CYCLE_{GPIO_{TERM}}} N_{PERIOD}} \\ &+ \frac{2T_{CXOPEN_{SET}} + 2T_{CYCLEADC_{000}}}{N_{CYCLE_{HADC_{CONO}}} + \frac{3T_{CYCLEADC_{000}}}{N_{CYCLE_{GPIO_{TERM}}} N_{PERIOD}} \\ W_{BAL_{CU}} &= \frac{2T_{BAL_{OL}}}{N_{CYCLE_{BAL_{TERM}}} N_{CYCLE_{SLEEP}} \\ W_{LP} &= 1 - W_{CONV} - W_{BAL_{CU}} \\ T_{PERIOD} &= \begin{cases} T_{CYCLE_{SLEEP}} & \text{if CSA is disabled} \\ T_{CYCLE_{SLEEP}} & \text{if CSA is disabled} \end{cases} \\ I_{REG_{NORM}_{ADC}} &= \begin{cases} I_{REG_{NORM}_{ADCCSEN0}} & \text{if CSA is disabled} \\ I_{REG_{NORM}_{ADC}} & \text{if CSA is enabled} \end{cases} \\ I_{REG_{NORM}_{ADC}} &= \begin{cases} I_{REG_{NORM}_{ADCCSEN0}} & \text{if CSA is enabled} \\ I_{REG_{NORM}_{CSEN0}} & \text{if CSA is enabled} \end{cases} \\ I_{SLEEP} &= \begin{cases} I_{BAT_{SLP}_{BAL_{CONF}}} & \text{if N}_{BAL} > 0} \\ I_{BAT_{SLP_{BAL_{CONF}}}} & \text{if Cyclic Wakeup mode is activated} \end{cases} \\ I_{LP} &= \begin{cases} I_{SLEEP} + \frac{N_{BAL}}{14} \times I_{BAT_{BALANCE}} & \text{if Cyclic Wakeup mode is activated} \\ I_{BAT_{NORM}} + I_{REG_{NORM}} + \frac{N_{BAL}}{14} \times I_{BAT_{BALANCE}} + I_{REG_{GPIO_{DIGOUT}}} N_{DIGOUT_{COUT_{COUT_{COUT_{COUT_{COUT_{COUT_{COUT_{COUT_{COUT_{COUT_{COUT_{COUT_{COUT_{COUT_{COUT_{COUT_{COUT_{COUT_{COUT_{COUT_{COUT_{COUT_{COUT_{COUT_{COUT_{COUT_{COUT_{COUT_{COUT_{COUT_{COUT_{COUT_{COUT_{COUT_{COUT_{COUT_{COUT_{COUT_{COUT_{COUT_{COUT_{COUT_{COUT_{COUT_{COUT_{COUT_{COUT_{COUT_{COUT_{COUT_{COUT_{COUT_{COUT_{COUT_{COUT_{COUT_{COUT_{COUT_{COUT_{COUT_{COUT_{COUT_{COUT_{COUT_{COUT_{COUT_{COUT_{COUT_{COUT_{COUT_{COUT_{COUT_{COUT_{COUT_{COUT_{COUT_{COUT_{COUT_{COUT_{COUT_{COUT_{COUT_{COUT_{COUT_{COUT_{COUT_{COUT_{COUT_{COUT_{COUT_{COUT_{COUT_{COUT_{COUT_{COUT_{COUT_{COUT_{COUT_{COUT_{COUT_{COUT_{COUT_{COU$$

DS13636 - Rev 2 page 13/184

## 4 Functional description

In the following paragraphs, the functionalities of the device are listed and described in detail.

### 4.1 Device functional state

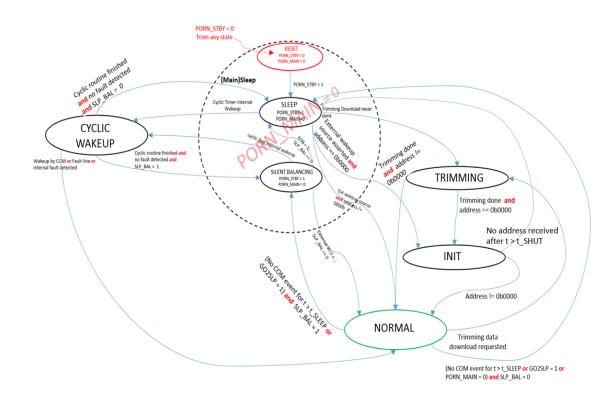

Figure 6. Device functional states

#### 4.1.1 Reset and Sleep states

**Reset state:** when stand-by logic is reset, all registers on device are reset. The battery voltage is still under threshold.

From here, as soon as the PORN\_STBY goes high the Stby Logic gets its supply power and the **Sleep** state is reached.

#### 4.1.1.1 Operations in Reset state

No operation is possible in Reset state

### Sleep state:

This state is reached:

- coming from Reset state on PORN\_STBY rising

- from other states in case a Go2SLP cmd is sent by uP or no communication is received for t > t SLEEP

- from Init State in case the device address is still 0b0000 after t > t SHUT

- from Cyclic\_Wup state once the Cyclic Wup job is done and a silent balancing is not to be resumed.

In this state the device is sensitive to External Sources in order to wake up the Main Logic. External sources are: ISO lines, Fault line, SPI\_CS (SPI\_CLK) pins, also a GPIO pin for "Master" units.

In this state a slow oscillator is working allowing the device to wake itself up every  $t = t_{CYCLIC\_SLEEP} + t_{CYCLIC\_WUP}$  and move to **Cyclic Wup** state.

DS13636 - Rev 2 page 14/184

During **Sleep** state, the current consumption is significantly reduced to I<sub>SLEEP</sub> current value: only the Communication wake up sources monitoring, low-speed oscillator for cyclic wake up timer, and the corresponding reference and power supply are activated.

Different events can cause a wake up, depending on the configuration decided by the microcontroller:

- ISO COMM/ SPI SIGNAL: this wake-up during a regular SLEEP mode state moves the L9963 FSM to Init or Normal State. A proper signal will be detected as pre-wake up (simple edge readout), and later it must be followed by a wake-up signal that will be decoded by the L9963 which, in the meanwhile, has entered in a higher consumption mode (regulators turned ON, isolated RX/TX enabled). Any protocol frame recognized as electrically consistent will wake up the device. However, the command will not be interpreted and thus no execution takes place;

- INTERNAL COUNTER: it is possible that the microcontroller defines an automatic wake up of L9963 (when

put in SLEEP mode) every T<sub>CYCLE\_SLEEP</sub>, in order to perform the diagnostics in the CYCLIC WAKEUP

state;

- **GPIO SIGNAL**: In case GPIO7 is configured as wake up source (**GPIO7\_WUP\_EN = 1**), a high logic level on it will wake up L9963;

- FAULT: in case a fault is detected in an upper L9963, a proper signal is communicated through the FAULT line. The receiver connected to GPIO1/FAULTH pin will detect the event and the device will be forced to evolve into the normal state, in order to transmit the fault downward.

The wake-up event coming from external wake up sources is verified by the stby logic (pattern confirmation step) before waking up the main logic (the main logic is kept under reset and its clock is gated off until the Sleep state is left).

The wakeup sequence lasts T<sub>WAKEUP</sub>.

#### 4.1.1.2 Operations in Sleep state

Only the Stand-by logic is working in Sleep state.

| Operation                   | Operation Timing mode Functions involv |                                                                                                                              |  |  |

|-----------------------------|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------|--|--|

| Wake up Management          | Always ON                              | Timers, Pin Input Buffer and ISO lines receiver ON. External sources activity detection, receivers and input buffers powered |  |  |

| Awakening Pattern Detection | Once                                   | Comparison logic                                                                                                             |  |  |

Table 7. Operations in Sleep state

#### 4.1.2 Init state

In **Init** state, after having been woken up, the device waits for the uP to send the Address assignment command. Refer to Section 4.1.2.2 Addressing procedure.

If the address command is received before the Init timer expires (t\_SHUT), the device address is stored into a stand-by logic register (**chip\_ID**) and the device goes to **Normal** state.

The **chip\_ID** field is then locked and no longer editable. Two actions can correctly re-initialize the device (including the **chip\_ID**):

- Hard reset: (POR STBY)

- Soft reset: it is recommended to set SW\_RST and GO2SLP in the same frame

- Note that Soft reset will leave communication timeout (CommTimeout) unmodified

- Note that Soft reset will also clear the chip ID

- If only SW RST is sent, the device will wait for CommTimeout and then move to Sleep state

If the Init timer (t\_SHUT) expires before the command is received, the device goes back to **Sleep** state.

All references are powered, interfaces are ready data transmission. The commands sent by the micro-controller can be read from both ISO lines and SPI pins. However, while in Init state, only the **chip\_ID**, **isotx\_en\_h** and **iso\_freq\_sel** fields are writable. It is not possible to write/read other registers.

Any failure is masked until the device receives an address.

DS13636 - Rev 2 page 15/184

#### 4.1.2.1 Operations in Init state

Here below a list of operations the device can perform during Init State.

Table 8. Operations in Init state

| Operation     | Timing mode | Functions involved                 |

|---------------|-------------|------------------------------------|

| Communication | Always ON   | SPI/isolated SPI Logic and storage |

| Init Timeout  | Always ON   | t_SHUT timer                       |

### 4.1.2.2 Addressing procedure

The following algorithm describes the correct daisy-chain addressing procedure for a stack of N<sub>DEVICES</sub>:

Send BROADCAST command with chip\_ID = X, lsotx\_en\_h = 1, iso\_freq\_sel = 00

Send READ command with dhip\_ID = X, lsotx\_en\_h = 1, iso\_freq\_sel = 00

Send READ command with chip\_ID = X, lsotx\_en\_h = 1, iso\_freq\_sel = 00

Send READ command with chip\_ID = X, lsotx\_en\_h = 1, iso\_freq\_sel = 00

Send READ command with chip\_ID = X, lsotx\_en\_h = 1, iso\_freq\_sel = 00

Send WRITE command with chip\_ID = 00 = 00 = 1, iso\_freq\_sel = 10 iso freq\_sel = 10 isotx\_en\_h = 0, iso\_freq\_sel = 10 isotx\_en\_h = 0, i

Figure 7. Daisy chain addressing algorithm

Switching to high frequency (**iso\_freq\_sel = 11**) before initialization procedure has been completed is not recommended, since it might prevent other units from being initialized.

Once initialization procedure is done, it is possible to lock ISOH port status and ISO frequency configuration by setting **Lock\_isoh\_isofreq = 1**: the lock adds more safety against unwanted write access to **iso\_freq\_sel** and **isotx\_en\_h** bit in DEV\_GEN\_CFG register.

#### 4.1.3 Normal state

All references are powered, and the **ADCs** and interfaces are ready for measurement and data transmission respectively. The commands sent by the micro-controller can be read from both ISO lines and SPI pins.

On receiving a valid command, the L9963 executes the corresponding operations, such as voltage, current and over-temperature measurement.

Some core safety operations (e.g. OV, UV, OT, UV, and VBAT monitoring) are checked in the background automatically.

In case the communication with MCU is missing for t > t\_SLEEP (programmable via **CommTimeout**, maskable via **comm\_timeout\_dis**) or a GO2SLP command is received, the device moves either to **Sleep** state or to **Silent Balancing** state, depending on **slp\_bal\_conf** bit and balancing state.

DS13636 - Rev 2 page 16/184

A Soft RESET command received when in Normal state clears all registers except **CommTimeout**. The device is kept in Normal and doesn't move to Reset state.

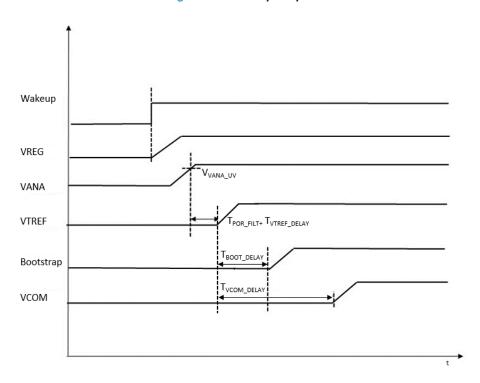

#### 4.1.4 Power up sequence

Final **Normal** state is reached through a power up sequence, which involves the turn ON of all regulators. The following power up sequence is performed correctly if VBAT pin voltage lays in the operating range (refer to Table 3):

- VREG is the first regulator to turn ON

- As soon as VREG reaches enough voltage dynamic (> 3V), also VANA regulator starts to turn ON

- When VANA regulator voltage reaches V<sub>VANA\_UV</sub> threshold and related digital filter time T<sub>POR\_FILT</sub> + T<sub>VTREF\_DELAY</sub> expires, VTREF regulator is turned ON

- After T<sub>BOOT\_DELAY</sub> in respect to VTREF enable, Bootstrap circuit is enabled in charge phase (CAP2 connected to VREG, CAP1 to GND)

- After T<sub>VCOM DELAY</sub> in respect to VTREF enable, VCOM regulator is turned ON

Normally, the power up sequence lasts  $T_{WAKEUP}$ . In case it lasts longer than a specific timeout, the device moves back to a low power state (Sleep or Silent Balancing, depending on the previous state). The following timeouts are implemented:

- timeout\_VCOM\_UP\_first, valid only for the first power up

- timeout VCOM UP, valid for each wake up

- timeout\_OSCI\_MAIN, valid for each wake up

#### During power down:

- VCOM, VTREF and Bootstrap are turned off at the same time

- VREG is turned off after T<sub>VREG</sub> OFF

- When VREG falls below 4 V (typical value), VANA starts falling along with VREG.

Figure 8. Power up Sequence

DS13636 - Rev 2 page 17/184

The device is still able to communicate if VTREF and Bootstrap power up fails: VCOM regulator is started anyway. It is not recommended to send any SPI frame to the device before T<sub>WAKEUP</sub> expires. Any incoming frame while L9963E is still performing the power up routine might be discarded.

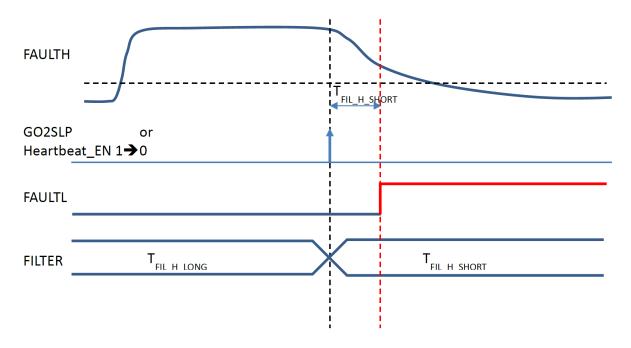

#### 4.1.5 Silent Balancing state

There is the possibility to perform the balancing of one (or more) cells with a reduced current consumption with respect to doing that in **Normal** mode: this state is called **Silent Balancing**.

In **Silent\_Bal** the same resources as in **Sleep** state are active, in addition to the balance predrivers and the necessary bias circuitry.

To enter in Silent Balancing state from Normal state, the following conditions shall be verified:

- Cell balancing must be ON

- 2. The slp\_bal\_conf flag shall be set to '1'

- 3. A "go to sleep" condition shall be verified (either an explicit GO2SLP command or communication timeout expiration)

If a cell balancing is previously demanded in **Normal** mode and the **slp\_bal\_conf** flag is set to 1, when a condition to go to sleep (low consumption) occurs the device enters **Silent Balancing**, not Sleep state and the required cell-balancing starts (or continues).

3 possible leaving ways from Silent Balancing mode:

- any wake up signal on communication or FAULT Line can force the chip to stop the balancing and then go back to the Normal state. Any protocol frame recognized as electrically consistent will wake up the device. However, the command will not be interpreted and thus no execution takes place.

- An external Fault must bring the device to Normal state and stop the balancing.

- As soon as the required balancing target is finished, the EOB (End of Balancing) bit is set to one and the chip enters the Sleep state.

- If the Cyclic signal is raised the device goes to Cyclic\_Wup state, runs the diagnosis then it goes back to Silent Balancing (if slp\_bal\_conf flag = 1) where the balancing resumes

#### 4.1.5.1 Operations in Silent Balancing state

Here below a list of operations the device can perform during Silent Balancing state.

Table 9. Opeations in Silent Balancing state

| Operation           | Timing mode | Functions involved                                     |

|---------------------|-------------|--------------------------------------------------------|

| Balancing low power | Always ON   | Balancing timer, Drivers ON, Balance short comparators |

| Wakeup management   | Always ON   | Wakeup logic and wakeup sources interfaces ON          |

#### 4.1.6 Cyclic wake up state

From both Sleep and Silent Balancing states, the device moves periodically (once every t<sub>CYCLIC\_SLEEP</sub>) to Cyclic Wup state in order to perform a fault monitoring.

Diagnostic checks are done in this state as well as always-on monitorings. ADC must be ON to check possible critical battery conditions. Any detected fault moves the device to the Normal state.

An "On-demand" operation is only possible once the device has moved to Normal in case of any detected fault Possible ways to leave this state:

- Any fault detected during this mode moves the device to the Normal state.

- A wake up from Fault line or Comm lines moves the device to the Normal state. Any protocol frame

recognized as electrically consistent will wakeup the device. However, the command will not be interpreted

and thus no execution takes place

- If the defined monitoring tasks are finished, the device can move to the SLEEP or SILENT BALANCING states automatically based on the state before Cyclic Conversions (slp\_bal\_conf flag).

#### 4.1.6.1 Operations in Cyclic wake up state

Here below a list of operations the device can perform during Cyclic wake up state.

DS13636 - Rev 2 page 18/184

Table 10. Operations in Cyclic Wakeup state

| Operation                 | Timing mode | Functions involved                             |

|---------------------------|-------------|------------------------------------------------|

| Battery fast OV/UV        | Always ON   | Threshold Comparator                           |

| Battery OV/UV             | Once        | ADCV measurements vs. threshold                |

| Cells OV/UV               | Once        | ADCV measurements vs. threshold                |

| GPIO OT/UT                | Once        | ADCV measurements vs. threshold                |

| OC Monitor                | Always ON   | ADCC measurements vs. threshold                |

| OT Monitor                | Always ON   | ADCT measurements vs. threshold                |

| GPO Short Detection       | Always ON   | Logical Comparison                             |

| Clock Monitor             | Always ON   | Frequency comparison to secondaty monitor      |

| Downward Fault Signalling | Always      | Receivers and Transmitters                     |

| Cell Open                 | Once        | ADCV measurements vs. threshold                |

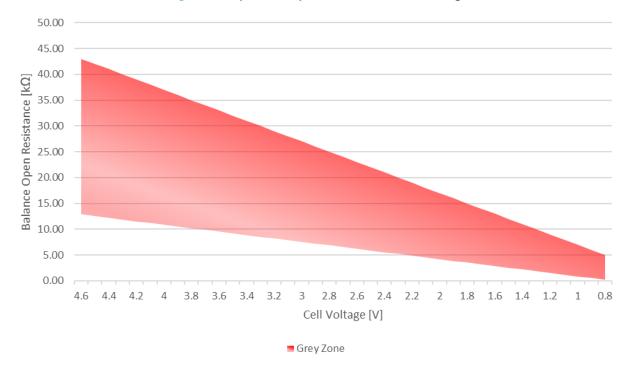

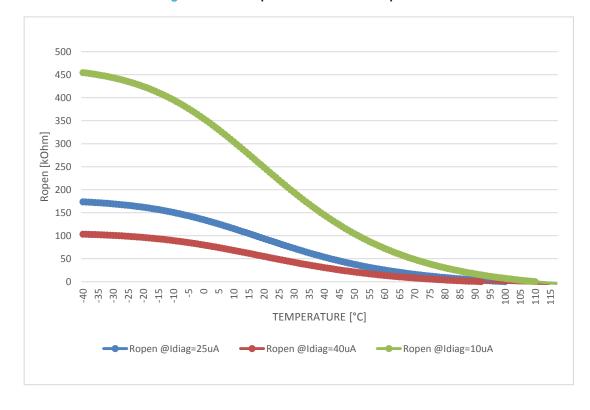

| Balancing Open            | Once        | Voltage Comparator, Timer                      |

| Wake up Management        | Always ON   | Wake up logic and wakeup sources interfaces ON |

Cyclic operations have their own periods written by MCU in specific SPI registers.

In case the "On-demand" and "cyclic" timing modes are both possible, an "on-demand" command starts a single operation immediately, breaking the cyclic period, and resets the cyclic counter.

In GPIO short detection the detection is guaranteed only in the duty phase, if the pin is configured as an output.

### 4.1.7 Sleep parameters

All parameters are tested and guaranteed in the following conditions, unless otherwise noted: 9.6 V < VBAT < 64 V;  $-40 \,^{\circ}\text{C} < \text{Tambient} < 105 \,^{\circ}\text{C}$

Table 11. Sleep parameters

| Symbol                        | Parameter                                                                                                | Test conditions | Min. | Тур. | Max. | Unit |

|-------------------------------|----------------------------------------------------------------------------------------------------------|-----------------|------|------|------|------|

| T <sub>GPIO7_WAKEUP</sub>     | GPIO7 deglitch filter when used as Wakeup Source                                                         | Tested by SCAN  |      | 150  |      | μs   |

| T <sub>UV_SHORT_DELAY</sub>   | Delay after POR. Used to latch VCOM_UV and VTREF_UV                                                      | Tested by SCAN  |      | 40   |      | μs   |

| T <sub>WAKEUP</sub>           | Time necessary to complete Wake up from SLEEP mode (between Wake up source and VCOM out of UV condition) |                 |      |      | 2    | ms   |

| t_SHUT                        |                                                                                                          | Tested by SCAN  |      | 60   |      | S    |

| t SLEEP 00                    | Communication Timeout                                                                                    | Tested by SCAN  |      | 32   |      | ms   |

| i_SLEEP_00                    | CommTimeout = 00                                                                                         | rested by SCAN  |      | 32   |      | 1115 |

| t SLEEP 01                    | Communication Timeout                                                                                    | Tested by SCAN  |      | 256  |      | ms   |

| (_SLLLF_01                    | CommTimeout = 01                                                                                         | rested by SCAN  |      | 230  |      | 1115 |

| t_SLEEP_10                    | Communication Timeout                                                                                    | Tested by SCAN  |      | 1024 |      | ms   |

| LOLLLI _10                    | CommTimeout = 10                                                                                         | rested by SOAN  |      | 1024 |      | 1113 |

| t_SLEEP_11                    | Communication Timeout                                                                                    | Tested by SCAN  |      | 2048 |      | ms   |

| COLLEI _ II                   | CommTimeout = 11                                                                                         | rested by SOAN  |      | 2040 |      | 1113 |

| tcyclic_sleep_000             |                                                                                                          | Tested by SCAN  |      | 100  |      | ms   |

| tcyclic_sleep_001             |                                                                                                          | Tested by SCAN  |      | 200  |      | ms   |

| t <sub>CYCLIC_SLEEP_010</sub> |                                                                                                          | Tested by SCAN  |      | 400  |      | ms   |

DS13636 - Rev 2 page 19/184

| Symbol                          | Parameter                                                                                       | Test conditions | Min. | Тур.      | Max. | Unit |

|---------------------------------|-------------------------------------------------------------------------------------------------|-----------------|------|-----------|------|------|

| tCYCLIC_SLEEP_011               |                                                                                                 | Tested by SCAN  |      | 800       |      | ms   |

| tCYCLIC_SLEEP_100               |                                                                                                 | Tested by SCAN  |      | 1600      |      | ms   |

| tCYCLIC_SLEEP_101               |                                                                                                 | Tested by SCAN  |      | 3200      |      | ms   |

| tCYCLIC_SLEEP_110               |                                                                                                 | Tested by SCAN  |      | 6400      |      | Ms   |

| tcyclic_sleep_111               |                                                                                                 | Tested by SCAN  |      | 1280<br>0 |      | Ms   |

| T <sub>VREG_OFF</sub>           |                                                                                                 | Tested by SCAN  |      | 500       |      | μs   |

| FMAIN_OSC_stby                  | Internal standby Oscillator frequency                                                           |                 | 20   | 32        | 45   | KHz  |

| FAUX_OSC_stby                   | Internal standby redundant Oscillator frequency                                                 |                 | 20   | 32        | 45   | KHz  |

| timeout_VCOM_UP_first           | Timeout at first power up. From wakeup event to VCOM_UV release                                 | Tested by SCAN  |      | 8         |      | ms   |

| timeout_VCOM_UP                 | Default power up timeout. From wakeup event to VCOM_UV release                                  | Tested by SCAN  |      | 4         |      | ms   |

| timeout_OSCI_MAIN               | From wakeup event to main oscillator stable                                                     | Tested by SCAN  |      | 10        |      | ms   |

| timeout_POR_MAIN                | VANA settling time timeout                                                                      | Tested by SCAN  |      | 1.5       |      | ms   |

| T <sub>BOOT_DELAY</sub>         | Delay between VTREF enable and Bootstrap enable                                                 | Tested by SCAN  |      | 200       |      | μs   |

| T <sub>VTREF_DELAY</sub>        | Delay between VANA_UV release (POR_STBY asserted after T <sub>POR_FILT</sub> ) and VTREF enable | Tested by SCAN  |      | 630       |      | μs   |

| T <sub>VCOM_DELAY</sub>         | Delay between VTREF enable and VCOM enable                                                      | Tested by SCAN  |      | 400       |      | μs   |

| T <sub>WAKEUP_TIMEOUT_ISO</sub> | Timeout of the pulse counter for wakeup detection (isolated SPI)                                | Tested by SCAN  | 282  |           |      | μs   |

| T <sub>WAKEUP_TIMEOUT_SPI</sub> | Timeout of the pulse counter for wakeup detection (SPI)                                         | Tested by SCAN  | 84   |           | 138  | μs   |

| Twakeup_ncs_high                | Minimum NCS high time before sending SPI wake up frame                                          | Tested by SCAN  | 400  |           |      | μs   |

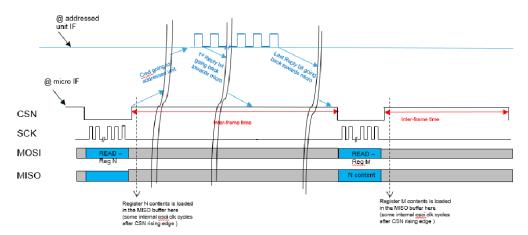

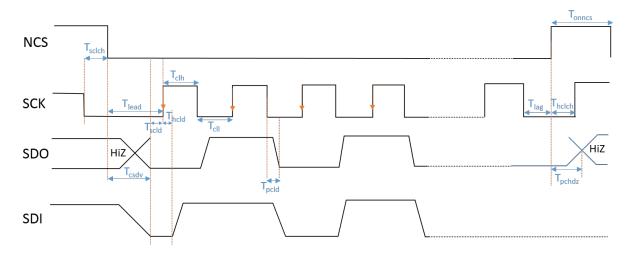

### 4.2 Serial communication interface

Two types of serial communication ports are included in L9963E: SPI and isolated interface:

- SPI can be used for the local communication between MCU and the closest L9963E

- Isolated SPI can be used for the global communication between several L9963E stacked in a daisy chain

Refer to Section 6.11 Communication architectures for all the different application scenarios.

The frequencies on the 2 communication interfaces are different and not related.

From micro-controller point of view a daisy chain of many L9963E devices is controlled as a single device addressable by using both the device ID and the device's internal register addresses.

### 4.2.1 Communication interface selection

Two communication ports are available:

- Port H: implemented via the ISOHp and ISOHm pins. It always works as Isolated SPI interface. It can be enabled by setting isotx\_en\_h = 1

- **Port L**: implemented via the ISOLp\_SDI, ISOLm\_NCS, GPIO8\_SCK, GPIO9\_SDO pins. It is always enabled and its configuration is latched upon first powe up and depends on the **SPIEN** pin

DS13636 - Rev 2 page 20/184

| Table 12. I | Port L | configuration | determination |

|-------------|--------|---------------|---------------|

|-------------|--------|---------------|---------------|

| Electrical condition                                        | Latched when         | Configuration                                                                  | Wake up source          |

|-------------------------------------------------------------|----------------------|--------------------------------------------------------------------------------|-------------------------|

| SPIEN = 1                                                   | Upon VCOM_UV release | Port L configured as SPI. Master Unit. SPIEN must be connected to VCOM         | SPI wake up logic       |

| SPIEN = 0 (default<br>condition if pin is left<br>floating) | Upon VCOM_UV release | Port L configured as isolated SPI. Slave Unit. SPIEN must be connected to AGND | ISOL wake up comparator |

In case the first power up fails and L9963E comes back to Sleep state without having latched the PORT L operating mode, both wake up sources will be kept active in order to allow subsequent power up trigger in both operating configurations.

When first power up completes successfully, only the wake up source related to the units with **SPIEN = 1** are **Master** units of the daisy chain. A **Master** Unit differs from the **Slave** ones (**SPIEN = 0**) because:

- It manages the asynchronicity between SPI CLK and the programmable bit-rate on the isolated line;

- · It exploits an internal buffer to store answers received from the slaves on ISOH port;

- It implements timeout mechanisms and frame error checks described in Section 4.2.4.4 Special frames;

- It forwards commands only if they are addressing Slave units. Any command addressed to the Master unit is not propagated on the ISOH port;