# サイプレスはインフィニオン テクノロジーズになりました

この表紙に続く文書には「サイプレス」と表記されていますが、これは同社が最初にこの製品を開発したからです。新規および既存のお客様いずれに対しても、引き続きインフィニオンがラインアップの一部として当該製品をご提供いたします。

# 文書の内容の継続性

下記製品がインフィニオンの製品ラインアップの一部として提供されたとしても、それ を理由としてこの文書に変更が加わることはありません。今後も適宜改訂は行います が、変更があった場合は文書の履歴ページでお知らせします。

# 注文時の部品番号の継続性

インフィニオンは既存の部品番号を引き続きサポートします。ご注文の際は、データシート記載の注文部品番号をこれまで通りご利用下さい。

www.infineon.com

# 4M ビット (512K×8) シリアル (SPI) F-RAM

# 特長

- 512K×8 構成の 4M ビット強誘電体ランダム アクセス メモリ (F-RAM)

- □ 高いアクセス可能回数:100 兆(10<sup>14</sup>)回の読み出し/書き込み

- □ 151年のデータ保持(データ保持期間およびアクセス可能回数表を参照してください。)

- □ NoDelay™ 書き込み

- □ 信頼性の高い強誘電体プロセスを使用

- 高速のシリアル ペリフェラル インターフェース (SPI)

- □最大周波数 40MHz

- □ シリアル フラッシュおよび EEPROM からの置き換え

- □ SPI モード 0 (0、0) およびモード 3 (1、1) に対応

- 洗練された書き込み保護スキーム

- □書き込み保護 (WP) ピンを使用したハードウェアによる保護

- 書き込みディスエーブル命令を使用したソフトウェアによる保護

- ロアレイの 1/4、1/2、または全体を対象としたソフトウェア ブロック保護

- デバイス ID

- □メーカー ID および製品 ID

- 低消費電力

- 1MHz でのアクティブ電流 300μA

- スタンバイ電流 100μA (typ)

- ロスリープ モード電流 3μA (typ)

- 低電圧動作: V<sub>DD</sub>=2.0V ~ 3.6V

- 産業機器用途向け温度範囲: -40°C ~ +85°C

- パッケージ

- □8ピン小型集積回路 (SOIC) パッケージ

- □8 ピンの薄型デュアル フラット ノーリード (TDFN) パッケージ

- RoHS 準拠

# 機能の説明

CY15B104Q は高度な強誘電体プロセスを適用した 4M ビットの不揮発性メモリです。強誘電体ランダム アクセス メモリ (F-RAM) は不揮発性であり、RAM 同様に読み書きを実行します。またシリアル フラッシュや EEPROM、その他の不揮発性メモリによる複雑さ、オーバーヘッド、システム レベルの信頼性関連問題を回避し、151 年間にわたって信頼できるデータ保持ができます。

シリアル フラッシュや EEPROM と違って、CY15B104Q はバス速度で書き込み動作を実行します。書き込み遅延は発生しません。データは、各バイトがデバイスに正常に転送された直後にメモリ アレイに書き込まれます。次のバス サイクルはデータポーリングを必要とせず開始できます。また本製品は他の不揮発性メモリと比較して多くの書き込み可能回数を提供します。CY15B104Q は 10<sup>14</sup> 回の読み出し/書き込みサイクル、即ちEEPROMに比べ1億倍の書き込みサイクルに対応できます。これらの能力により、CY15B104Q は頻繁で高速書き込みを必要とする不揮発性メモリの用途に理想的なものです。これらの用途例は、書き込み回数を重視するデータ収集から、シリアルフラッシュや EEPROM を使った長い書き込みデータ保持期間に起因してデータを損失する可能性がある厳しい工業用制御まで及びます。

CY15B104Q はハードウェア置き換えができるため、シリアルEEPROM やフラッシュを使用するユーザーに大幅な利点を提供します。CY15B104Q は F-RAM 技術の高速な書き込み性能を生かすため高速の SPI バスを使用します。デバイスは読み出し専用デバイス ID を内蔵します。これにより、ホストはメーカー、製品の容量、製品のリビジョンを判断できます。デバイス仕様は、 $-40^{\circ}$ C  $\sim$  +85 $^{\circ}$ C の産業機器用温度範囲において保証されます。

すべての関連資料の一覧を表示するには、ここをクリックして ください。

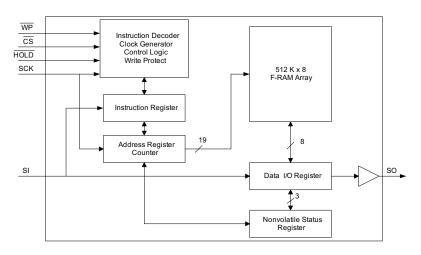

# 論理ブロックダイヤグラム

# 目次

| ピン配置                          | 3  |

|-------------------------------|----|

| ピンの機能                         |    |

| 概要                            | 4  |

| メモリ アーキテクチャ                   |    |

| シリアル ペリフェラル インターフェース (SPI) バス | 4  |

| SPI概要                         | 4  |

| SPIモード                        |    |

| 電源投入時から最初のアクセスまで              | 6  |

| コマンドの構成                       | 6  |

| WREN - 書き込みイネーブル ラッチのセット      | 6  |

| WRDI - 書き込みイネーブル ラッチのリセット     |    |

| ステータス レジスタおよび書き込み保護           | 7  |

| ステータス レジスタ読み出し (RDSR)         | 7  |

| ステータス レジスタ書き込み (WRSR)         | 7  |

| メモリの動作                        | 8  |

| 書き込み動作                        | 8  |

| 読み出し動作                        |    |

| 高速読み出し動作                      | 8  |

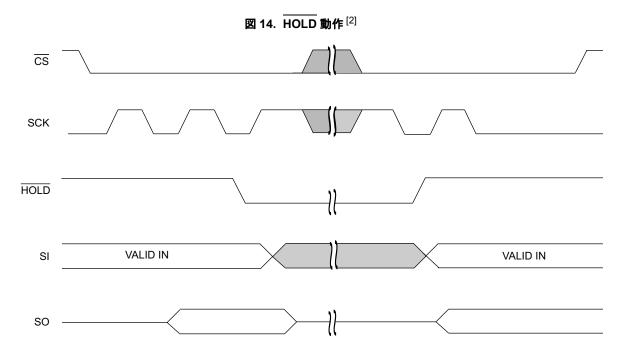

| HOLDピンの動作                     | 10 |

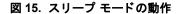

| スリープ モード                      | 10 |

| デバイスID                        |    |

| アクセス可能回数                      |    |

|                               |    |

| 眨人上怕                                  |    |

|---------------------------------------|----|

| 動作範囲                                  | 12 |

| DC電気的特性                               | 12 |

| データ保持期間およびアクセス可能回数                    | 13 |

| 静電容量                                  |    |

| <br>熟抵抗                               |    |

| <br>ACテスト条件                           | 13 |

| ACスイッチング特性                            |    |

| パワー サイクル タイミング                        |    |

| 注文情報                                  |    |

| <br>注文コードの定義                          |    |

| パッケージ図                                |    |

| · · · · · · · · · · · · · · · · · · · |    |

| <br>本書の表記法                            |    |

| 測定単位                                  |    |

| 改訂履歴                                  |    |

| セールス、ソリューションおよび法律情報                   |    |

| ワールドワイドな販売と設計サポート                     |    |

| 製品                                    |    |

| PSoC <sup>®</sup> ソリューション             |    |

| サイプレス開発者コミュニティ                        |    |

| ニカーナル 土土 し                            |    |

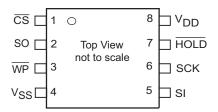

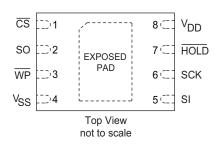

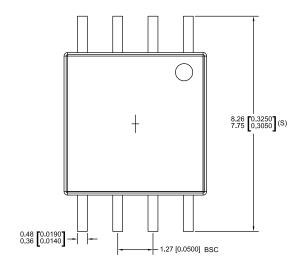

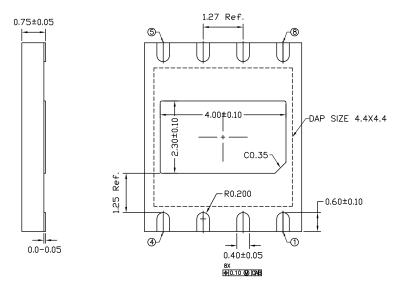

# ピン配置

## 図 1. 8 ピン SOIC ピン配置

図 2. 8ピン TDFN ピン配置

# ピンの機能

| ピン名                             | 入出力<br>タイプ | 説明                                                                                                                                                                                                              |

|---------------------------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <u>CS</u>                       | 入力         | チップ セレクト: このアクティブ LOW 入力でデバイスを起動。HIGH になった場合、デバイスは低消費電力スタンバイ モードに移行し、他の入力を無視し、出力がトライステートにされます。LOW になった場合、デバイスは SCK 信号を内部でアクティブにします。CS の立ち下りエッジは、すべてのオペコードの発行前に発生する必要があります。                                      |

| SCK                             | 入力         | <b>シリアル クロック</b> :入出力はシリアル クロックに同期。入力は立ち上りエッジでラッチされ、出力は立ち下りエッジで発生。同期デバイスであるため、クロック周波数は 0 ~ 40MHz 範囲内であり、いつでも割り込まれる可能性があります。                                                                                     |

| SI <sup>[1]</sup>               | 入力         | シリアル 入力: このピンからデバイスにデータを入力。入力は SCK の立ち上りエッジでサンプリングされ、その時以外では無効。IDD 仕様を満たすため、入力を有効な論理レベルに駆動することが必要です。                                                                                                            |

| SO <sup>[1]</sup>               | 出力         | シリアル出力: これはデータ出力ピン。このピンは読み出し中に駆動。その時以外では HOLD が LOW になる時も含めトライステートのままです。データ遷移はシリアル クロックの立ち下りエッジで実現します。                                                                                                          |

| WP                              | 入力         | <b>書き込み保護</b> : このアクティブ LOW ピンは、WPEN が「1」にセットされた時にステータス レジスタへの書き込み動作を無効。その他の書き込み保護機能はステータス レジスタによって制御されるため、このことは重要。書き込み保護の詳細については、7 ページのステータス レジスタおよび書き込み保護を参照してください。このピンを使用しない場合、V <sub>DD</sub> に接続する必要があります。 |

| HOLD                            | 入力         | HOLD ピン: ホスト CPU が他のタスクのためメモリ動作に割り込む必要がある場合、HOLD ピンを使用。HOLD が LOW になると、現時点の動作が一時停止。デバイスは SCK もしくは CS の遷移を無視。HOLD の遷移は SCK が LOW の間に発生する必要があります。このピンを使用しない場合、V <sub>DD</sub> に接続する必要があります。                       |

| $V_{SS}$                        | 電源         | デバイス グランド。システム グランドに接続する必要があります。                                                                                                                                                                                |

| $V_{DD}$                        | 電源         | デバイスへの電源入力                                                                                                                                                                                                      |

| EXPOSED PAD<br>(エクスポーズド<br>パッド) | 未接続        | 8 ピン TDFN パッケージの EXPOSED PAD はダイに接続されません。EXPOSED PAD は開放にします。                                                                                                                                                   |

ページ 3/22 文書番号: 001-94897 Rev. \*C

**注:**1. SI を SO と接続し 1 ピンのデータ インターフェースとして利用されることがあります。

## 概要

CY15B104Q はシリアル F-RAM メモリです。メモリ アレイは  $524,288 \times 8$  ビットに論理構成され、業界標準のシリアル ペリフェラル インターフェース (SPI) バスを使用してアクセスされます。F-RAM の機能はシリアルフラッシュ、シリアル EEPROM と類似します。同じピン配置の CY15B104Q とシリアル フラッシュや EEPROM の大きな違いは、F-RAM の優れた書き込み性能、高いアクセス可能回数、低消費電力です。

#### メモリ アーキテクチャ

CY15B104Qのアクセスには、512K番地までの(それぞれが8データビット)アドレス指定します。これらの8データビットは順次シフトイン/シフトアウトされます。アドレスは、チップセレクト(バス上で複数デバイスを可能にする用)、オペコードと3バイトのアドレスを含むSPIプロトコルを使ってアクセスされます。アドレス範囲の上位5ビットは「ドントケア」値です。19ビットのアドレスで、一意に各バイトアドレスを指定します。

CY15B104Q の殆どの機能は、SPI インターフェースにより制御されるか、または基板搭載の回路によって処理されます。メモリ動作に対応したアクセス時間は基本的にシリアル プロトコルに必要な時間以外は 0 です。すなわち、メモリは SPI バスの速度で読み書きされます。シリアル フラッシュや EEPROMと異なり、書き込み処理がバス速度で行われるため、デバイスの書き込み準備を知るためにポーリングする必要はありません。新しいバストランザクションがデバイスに送り込まれるまでに書き込み動作は完了します。これはインターフェースの項で詳しく説明されます。

#### シリアル ペリフェラル インターフェース (SPI) バス

CY15B104Q は SPI スレーブ デバイスであり、最速 40MHz で動作します。この高速シリアル バスにより、SPI マスターとの間で高性能のシリアル通信が可能です。多くの一般的なマイクロコントローラーは、ハードウェア SPI ポートを持っているため、直接インターフェースを可能にします。SPI ポートを持たないマイクロコントローラーで、通常のポートを使用して SPI ポートをエミュレートするのは簡単です。CY15B104Q は、SPIモード 0 および 3 で動作します。

## SPI 概要

SPI は、チップ セレクト ( $\overline{CS}$ )、シリアル入力 (SI)、シリアル出力 (SO)、シリアル クロック (SCK) ピンの4ピン インターフェースです。

SPI は、メモリ アクセスにクロックとデータ ピンを使用し、データバス上の複数デバイスをサポートする同期シリアル インターフェースです。SPI バス上のデバイスは、CS ピンを使用してアクティブにされます。

チップ セレクト、クロック、データの相互関係は SPI モードによります。このデバイスは、SPI モード 0 および 3 をサポートします。これらの両モードで、CS がアクティブになった後の最初の立ち上りエッジから始まる SCK の立ち上りエッジで、データが F-RAM にクロック入力されます。

SPI プロトコルはオペコードによって制御されます。これらのオペコードは、バス マスターからスレーブ デバイスへのコマンドを指定します。CS がアクティブにされた後、バス マスターから最初に転送されるバイトがオペコードです。オペコードに続いて、アドレスとデータが転送されます。処理が完了した後、

新しいオペコードが発行される前に、CS を非アクティブにする必要があります。SPI プロトコルで一般的に使用される用語は以下のとおりです。

#### SPI マスター

SPI マスター デバイスは SPI バス上で制御します。SPI バスは、1 つまたは複数のスレーブ デバイスを制御するマスターを 1 つだけ持つことがあります。すべてのスレーブが同じ SPI バス ラインを共有し、マスターは CS ピンを使用してスレーブ デバイスのいずれかを選択できます。 すべての処理は、マスターがスレーブの CS ピンを LOW にプルダウンすることによってスレーブ デバイスをアクティブにして開始する必要があります。マスターは SCK も生成し、SI と SO ライン上のすべてのデータ転送はこのクロックに同期されます。

#### SPIスレーブ

SPI スレーブ デバイスは、チップ セレクト ラインを介してマスターによってアクティブにされます。スレーブ デバイスは、SPI マスターからの入力として SCK を取得し、すべての通信はこのクロックに同期されます。 SPI スレーブが SPI バス上で通信を開始することはなく、単にマスターからの命令に従い実行します。

CY15B104Q は SPI スレーブとして動作し、他の SPI スレーブデバイスと SPI バスを共有する場合があります。

## チップ セレクト (CS)

あらゆ<u>るス</u>レーブ デバイスを選択するためには、マ<u>ス</u>ターは対応する CS ピンをプルダウンする必要があります。CS ピンがLOW の時のみ、命令をスレーブ デバイスに発行できます。デバイスが選択されていない場合、SI ピン経由のデータは無視され、シリアル出力ピン (SO) は高インピーダンス状態のままとなります。

注:新しい命令は CS の立ち下りエッジで開始する必要があります。したがって、アクティブなチップ セレクト サイクルごとに 1 つのオペコードのみが発行できます。

#### シリアル クロック (SCK)

シリアル クロックは SPI マスターによって生成され、 $\overline{CS}$  が LOW になった後、通信がこのクロックと同期されます。

CY15B104Q はデータ通信のために SPI モード 0 と 3 を有効にします。これらの両モードにおいて、入力は SCK の立ち上りエッジでスレーブ デバイスによってラッチされ、出力は立ち下りエッジで発行されます。そのため、SCK の最初の立ち上りエッジは、SIピンに SPI 命令の最初の最上位ビット (MSB) が到着したことを意味します。さらに、すべてのデータの入力と出力は SCK と同期されます。

## データ転送 (SI // SO)

SPI データ バスは、シリアル データ通信用に SI と SO の 2 ラインで構成されます。SI はマスター アウト スレーブ イン (MOSI)、SO はマスター イン スレーブ アウト (MISO) とも呼ばれます。マスターは SI ピンを介してスレーブに命令を発行し、スレーブは SO ピンを介して応答します。複数のスレーブデバイスは、前述のように SI と SO ラインを共有する場合があります。

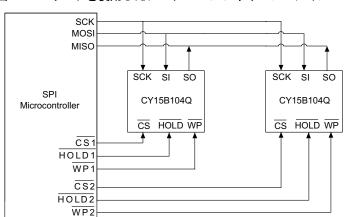

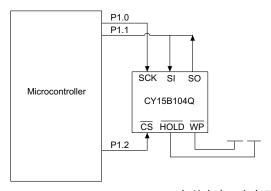

図 3 に示すように、CY15B104Q にはマスターと接続できる SIと SO 用の 2 本の独立したピンがあります。

専用 SPI バスを持たないマイクロコントローラーでは、汎用ポートが使用されることもあります。マイコンのハードウェアリソースを減らすために、2つのデータピン (SI、SO)を1つにまとめて接続し、HOLDピンとWPピンをHIGHに固定接続できます。図4に、マイコンのピンを3本のみ使用しているこのコンフィギュレーションを示します。

#### 最上位ビット (MSB)

SPI プロトコルでは、最初に送信されるビットが最上位ビット (MSB) でなければなりません。この方式はアドレスとデータ転送の両方に適用できます。

4M ビット シリアル F-RAM は、あらゆる読み出しまたは書き込み動作に3バイトのアドレスを必要とします。アドレスは19ビットであるため、入力された最初の5ビットは「ドントケア」ですよって無視されます。これらの5ビットは「ドントケア」ですが、より高容量メモリへの円滑な移行のために、これらを0にセットすることをサイプレスは推奨します。

#### シリアル オペコード

CS が LOW になる状態でスレーブ デバイスが選択された後、最初に受信されたバイトは、意図されている動作用のオペコード として扱われます。CY15B104Q はメモリ アクセスに標準オペコードを使用します。

#### 無効なオペコード

無効なオペコードが受信されるとそのオペコードは無視され、 デバイスは SI ピン上にある追加のシリアル データを CS の次 の立ち下りエッジまで無視し、SO ピンはトライステートのま まです。

#### ステータス レジスタ

CY15B104Qには、8 ビットのステータス レジスタが 1 個あります。ステータス レジスタ内のビットはデバイスをコンフィギュレーションするために使用されます。これらのビットは 7ページの表 3 で説明されます。

図 3. SPI ポートを使用したシステム コンフィギュレーション

図 4. SPI ポートを使用しないシステム コンフィギュレーション

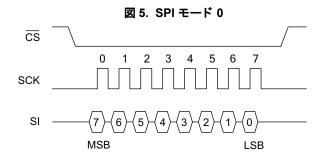

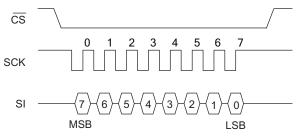

#### SPIモード

CY15B104Q は、SPI ペリフェラルが次の 2 つのモードのいずれかで動作しているマイクロコントローラーによって駆動できます。

- SPI  $\pm$  F 0 (CPOL = 0、CPHA = 0)

- SPI モード 3 (CPOL = 1、CPHA = 1)

この両モードでは、入力データは CS がアクティブになった後の最初の立ち上りエッジから始まる SCK の立ち上りエッジでラッチされます。クロックが HIGH 状態から起動される場合 (モード 3) では、クロック トグル後の最初の立ち上りエッジに

なります。出力データは SCK の立ち下りエッジで利用可能となります。

2 つの SPI モードは図 5 と 6 ページの図 6 に示されます。バスマスターがデータを転送していない時のクロックの状態は以下のとおりです。

- モード 0 では、SCK が 0 のままです。

- モード 3 では、SCK が 1 のままです。

CS ピンを LOW にすることによりデバイスが選択された時、デバイスは SCK ピンの状態から SPI モードを検出します。デバイスが選択された時に、SCK ピンが LOW の場合、デバイスは

SPI モード 0 で動作し、SCK ピンが HIGH の場合、SPI モード 3 で動作します。

図 6. SPI モード 3

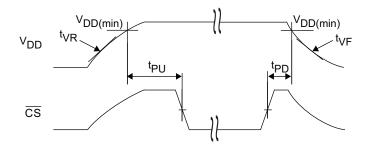

#### 電源投入時から最初のアクセスまで

電源投入後の  $t_{PU}$  の間、CY15B104Q へはアクセスできません。 ユーザーはタイミング パラメーター  $t_{PU}$  ( $V_{DD}$  (min) から CS が初めてLOWになる時までの最短期間)に従わねばなりません。

#### コマンドの構成

バスマスターが CY15B104Q に発行するコマンド (オペコード と呼ばれる) は 9 個あります (表 1 を参照してください)。これらのオペコードはメモリが実行する機能を制御します。

表 1. オペコード コマンド

| 名称    | 説明                 | オペコード      |

|-------|--------------------|------------|

| WREN  | 書き込みイネーブル ラッチのセット  | 0000 0110b |

| WRDI  | 書き込みイネーブル ラッチのリセット | 0000 0100b |

| RDSR  | ステータス レジスタの読み出し    | 0000 0101b |

| WRSR  | ステータス レジスタの書き込み    | 0000 0001b |

| READ  | メモリ データの読み出し       | 0000 0011b |

| FSTRD | メモリ データの高速読み出し     | 0000 1011b |

| WRITE | メモリ データ書き込み        | 0000 0010b |

| SLEEP | スリープ モードへの移行       | 1011 1001b |

| RDID  | デバイス ID の読み出し      | 1001 1111b |

| 予約    | 予約済み               | 1100 0011b |

| 済み    |                    | 1100 0010b |

|       |                    | 0101 1010b |

|       |                    | 0101 1011b |

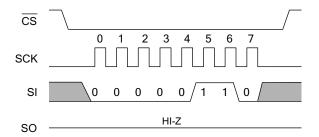

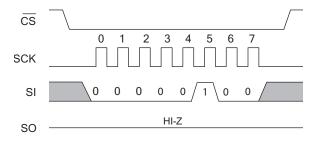

#### WREN - 書き込みイネーブル ラッチのセット

CY15B104Q は、書き込みが無効の状態で電源投入されます。WREN コマンドを書き込み動作の前に発行する必要があります。WREN オペコードを送信することにより、ユーザーは書き込み動作用に次のオペコードを発行できます。これらはステータス レジスタへの書き込み (WRSR) とメモリへの書き込み (WRITE) を含みます。

WREN オペコードを発行すると、内部書き込みイネーブルラッチはセットされます。WEL と呼ばれるステータス レジスタ内のフラグ ビットはラッチの状態を示します。WEL = 「1」は、書き込みが許可されることを示します。ステータス レジスタのWEL ビットに書き込んでもこのビットの状態に影響を与えません。WREN オペコードのみがこのビットをセットできます。WELビットは、WRDI や WRSR、WRITE 動作に続く CS の立ち上りエッジで自動的にクリアされます。これにより、別のWRENコマンドを発行せず、ステータス レジスタまたはF-RAMアレイへの2 重の書き込みを回避できます。図 7 は、WRENコマンドのバス コンフィギュレーションを示します。

図 7. WREN バス コンフィギュレーション

#### WRDI - 書き込みイネーブル ラッチのリセット

WRDI コマンドは、書き込みイネーブル ラッチをクリアすることによりすべての書き込み動作を無効にします。ステータス レジスタ内の WEL ビットを読み出し、WEL ビットが「0」であることを確認することにより、ユーザーは書き込みが無効であることを確認できます。図 8 は、WRDI コマンドのバス コンフィギュレーションを示します。

図 8. WRDI バス コンフィギュレーション

## ステータス レジスタおよび書き込み保護

CY15B104Q の書き込み保護機能は多層的であり、ステータス レジスタを介して有効にされます。ステータス レジスタは以下のように構成されます。(WEL、BP0、BP1、ビット 4  $\sim$  5、WPEN の工場出荷時の初期値は「0」であり、ビット 6 は「1」です)。

#### 表 2. ステータス レジスタ

| ビット7     | ビット 6 | ビット 5 | ビット4  | ビット3    | ビット2    | ビット1    | ビット 0 |

|----------|-------|-------|-------|---------|---------|---------|-------|

| WPEN (0) | X (1) | X (0) | X (0) | BP1 (0) | BP1 (0) | WEL (0) | X (0) |

#### 表 3. ステータス レジスタのビット定義

| ビット             | 定義              | 説明                                                                                                |

|-----------------|-----------------|---------------------------------------------------------------------------------------------------|

| ビット 0           | ドント ケア          | このビットは書き込み不可であり、読み出す時に常に「0」を返します。                                                                 |

| ビット 1 (WEL)     | 書き込みイネーブル       | WEL はデバイスの書き込みが有効かどうかを示します。電源投入時、このビットの初期値は「0」(無効)です。<br>WEL = 「1」> 書き込みが有効<br>WEL = 「0」> 書き込みが無効 |

| ビット 2 (BP0)     | ブロック保護ビット「0」    | ブロック保護に使用。詳細については、表 4 を参照してください。                                                                  |

| ビット 3 (BP1)     | ブロック保護ビット「1」    | ブロック保護に使用。詳細については、表 4 を参照してください。                                                                  |

| ビット4~5          | ドント ケア          | これらのビットは書き込み不可であり、読み出し時に常に「0」を返します。                                                               |

| ビット6            | ドント ケア          | このビットは書き込み不可であり、読み出し時に常に「1」を返します。                                                                 |

| ビット 7<br>(WPEN) | 書き込み保護イネーブル ビット | 書き込み保護ピン ( $\overline{\text{WP}}$ ) の機能を有効にするために使用します。詳細については、表 5 を参照してください。                      |

ビット 0 と 4 ~ 5 は「0」に、ビット 6 は「1」に固定され、これらのビットは修正できません。F-RAM はリアルタイムで書き込まれビジーの時がないため、ビット 0 (シリアル フラッシュや EEPROM での「Ready or Write in progress (待機または書き込み中)」の状態を示すビット)は不要であり、「0」として読み出されます。しかしデバイスがスリープモードから復帰する時は例外です。10 ページのスリープモードを参照してください。BP1 および BP0 はソフトウェアの書き込み保護機能を制御する不揮発性ビットです。WEL フラグは、書き込みイネーブルラッチの状態を示します。ステータス レジスタの WEL ビットに直接書き込んでも状態は変わりません。このビットは内部で WREN、WRDI コマンドを介してそれぞれセットおよびクリアされます。

BP1 と BP0 は、メモリ ブロックの書き込み保護ビットです。 それらは表 4 に示すように書き込み保護されるメモリ領域を指定します。

表 4. ブロック メモリへの書き込み保護

| BP1 | BP0 | 保護されるアドレス範囲                   |  |

|-----|-----|-------------------------------|--|

| 0   | 0   | なし                            |  |

| 0   | 1   | 60000h ~ 7FFFFh (アレイの最上部 1/4) |  |

| 1   | 0   | 40000h ~ 7FFFFh (アレイの最上部 1/2) |  |

| 1   | 1   | 00000h ~ 7FFFFh (アレイ全体)       |  |

BP1 と BP0 ビットと書き込みイネーブル ラッチは、メモリを書き込みから保護する唯一のメカニズムです。残りの書き込み保護機能は、ブロック保護ビットへの不用意な変更を防止します。

ステータス レジスタの書き込み保護  $\underline{/ \lambda}$ ーブル ビット (WPEN) は、ハードウェア書き込み保護 (WP) ピンの効果を制

御します。WPEN ビットが「0」にクリアされると、 $\overline{\text{WP}}$  ピンの状態は無視されます。WPEN ビットが「1」にセットされた時、 $\overline{\text{WP}}$  ピンが LOW になるとステータス レジスタへの書き込みが禁止されます。そのためステータス レジスタは、WPEN = 「1」かつ  $\overline{\text{WP}}$  = 「0」の場合のみ書き込み保護されます。表 5に書き込み保護条件をまとめます。

表 5. 書き込み保護

| WEL | WPEN | WP | 保護<br>ブロック | 非保護<br>ブロック | ステータス<br>レジスタ |

|-----|------|----|------------|-------------|---------------|

| 0   | X    | Χ  | 保護         | 保護          | 保護            |

| 1   | 0    | Х  | 保護         | 非保護         | 非保護           |

| 1   | 1    | 0  | 保護         | 非保護         | 保護            |

| 1   | 1    | 1  | 保護         | 非保護         | 非保護           |

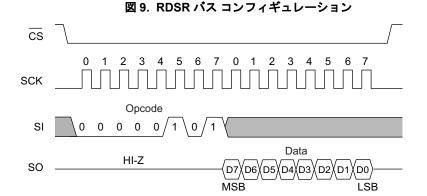

# ステータス レジスタ読み出し (RDSR)

RDSR コマンドでは、バス マスターがステータス レジスタの 内容を検証できます。ステータス レジスタを読み出すことで、書き込み保護機能の現時点の状態に関する情報を得ます。 RDSR オペコードに続いて、CY15B104Q はステータス レジスタの内容を持つ 1 バイトを返します。

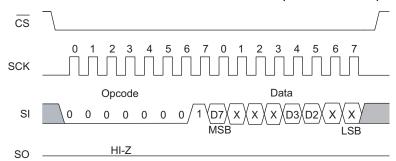

#### ステータス レジスタ書き込み (WRSR)

WRSR コマンドでは、SPIバス マスターがステータス レジス タへ書き込み、WPEN、BP0、BP1 ビットを必要に応じて設定 することで書き込み保護のコンフィギュレーションを変更できます。WRSR コマンドを発行する前には、WP ピンが HIGH または非アクティブである必要があります。CY15B104Q では、WPがメモリアレイではなくステータス レジスタのみへの書き 込みのみを防止することに注意してください。WRSR コマンド

文書番号: 001-94897 Rev. \*C

を送信する前に、書き込みを有効にするため WREN コマンド を送信する必要があります。WRSR コマンドの実行は書き込み 動作に相当するため、書き込みイネーブル ラッチがクリアされます。

図 10. WRSR バス コンフィギュレーション (WREN が非表示 )

## メモリの動作

高いクロック周波数での動作が可能な SPI インターフェースは、F-RAM 技術の高速書き込み機能を際立たせます。シリアルフラッシュや EEPROM と違って、CY15B104Q はバス速度でシーケンシャルに書き込みを実行できます。ページ レジスタは不要であり、シーケンシャルな書き込みは何回でも実行できます。

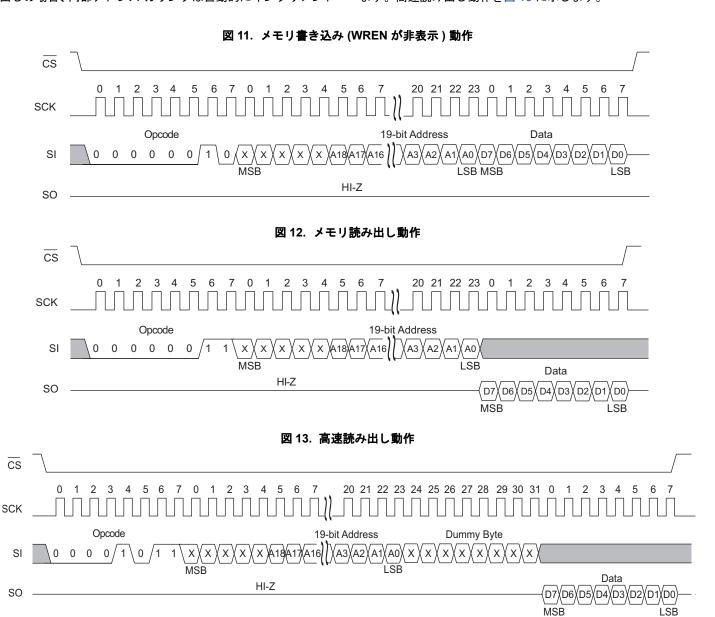

## 書き込み動作

メモリへのすべての書き込みは、アサートおよびデアサートされる CS を伴う WREN オペコードで始まります。次のオペコードは WRITE です。WRITE オペコードの後には、メモリへ書き込む最初のデータ バイトを示す 19 ビット アドレス (A18 ~ A0)の 3 バイト アドレスが続きます。3 バイト アドレスの上位 5 ビットは無視されます。後続のバイトはシーケンシャルに書き込まれるデータ バイトです。バス マスターがクロックを送り、CS を LOW に維持している限り、アドレスは内部でインクリメントされます。7FFFFh の最終アドレスに達すると、カウントは 00000h に戻ります。データは MSB から書き込みます。CS の立ち上りエッジで書き込み動作を終了します。書き込み動作を図 11 に示します。

注:バースト書き込みが保護されたブロックに達すると、アドレスの自動インクリメントは停止し、書き込み用に受信された後続のデータ バイトのすべてがデバイスに無視されます。 EEPROM はページ バッファを使用して書き込みスループットを上げます。ページ バッファは、書き込み動作が遅いという本来の特性を補完するものです。F-RAM メモリは、各データ バイトが (8 番目のクロックの後) クロック入力された直後にF-RAM アレイに書き込まれるため、ページ バッファを持ちま せん。そのため、ページ バッファの遅延なしに何バイトでも書き込めます。

注:書き込み中に電源を喪失すると、最後に完了したバイトの みが書き込まれます。

## 読み出し動作

$\overline{\text{CS}}$  の立ち下りエッジの後に、バスマスターはREADオペコードを発行できます。READコマンドの後に、読み出し動作の最初のバイトを指定する 19 ビット アドレス (A18 ~ A0) の 3 バイトアドレスが続きます。アドレスの上位 5 ビットは無視されます。オペコードとアドレスが発行された後、デバイスは次の 8 クロック サイクルで読み出しデータを出力します。 $\overline{\text{SI}}$  入力は読み出しデータ バイトの出力中には無視されます。後続のバイトは順次に読み出され $\overline{\text{S}}$  データ バイトです。バス マスターがクロックを送り、かつ  $\overline{\text{CS}}$  が LOW である限り、アドレスは内部でインクリメントされます。7FFFFh の最終アドレスに達すると、カウントは 00000h に戻ります。データは MSB から読み出します。 $\overline{\text{CS}}$  の立ち上りエッジで読み出し動作を 図 12 に示します。

## 高速読み出し動作

CY15B104Q は、シリアル フラッシュ デバイスとのコード互換性のために提供される FAST READ オペコード (0Bh) をサポートします。 FAST READ オペコードの後には、読み出し動作の最初のバイトを指定する 19 ビット アドレス (A18  $\sim$  A0) の 3 バイト アドレスが続き、次はダミー バイトとなります。ダミーバイトは 8 クロック サイクルの読み出し遅延を入れます。ダミー バイトを追加することを除き、高速読み出し動作は通常の

読み出し動作と同じです。オペコード、アドレス、ダミー バイトを受信した後、CY15B104Q は SO ライン上で MSB ファースト方式でデータ バイトを出力し始めます。またデバイスが選択されクロックが有効である限り出力を継続します。 バルク読み出しの場合、内部アドレス カウンタは自動的にインクリメント

され、最終アドレス 7FFFFh に達するとカウンターは 00000h に戻ります。デバイスが SO ライン上でデータを出力している時、SI ライン上の遷移は無視されます。 CS の立ち上りエッジで高速読み出し動作を停止し、SO ピンをトライステートにします。高速読み出し動作を図 13 に示します。

文書番号 : 001-94897 Rev. \*C ページ 9/22

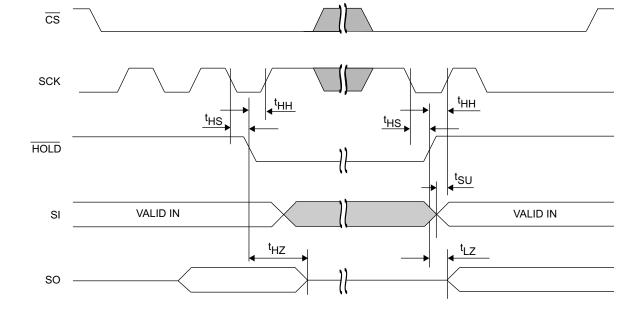

# HOLD ピンの動作

HOLD ピンを使って、連続動作を中断せずそれに割り込め<u>ます。SCK が LOW の間に、バス マスターが HOLD</u> ピンを LOW にすると、その時点の動作は一時停止します。SCK が LOW の間に HOLD ピンを HIGH にすると、動作を再開します。SCK が LOW の間に HOLD の遷移を行う必要がありますが、SCK と  $\overline{\text{CS}}$  ピンはホールド状態中に切り替えられます。

#### スリープ モード

低消費電力スリープモードがCY15B104Qデバイスに実装されています。SLEEP オペコード B9h が入力されて  $\overline{CS}$  が HIGHになると、デバイスは低消費電力モードに移行します。スリープモードになると  $\overline{SCK}$   $\underline{CS}$  SI ピンは無視され、 $\overline{SO}$  は  $\overline{HI-Z}$  になりますが、デバイスは  $\overline{CS}$  ピンの監視を継続します。 $\overline{CS}$  の次

の立ち下りエッジで、デバイスは  $t_{REC}$  以内に通常の動作に復帰します。SO ピンは、ウェイクアップ期間中は HI-Z 状態のままです。デバイスは、ウェイクアップ期間内でオペコードに応答する必要はありません。ウェイクアップの手順を開始するために、コントローラーが、例えば「ダミー」の読み出しを送信し、残りの  $t_{REC}$  時間で待機することもあります。

#### 注:

-----2. 図 14 に、入力モードと出力モードでの HOLD 動作を示します。

文書番号 : 001-94897 Rev. \*C ページ 10/22

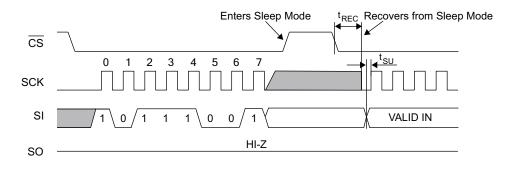

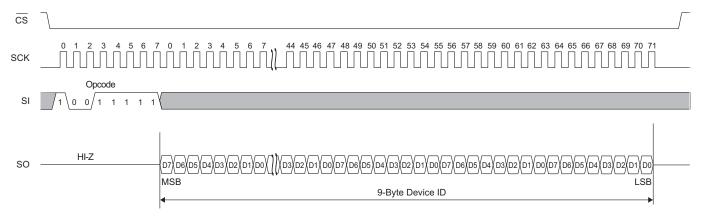

#### デバイス ID

CY15B104Q デバイスは、メーカー、製品 ID、ダイ リビジョンについて問い合わせを行えます。RDID オペコード 9Fh は、両方とも読み出し専用バイトのメーカー ID と製品 ID を読むことができます。JEDEC から割り当てられたメーカー ID は、バンク 7 の中にサイプレス (Ramtron) の識別子を配置します。そのため、6 バイトの連続コード 7Fh があり、その後に 1 バイトの C2h が続きます。製品 ID の 2 バイトはファミリ コードと容量コード、サブ コード、および製品リビジョン コードを含みます。

表 6. デバイス ID

|                    | デバイス ID の説明                                  |                    |                  |               |               |               |

|--------------------|----------------------------------------------|--------------------|------------------|---------------|---------------|---------------|

| デバイス ID            | 71 ~ 16<br>(56 ビット )                         | 15 ~ 13<br>(3 ビット) | 12~8<br>(5ビット)   | 7~6<br>(2ビット) | 5~3<br>(3ビット) | 2~0<br>(3ビット) |

| (9 バイト )           |                                              | 製品 ID              |                  |               |               |               |

|                    | メーカー ID                                      | ファミリ<br>コード        | <b>全国</b><br>イーロ | サブ<br>コード     | リビジョン<br>コード  | 予約済み          |

| 7F7F7F7F7F7C22608h | 01111111011111110111111110111<br>11110111111 | 001                | 00110            | 00            | 001           | 000           |

図 16. デバイス ID の読み出し

## アクセス可能回数

CY15B104Q デバイスには 10<sup>14</sup> 回以上、読み書きを問わずアクセスできます。F-RAM メモリは読み出しと書き戻しメカニズムを伴い動作します。そのため、メモリアレイへのアクセス (読み出し/書き込み)に対して、アクセスサイクルが行単位で適用されます。F-RAM のアーキテクチャは、64 ビットの列と 32K の行からなるアレイを基にします。読み出しまたは書き込みは行単位に行われます。1 行内のデータのアクセスバイト数に関わらず内部的に行に対するアクセスは1回です。行内の各バイトは、アクセス可能回数の計算では1回のみカウントされます。表7は、オペコード、開始アドレス、および連続する 64 バイト データの流れを含む、64 バイトの繰り返しループによって各バイトが1回のアクセス回数を費やしたことになります。F-RAM の

読み出しと書き込み可能回数は、40MHz のクロック速度でも事 実上無制限です。

表 7. 64 バイト ループの繰り返しでアクセス可能回数が限界に 達する期間

| SCK 周波数<br>(MHz) | アクセス可能<br>回数<br>(サイクル/秒) | アクセス可能<br>回数<br>(サイクル/年) | 限界到達年数 |

|------------------|--------------------------|--------------------------|--------|

| 40               | 73,520                   | 2.32×10 <sup>12</sup>    | 43.1   |

| 10               | 18,380                   | 5.79×10 <sup>11</sup>    | 172.7  |

| 5                | 9,190                    | 2.90×10 <sup>11</sup>    | 345.4  |

文書番号 : 001-94897 Rev. \*C ページ 11/22

# 最大定格

| パッケージ許容電力損失 (T <sub>A</sub> = 25°C)        | 1.0W    |

|--------------------------------------------|---------|

| 表面実装ハンダ付け温度 (3 秒)                          | +260°C  |

| DC 出力電流 (出力 1 本当り、1 秒間)                    | 15mA    |

| 静電気の放電電圧<br>人体モデル (JEDEC 準拠 JESD22-A114-B) | 2kV     |

| 帯電デバイス モデル (JEDEC 準拠 JESD22-C101-A)        | 500V    |

| ラッチアップ電流                                   | .>140mA |

## 動作範囲

| 範囲     | 周囲温度 (T <sub>A</sub> ) | $V_{DD}$    |

|--------|------------------------|-------------|

| 産業機器向け | –40°C <b>~</b> +85°C   | 2.0V ~ 3.6V |

# DC 電気的特性

## 動作範囲において

| パラメーター           | 説明                      | テスト条件                                               |                         | Min                  | <b>Typ</b> <sup>[3]</sup> | Max                   | 単位 |

|------------------|-------------------------|-----------------------------------------------------|-------------------------|----------------------|---------------------------|-----------------------|----|

| $V_{DD}$         | 電源                      |                                                     |                         | 2.0                  | 3.3                       | 3.6                   | V  |

| I <sub>DD</sub>  | V <sub>DD</sub> 電源電流    | SCK は V <sub>DD</sub> -0.2V と V <sub>SS</sub> 間     | f <sub>SCK</sub> =1MHz  | _                    | 0.13                      | 0.30                  | mA |

|                  |                         | でトグル。他の入力は $V_{SS}$ または $V_{DD}$ - 0.2V を印加。 SO= 開放 | f <sub>SCK</sub> =40MHz | _                    | 1.4                       | 3                     | mA |

| I <sub>SB</sub>  | V <sub>DD</sub> スタンバイ電流 | CS = V <sub>DD</sub> 。他のすべての入                       | T <sub>A</sub> =25°C    | -                    | 100                       | 150                   | μΑ |

|                  |                         | 力は V <sub>SS</sub> または V <sub>DD</sub> を印加          | T <sub>A</sub> =85°C    | -                    | _                         | 250                   | μΑ |

| I <sub>ZZ</sub>  | スリープ モード電流              | <br>CS=V <sub>DD</sub> 。他のすべての入力                    | T <sub>A</sub> =25°C    | -                    | 3                         | 5                     | μΑ |

|                  |                         | は V <sub>SS</sub> または V <sub>DD</sub> を印加           | T <sub>A</sub> =85°C    | -                    | _                         | 8                     | μΑ |

| ILI              | 入力リーク電流                 | $V_{SS} \le V_{IN} \le V_{DD}$                      |                         | _                    | _                         | ±1                    | μΑ |

| I <sub>LO</sub>  | 出カリーク電流                 | $V_{SS} \le V_{OUT} \le V_{DD}$                     |                         | _                    | -                         | ±1                    | μА |

| V <sub>IH</sub>  | 入力 HIGH 電圧              |                                                     |                         | 0.7×V <sub>DD</sub>  | -                         | V <sub>DD</sub> +0.3  | V  |

| $V_{IL}$         | 入力 LOW 電圧               |                                                     |                         | - 0.3                | _                         | 0.3 × V <sub>DD</sub> | V  |

| V <sub>OH1</sub> | 出力 HIGH 電圧              | I <sub>OH</sub> =-1mA、V <sub>DD</sub> =2.7V         |                         | 2.4                  | -                         | -                     | V  |

| V <sub>OH2</sub> | 出力 HIGH 電圧              | I <sub>OH</sub> =–100μA                             |                         | V <sub>DD</sub> -0.2 | _                         |                       | V  |

| V <sub>OL1</sub> | 出力 LOW 電圧               | I <sub>OL</sub> =2mA、V <sub>DD</sub> =2.7V          |                         | _                    | _                         | 0.4                   | V  |

| V <sub>OL2</sub> | 出力 LOW 電圧               | I <sub>OL</sub> =150μA                              |                         | _                    | _                         | 0.2                   | V  |

#### 注:

3. 標準値は 25°C、V<sub>DD</sub>=V<sub>DD (Typ)</sub> の場合です。100% はテストされません。

文書番号: 001-94897 Rev. \*C ページ 12/22

# データ保持期間およびアクセス可能回数

| パラメーター   | 説明       | テスト条件                | Min              | Max | 単位   |

|----------|----------|----------------------|------------------|-----|------|

| $T_{DR}$ | データ保持期間  | T <sub>A</sub> =85°C | 10               | _   | 年    |

|          |          | T <sub>A</sub> =75°C | 38               | _   |      |

|          |          | T <sub>A</sub> =65°C | 151              | _   |      |

| $NV_C$   | アクセス可能回数 | 動作温度範囲内              | 10 <sup>14</sup> | 1   | サイクル |

# 静電容量

| パラメーター[4]      | 説明            | テスト条件                                                              | Max | 単位 |

|----------------|---------------|--------------------------------------------------------------------|-----|----|

| C <sub>O</sub> | 出カピン静電容量 (SO) | T <sub>A</sub> =25°C、f=1MHz、V <sub>DD</sub> =V <sub>DD</sub> (typ) | 8   | pF |

| C <sub>I</sub> | 入力ピン静電容量      |                                                                    | 6   | pF |

# 熱抵抗

| パラメーター        | 説明                | テスト条件                                         | 8ピン SOIC | 8ピンTDFN | 単位   |

|---------------|-------------------|-----------------------------------------------|----------|---------|------|

| $\Theta_{JA}$ |                   | テスト条件は、EIA/JESD51 に準拠する<br>熱インピーダンスを測定するための標準 |          | 30      | °C/W |

| $\Theta_{JC}$ | 熱抵抗<br>(接合部からケース) | 試験方法と手順に従います。<br>                             | 52       | 26      | °C/W |

# AC テスト条件

| 入力パルス レベル      | V <sub>DD</sub> の 10% および 90% |

|----------------|-------------------------------|

| 入力の立ち上りと立ち下り時間 | ∄3ns                          |

| 入力と出力タイミングの基準レ | バル0.5×V <sub>DD</sub>         |

| 出力負荷容量         | 30pF                          |

注: 4. このパラメーターは定期的にサンプリングされ 100% はテストされません。

文書番号: 001-94897 Rev. \*C ページ 13/22

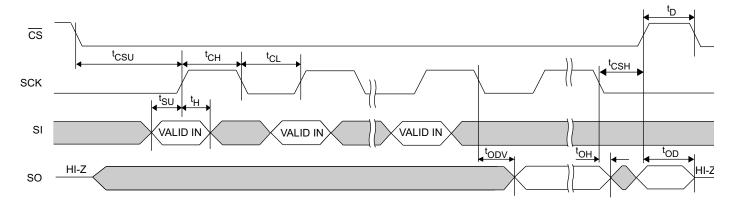

# AC スイッチング特性

## 動作範囲において

| パラメーター <sup>[5]</sup>            |                   |                         | V <sub>DD</sub> =2.0 | √ ~ 3.6V | V <sub>DD</sub> =2.7\ | ∕ ~ 3.6V |     |

|----------------------------------|-------------------|-------------------------|----------------------|----------|-----------------------|----------|-----|

| サイプレス<br>パラメーター                  | 他社の<br>パラメーター     | 説明                      | Min                  | Max      | Min                   | Max      | 単位  |

| f <sub>SCK</sub>                 | _                 | SCK クロック周波数             | 0                    | 25       | 0                     | 40       | MHz |

| t <sub>CH</sub>                  | _                 | クロック HIGH 時間            | 18                   | -        | 11                    | -        | ns  |

| t <sub>CL</sub>                  | _                 | クロック LOW 時間             | 18                   | -        | 11                    | -        | ns  |

| t <sub>CSU</sub>                 | t <sub>CSS</sub>  | チップ セレクトのセットアップ時間       | 12                   | _        | 10                    | _        | ns  |

| t <sub>CSH</sub>                 | t <sub>CSH</sub>  | チップ セレクト ホールド時間         | 12                   | -        | 10                    | _        | ns  |

| t <sub>OD</sub> <sup>[6、7]</sup> | t <sub>HZCS</sub> | 出力ディセーブル時間              | _                    | 20       | _                     | 12       | ns  |

| t <sub>ODV</sub>                 | t <sub>CO</sub>   | 出力データ有効時間               | _                    | 16       | _                     | 9        | ns  |

| t <sub>OH</sub>                  | _                 | 出力ホールド時間                | 0                    | -        | 0                     | _        | ns  |

| t <sub>D</sub>                   | _                 | 選択解除時間                  | 60                   | _        | 40                    | _        | ns  |

| t <sub>R</sub> [7、8]             | _                 | データ入力立ち上り時間             | _                    | 50       | _                     | 50       | ns  |

| t <sub>F</sub> <sup>[7、8]</sup>  | _                 | データ入力立ち下り時間             | _                    | 50       | _                     | 50       | ns  |

| t <sub>SU</sub>                  | t <sub>SD</sub>   | データ セットアップ時間            | 8                    | _        | 5                     | _        | ns  |

| t <sub>H</sub>                   | t <sub>HD</sub>   | データ ホールド 時間             | 8                    | _        | 5                     | _        | ns  |

| t <sub>HS</sub>                  | t <sub>SH</sub>   | HOLD セットアップ時間           | 12                   | -        | 10                    | _        | ns  |

| t <sub>HH</sub>                  | t <sub>HH</sub>   | HOLD ホールド時間             | 12                   | -        | 10                    | _        | ns  |

| t <sub>HZ</sub> [6、7]            | t <sub>HHZ</sub>  | HOLD LOW から HI-Z まで     | _                    | 25       | ı                     | 20       | ns  |

| t <sub>LZ</sub> <sup>[7]</sup>   | t <sub>HLZ</sub>  | HOLD HIGH からデータ アクティブまで | _                    | 25       | _                     | 20       | ns  |

文書番号: 001-94897 Rev. \*C ページ 14/22

<sup>5. 13</sup> ページの AC テスト条件に示すように、テスト条件では、3ns 以下の信号遷移時間、0.5×V<sub>DD</sub> のタイミング リファレンス レベル、V<sub>DD</sub> の 10% ~ 90% の入 カパルス レベル、指定の I<sub>OL</sub>/I<sub>OH</sub> の出力負荷、30pF の負荷容量を前提にします。 6. t<sub>OD</sub> および t<sub>HZ</sub> は、5pF の負荷容量で規定されます。出力が高インピーダンス状態に入る時に、遷移が測定されます。

<sup>7.</sup> 特性付けされていますが、すべてのデバイスでテストはされません。

<sup>8.</sup> 立ち上りと立ち下り時間は波形の 10% と 90% の間で測定されます。

# 図 17. 同期データ タイミング (モード 0)

図 18. HOLD タイミング

文書番号 : 001-94897 Rev. \*C

# パワー サイクル タイミング

# 動作範囲において

| パラメーター                           | 説明                                                              | Min | Max | 単位   |

|----------------------------------|-----------------------------------------------------------------|-----|-----|------|

| t <sub>PU</sub>                  | 電源投入時 (V <sub>DD</sub> (min)) から最初のアクセス ( <del>CS</del> LOW) まで | 1   | 1   | ms   |

| t <sub>PD</sub>                  | 最後のアクセス (CS HIGH) から電源切断 (V <sub>DD</sub> (min)) 時まで            | 0   | _   | μs   |

| t <sub>VR</sub> <sup>[9]</sup>   | V <sub>DD</sub> 電源投入時のランプ レート                                   | 50  | _   | μs/V |

| t <sub>VF</sub> <sup>[9]</sup>   | V <sub>DD</sub> 電源切断時のランプ レート                                   |     | _   | μs/V |

| t <sub>REC</sub> <sup>[10]</sup> | スリープ モードからの復帰時間                                                 | _   | 450 | μs   |

# 図 19. パワー サイクル タイミング

文書番号: 001-94897 Rev. \*C

注:

9. V<sub>DD</sub> 波形上の任意の点で測定したスロープです。

10. 設計保証です。スリープ モードからの復帰タイミングについては、図 15 を参照してください。

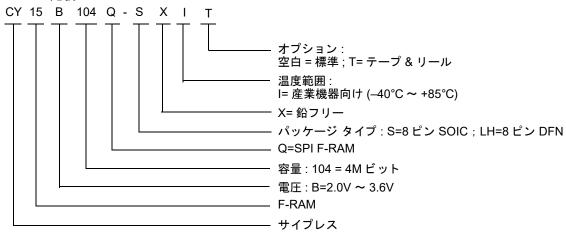

# 注文情報

| 注文コード           | パッケージ図    | パッケージ タイプ | 動作範囲   |

|-----------------|-----------|-----------|--------|

| CY15B104Q-SXI   | 001-85261 | 8ピン SOIC  |        |

| CY15B104Q-SXIT  | 001-85261 | 8ピン SOIC  | ᆂᄴᄴᄜᄼᇿ |

| CY15B104Q-LHXI  | 001-85579 | 8ピンTDFN   | 産業機器向け |

| CY15B104Q-LHXIT | 001-85579 | 8ピンTDFN   |        |

これらすべてのデバイスは鉛フリーです。在庫状況については、最寄りのサイプレスの販売代理店にお問い合わせください。

# 注文コードの定義

文書番号: 001-94897 Rev. \*C ページ 17/22

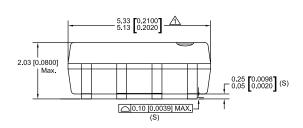

# パッケージ図

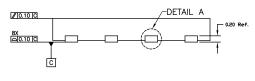

# 図 20. 8ピン SOIC (208mil) パッケージ外形図、001-85261

#### NOTE:

- ⚠ DOES NO INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS.

MOLD FLASH, PROTRUSIONS AND GATE BURRS SHALL NOT

EXCEED 0.006 INCH PER SIDE

- DOES NOT INCLUDE INTER-LEAD FLASH OR PROTRUSIONS. INTER-LEAD FLASH AND PROTRUSION SHALL NOT EXCEED 0.010 INCH PER SIDE.

- 3. THIS PART IS COMPLIANT WITH EIAJ SPECIFICATION EDR-7320  $\,$

- 4. LEAD SPAN/STAND OF HEIGHT/COPLANARITY ARE CONSIDERED AS SPECIAL CHARACTER.

- 5. CONTROLLING DIMENSIONS IN MM. [INCH]

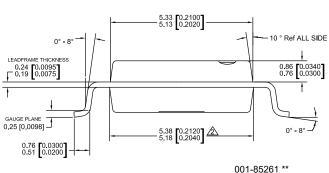

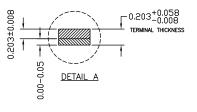

# パッケージ図(続き)

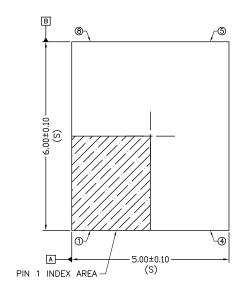

## 図 21. 8ピン DFN (5mm×6mm×0.75mm) パッケージ外形図、001-85579

- NOTE:

1. ALL DIMENSION ARE IN mm. ANGLES IN DEGREES.

2. COPLANARITY APPLIES TO THE EXPOSED PAD AS WELL AS THE TERMINALS.

COPLANARITY SHALL NOT EXCEED 0.08mm.

3. WARPAGE SHALL NOT EXCEED 0.10mm.

4. PACKAGE LENGTH / PACKAGE WIDTH ARE CONSIDERED AS SPECIAL CHARACTERISTICS.(S)

5. REFER TO JEDEC MO-229.

6. FRAME STOCK# FL0106 (Ag Ring Plate), UTL PKG CODE TD56006008A OR TD50016000008A

OR TD50016000008A OR TD50016006008A OR TD5001600G008A.

7. L/F STOCK# FR0221 (Ag Ring), UTL PKG CODE TD500600G008A OR TD500800G008A

OR TD500M600G008A OR TD500D600G008A.

001-85579 \*A

# 略語

| 略語     | 説明                                                                                 |

|--------|------------------------------------------------------------------------------------|

| СРНА   | Clock Phase ( クロック位相 )                                                             |

| CPOL   | Clock Polarity (クロック極性)                                                            |

| EEPROM | Electrically Erasable Programmable Read-Only<br>Memory(電気的消去プログラム可能な読み出し<br>専用メモリ) |

| EIA    | Electronic Industries Alliance (米国電子工業会)                                           |

| F-RAM  | Ferroelectric Random Access Memory<br>(強誘電体ランダム アクセス メモリ)                          |

| I/O    | Input/Output (入力/出力)                                                               |

| JEDEC  | Joint Electron Devices Engineering Council<br>(半導体技術協会)                            |

| JESD   | JEDEC 準拠                                                                           |

| LSB    | Least Significant Bit (最下位ビット)                                                     |

| MSB    | Most Significant Bit ( 最上位ビット )                                                    |

| RoHS   | Restriction of Hazardous Substances<br>(特定有害物質使用制限指令)                              |

| SPI    | Serial Peripheral Interface                                                        |

|        | (シリアル ペリフェラル インターフェース)                                                             |

| SOIC   | Small Outline Integrated Circuit<br>(小型外形集積回路)                                     |

| TDFN   | Thin Dual Flat No-lead<br>(薄型デュアル フラット ノーリード)                                      |

# 本書の表記法

# 測定単位

| 記号   | 測定単位     |

|------|----------|

| °C   | 摄氏温度     |

| Hz   | ヘルツ      |

| kHz  | キロヘルツ    |

| kΩ   | キロオーム    |

| Mbit | メガビット    |

| MHz  | メガヘルツ    |

| μΑ   | マイクロアンペア |

| μF   | マイクロファラド |

| μs   | マイクロ秒    |

| mA   | ミリアンペア   |

| ms   | ミリ秒      |

| ns   | ナノ秒      |

| Ω    | オーム      |

| %    | パーセント    |

| pF   | ピコファラド   |

| V    | ボルト      |

| W    | ワット      |

文書番号: 001-94897 Rev. \*C ページ 20/22

# 改訂履歴

| 文書名 : CY15B104Q、4M ビット (512K×8) シリアル (SPI) F-RAM<br>文書番号 : 001-94897 |         |            |                                                          |  |  |  |

|----------------------------------------------------------------------|---------|------------|----------------------------------------------------------|--|--|--|

| 版                                                                    | ECN 番号  | 発行日        | 変更内容                                                     |  |  |  |

| **                                                                   | 4564213 | 11/13/2014 | これは英語版 001-94240 Rev. ** を翻訳した日本語版 001-94897 Rev. ** です。 |  |  |  |

| *A                                                                   | 4699882 | 03/26/2015 | これは英語版 001-94240 Rev. *B を翻訳した日本語版 001-94897 Rev. *A です。 |  |  |  |

| *B                                                                   | 4959436 | 10/16/2015 | これは英語版 001-94240 Rev. *C を翻訳した日本語版 001-94897 Rev. *B です。 |  |  |  |

| *C                                                                   | 6911971 | 07/07/2020 | これは英語版 001-94240 Rev. *E を翻訳した日本語版 001-94897 Rev. *C です。 |  |  |  |

文書番号: 001-94897 Rev. \*C ページ 21/22

# セールス、ソリューションおよび法律情報

### ワールドワイドな販売と設計サポート

サイプレスは、事業所、ソリューション センター、メーカー代理店、および販売代理店の世界的なネットワークを保持しています。お客様の最寄りのオフィスについては、サイプレスのロケーション ページをご覧ください。

## 製品

Arm® Cortex® Microcontrollers cypress.com/arm 車載用 cypress.com/automotive クロック&バッファ cypress.com/clocks インターフェース cypress.com/interface loT(モノのインターネット) cypress.com/iot メモリ cypress.com/memory マイクロコントローラ cypress.com/mcu **PSoC** cypress.com/psoc 電源用 IC cypress.com/pmic タッチ センシング cypress.com/touch USB コントローラー cypress.com/usb ワイヤレス cypress.com/wireless

## PSoC® ソリューション

PSoC 1 | PSoC 3 | PSoC 4 | PSoC 5LP | PSoC 6 MCU

## サイプレス開発者コミュニティ

コミュニティ | サンプルコード | Projects | ビデオ | ブログ | トレーニング | Components

## テクニカル サポート

cypress.com/support

© Cypress Semiconductor Corporation、2014-2020. 本書面は、Cypress Semiconductor Corporation 及び Spansion LLC を含むその子会社(以下「Cypress」という。) に帰属する財産である。本書面(本書面に含まれ又は言及されているあらゆるソフトウェア苦しくはファームウェア(以下「本ソフトウェア」という。)を含む)は、アメリカ合衆国及び世界のその他の国における知的財産法令及び条約に基づき Cypress が所有する。Cypress はこれらの法令及び条約に基づく全ての権利を留保し、本段落で特に記載されているものを除き、その特許権、著作権、商標権又はその他の知的財産権のライセンスを一切許諾しない。本ソフトウェアにライセンス契約書が伴っておらず、かつ Cypress との間で別途本ソフトウェアの使用方法を定める書面による合意がない場合、Cypress は、(1) 本ソフトウェアの著作権に基づき、(a) ソースコード形式で提供されている本ソフトウェアについて、Cypress ハードウェア製品と共に用いるためにのみ、かつ組織内部でのみ、本ソフトウェアの修正及び複製を行うこと、並びに(b) Cypress のハードウェア製品ユニットに用いるためにのみ、(直接又は再販売者及び販売代理店を介して間接のいずれかで)本ソフトウェアをバイナリーコード形式で外部エンドユーザーに配布すること、並びに(2) 本ソフトウェア(Cypress により提供され、修正がなされていないもの)が抵触する Cypress の特許権のクレームに基づき、Cypress ハードウェア製品と共に用いるためにのみ、本ソフトウェアの作成、利用、配合なが納入を行うことについての非独占的で譲渡不能な一身専属的ライセンス(サブライセンスの権利を除く)を付与する。本ソフトウェアのその他の使用、複製、修正、変換又はコンパイルを禁止する。

適用される法律により許される範囲内で、Cypress は、本書面又はいかなる本ソフトウェア若しくはこれに伴うハードウェアに関しても、明示又は黙示をとわず、いかなる保証(商品性及び特定の目的への適合性の黙示の保証を含むがこれらに限られない)も行わない。いかなるマンピューティングデバイスも絶対に安全ということはない。従って、Cypress のハードウェアまたはソフトウェア製品に議じられたセキュリティ対策にもかかわらず、Cypress は、Cypress 製品への権限のないアクセスままには使用といったセキュリティ違反から生じる一切の責任を負わない。加えて、本書面に記載された製品には、エラッタと呼ばれる設計上の欠陥またはエラーが含まれている可能性があり、公表された仕様とは異なる動作をする場合がある。適用される法律により許される範囲内で、Cypress は、別途通知することなく、本書面を変更する権利を習保する。Cypress は、本書面に記載のある、いかなる製品若しくは回路の適用又は使用から生じる一切の責任を負わない。本書面で提供されたあらゆる情報(あらゆるサンブルデザイン情報又はプログラムコードを含む)は、参照目的のためのみに提供されたものである。この情報で構成するあらゆるアプリケーション及びその結果としてのあらゆる製品の機能性及び安全性を適切に設計、プログラム、かつテストすることは、本書面のユーザーの責任において行われるものとする。Cypress 製品は、兵器、兵器システム、原子力施設、生命維持装置若しくは生命維持システム、募集用の設備及び外科的移植を含むその他の医療機器若しくは医療システム、汚染管理若しくは有害物質管理の運用のために設計され若しくは意図されたシステムの重要な構成部分としての使用、又は装置若しくはシステムの不具合が人身傷害、死亡若しくは物的損害を生じさせるようなその他の使用(以下、本目的外使用)という。)のためには設計、意図又は承認されていない。重要な構成部分とは、それの不具合が装置若しくはシステムの不具合を生じさせるか又はその安全性若しくは実効性に影響すると合理的に予想できるような装置若しくはシステムのあらゆる構成部分をいう。Cypress 製品のあらゆる本目的外使用から生じ、若しくは本目的外使用に関連するいかなる請求、損害又はその他の責任についても、Cypress はその全部又は一部をとわず一切の責任を負わず、かつ Cypress はそれら一切かを本書により免除される。Cypress は Cypress 製品の本目的外使用に関連するあらゆる請求、費用、損害及びその他の責任(人身傷害又は死亡に基づく請求を含む)から免責・確償される。

Cypress, Cypress のロゴ, Spansion, Spansion のロゴ及びこれらの組み合わせ, WICED, PSoC, CapSense, EZ-USB, F-RAM, 及び Traveo は, 米国及びその他の国における Cypress の商標又は登録商標である。Cypress のより完全な商標のリストは, cypress.com を参照すること。その他の名称及びブランドは, それぞれの権利者の財産として権利主張がなされている可能性がある。

文書番号 : 001-94897 Rev. \*C 改訂日 2020 年 7 月 7 日 ページ 22/22