## **MPQ7225A**

# 16-Channel, Current Sink LED Driver with Adaptive Feedback Control (AFC), AEC-Q100 Qualified

### DESCRIPTION

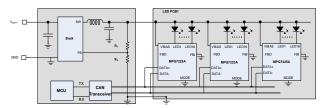

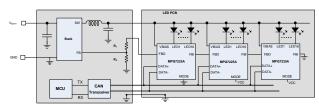

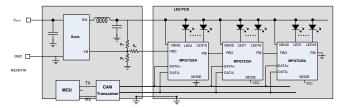

The MPQ7225A is a 16-channel, current sink LED driver. Each channel is rated for up to 200mA of current, and 16 ICs can be cascaded together to create a 256-channel solution.

The MPQ7225A is optimized for animated or dynamic lighting applications. It employs 12-bit pulse-width modulation (PWM) dimming and 6-bit analog dimming register per channel, with individual control of each channel. The MPQ7225A is designed to function across distanced PCBs with a robust, high-speed, CANcompatible differential interface.

The MPQ7225A features adaptive feedback control (AFC) to maximize system efficiency. The output voltage of the pre-regulator (e.g. buck voltage regulator) is adjusted in real time so that the voltage across the channels is kept to a minimum (300mV headroom at 200mA).

Frequency spread spectrum (FSS) optimizes EMC performance. The LED current's ramping rate and the phase shift between channels can be digitally configured as well.

The MPQ7225A can aid a system design for functional safety with failsafe (/FS) indicator. It also features an enhanced LED open/short protection scheme (hiccup and latch modes). Additional protection features include ISET pin open/short protection and thermal shutdown. If a fault condition occurs, then the fault indicator pulls low and the matching fault register is set.

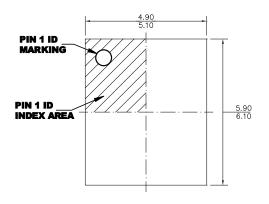

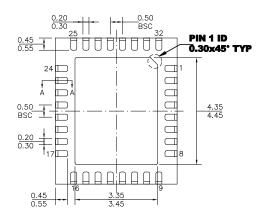

The MPQ7225A is available in a QFN-32 (5mmx6mm) package, and is AEC-Q100 qualified.

### **FEATURES**

- Scalability:

- o 16 Channels, 200mA (Max) per Channel

- o Cascade Up to 16 ICs /256 Channels

- o Pin-Configurable Device Address

- Designed for Automotive Applications:

- Supports Up to 2.5V Cold Crank

- -40°C to +150°C Operating Junction Temperature (T<sub>J</sub>)

### FEATURES (continued)

- Cooler Thermals and Optimized Efficiency:

- Adaptive Feedback Control (AFC)

Dynamically Optimizes Pre-Regulator

Output (300mV Headroom at 200mA)

- Headroom Optimization for Multiple ICs

- Robust Communication:

- 2Mbps CAN Compatible Differential Interface

- 12-Bit Pulse-Width Modulation (PWM)

Dimming or 6-Bit Analog Dimming for Each Channel

- Optimized EMI/EMC:

- Configurable Phase Shift and Slew Rate

- Frequency Spread Spectrum (FSS) (Internal Clock)

- Selectable PWM Dimming Frequency

- CISPR25 Class 5 Compliant

- Additional Features:

- Functional Safety Document Available to Support System in Achieving ASIL Requirements

- Failsafe (/FS) Pin and Fault Registers for System Protection and Diagnostics

- LED Short (to GND and Battery)

- LED Open

- Thermal Warning and Shutdown

- ISET Pin Open/Short

- One-Time Programmable (OTP) Memory

- Available in a QFN-32 (5mmx6mm) Package with Wettable Flanks

- Available in AEC-Q100 Grade 1

### **APPLICATIONS**

- Dynamic/Animated Tail Lights

- Adaptive Matrix Headlights

- Daytime Running Lights (DRLs)

- Turn Signals

- Puddle Lights

All MPS parts are lead-free, halogen-free, and adhere to the RoHS directive. For MPS green status, please visit the MPS website under Quality Assurance. "MPS", the MPS logo, and "Simple, Easy Solutions" are trademarks of Monolithic Power Systems, Inc. or its subsidiaries.

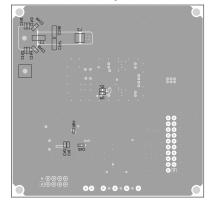

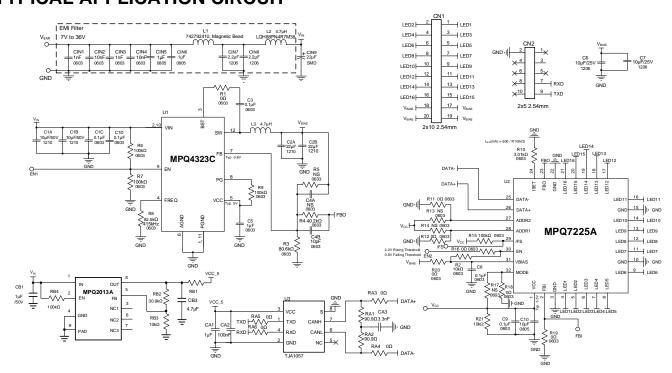

## TYPICAL APPLICATION

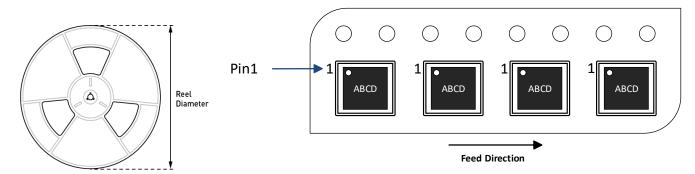

### ORDERING INFORMATION

| Part Number*                       | Package          | Top Marking | MSL Rating** |

|------------------------------------|------------------|-------------|--------------|

| MPQ7225AGQJE-xxxx-<br>AEC1***,**** | QFN-32 (5mmx6mm) | See Below   | 2            |

<sup>\*</sup> For Tape & Reel, add suffix -Z (e.g. MPQ7225AGQJE-xxxx-AEC1-Z).

\*\*\*\*Wettable flank

TOP MARKING

MPSYYWW

MP7225A

LLLLLLL

E

MPS: MPS prefix YY: Year code WW: Week code MP7225A: Part number LLLLLL: Lot number E: Wettable flank

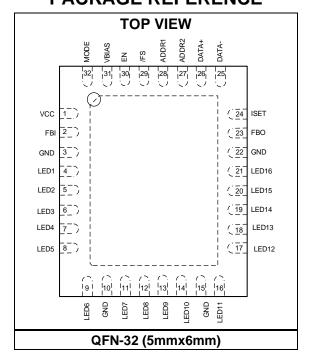

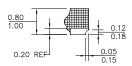

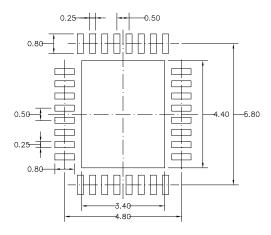

## **PACKAGE REFERENCE**

<sup>\*\*</sup> Moisture Sensitivity Level Rating

<sup>\*\*\* &</sup>quot;xxxx" is the configuration code identifier for the register settings stored in the OTP register. Each "x" can be a hexadecimal value between 0 and F. The default code is "0000". Contact an MPS FAE to create this unique number.

## **PIN FUNCTIONS**

| Pin#                                                                 | Name           | Description                                                                                                                                                                                                                                                                                                                  |

|----------------------------------------------------------------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                                                                    | VCC            | Internal bias supply. The VCC pin is powered by VBIAS, and supplies power to the internal control circuit and gate drivers. Place a ≥10µF decoupling capacitor between VCC and ground, close to VCC. VCC requires power from an external source if V <sub>BIAS</sub> is below 3.5V.                                          |

| 2                                                                    | FBI            | <b>Feedback input.</b> The FBI pin indicates the current sink headroom information input between multiple MPQ7225A devices. Connect FBI to GND if it is not used.                                                                                                                                                            |

| 3, 10, 15, 22                                                        | GND            | <b>Ground.</b> GND is the reference ground of the power device, and requires careful consideration during PCB layout.                                                                                                                                                                                                        |

| 4, 5, 6, 7, 8,<br>9, 11, 12, 13,<br>14, 16, 17,<br>18, 19, 20,<br>21 | LED1–<br>LED16 | <b>LED channel 1–16 current inputs</b> . Connect the cathodes of LED channels 1–16 to these pins. Connect any unused LEDx pins to GND, and disable LEDx through the CHx_EN (0x03) register.                                                                                                                                  |

| 23                                                                   | FBO            | <b>Feedback output.</b> Connect the FBO pin to the DC/DC converter's feedback pin through a resistor divider network. FBO provides the current sink headroom information output between multiple MPQ7225A devices. Float this pin if adaptive feedback control (AFC) is not used.                                            |

| 24                                                                   | ISET           | <b>LED current set.</b> Connect an external resistor from ISET to GND to set the average LED current ( $I_{LED}$ ). $I_{LED}$ for each channel (mA) = 600 / $R_{ISET}$ (k $\Omega$ ). If the ISET pin is shorted to ground or an open condition is detected, the device latches off and asserts the /FS pin.                 |

| 25                                                                   | DATA-          | Differential interface (negative).                                                                                                                                                                                                                                                                                           |

| 26                                                                   | DATA+          | Differential interface (positive).                                                                                                                                                                                                                                                                                           |

| 27                                                                   | ADDR2          | <b>Address setting.</b> Configure the device's address by connecting this pin to VCC/GND or to GND with a $35k\Omega$ resistor (with $\pm 10\%$ range). For more details, see the Device Address section on page 27.                                                                                                         |

| 28                                                                   | ADDR1          | Address setting. Configure the device's address by connecting this pin to VCC/GND or to GND with a $35k\Omega$ resistor (with $\pm 10\%$ range). For more details, see the Device Address section on page 27.                                                                                                                |

| 29                                                                   | /FS            | <b>Failsafe output.</b> The /FS pin is an active-low, open-drain output. /FS pulls low if any of the following occur: LED short, LED open, thermal shutdown, ISET pin open, or ISET pin short. The /FS pin can support a continuous connection to VBIAS or VCC through a pull-up resistor. Float this pin if it is not used. |

| 30                                                                   | EN             | <b>Enable input.</b> Pull EN above 2.2V to enable the part; pull EN below 0.8V to shut down the part. The EN pin can be pulled directly to VBIAS through a resistor.                                                                                                                                                         |

| 31                                                                   | VBIAS          | <b>Bias supply.</b> The MPQ7225A operates from a 2.5V to 18V input rail. A capacitor (C <sub>IN</sub> ) is required, and must be placed close to VBIAS to decouple the input rail.                                                                                                                                           |

| 32                                                                   | MODE           | <b>Mode selection.</b> The MODE pin is the master/slave mode selection pin. Tie MODE to GND to configure the device in master mode, or tie MODE to VCC to configure the device in slave mode. If AFC is not used, connect all devices' MODE pins to GND.                                                                     |

| -                                                                    | Exposed pad    | <b>Exposure thermal pad.</b> The exposed pad has no internal electrical connection to GND. Connect the exposed pad to the external GND plane on the board for optimal thermal performance.                                                                                                                                   |

### **ABSOLUTE MAXIMUM RATINGS (1)**

| V <sub>VBIAS</sub> 0.3V to +20V                       |

|-------------------------------------------------------|

| V <sub>LEDx</sub> 0.3V to +20V                        |

| FBO, EN, /FS0.3V to +20V                              |

| DATA+, DATA0.3V to +18V                               |

| All other pins0.3V to +4V                             |

| Continuous power dissipation ( $T_A = 25$ °C) (2) (6) |

| QFN-32 (5mmx6mm) 5.9W                                 |

| Junction temperature (T <sub>J</sub> )150°C           |

| Lead temperature260°C                                 |

| Storage temperature65°C to +150°C                     |

| ESD Ratings                                           |

| Human body model (HBM)Class 2 (3)                     |

| Charged-device model (CDM) Class C2b (4)              |

| Recommended Operating Conditions                      |

| VCC (if externally supplied)3.2V to 3.5V              |

| VBIAS voltage (V <sub>VBIAS</sub> )2.5V to 18V        |

| LED current (I <sub>LED</sub> )                       |

| Operating junction temperature (T <sub>J</sub> )      |

|                                                       |

.....-40°C to +150°C

### Thermal Resistance θ<sub>JA</sub> θ<sub>JC</sub>

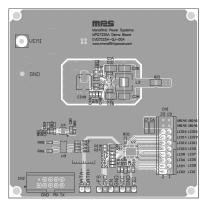

QFN-32 (5mmx6mm) JESD51-7......23.8.....1.4....°C/W<sup>(5)</sup> EVQ7225A-QJ-00A......21.2....0.93....°C/W<sup>(6)</sup>

#### Notes:

- 1) Exceeding these ratings may damage the device.

- 2) The maximum allowable power dissipation is a function of the maximum junction temperature, T<sub>J</sub> (MAX), the junction-to-ambient thermal resistance, θ<sub>JA</sub>, and the ambient temperature, T<sub>A</sub>. The maximum allowable continuous power dissipation at any ambient temperature is calculated by P<sub>D</sub> (MAX) = (T<sub>J</sub> (MAX) T<sub>A</sub>) / θ<sub>JA</sub>. Exceeding the maximum allowable power dissipation can cause excessive die temperature, and the regulator may go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

- 3) Per AEC-Q100-002.

- 4) Per AEC-Q100-011.

- 5) Measured on a JESD51-7, 4-layer PCB. The values given in this table are only valid for comparison with other packages and cannot be used for design purposes. These values were calculated in accordance with JESD51-7, and simulated on a specified JEDEC board. They do not represent the performance obtained in an actual application. The value of  $\theta_{\text{JC}}$  shows the thermal resistance from junction-to-case bottom.

- 6) Measured on a standard EVB for the MPQ7225A: 83.5mmx83.5mm size, 4-layer PCB, 2oz. The value of  $\theta_{\text{JC}}$  shows the thermal resistance from junction-to-case top.

## **ELECTRICAL CHARACTERISTICS**

$V_{BIAS} = 6.5V$ ,  $T_J = -40$ °C to +150°C, typical values are at  $T_J = 25$ °C, unless otherwise noted.

| Parameter                                           | Symbol                 | Condition                                               |                                                                                                                                   | Min    | Тур    | Max    | Units |

|-----------------------------------------------------|------------------------|---------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|--------|--------|--------|-------|

| Supply Voltage                                      |                        |                                                         |                                                                                                                                   |        |        |        |       |

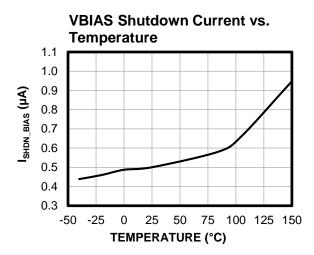

|                                                     |                        | Disabled, E                                             | N pin is low (shutdown)                                                                                                           |        | 0.5    | 2.5    | μA    |

|                                                     |                        | EN_ANA bi                                               | o LED load (EN pin is high, it = 0, quiescent current [Ia]), ed externally, VBIAS = 6.5V                                          |        | 0.6    | 1      | mA    |

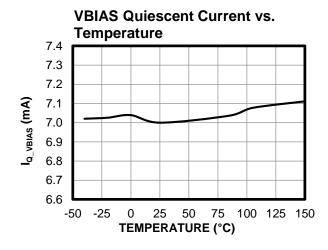

| BIAS supply current                                 | I <sub>BIAS</sub>      |                                                         | o LED load (EN pin is high, bit = 0, $I_Q$ ), VCC supplied $V_{BIAS} = 14V$                                                       |        | 1.4    | 2.1    | mA    |

|                                                     |                        |                                                         | o LED load (EN pin is high, bit = 0, $I_Q$ ), VCC supplied $I_{BIAS} = 6.5V$                                                      |        | 7      | 12     | mA    |

|                                                     |                        |                                                         | o LED load (EN pin is high, bit = 0, $I_Q$ ), VCC supplied $I_{BIAS} = 14V$                                                       |        | 8      | 13     | mA    |

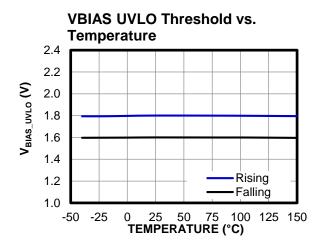

| VBIAS under-voltage                                 | Valva inii a           | Rising edge                                             | e                                                                                                                                 |        | 1.8    |        | V     |

| lockout (UVLO) threshold                            | V <sub>BIAS_UVLO</sub> | Falling edg                                             | е                                                                                                                                 |        | 1.6    |        | V     |

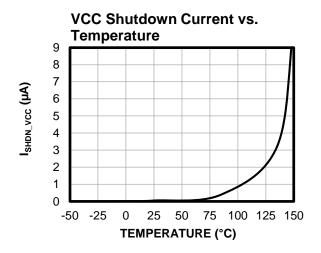

|                                                     | lcc                    | Only<br>required if<br>VCC is<br>supplied<br>externally | Disabled, EN pin is low (shutdown), Vcc = 3.5V                                                                                    |        | 0.05   | 60     | μA    |

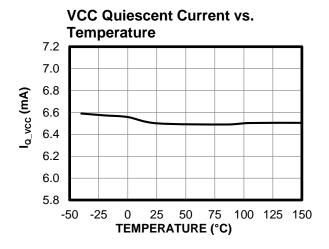

| VCC supply current                                  |                        |                                                         | $V_{CC}$ = 3.5V, enabled, no LED load (EN pin is high, $I_Q$ )                                                                    |        | 6.5    | 13     | mA    |

|                                                     |                        |                                                         | $V_{CC}=3.5V,~16~LED$ channels are enabled (EN pin is high, EN_ANA bit = 1, PWM = 100%, RISET = $6.04k\Omega$ , $I_{LED}=100mA$ ) |        | 12     | 20     | mA    |

| Internal VCC regulator voltage                      | Vcc                    | I <sub>VCC</sub> = 0mA                                  |                                                                                                                                   | 3.1    | 3.3    | 3.5    | V     |

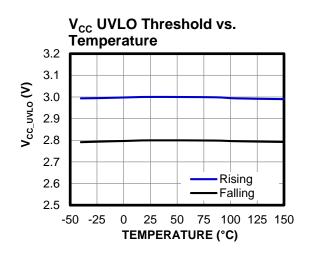

| VCC supply UVLO                                     | V                      | Rising edge                                             | 9                                                                                                                                 | 2.8    | 3      | 3.2    | V     |

| threshold                                           | V <sub>CC_UVLO</sub>   | Falling edg                                             | e                                                                                                                                 | 2.6    | 2.8    | 3.0    | V     |

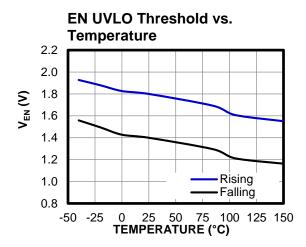

| EN threshold                                        | $V_{EN_{-}R}$          | V <sub>EN</sub> - V <sub>GND</sub>                      |                                                                                                                                   | 2.2    |        |        | V     |

| EN tilleshold                                       | V <sub>EN_F</sub>      | V <sub>EN</sub> - V <sub>GND</sub>                      |                                                                                                                                   |        |        | 0.8    | V     |

| LED Current                                         |                        |                                                         |                                                                                                                                   |        |        |        |       |

| 1 <b>50</b> (()                                     |                        | R <sub>ISET</sub> = 3.0 <sup>2</sup>                    | IkΩ, T <sub>J</sub> = 25°C                                                                                                        | 194.35 | 199.34 | 204.32 | mA    |

| LED current (channel output to ideal current error) | luss                   | R <sub>ISET</sub> = 3.01                                | $IkΩ$ , $T_J = -40$ °C to $+150$ °C                                                                                               | 189.37 | 199.34 | 209.3  | mA    |

|                                                     | ILED                   | R <sub>ISET</sub> = 6.04                                | 4kΩ, T <sub>J</sub> = 25°C                                                                                                        | 96.85  | 99.34  | 101.82 | mA    |

| ,<br>                                               |                        | $R_{ISET} = 6.04$                                       | $1k\Omega$ , $T_J = -40^{\circ}C$ to $+150^{\circ}C$                                                                              | 94.37  | 99.34  | 104.3  | mA    |

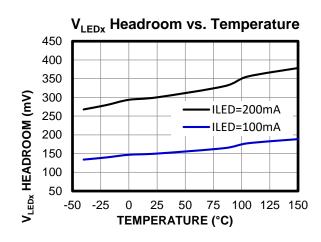

| I CDy ourrent sink                                  |                        | I <sub>LED</sub> = 200m                                 | nA                                                                                                                                |        | 300    | 400    |       |

| LEDx current sink headroom voltage                  | $V_{LEDx}$             | I <sub>LED</sub> = 100m                                 | nA                                                                                                                                |        | 150    | 250    | mV    |

|                                                     |                        | $I_{LED} = 50 \text{m/s}$                               | I <sub>LED</sub> = 50mA                                                                                                           |        | 75     | 125    |       |

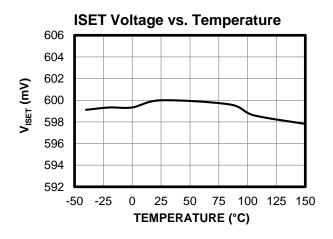

| ISET voltage                                        | V <sub>ISET</sub>      | $R_{ISET} = 3.0^{\circ}$                                | $IkΩ$ (or $I_{ISET} = 200μA$ )                                                                                                    | 0.57   | 0.60   | 0.63   | V     |

## **ELECTRICAL CHARACTERISTICS** (continued)

$V_{BIAS} = 6.5V$ ,  $T_J = -40$ °C to +150°C, typical values are at  $T_J = 25$ °C, unless otherwise noted.

| Parameter                                         | Symbol                | Condition                                                                    | Min  | Тур  | Max  | Units |

|---------------------------------------------------|-----------------------|------------------------------------------------------------------------------|------|------|------|-------|

| Channel output leakage                            | I <sub>LKG</sub>      | PWM = 0% (single channel),<br>T <sub>J</sub> = -40°C to +150°C               |      |      | 2    | μΑ    |

| current                                           | ILKG                  | PWM = 0% (all 16 channels),<br>$T_J = -40^{\circ}\text{C}$ to +150°C         |      |      | 32   | μΑ    |

| Channel-to-channel current error                  | leer_cc               | $I_{ERR\_CC} = (I_{OUTI} - I_{AVE}) / I_{AVE} \times 100\%,$<br>100mA, 200mA | -5%  |      | +5%  |       |

| Dimming                                           |                       |                                                                              |      |      |      |       |

| PWM frequency                                     | f <sub>PWM</sub>      | Default setting                                                              | 225  | 250  | 275  | Hz    |

| PWM frequency range                               |                       | Configuration range                                                          | 250  |      | 1000 | Hz    |

| PWM duty slew rate                                | tрwм                  | 12-bit resolution, f <sub>PWM</sub> = 250Hz                                  | 0.8  | 1    | 1.2  | μs    |

| Phase shift delay                                 | tDELAY                | PHASE_SHIFT[1:0] = 11                                                        | 16   | 20   | 24   | μs    |

| LED current slew rate in PWM                      |                       | SLEW_RATE[1:0] = 01, rising edge, $R_{ISET} = 6.04k\Omega$                   | 2    | 5    | 10   | μs    |

| dimming                                           |                       | SLEW_RATE[1:0] = 11, rising edge, $R_{ISET} = 6.04k\Omega$                   | 8    | 20   | 32   | μs    |

| Protection (Selectable Latch of                   | or Hiccup M           | ode)                                                                         |      |      |      |       |

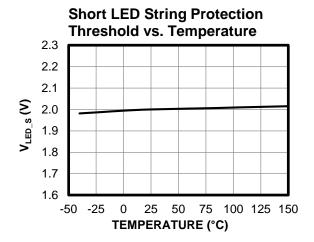

| Short LED string protection threshold             | V <sub>LED_S</sub>    | LED_SHORT_THR[1:0] = 00                                                      | 1.8  | 2.1  | 2.3  | V     |

| Short LED string protection time                  | t <sub>LED_</sub> s   | V <sub>LEDx</sub> > V <sub>LED_S</sub>                                       | 3.6  | 4    | 4.4  | ms    |

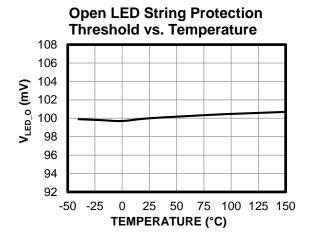

| Open LED string protection threshold              | V <sub>LED_O</sub>    | LED on, real-time monitoring (cover pin short-to-GND)                        | 50   | 100  | 150  | mV    |

| Open LED string protection time                   | tLED_O                | V <sub>LEDx</sub> < V <sub>LED_O</sub> (100mV)                               | 3.6  | 4    | 4.4  | ms    |

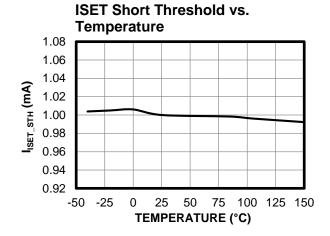

| ISET current threshold for pin short (/FS, latch) | I <sub>ISET_STH</sub> |                                                                              | 0.7  | 1    | 1.3  | mA    |

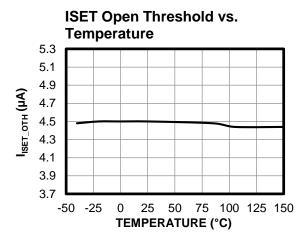

| ISET current threshold for pin open (/FS, latch)  | I <sub>ISET_OTH</sub> |                                                                              | 2    | 4.5  | 7    | μΑ    |

| Thermal warning threshold (7)                     | T <sub>WARN</sub>     |                                                                              | 135  | 150  | 165  | °C    |

| Thermal warning hysteresis (7)                    | Twarn_hys             |                                                                              |      | 20   |      | °C    |

| Thermal shutdown threshold (7)                    | T <sub>SD</sub>       |                                                                              | 155  | 170  | 185  | °C    |

| Thermal shutdown hysteresis                       | T <sub>SD_HYS</sub>   |                                                                              |      | 20   |      | °C    |

| /FS (Open Drain)                                  |                       |                                                                              | •    |      |      |       |

| Failsafe low output level                         | V <sub>FS_OL</sub>    | I <sub>FS_OL</sub> = 2mA, active                                             | 0.15 | 0.33 | 0.5  | V     |

| Failsafe input current leakage                    | I <sub>FS_LKG</sub>   | Inactive                                                                     |      |      | 1    | μΑ    |

| Failsafe assert deglitch time                     | t <sub>FS-TD</sub>    |                                                                              | 5    | 20   | 40   | μs    |

|                                                   |                       |                                                                              |      |      |      |       |

7

## **DIGITAL INTERFACE CHARACTERISTICS**

$V_{BIAS} = 6.5V$ ,  $T_J = -40$ °C to +150°C, typical values are at  $T_J = 25$ °C, unless otherwise noted.

| Parameters                                           | Symbol                | Condition                                                                    | Min  | Тур  | Max  | Units |

|------------------------------------------------------|-----------------------|------------------------------------------------------------------------------|------|------|------|-------|

| Driver                                               |                       |                                                                              |      |      |      |       |

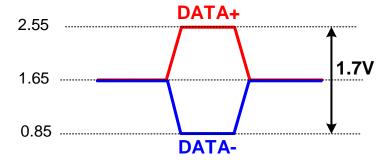

| Bus output voltage (recessive)                       | V <sub>O(R)</sub>     | $R_L = 180\Omega$                                                            | 1.15 | 1.65 | 2.15 | V     |

| Bus output voltage (DATA+) (dominant)                | V <sub>O(D+)</sub>    | $R_L$ = 180 $\Omega$ , see Figure 1 on page 9                                | 2.35 | 2.55 | 2.85 | V     |

| Bus output voltage (DATA-) (dominant)                | V <sub>O(D-)</sub>    | $R_L$ = 180Ω, see Figure 1 on page 9                                         | 0.5  | 0.85 | 1.15 | V     |

| Differential output voltage (dominant)               | V <sub>OD(D)</sub>    | $R_L = 180\Omega, V_{CC} = 3.3V$                                             | 1.4  | 1.7  | 2.35 | V     |

| Output symmetry (dominant or recessive)              | Vsym                  | $V_{CC} = 3.3V$ , $V_{O(DATA+)} + V_{O(DATA-)}$                              | 2.97 | 3.4  | 3.63 | V     |

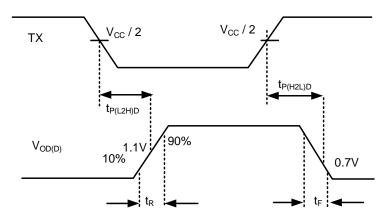

| Differential output rising time (7)                  | <b>t</b> <sub>R</sub> | $R_L$ = 180 $\Omega$ , $C_L$ = 50pF, $V_{CC}$ = 3.3V, see Figure 2 on page 9 | 2    | 5    | 15   | ns    |

| Differential output falling time (7)                 | t <sub>F</sub>        | $R_L$ = 180 $\Omega$ , $C_L$ = 50pF, $V_{CC}$ = 3.3V, see Figure 2 on page 9 | 20   | 25   | 35   | ns    |

| Propagation delay time (low-to-high level) (7)       | t <sub>P(L2H)D</sub>  | $R_L$ = 180 $\Omega$ , $C_L$ = 50pF, $V_{CC}$ = 3.3V, see Figure 2 on page 9 | 2    | 7    | 15   | ns    |

| Propagation delay time (highto-low level) (7)        | t <sub>P(H2L)D</sub>  | $R_L = 180\Omega$ , $C_L = 50pF$ , $V_{CC} = 3.3V$ , see Figure 2 on page 9  | 10   | 22   | 40   | ns    |

| Receiver                                             | •                     |                                                                              | •    | •    | •    |       |

| Input resistance (DATA+/-)                           | R <sub>IN</sub>       | $V_{CC} = 3.3V$ ,<br>$R_{IN} = \triangle V(DATA+) / \triangle I(DATA+)$      | 14   | 30   | 58   | kΩ    |

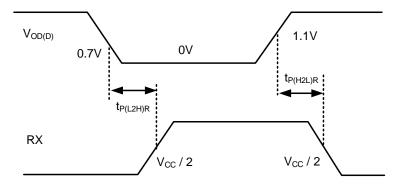

| Differential threshold voltage for RX going negative | V <sub>RXTH</sub> -   | Vcc = 3.3V                                                                   | 0.7  | 1.1  | 1.5  | V     |

| Differential threshold voltage for RX going positive | V <sub>RXTH+</sub>    | Vcc = 3.3V                                                                   | 0.3  | 0.7  | 1.1  | V     |

| Propagation delay time (low-to-high level) (7)       | t <sub>P(L2H)R</sub>  | $R_L$ = 180 $\Omega$ , $C_L$ = 50pF, $V_{CC}$ = 3.3V, see Figure 3 on page 9 | 3    | 13   | 30   | ns    |

| Propagation delay time (highto-low level) (7)        | t <sub>P(H2L)R</sub>  | $R_L = 180\Omega$ , $C_L = 50pF$ , $V_{CC} = 3.3V$ , see Figure 3 on page 9  | 5    | 18   | 35   | ns    |

| Input capacitance to ground (7)                      | CIN                   |                                                                              |      | 20   |      | pF    |

### Notes:

<sup>7)</sup> Not tested in production. Guaranteed by design and characterization.

## **TIMING DIAGRAMS**

**Recessive Dominant Recessive**

**Figure 1: Differential Interface Timing**

**Figure 2: Driver Interface Timing**

**Figure 3: Receiver Interface Timing**

### TYPICAL CHARACTERISTICS

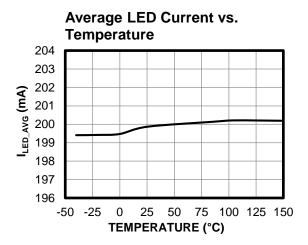

$V_{BIAS} = 6.5V$ ,  $T_J = -40$ °C to +150°C, unless otherwise noted.

## TYPICAL CHARACTERISTICS (continued)

$V_{BIAS} = 6.5V$ ,  $T_J = -40$ °C to +150°C, unless otherwise noted.

## TYPICAL CHARACTERISTICS (continued)

$V_{BIAS} = 6.5V$ ,  $T_J = -40$ °C to +150°C, unless otherwise noted.

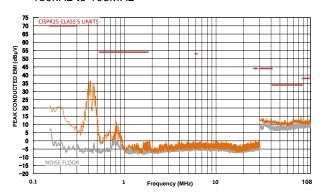

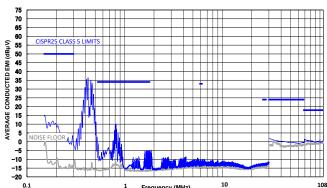

### TYPICAL PERFORMANCE CHARACTERISTICS

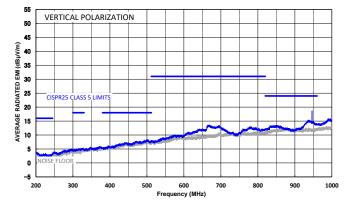

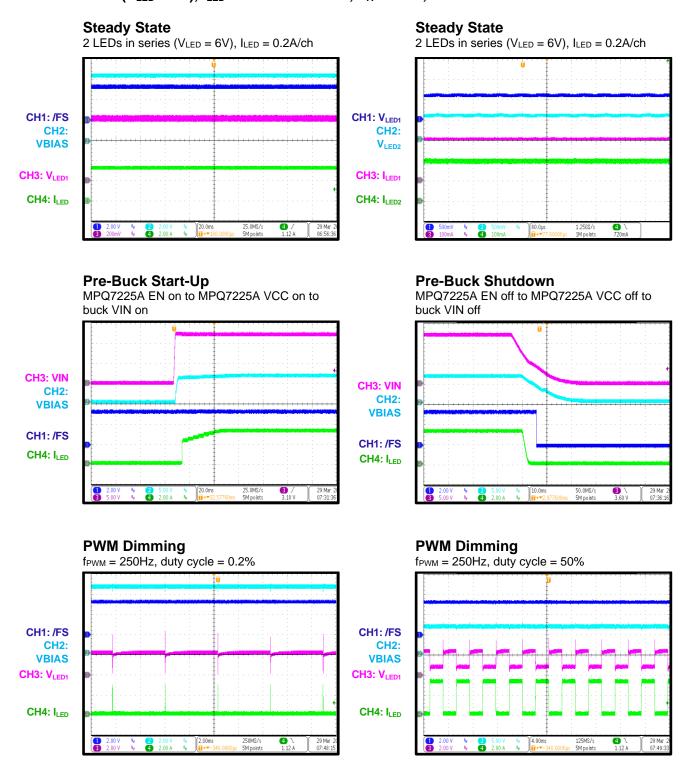

2 LEDs in series (V<sub>LED</sub> = 6V), I<sub>LED</sub>/channel = 200mA, T<sub>A</sub> = 25°C, unless otherwise noted. (8)

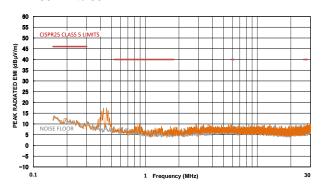

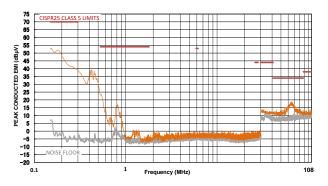

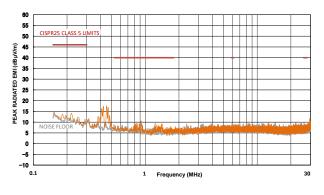

### CISPR25 Class 5 Peak Conducted Emissions

150kHz to 108MHz

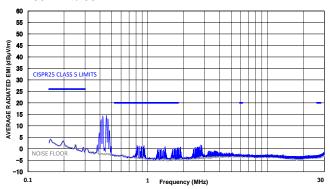

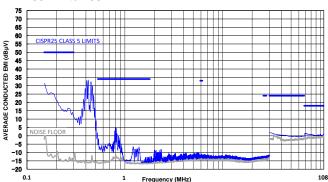

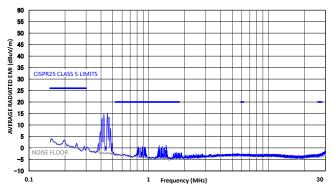

## **CISPR25 Class 5 Average Conducted Emissions**

150kHz to 108MHz

### CISPR25 Class 5 Peak Radiated Emissions

150kHz to 30MHz

### CISPR25 Class 5 Average Radiated Emissions

150kHz to 30MHz

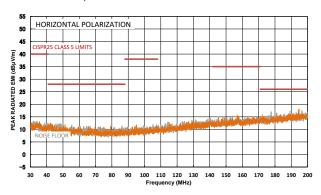

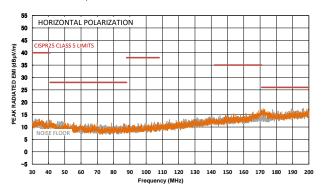

### CISPR25 Class 5 Peak Radiated Emissions

Horizontal, 30MHz to 200MHz

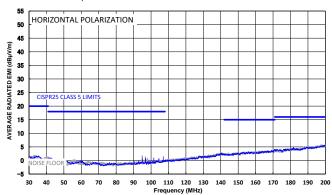

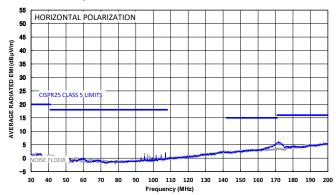

## CISPR25 Class 5 Average Radiated Emissions

Horizontal, 30MHz to 200MHz

2 LEDs in series (V<sub>LED</sub> = 6V), I<sub>LED</sub>/channel = 200mA, T<sub>A</sub> = 25°C, unless otherwise noted. (8)

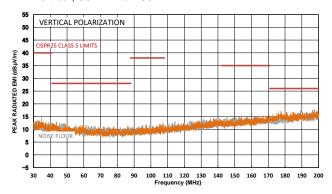

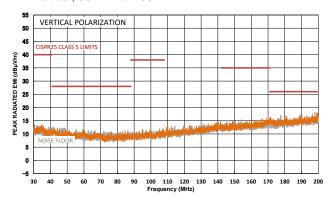

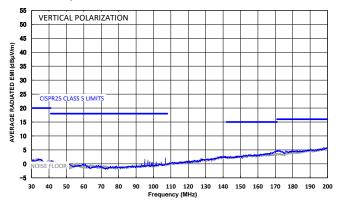

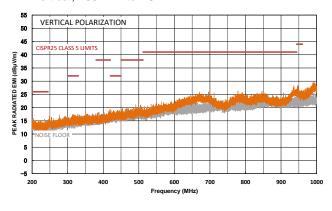

### CISPR25 Class 5 Peak Radiated **Emissions**

Vertical, 30MHz to 200MHz

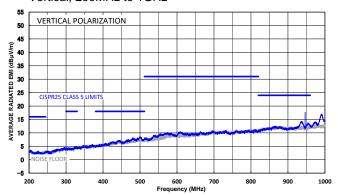

## **Emissions** Vertical, 30MHz to 200MHz

CISPR25 Class 5 Average Radiated

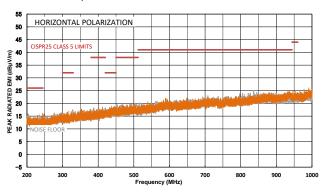

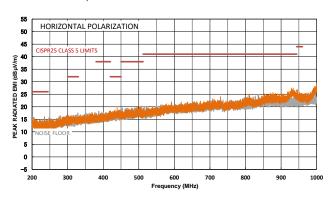

### **CISPR25 Class 5 Peak Radiated Emissions**

Horizontal, 200MHz to 1GHz

### **CISPR25 Class 5 Average Radiated Emissions**

Horizontal, 200MHz to 1GHz

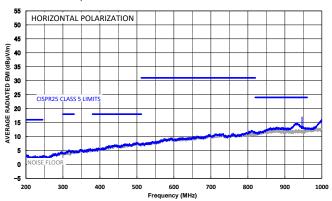

### **CISPR25 Class 5 Peak Radiated Emissions**

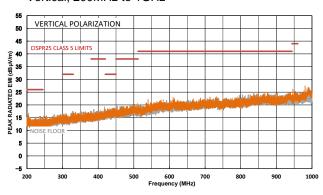

Vertical, 200MHz to 1GHz

## **CISPR25 Class 5 Average Radiated Emissions**

Vertical, 200MHz to 1GHz

8) The EMC test results are based on the typical application circuit with EMI filters (see Figure 23 on page 44).

2 LEDs in series (V<sub>LED</sub> = 6V), I<sub>LED</sub>/channel = 200mA, T<sub>A</sub> = 25°C, unless otherwise noted. (9)

### CISPR25 Class 5 Peak Conducted **Emissions**

150kHz to 108MHz

### CISPR25 Class 5 Average Conducted **Emissions**

150kHz to 108MHz

### **CISPR25 Class 5 Peak Radiated Emissions**

150kHz to 30MHz

### CISPR25 Class 5 Average Radiated **Emissions**

150kHz to 30MHz

### **CISPR25 Class 5 Peak Radiated Emissions**

Horizontal, 30MHz to 200MHz

### CISPR25 Class 5 Average Radiated **Emissions**

Horizontal, 30MHz to 200MHz

2 LEDs in series (V<sub>LED</sub> = 6V), I<sub>LED</sub>/channel = 200mA, T<sub>A</sub> = 25°C, unless otherwise noted. (9)

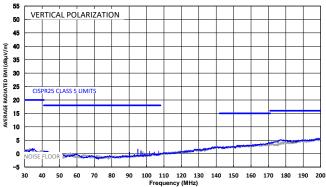

### CISPR25 Class 5 Peak Radiated Emissions

Vertical, 30MHz to 200MHz

# CISPR25 Class 5 Average Radiated Emissions Vertical, 30MHz to 200MHz

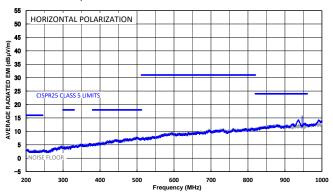

### CISPR25 Class 5 Peak Radiated Emissions

Horizontal, 200MHz to 1GHz

## CISPR25 Class 5 Average Radiated Emissions

Horizontal, 200MHz to 1GHz

## CISPR25 Class 5 Peak Radiated Emissions

Vertical, 200MHz to 1GHz

## CISPR25 Class 5 Average Radiated Emissions

Vertical, 200MHz to 1GHz

#### Notes:

9) The EMC test results are based on the typical application circuit with EMI filters (see Figure 23 on page 44). The configurations are as follows: f<sub>PWM</sub> = 250Hz, duty cycle = 50%, phase shift = 1μs, slew rate = 5μs.

CH4: I<sub>LED1</sub>

## TYPICAL PERFORMANCE CHARACTERISTICS (continued)

2 LEDs in series (V<sub>LED</sub> = 6V), I<sub>LED</sub>/channel = 200mA, T<sub>A</sub> = 25°C, unless otherwise noted.

CH4: I<sub>LED1</sub>

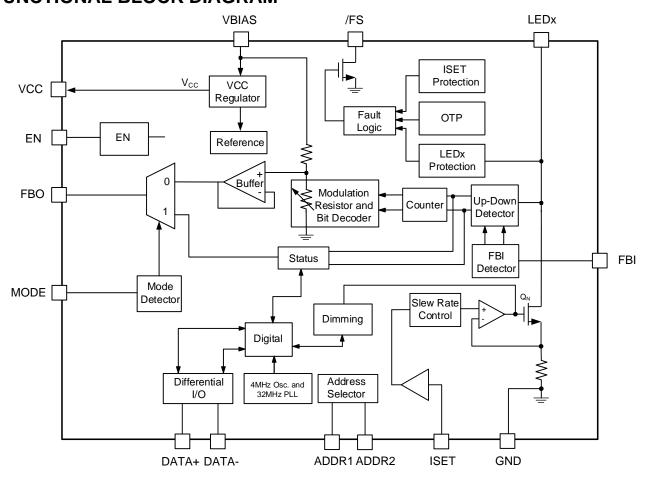

## **FUNCTIONAL BLOCK DIAGRAM**

Figure 4: Functional Block Diagram

### **OPERATION**

### **LED Current Sinks**

The current sink regulators (16 channels) embedded in the MPQ7225A can be individually configured to provide up to 200mA of current for each channel. These 16 specialized current sinks are accurate to within ±5% for currents at 200mA across the full temperature range, with a string-to-string difference of ±5%.

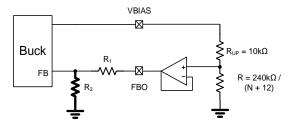

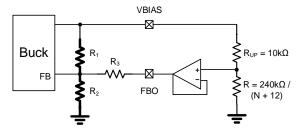

## Pre-Regulator Adaptive Feedback Control (AFC)

The MPQ7225A features adaptive feedback control (AFC) for the external pre-regulator. The output voltage of the pre-regulator (e.g. the buck) is always self-adjusted based on the LED string with the lowest headroom voltage. This minimizes the LEDx pin voltage (V<sub>LEDx</sub>) and maintains the target LED current (I<sub>LED</sub>) for the 16 channels. Overall efficiency is maximized when the MPQ7225A's current sinks operate with the minimum headroom voltage.

The number of used LED outputs is automatically detected, and only the active LED outputs are monitored for AFC. If any LED strings are not used, they can be disabled via the one-time programmable (OTP) memory using CHx\_EN (0x03).

V<sub>LEDx</sub> is periodically monitored by the control loop. If any of the LED outputs fall below the low-band threshold (0.45V), the external pre-regulator's output voltage increases. If all LED outputs exceed the high-band threshold (0.55V), the external pre-regulator's output decreases.

$V_{LEDx}$  should remain between the low band and high band. The band can be configured via register 0x27 based on  $I_{LED}$ . The high-band voltage can be set between 0.25V and 0.6V, while the low-band voltage can be set between 0.2V and 0.55V. If 150mA <  $I_{LED} \le 200$ mA, it is recommended to set the overall band between 0.45V and 0.55V. If  $I_{LED} \le 150$ mA, it is recommended to set the overall band between 0.3V and 0.4V to improve efficiency.

The initial VBIAS voltage ( $V_{BIAS}$ ) can also be configured via the OTP. The internal divider resistor (R1 and R2) defines both the minimum and maximum adaptive  $V_{BIAS}$  levels (see Figure 7 on page 26).

Choose the maximum V<sub>BIAS</sub> based on the maximum LED string voltage specification. Before the LED drivers are active, the initial preregulator output voltage exceeds the maximum LED string voltage by about 0.3V.

One of the MPQ7225A's key benefits is that its dropout information can be transferred to the DC/DC converter's feedback pin via the FBO pin to optimize system efficiency in real time. This information sharing is also available between multiple MPQ7225A devices via the FBI and FBO pins. The channel with the lowest  $V_{\text{LEDx}}$  uses its  $V_{\text{LEDx}}$  to determine the DC/DC converter's power supply output. AFC also works if multiple MPQ7225A devices are connected in parallel.

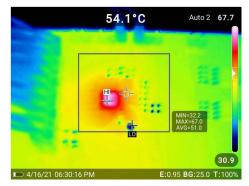

Figure 5 shows the thermal image when  $V_{\text{BIAS}}$  is set with AFC.

Figure 5: VBIAS with AFC

Figure 6 shows the thermal image when  $V_{BIAS}$  has a fixed voltage ( $V_{LEDx} = 1V$ ) without AFC.

Figure 6: VBIAS without AFC

AFC improves thermal performance and efficiency. When  $I_{LED} = 200 \text{mA}$ , the temperature deviation is about  $38.3^{\circ}\text{C}$ .

If AFC is not used, float the MPQ7225A's FBO

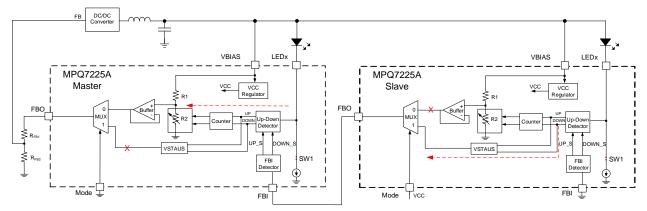

and MODE pins, and connect the FBI pin to GND. **Multiple Devices**

The MPQ7225A can also support several devices in parallel by setting the part to master mode or slave mode through the MODE pin. If the MODE pin is connected to GND, the part is configured as the master. The slave device's FBO pin should be connected to the master device's FBI pin. If the MODE pin is connected to VCC, the part is configured as a slave device. The master device's FBO pin is connected to the pre-regulator's FB resistor divider (see Figure 7). Only the master device can directly adjust V<sub>BIAS</sub>; the slave device can only deliver the V<sub>BIAS</sub> information to master device through the FBI pin.

For the master device, the FBI pin voltage (V<sub>FBI</sub>) and V<sub>LEDx</sub> determine how to adjust V<sub>BIAS</sub>. If the high band is set to 0.55V and the low band is set to 0.45V, and  $0.75V < V_{FBI} < 1.2V$  (or any of the master devices'  $V_{LEDx}$  < 0.45V), then the chip decreases R2. This decreases the FBO voltage (V<sub>FBO</sub>), which regulates V<sub>BIAS</sub> to be high via the pre-regulator. If V<sub>FBI</sub> < 0.3V and all the masters'  $V_{LEDx} > 0.55V$ , then the chip increases R2. This increases V<sub>FBO</sub>, which regulates V<sub>BIAS</sub> be to low

via the pre-regulator. For other conditions, V<sub>BIAS</sub> is maintained as normal.

Refer to the FBI detector. When  $0.75V < V_{FBI} <$ 1.2V,  $UP_S = 1$ , and  $DOWN_S = 0$ , this means that V<sub>BIAS</sub> is not sufficient for the slave device, so V<sub>BIAS</sub> must be increased for the slave device. When  $V_{FBI} < 0.3V$ , DOWN\_S = 1, and UP\_S = 0, this means that V<sub>BIAS</sub> is too high for the slave device, so V<sub>BIAS</sub> must be decreased. When 0.3V  $< V_{FBI} < 0.75V$ , UP\_S = 0, and DOWN\_S = 0, this means that V<sub>BIAS</sub> must stay the same for the slave device.

For any slave device, if  $V_{LEDx} < 0.45V$ , or 0.75 <  $V_{FBI}$  < 1.2V, then  $V_{FBO}$  = 1V ( $V_{BIAS}$  is not sufficient; increase V<sub>BIAS</sub> for the slave device). If all V<sub>LEDx</sub> > 0.55V and  $V_{FBI} < 0.3V$ , then  $V_{FBO} = 0V$  ( $V_{BIAS}$  is too high; decrease V<sub>BIAS</sub> for the slave device); for other conditions,  $V_{FBO} = 0.5V$  (maintain  $V_{BIAS}$  for the slave device).

In summary, if  $V_{LEDx}$  < 0.45V, then  $V_{BIAS}$ increases; does V<sub>BIAS</sub> decreases only when each  $V_{LEDx} > 0.55V$ . For other conditions,  $V_{BIAS}$  stays the same. Table 1 summarizes relationships.

| Slave Device         |                                                                   |                                             |                 |

|----------------------|-------------------------------------------------------------------|---------------------------------------------|-----------------|

| Condition            | Any V <sub>LEDx</sub> < 0.45 or<br>0.75 < V <sub>FBI</sub> < 1.2V | All $V_{LEDx} > 0.55V$ and $V_{FBI} < 0.3V$ | Other condition |

| V <sub>FBO</sub>     | 1V                                                                | 0V                                          | 0.5V            |

| <b>Master Device</b> |                                                                   |                                             |                 |

| Condition            | Any $V_{LEDx} < 0.45$ or $0.75 < V_{FBI} < 1.2V$                  | All $V_{LEDx} > 0.55V$ and $V_{FBI} < 0.3V$ | Other condition |

| V <sub>FBO</sub>     | Decreases                                                         | Increases                                   | Stays the same  |

| VBIAS                | Increases                                                         | Decreases                                   | Stays the same  |

Table 1: Relationship between FBI, FBO, VBIAS, and VLEDX

Figure 7 shows how to set up master and slave modes for the MPQ7225A.

Figure 7: Master and Slave Mode Set-Up

#### **Device Address**

The device address is configured via ADDR1,

ADDR2, and the SADDR\_PAGE bit. A total of 16 different addresses can be configured (see Table 2).

**Table 2: Address Setting**

| ADDR2                          | ADDR1                                         | SADDR_PAGE | Bits[3:0] |

|--------------------------------|-----------------------------------------------|------------|-----------|

| Connect to VCC                 | Connect to VCC                                | 0          | 0000      |

| Connect to VCC                 | Connect R = $35k\Omega$ to GND                | 0          | 0001      |

| Connect to VCC                 | Connect to GND                                | 0          | 0010      |

| Connect R = $35k\Omega$ to GND | Connect to VCC                                | 0          | 0011      |

| Connect R = $35k\Omega$ to GND | Connect R = $35k\Omega$ to GND                | 0          | 0100      |

| Connect R = $35k\Omega$ to GND | Connect to GND                                | 0          | 0101      |

| Connect to GND                 | Connect to VCC                                | 0          | 0110      |

| Connect to GND                 | Connect R = $35k\Omega$ to GND                | 0          | 0111      |

| Connect to GND                 | Connect to GND                                | 0          | 1000      |

| Connect to GND                 | Connect to GND                                | 1          | 1000      |

| Connect to VCC                 | Connect to VCC                                | 1          | 1000      |

| Connect to VCC                 | Connect R = $35k\Omega$ to GND                | 1          | 1001      |

| Connect to VCC                 | Connect to GND                                | 1          | 1010      |

| Connect R = $35k\Omega$ to GND | Connect to VCC                                | 1          | 1011      |

| Connect R = $35k\Omega$ to GND | Connect R = $35k\Omega$ to GND                | 1          | 1100      |

| Connect R = $35k\Omega$ to GND | Connect to GND                                | 1          | 1101      |

| Connect to GND                 | Connect to VCC                                | 1          | 1110      |

| Connect to GND                 | Connect to GND Connect R = $35k\Omega$ to GND |            | 1111      |

At start-up, the IC checks the address first. Once the address is checked, the address is maintained during operation unless there is a power-on reset (POR). Note that the  $35 k\Omega$  resistor must be within the  $\pm 10\%$  range. If SADDR\_PAGE is set to 0 via the OTP, the solution can support a maximum of 9 devices in one system. To use more than 9 devices, set SADDR\_PAGE to 1.

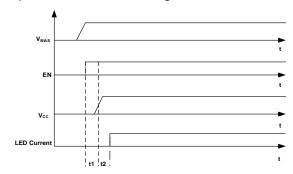

### **Enable (EN) and Start-Up**

The EN pin can connected to VBIAS through a resistor, or it can be controlled by the MCU's I/O pin. Pull EN above 2.2V to enable the part; pull EN below 0.8V to disable the part.

If using VBIAS to power VCC,  $V_{CC}$  does not rise until  $V_{BIAS}$  and EN are higher than UVLO. Then the internal logic circuits, including the differential interface, are active. The start-up sequence is as follows:

- 1.  $V_{\text{BIAS}}$  and EN pull high. Make sure the  $V_{\text{BIAS}}$  reach to the target value in 5ms.

- 2. V<sub>CC</sub> exceeds its UVLO threshold.

- 3. The internal logic circuits are active and provide the output to the LEDs.

Each channel can be enabled or disabled individually by setting the corresponding ChxEN bit (register address: 0x03) to "disabled."

Figure 8 shows the start-up sequence. This sequence is described in greater detail below.

Figure 8: Start-Up Sequence

- $\underline{t1}:$  The rising time from EN going high to  $V_{\text{CC}}$  >  $V_{\text{CC\_UVLO}}$  is about 200µs, which is based on the 10µF VCC capacitor.

- $\underline{t2}$ : The delay time from  $V_{CC}$  rising to when the internal logic is ready is about 5.5ms.

- If  $V_{BIAS}$  < 3.5V, then another external LDO is required to power VCC. Set the external LDO voltage to 3.3V, with a current ability > (n20mA + 50mA), where n is the number of MPQ7225A devices in the system.

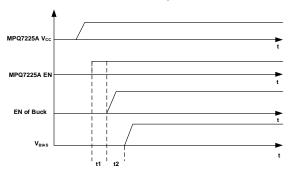

If using a buck converter as the MPQ7225A's pre-regulator, the FBO pin must be connected to the pre-regulator's FB pin through a divider network. In this scenario, start-up should follow the sequence below:

- 1. Power the MPQ7225A's VCC pin with an external 3.3V LDO.

- 2. The MPQ7225A's EN pin goes high.

- 3. The pre-regulator starts up.

Figure 9 shows this start-up sequence. This sequence is described in greater detail below.

Figure 9: Start-Up Sequence

t1: The IC requires 500µs to load the OTP. It is recommended to wait longer than 500µs to initially start up the MPQ7225A or the buck converter.

<u>t2</u>: This time period is based on the buck's startup delay.

If VBIAS is disconnected from the pre-regulator or the FBO pin is disconnected from the FB divider, then the pre-regulator works at a maximum duty cycle, and the pre-regulator's output voltage is regulated to its input voltage. Then all LEDx pins detect an LED short after 4ms, and all LEDx pins shut off.

If AFC is not used, then  $V_{\text{BIAS}}$  can be set to a fixed voltage.  $V_{\text{BIAS}}$  must exceed the maximum  $V_{\text{LEDx}}$  by at least 0.4V.

### **LED Current Setting**

The LED currents of all channels are set by an external resistor at the ISET pin, calculated with Equation (1):

$$I_{LED}(mA) = \frac{600}{R_{ISET}(k\Omega)}$$

(1)

The nominal ISET voltage (V<sub>ISET</sub>) is 0.6V. When the ISET current exceeds a specific value, it is detected as a pin short to ground. The ISET

current threshold for short detection is 1mA (corresponding to a  $0.6k\Omega$  resistor, or a 1000mA I<sub>LED</sub>). When the ISET current is below 5µA (corresponding to a 120k $\Omega$  resistor or 5mA I<sub>LED</sub>), an ISET open condition is detected.

If an open or short condition is detected, the device latches off and asserts the /FS pin.

### **EMI Reduction**

The MPQ7225A features three EMI reduction methods.

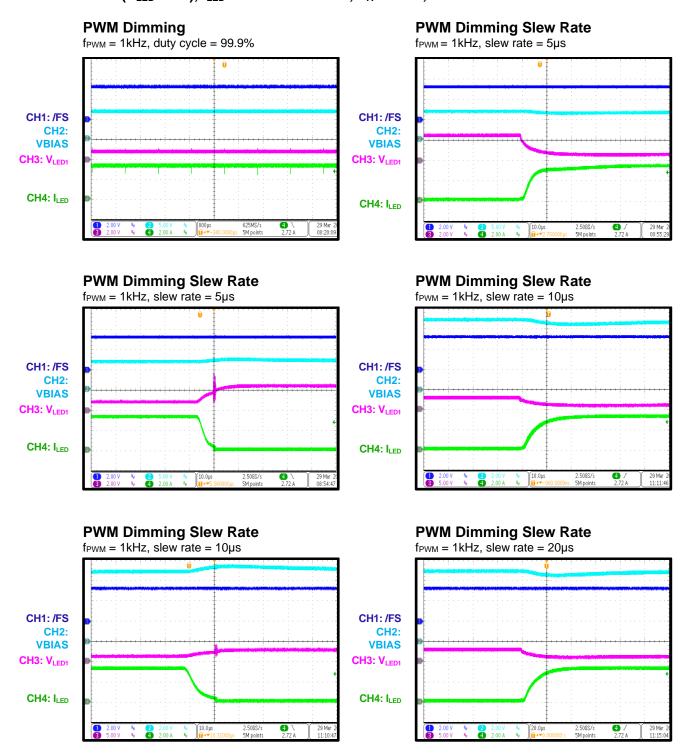

The first method requires configuring the LED current's rising/falling slew rates during pulsewidth modulation (PWM) dimming, as this can sufficiently optimize EMI performance. The LED current rising/falling slew rates are controlled via register 0x01, bits[13:12]. The slew rates can be set to no slew rate, 5µs, 10µs, and 20µs. The default value is 5µs.

The second method requires configuring the LED current's phase-shift function. This function is controlled via register 0x01, bits[11:10]. When phase-shift is enabled, the channel x + 1 (where x = 1, 2...13) LED current phase shift is 1 $\mu$ s, 5 $\mu$ s, or 20 $\mu$ s after channel x's LED current rising edge.

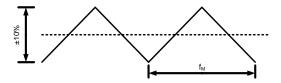

The third EMI reduction method is frequency spread spectrum (FSS). FSS reduces EMI noise around the internal clock frequency and its harmonic frequencies. This method deliberately spreads the frequency of the clock waveform and widens the bandwidth of the switching waveform, which ultimately reduces its EMI spectral density. FSS modulates the internal clock frequency within ±10% from the central frequency, with a 15.6kHz modulation frequency (f<sub>M</sub>) (see Figure 10). FSS can be disabled via register 0x01, bit[0].

Figure 10: Frequency Spread Spectrum

### **Pulse-Width Modulation (PWM) Dimming**

During PWM dimming, the LED current is chopped. This means that the LED current amplitude stays the same, while the LED current duty cycle varies with the PWM dimming register.

The PWM dimming duty cycle is set via PWM dimming registers 0x07~0x26, bits[11:0].

The duty cycle (D) can be estimated with Equation (2):

$$D = \frac{PWMx}{2^{12} - 1} = \frac{PWMx}{4095}$$

(2)

Where PWMx is the PWM dimming register for channel x (x = 1, 2...16).

PWMx, When bits[11:0] 0x000.corresponding LED channel current is 0. The PWM dimming frequency can be set via register 0x01, bits[9:8]. The dimming frequency can be set to 250Hz, 500Hz, or 1kHz. Ensure that the minimum dimming on time > 10µs.

The PWM dimming frequency and PWM dimming duty cycle can be changed on the fly.

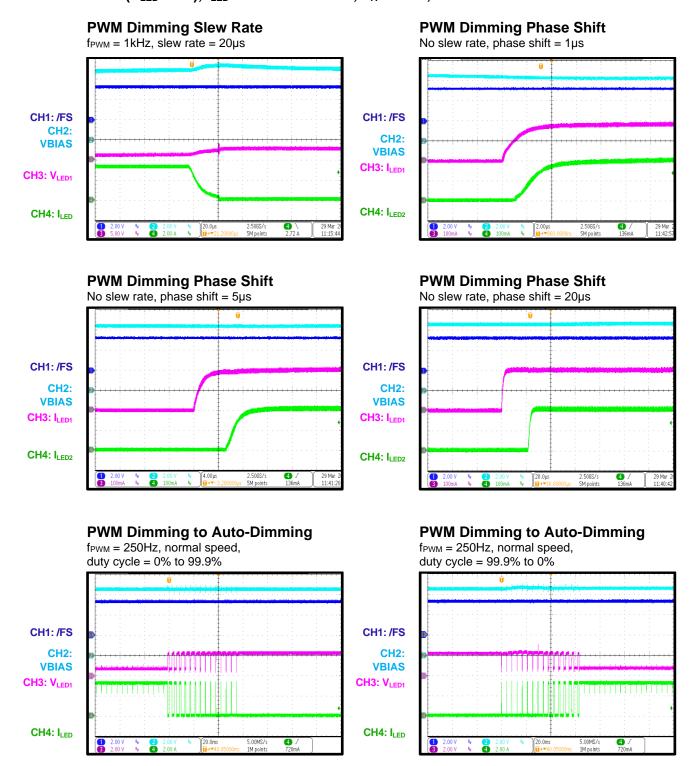

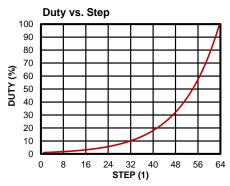

### **Automatic Logarithmic Dimming**

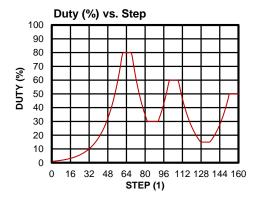

To reduce the burden on the communication bus, the MPQ7225A provides embedded, automatic logarithmic dimming based on a fixed 64-point lookup table. Assume there are a total of 64 steps between when the duty cycle = 1% and when the duty cycle = 100%. For a fixed constant (k = 1.075), the logarithmic curve can be fixed, so the duty cycle value for the 64 points can be calculated via software and solidified in digital circuitry. The duty cycle for Duty x is equal to (k x Duty (x - 1), where k = 1.075 and the initial duty cycle is 1%.

Figure 11 shows the logarithmic dimming curve.

Figure 11: Logarithmic Dimming Curve

If the configurable cycle duty is not equal to the duty cycle on the curve, one more step is required to change the configured duty cycle.

The automatic logarithmic dimming speed can be set via register 0x02, bits[10:8]. The speed can be set to 4, 8, 16, 32, or 64 points, with a default of 16 points.

Figure 12 shows an example of the logarithmic dimming curve when the duty cycle changes. In this example, the duty cycle follows the sequence below:

- The duty cycle is configured from 0% to 80%

- The duty cycle is reduced to 30%

- The duty cycle is increased to 60%

- The duty cycle is decreased to 15%

- The duty cycle is increased to 50%

Figure 12: Logarithmic Dimming Curve with **Continuous Duty Cycle Changes**

### **Analog Dimming**

During analog dimming, the LED current amplitude changes when the analog dimming register changes. Change the value of the analog dimming register for the corresponding channel via 0x17~0x26, bits[5:0]. The initial value of the analog dimming register is 0x20. though it can be set from 0x00 to 0x3F. When the register increases by 1 bit, the LED current amplitude increases by 0.5%. When the register decreases by 1 bit, the LED current amplitude decreases by 0.5%. ILED can be adjusted to be between 84% and 115.5% of its normal value.

### **Global Dimming Function**

global dimming is disabled. MPQ7225A can execute both analog dimming PWM dimming for and each channel independently. When global dimming is enabled, the dimming duty cycle and amplitude for each channel follows channel 1. This means that it is possible to adjust the LED current for each channel by only adjusting channel 1.

### **Phase Shift**

The MPQ7225A can set the channel-by-channel current phase-shift function. This function is enabled via register 0x01, bits[13:12]. When phase-shift is enabled, the channel x + 1 (x = 1, 2...13) LED current phase shift is 1 $\mu$ s, 5 $\mu$ s, or 20 $\mu$ s after channel x's LED current rising edge.

### **Diagnostic and Fault Indications**

The MPQ7225A supports a variety of diagnostic features, including the following:

- LED short protection

- LED open protection

- ISET pin open/short protection

- Thermal warning and shutdown

The /FS pin is an active-low open drain that is pulled high to an external voltage source via a  $100k\Omega$  resistor. If a protection is triggered, the corresponding fault bit in the register is set.

The LATCH\_EN bit determines the channel behavior and pin behavior. Fault channels should latch off or set to hiccup mode if LED open or short protection occurs (not including V<sub>CC</sub> UVLO, ISET pin open/short protection, thermal warning, and thermal shutdown). The integrated failsafe flag register indicates which channel triggered the protection; if any channel triggers a protection, the related register bit is set to 1.

If LATCH\_EN = 1 (latch-off mode) and a fault is triggered, the fault channel remains off until POR or until EN turns off to reset the channel. Meanwhile, the other channels operate normally. Since the fault register is R1C (the register is cleared after being read once), the fault is not flagged again — even if the fault is present — unless VCC or EN is reset.

If LATCH\_EN = 0 (hiccup mode), the fault channel tries to conduct for 32µs within every 1ms to detect whether the fault has been cleared. Once the fault condition is removed, the /FS pin is released high and the fault flag must be read by the MCU to be cleared . The fault bit and /FS pin cannot be reset until the fault condition is removed. VCC, EN, or EN\_BIT can also reset the fault.

### V<sub>CC</sub> Under-Voltage Lockout (UVLO)

Under-voltage lockout (UVLO) protects the chip

from operating at an insufficient supply voltage.  $V_{\text{CC}}$  UVLO does not trigger the /FS pin. If  $V_{\text{CC}}$  UVLO is triggered, the IC stops working and all the registers are reset.

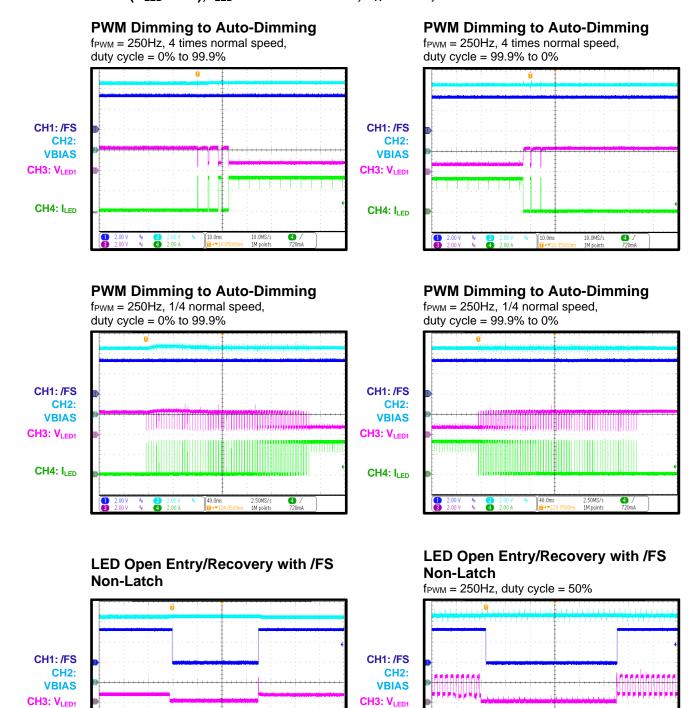

### **LED Open Protection**

The MPQ7225A features integrated LED open diagnostics. If  $V_{LEDx}$  drops below  $V_{LED_O}$  (about 100mV) for longer than 4ms, an open-load condition is detected. If there is an open load on one of the outputs, then the output turns off, the corresponding open fault bit (CHx\_OPEN, where x = 1, 2...16) is set, and /FS is pulled low.

If LATCH\_EN = 1 (latch-off mode), the fault channel remains off until POR or until EN turns off to reset the channel. Meanwhile, the other channels operate normally. /FS is released high once the fault bit is read-cleared by the MCU.

If LATCH\_EN = 0 (hiccup mode), the LED open channel is not latched, and the fault channel tries to conduct for 32µs within every 1ms to detect whether the fault has been cleared. Once the open-load condition is no longer present, the channel turns on again and /FS releases high. The LED open bit remains set until it is read-cleared by the MCU and the open-load condition removed. The open fault bit and /FS pin cannot be reset until the open-load condition is removed.

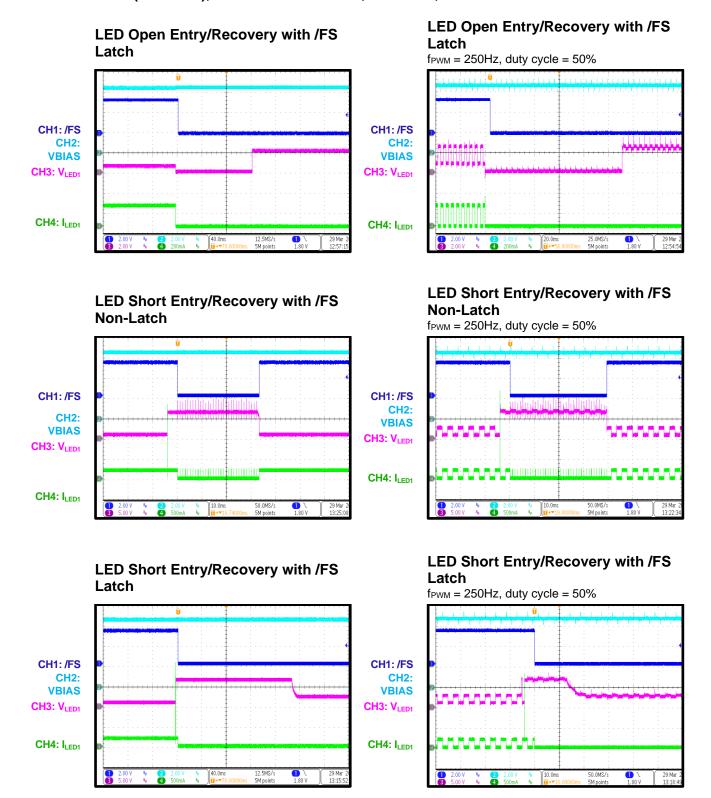

### **LED Short Protection**

During an LED short condition,  $V_{\text{BIAS}}$  -  $V_{\text{LEDX}}$  drops to low. If  $V_{\text{LEDx}}$  exceeds  $V_{\text{LED_S}}$  for 4ms, then LED short protection is triggered. The shorted channel turns off, the corresponding fault bit (CHx\_SHORT) is set, and /FS is pulled low.

If LATCH\_EN = 1 (latch-off mode), the fault channel remains off until VCC or EN go low to reset the channel. Meanwhile, the other channels operate normally. /FS is released high once the fault bit is read-cleared by the MCU.

If LATCH\_EN = 0 (hiccup mode), the LED short channel is not latched, and the fault channel tries to conduct for 32µs within every 1ms to detect whether the fault has been cleared. Just as with an LED open fault, the short fault bit and /FS pin cannot be reset until the short condition is removed.

The LED short protection threshold can be configured via LED SHORT THR, bits[1:0].

There are four potential thresholds:

- If LED SHORT THR = 00, the threshold is

- If LED SHORT THR = 01, the threshold is 3V

- If LED\_SHORT\_THR = 10, the threshold is

- If LED\_SHORT\_THR = 11, the threshold is

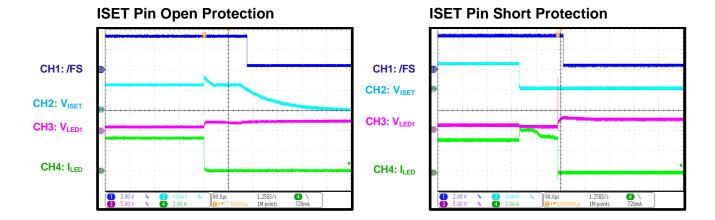

### **ISET Pin Open/Short Protection**

The MPQ7225A implements a current monitor for the ISET resistor to provide open and short fault diagnostics and protection. The device monitors the current (I<sub>ISET</sub>) flowing out of the ISET pin. If I<sub>ISET</sub> exceeds I<sub>ISET</sub> STH (1mA), a short condition asserts. If I<sub>ISET</sub> falls below I<sub>ISET OTH</sub> (5µA), an ISET pin open condition asserts.

ISET open or short protection is a latch-off protection. If an open or short condition is ISET\_PIN\_OPEN detected. the ISET PIN SHORT bit is set, respectively. Then the MPQ7225A latches off and asserts /FS.

The fault bit can be cleared by the MCU, POR, or an EN reset. However, the /FS pin does not release high until POR or until EN goes high.

### Thermal Warning

If the temperature exceeds 150°C, the OT\_WARN bit is set and /FS asserts. The MPQ7225A continues working. /FS releases high once the thermal warning condition is removed. The fault bit remains set until it is cleared by the MCU, POR, or an EN reset.

Thermal warning can be individually masked via OT WARN MASK to prevent the /FS opendrain output from pulling low. Even if the fault is masked, the fault status can still be flagged by the registers.

### Thermal Shutdown

Thermal shutdown prevents the chip from operating at exceedingly high temperatures. If the die temperature exceeds 170°C, all output channels turn off, the OT STD bit is set, and /FS asserts. /FS releases high once the MPQ7225A recovers from thermal shutdown. The fault bit remains set until it is cleared by the MCU, POR, or an EN reset.

Thermal protection is a non-latch protection.

Once the temperature drops 20°C below the thermal shutdown threshold, the MPQ7225A recovers, and the channels turn on using the previous settings without reinitializion.

### **Differential Interface**

The MPQ7225A is designed to operate with a differential interface for automotive lighting applications. By using the differential interface, the onboard MCU controls the settings and timings through a CAN transceiver.

The integrated differential interface is compatible with most CAN transceivers. It can communicate with other CAN transceivers by connecting the DATA+ and DATA- pins to the CAN bus. The interface features a high-speed receiver and transmitter capable of operating up to 2Mbps.

The differential interface is supplied by a 3.3V V<sub>CC</sub> to maintain driver symmetry; the typical output common-mode voltage is 1.65V in the dominant state. The internal common-mode reference is  $V_{CC}$  / 2 = 1.65V to match the dominant state's common-mode output voltage. The transmitter converts a single-ended input (TXD) from the external CAN transceiver to differential outputs for the bus lines (DATA+ and DATA-).

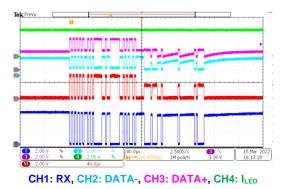

The receiver reads differential inputs from the bus lines (DATA+ and DATA-) and transfers this data as a single-ended output (RXD) to the internal digital circuitry. The receiver consists of a comparator that senses the voltage difference (V<sub>DIFF</sub>) = (DATA+, DATA-) with respect to an internal 1.1V threshold. If VDIFF exceeds 1.1V, a low logic is present at RXD. If V<sub>DIFF</sub> falls below 0.7V, a high logic is present. The receiver always echoes the CAN bus data. Figure 13 shows the differential interface with a read command.

Figure 13: Differential Interface with Read CMD

Figure 14 shows the differential interface with a write command.

Figure 14: Differential Interface with Write CMD

### **Communication Protocol**

The differential interface is a CAN-based protocol supported by most MCUs. Each frame contains multiple bytes, starting with a synchronization byte. The synchronization byte allows LED drivers to synchronize to the master

MCU's frequency, which reduces costs on highprecision oscillators that are commonly used in CAN interfaces. The differential interface can support communication baud rates between 150kbps and 2Mbps.

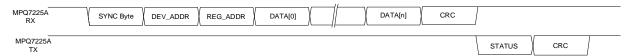

The protocol supports the master and slave with a star-connected topology. The differential interface supports both write and readback commands (CMD).

Table 3 describes the frame structure of a typical 1-byte write action. When the MCU writes data to the MPQ7225A, the MPQ7225A's internal RX receives data from DATA+ and DATA- with a SYNC byte, DEV\_ADDR, REG\_ADDR, DATA, and CRC. Once the MPQ7225A verifies the cyclic redundancy check (CRC), it sends back a status byte and a CRC byte from TX to DATA+ and DATA-. Since the register is 16 bits long, it is transferred with the 8-bit LSB first, following by the 8-bit MSB.

**Table 3: Write Frame**

| ST +       | ST +                      | ST +                        | ST +       | ST +       | ST +       | ST +        | ST +       |

|------------|---------------------------|-----------------------------|------------|------------|------------|-------------|------------|

| 8-Bit + SP | 8-Bit + SP                | 8-Bit + SP                  | 8-Bit + SP | 8-Bit + SP | 8-Bit + SP | 8-Bit + SP  | 8-Bit + SP |

| Sync Byte  | Device<br>address<br>byte | Register<br>address<br>byte | DATA[0]    | DATA[n]    | CRC byte   | Status byte | CRC byte   |

Figure 15 shows a write command with status feedback.

Figure 15: Write Command with Status Feedback

Table 4 describes the frame structure of a typical readback action. The master write frame consists of SYNC, DEV\_ADDR, REG\_ADDR, DATA, and CRC bytes. Once the MPQ7225A

verifies the CRC, the MPQ7225A immediately feeds back the status byte and CRC byte to the MCU through DATA+ and DATA-. The CRC calculation does not include the sync bits.

Table 4: Read Frame

| ST +       | ST +                | ST +                  | ST +       | ST +        | ST +       | ST +       | ST +       |

|------------|---------------------|-----------------------|------------|-------------|------------|------------|------------|

| 8-Bit + SP | 8-Bit + SP          | 8-Bit + SP            | 8-Bit + SP | 8-Bit + SP  | 8-Bit + SP | 8-Bit + SP | 8-Bit + SP |

| Sync Byte  | Device address byte | Register address byte | CRC byte   | Status byte | DATA[0]    | DATA[n]    | CRC byte   |

Figure 16 shows a read command with status feedback.

Figure 16: Read Command with Status Feedback

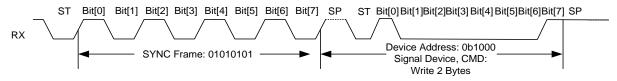

### Synchronization Byte

The first byte transmitted from the MCU to the MPQ7225A is 01010101 (see Table 5). The MCU sends the clock signal to the MPQ7225A by outputting a 01010101 binary code in the first frame. The slave device adaptively uses the

same clock to communicate with the MCU through the same internal, high-frequency clock. To avoid clock drift over time, the synchronization byte is always required for each new instruction transaction. This approach improves communication reliability and saves the cost of an external crystal oscillator.

**Table 5: Synchronization Bytes**

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|----|----|----|----|----|----|----|----|

| 0  | 1  | 0  | 1  | 0  | 1  | 0  | 1  |

Figure 17 shows the timing diagram for synchronization frame and device address frame.

Figure 17: Synchronization Byte

### Device Address Byte

The device address byte follows the synchronization byte (see Table 6).

**Table 6: Device Address Byte**

| Bits   | Bit Name  | Description                                                                                                                                                                                                                                                                                                        |

|--------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D[7:4] | DEV_ADDR  | Sets the device address.                                                                                                                                                                                                                                                                                           |

| D3     | BROADCAST | Sets the broadcast mode.  1: Broadcast mode 0: Single-device only. Broadcast only accepts write commands                                                                                                                                                                                                           |

| D[2:0] | CMD       | Sets the command mode. Since this register is 2 bytes, the MPQ7225A can only support ≥ 2 bytes.  000: Write 1 byte of data 001: Write 2 bytes of data 010: Write 4 bytes of data 011: Write 8 bytes of data 100: Read 1 byte of data 101: Read 2 bytes of data 110: Read 4 bytes of data 111: Read 8 bytes of data |

### Register Address Byte

As a read or write start address, the REG\_ADDR frame follows the device address frame. There are a total of 8 bits of binary code in the register address byte (see Table 7). The register value can range and 0x00 and 0x33, with a 16-bit width.

**Table 7: Register Address Byte**

| Bits   | Bit Name | Description                         |  |  |  |

|--------|----------|-------------------------------------|--|--|--|

| D[7:0] | REG_ADDR | Sets the REG_ADDR register address. |  |  |  |

### Data Byte

For the data bytes, the data frame follows the register address byte. The MPQ7225A supports single data byte or multiple data byte writing in a one-time data transaction. The number of data bytes is defined in the device address byte (see Table 5). There are total of four options: 1, 2, 4, or 8 data bytes.

### **Status Byte**

If no LED short or open condition is detected, then D5 and D4 are set to 0, and D3 is set to 1 to indicate that /FS is high (see Table 8).

**Table 8: Status Byte**

| D7 | D6 | D5       | D4      | D3            | D2 | D1 | D0 |

|----|----|----------|---------|---------------|----|----|----|

| 1  | 0  | CH_SHORT | CH_OPEN | FS_PIN_STATUS | 0  | 0  | 0  |

## **CRC Byte**

The CRC code algorithm for multiple bytes of binary data is based on the polynomial  $x^8 + x^5 + x^4 + 1$ . The CRC code contains an 8-bit binary code, and the initial value is 0xFF. The poly value is 0x31, and the XOR value is 0x00. The CRC calculation does not include the sync bits.

## REGISTER MAP WITHOUT OTP (10) (11)

| Reg.                         | R/W        | Addr.        | Default          | D[15]                                          | D[14]                      | D[13]              | D[12]                 | D[11]                 | D[10]          | D[9]           | D[8]          | D[7]          | D[6]                    | D[5]          | D[4]          | D[3]               | D[2]          | D[1]          | D[0]          |

|------------------------------|------------|--------------|------------------|------------------------------------------------|----------------------------|--------------------|-----------------------|-----------------------|----------------|----------------|---------------|---------------|-------------------------|---------------|---------------|--------------------|---------------|---------------|---------------|

| General Sett                 |            |              |                  | []                                             | -[]                        | _[]                | -[]                   | 1 -[]                 | [.0]           | -[0]           | -[0]          | ,,            | -[0]                    | -[0]          | -1.1          | -[0]               |               | -1.1          | -[0]          |

| SIL_REV                      | R          | 0x00         | 0x0001           |                                                |                            |                    |                       |                       | RESE           | RVED           |               |               |                         |               |               |                    | SIL_          |               |               |

| DEV_CFG_<br>1                | R/W        | 0x01         | 0x0200           |                                                | ED_SHORT_<br>THR SLEW_RATE |                    |                       | PHASE_SHIFT PWM_FREQ  |                |                | RESERVED      |               |                         |               |               | GLOB<br>AL_<br>DIM | FSS_<br>EN    |               |               |

| DEV_CFG_<br>2                | R/W        | 0x02         | 0x6003           | CH_FS<br>_MASK                                 | LATCH<br>_EN               | CRC_<br>EN         | AUTO_<br>DIM_<br>MODE | AUTO_<br>DIM_<br>HOLD | AUT            | AUTO_DIM_SPEED |               |               | RESERVED                |               |               |                    | MOD_<br>EN    | EN_<br>ANA    |               |

| CH_EN                        | R/W        | 0x03         | 0xFFFF           | CH16_<br>EN                                    | CH15_<br>EN                | CH14_<br>EN        | CH13_<br>EN           | CH12_<br>EN           | CH11_<br>EN    | CH10_<br>EN    | CH9_<br>EN    | CH8_EN        | CH7_<br>EN              | CH6_<br>EN    | CH5_<br>EN    | CH4_<br>EN         | CH3_EN        | CH2_<br>EN    | CH1_<br>EN    |

| Diagnostics                  |            |              |                  |                                                |                            |                    |                       |                       |                |                |               |               |                         |               |               |                    |               |               |               |

| DIAG_<br>STAT_1              | R1C        | 0x04         | 0x0000           | CH16_<br>OPEN                                  | CH15_<br>OPEN              | CH14_<br>OPEN      | CH13_<br>OPEN         | CH12_<br>OPEN         | CH11_<br>OPEN  | CH10_O<br>PEN  | CH9_<br>OPEN  | CH8_<br>OPEN  | CH7_<br>OPEN            | CH6_<br>OPEN  | CH5_<br>OPEN  | CH4_<br>OPEN       | CH3_<br>OPEN  | CH2_<br>OPEN  | CH1_<br>OPEN  |

| DIAG_<br>STAT_2              | R1C        | 0x05         | 0x0000           | CH16_<br>SHOR<br>T                             | CH15_<br>SHORT             | CH14_<br>SHOR<br>T | CH13_S<br>HORT        | CH12_<br>SHOR<br>T    | CH11_S<br>HORT | CH10_S<br>HORT | CH9_S<br>HORT | CH8_SH<br>ORT | CH7_S<br>HORT           | CH6_S<br>HORT | CH5_S<br>HORT |                    | CH3_SH<br>ORT | CH2_S<br>HORT | CH1_S<br>HORT |

| DIAG_<br>STAT_3              | R1C        | 0x06         | 0x0000           | RESE OT_ ISET ISET_<br>PIN_S PIN_<br>HORT OPEN |                            |                    | DESE                  |                       |                |                |               | RESERVED      |                         |               |               |                    |               |               |               |

| Dimming an                   |            |              |                  | s                                              |                            |                    |                       |                       |                |                |               |               |                         |               |               |                    |               |               |               |

| CH1_PWM                      | W/R        | 0x07         | 0x0FFF           |                                                |                            | RVED               |                       |                       |                |                |               |               | PWM_DII                 |               |               |                    |               |               |               |

| CH2_PWM<br>CH3_PWM           | W/R<br>W/R | 0x08<br>0x09 | 0x0FFF<br>0x0FFF |                                                |                            | RVED<br>RVED       |                       |                       |                |                |               |               | PWM_DI<br>PWM DI        |               |               |                    |               |               |               |

| CH3_PWM                      | W/R        | 0x09         | 0x0FFF           | 1                                              |                            | RVED               |                       |                       |                |                |               |               | PWM_DI                  |               |               |                    |               |               |               |

| CH5_PWM                      | W/R        | 0x0B         | 0x0FFF           |                                                | RESE                       | RVED               |                       |                       |                |                |               |               | PWM_DI                  | M_5           |               |                    |               |               |               |

| CH6_PWM                      | W/R        | 0x0C         | 0x0FFF           |                                                |                            | RVED               | ·                     |                       |                |                |               |               | PWM_DI                  |               |               |                    |               |               |               |

| CH7_PWM<br>CH8_PWM           | W/R<br>W/R | 0x0D<br>0x0E | 0x0FFF<br>0x0FFF | -                                              |                            | RVED<br>RVED       |                       |                       |                |                |               |               | PWM_DI<br>PWM_DI        |               |               |                    |               |               |               |

| CH9_PWM                      | W/R        | 0x0F         | 0x0FFF           |                                                |                            | RVED               |                       |                       |                |                |               |               | PWM_DI                  |               |               |                    |               |               |               |

| CH10_PW<br>M                 | W/R        | 0x10         | 0x0FFF           |                                                |                            | RVED               |                       |                       |                |                |               |               | PWM_DIN                 |               |               |                    |               |               |               |

| CH11_PW<br>M                 | W/R        | 0x11         | 0x0FFF           |                                                | RESE                       | RVED               |                       | PWM_DIM_11            |                |                |               |               |                         |               |               |                    |               |               |               |

| CH12_PW<br>M                 | W/R        | 0x12         | 0x0FFF           | RESERVED                                       |                            |                    | PWM_DII               |                       |                |                |               |               | M_12                    |               |               |                    |               |               |               |

| CH13_PW<br>M                 | W/R        | 0x13         | 0x0FFF           | RESERVED                                       |                            |                    | PWM_DIN               |                       |                |                |               |               | Л_13                    |               |               |                    |               |               |               |