## 特性

- 通用串行总线（USB）集成

- USB 3.0 和 USB 2.0 外设符合 USB 3.0 规范版本 1.0

- 5 Gbps USB 3.0 PHY 符合 PIPE 3.0

- 高速 On-The-Go (HS-OTG) 主机和外设符合 OTG 补充标准版本 2.0

- 具有 32 个物理端点

- 支持电池充电规范版本 1.1 以及辅助充电器适配器 (ACA) 检测

- 通用可编程接口 (GPIF™ II)

- 可编程的 100 MHz GPIF II 能连接多种类型的外部器件

- 包含 8 位和 16 位的数据总线

- 多达 16 种可配置的控制信号

- 支持大容量存储

- SD 3.0 (SDXC) UHS-1

- eMMC 4.41

- 两个端口可支持大小多达 2 TB 的存储卡。

- 对 RAID0 和 RAID1 提供内置 RAID 支持

- 使用两个安全数字 I/O (SDIO 3.0) 端口扩展系统 I/O

- 支持附加的 USB 储存 (UAS)、USB 大容量存储类别 (MSC)、人机界面设备 (HID)、全速外设以及 Turbo-MTP™

- 无障碍访问 32 位 CPU

- 运行频率为 200 MHz 的 ARM926EJ 内核

- 大小分别为 512 KB 或 256 KB 的嵌入式 SRAM

- 另外，还可连接下列外设

- 频率为 1 MHz 的 I<sup>2</sup>C 主控制器

- 采样频率为 32 kHz、44.1 kHz 和 48 kHz 的 I2S 主设备 (仅用于发送器)

- 支持速度高达 4 Mbps 的 UART

- 频率为 33 MHz 的 SPI 主设备

- 多种时钟输入频率可供选择

- 19.2、26、38.4 和 52 MHz

- 支持 19.2 MHz 的晶振输入

- 内核断电模式下功耗超低

- 打开 VBATT 时，电流消耗低于 60 μA

- 关闭 VBATT 时，电流消耗低于 20 μA

- 内核和 I/O 各有独立的供电区域

- 内核的工作电压为 1.2 V

- I2S、UART 和 SPI 的工作电压为 1.8 到 3.3 V

- I<sup>2</sup>C 的工作电压为 1.2 V

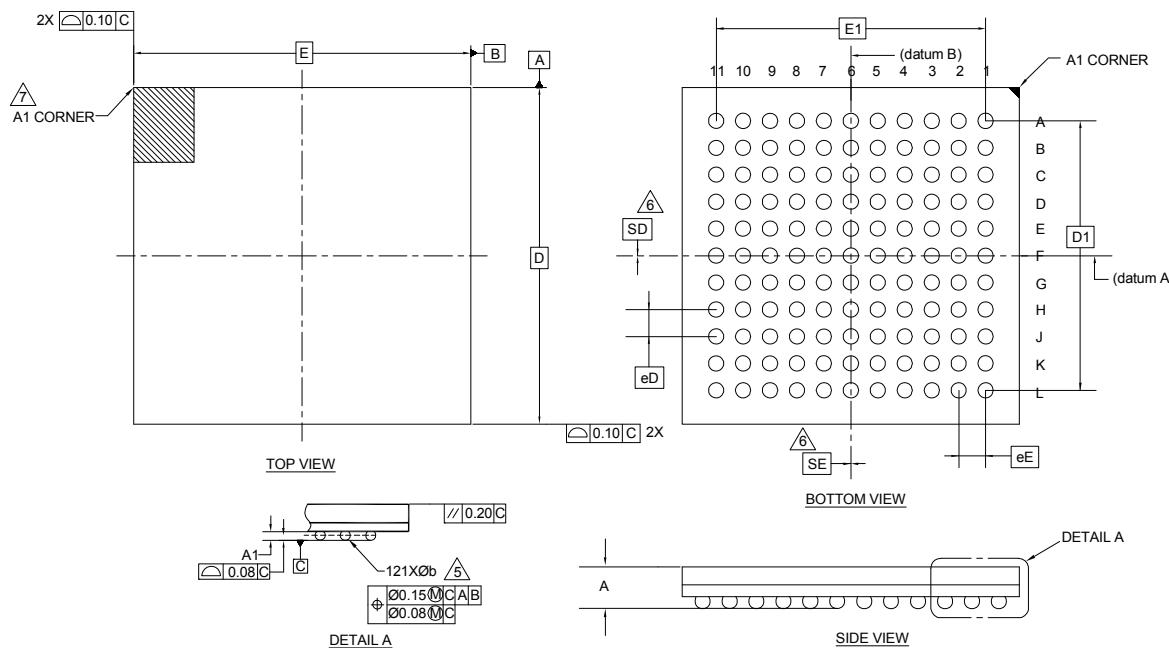

- 10 mm × 10 mm, 0.8 mm 间距 (pitch) 无铅球栅阵列 (BGA) 封装

- 通过 EZ-USB® 软件和开发套件 (DVK)，可轻松进行代码开发

## 应用

- 数字视频摄录机

- 数字摄像机

- 打印机

- 扫描仪

- 视频采集卡

- 测试和测量设备

- 监控摄像机

- 个人导航设备

- 医疗成像设备

- 视频 IP 电话

- 便携式媒体播放器

- 工业摄像机

- RAID 控制器

- 模块上的 USB 磁盘

## 功能描述

- 请点击[这里](#)，了解完整的相关资料

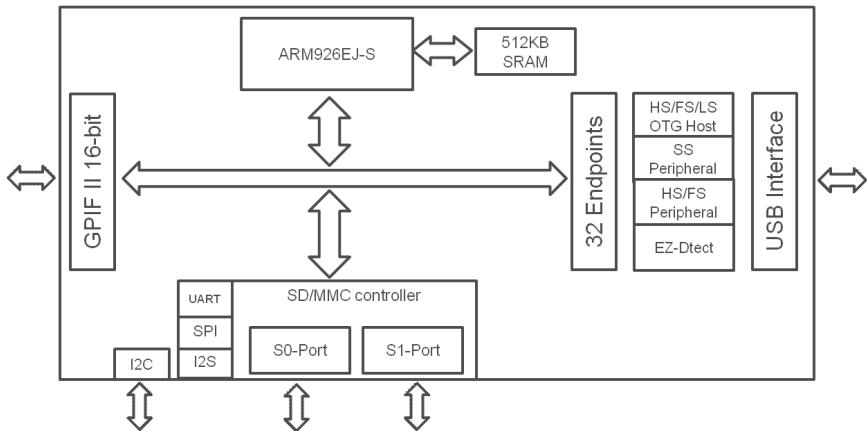

## 逻辑框图

## 更多信息

赛普拉斯在 [www.cypress.com](http://www.cypress.com) 上提供了详尽的数据，可以为您的设计方案选择正确的器件；同时也可以帮助您快速而有效的将我们的器件集成进入您的设计方案。有关资料的完整列表，请参阅知识库文章 [KBA87889, 如何设计 FX3/FX3S](#)。

- 概述: [USB组合](#) , [USB路线图](#)

- USB 3.0产品选择: [FX3](#), [FX3S](#), [CX3](#), [HX3](#), [WestBridge Benicia](#)

- 应用笔记: 赛普拉斯提供了大量的USB应用笔记，涵盖从基本到高级水平范围广泛的话题。以下是开始使用FX3的推荐的应用笔记：

- [AN75705](#) – 开始使用EZ-USB FX3

- [AN76405](#) – EZ-USB FX3 启动选择

- [AN70707](#) – EZ-USBFX3/FX3S硬件设计指南以及原理图清单

- [AN65974](#) – 使用EZ-USB FX3从设备FIFO接口进行设计

- [AN75779](#) – 在USB视频类（UVC）框架中，如何利用EZ-USB FX3实现图像传感器接口

- [AN86947](#) – 使用EZ-USB FX3优化USB 3.0 吞吐量

- [AN84868](#) – 使用赛普拉斯EZ-USB FX3通过USB配置FPGA

- [AN68829](#) – EZ-USB FX3的从属FIFO接口：5位地址模式示例

- [AN73609](#) – EZ-USB FX2LP/FX3 在Linux上的开发批量循环示例

## EZ-USB FX3 软件开发套件

赛普拉斯为 FX3 提供完整的软件和固件堆栈，以便将超高速 USB 轻松集成到任何嵌入式应用程序中。软件开发工具包 (SDK) 附带了工具，驱动程序和[应用程序示例](#)，有助于加速应用程序开发。

## GPIF™ II 设计器

[GPIF II 设计器](#)是一个图形软件，设计人员可以配置 EZ-USB FX3 USB 3.0 设备控制器的 GPIF II 接口。该工具允许用户从赛普拉斯提供的五个接口中选择一个，或者从头开始创建自己的 GPIF II 接口。此外赛普拉斯提供了行业标准接口，如异步和同步从属 FIFO，异步和同步 SRAM 以及异步 SRAM。在系统中已经具有这些预定义接口之一的设计者可以简单地选择这些接口，从诸如总线宽度（x8,16, x32）的永久性，时钟设置，编译接口。该工具为需要定制界面的用户精简了三步 GPIF 界面开发流程。用户可以先选择他们的引脚配置和标准参数。然后，他们可以使用可配置动作来设计虚拟状态机。最后，用户可以查看输出时钟信号来验证它是否与预期的时钟匹配。一旦三步过程完成，接口就可以编译并与 FX3 集成。

- [AN77960](#) – EZ-USB FX3 高速USB主机控制器介绍

- [AN76348](#) – EZ-USB FX3 和 FX2LP应用中的差异化设计

- [AN89661](#) – 使用EZ-USB FX3S实现USB RAID 1 磁盘设计

- 程序示例:

- [高速USB](#)

- [全速USB](#)

- [超高速USB](#)

- 技术参考手册 (TRM) :

- [EZ-USB FX3 技术参考手册](#)

- 开发套件:

- [CYUSB3KIT-003](#), EZ-USB FX3 超高速资源管理工具包

- [CYUSB3KIT-001](#), EZ-USB FX3 开发套件

- 模式: [IBIS](#)

## 目录

|                             |           |                           |           |

|-----------------------------|-----------|---------------------------|-----------|

| 功能概述 .....                  | 4         | 功耗模式 .....                | 12        |

| 应用示例 .....                  | 4         | 配置选项 .....                | 15        |

| <b>USB 接口 .....</b>         | <b>5</b>  | 数字 I/O .....              | 15        |

| OTG .....                   | 5         | 通用输入 / 输出 (GPIO) 数目 ..... | 15        |

| 重新枚举 .....                  | 6         | 系统电平 ESD .....            | 15        |

| EZ-Detect .....             | 6         | 引脚说明 .....                | 16        |

| VBUS 过电压保护 .....            | 6         | 最大绝对额定值 .....             | 20        |

| Carkit UART 模式 .....        | 6         | 运行条件 .....                | 20        |

| <b>主机处理器接口 (P 端口) .....</b> | <b>7</b>  | 直流规范 .....                | 20        |

| GPIF II .....               | 7         | 交流电时序参数 .....             | 22        |

| 从设备 FIFO 接口 .....           | 7         | GPIF II 时序 .....          | 22        |

| 异步 SRAM .....               | 7         | 异步 SRAM 时序 .....          | 25        |

| 异步地址 / 数据复用式接口 .....        | 8         | 用于异步访问的 ADMux 时序 .....    | 28        |

| 同步 ADMux 接口 .....           | 8         | 同步 ADMux 时序 .....         | 30        |

| 处理器 MMC (PMMC) 从设备接口 .....  | 8         | 从设备 FIFO 接口 .....         | 33        |

| <b>CPU .....</b>            | <b>9</b>  | 同步从设备 FIFO 写序列说明 .....    | 34        |

| <b>存储端口 (S 端口) .....</b>    | <b>9</b>  | 异步从设备 FIFO 读序列说明 .....    | 35        |

| SD/MMC 时钟停止 .....           | 9         | 异步从设备 FIFO 写序列说明 .....    | 36        |

| SD_CLK 输出时钟停止 .....         | 9         | 存储端口时序 .....              | 39        |

| 插入及移除存储卡检测 .....            | 10        | 串行外设时序 .....              | 42        |

| 写保护 (WP) .....              | 10        | <b>复位序列 .....</b>         | <b>47</b> |

| SDIO 中断 .....               | 10        | <b>封装图 .....</b>          | <b>48</b> |

| SDIO 读取 — 等待特性 .....        | 10        | <b>订购信息 .....</b>         | <b>49</b> |

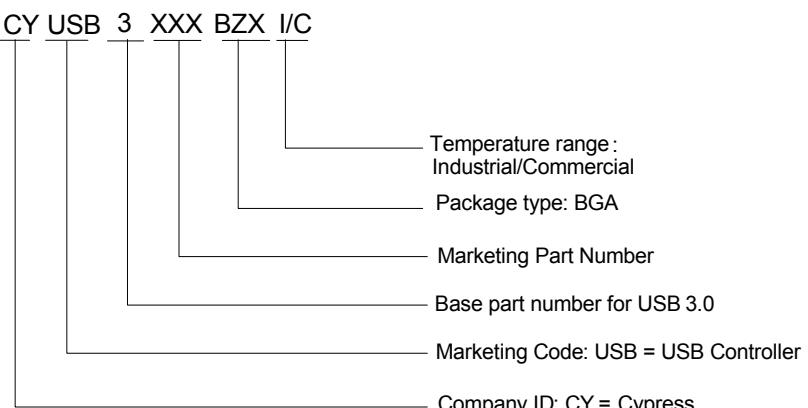

| <b>JTAG 接口 .....</b>        | <b>10</b> | 订购代码定义 .....              | 49        |

| <b>其他接口 .....</b>           | <b>10</b> | <b>缩略语 .....</b>          | <b>50</b> |

| UART 接口 .....               | 10        | <b>文档规范 .....</b>         | <b>50</b> |

| I2C 接口 .....                | 10        | 测量单位 .....                | 50        |

| I2S 接口 .....                | 10        | <b>文档修订记录页 .....</b>      | <b>51</b> |

| SPI 接口 .....                | 10        | <b>销售、解决方案和法律信息 .....</b> | <b>52</b> |

| <b>引导选项 .....</b>           | <b>10</b> | 全球销售和设计支持 .....           | 52        |

| <b>复位 .....</b>             | <b>11</b> | 产品 .....                  | 52        |

| 硬复位 .....                   | 11        | PSoC® 解决方案 .....          | 52        |

| 软复位 .....                   | 11        | 赛普拉斯开发者社区 .....           | 52        |

| <b>时钟 .....</b>             | <b>11</b> | 技术支持 .....                | 52        |

| 32 kHz 看门狗定时器时钟输入 .....     | 12        |                           |           |

| <b>电源 .....</b>             | <b>12</b> |                           |           |

## 功能概述

赛普拉斯 EZ-USB FX3S 是新一代 USB 3.0 外设控制器，可提供集成和灵活的功能。FX3S 具有一个完全可配置的并行通用可编程接口 GPIF II，它能够与任何处理器、ASIC 或 FPGA 连接。GPIF II 是赛普拉斯旗舰 USB 2.0 产品 FX2LP 中所使用 GPIF 的改进版本。它可轻松无缝地连接到多种常用接口，比如异步 SRAM、异步和同步地址数据复用式接口以及并行 ATA。FX3S 集成了 USB3.0 和 USB2.0 物理层 (PHY) 以及 32 位 ARM926EJ-S 微处理器，因此具有强大的数据处理能力，并可用于构建自定义应用。本产品采用了一种架构，使从 GPIF II 到 USB 接口的数据传输速度可达 185 MBps。

FX3S 集成了一个存储控制器，并且支持其存储端口上两个独立的大容量存储器。它也支持 SD 3.0 和 eMMC 4.41 存储卡。并且这些端口还支持 SDIO 功能。FX3 在 SD 或 eMMC 具有可支持 RAID 0 和 RAID 1 的内置 RAID。

FX3 内部具有一个集成的 USB 2.0 OTG 控制器，这可以使 FX3 在某些应用中扮演两个角色。例如，在一个应用中，EZ-USB FX3S 可以作为 OTG 主机控制 MSC 设备，同时可以作为 HID 设备。FX3S 具有大小为 512 KB 或 256 KB 的片上 SRAM，用于存储代码和数据。EZ-USB FX3 还具有可连接至 UART、SPI、I<sup>2</sup>C 和 I<sup>2</sup>S 等串行外设的接口。FX3S 带有应用开发工具。软件开发套件中带有应用示例，从而能够加快产品的上市时间。

FX3S 符合 USB 3.0 v1.0 规范，并可向下与 USB 2.0 相兼容。本设备还符合电池充电规范版本 1.1 以及 USB 2.0 OTG 规范版本 2.0。

## 应用示例

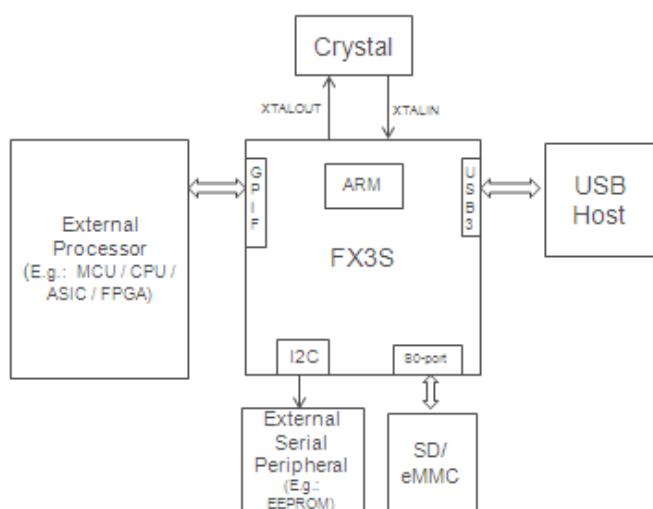

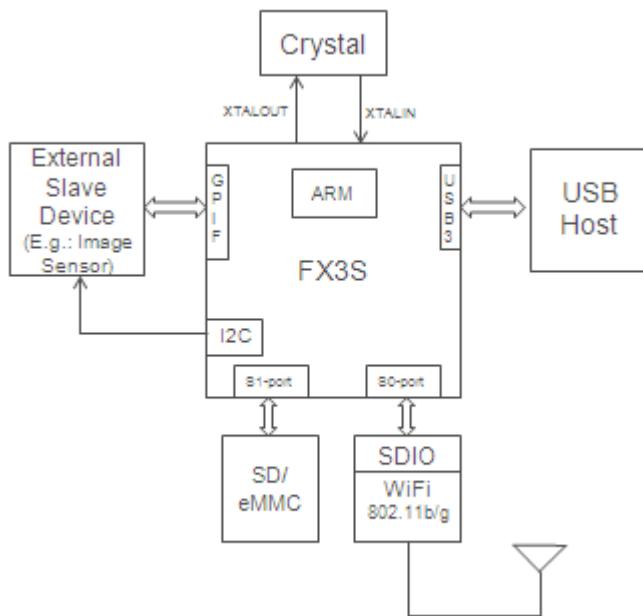

在典型的应用中（请参见图 1），可将 FX3S 作为一个协处理器使用，将其连接一个管理系统级功能的外部处理器。图 2 显示的是 FX3S 作为主处理器时典型的应用框图。

图 1. EZ-USB FX3S 作为协处理器

### 注释：

- 假设 GPIF II 是针对 16 位的数据总线进行配置（仅适用于一些器件型号；请参考 第 49 页上的订购信息），同步接口的运行频率为 100 MHz。该数字还包含协议开销。

图 2. EZ-USB FX3S 作为主处理器

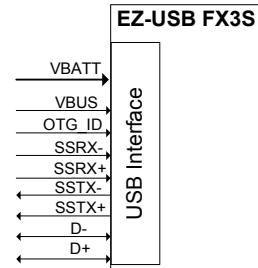

## USB 接口

FX3S 与下面的规范兼容，同时支持下面各性能：

- 支持符合 USB 3.0 规范版本 1.0 的 USB 外设功能，并可向下与 USB 2.0 规范相兼容。

- 符合 OTG 补充标准版本 2.0。它支持高速、全速和低速 OTG 双角色器件功能。作为一个外设，FX3S 能够执行超高速、高速以及全速的数据传输。作为主机，它能够实现高速、全速以及低速传输功能。

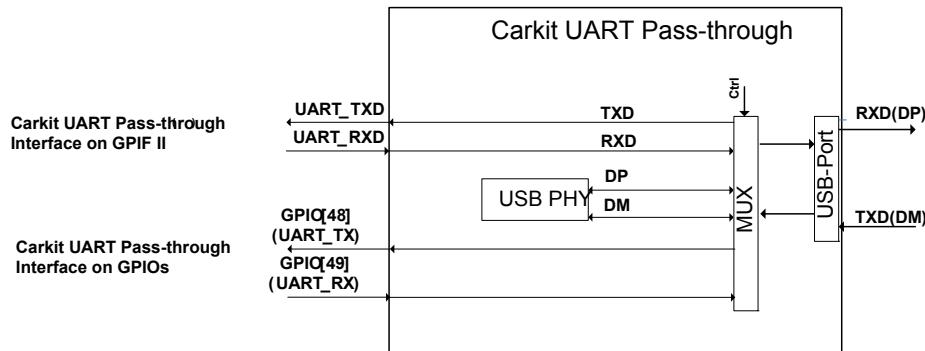

- 按照 CEA-936A 规格，在 USB D+/D- 行上支持 CarKit Pass-through UART 功能。

- 支持多达 16 个输入端点和 16 个输出端点。

- 支持 USB 3.0 的流特性。它还支持 USB 连接的 SCSI (UAS) 器件类别，能优化大容量存储性能。

- 作为 USB 外设时，FX3S 支持 UAS、USB 视频类别 (UVC)、大容量存储类别 (MSC) 和媒体传输协议 (MTP) 等 USB 外设类别。当完全由器件外部的主机处理器进行处理时，本产品作为 USB 外设仅在接通模式支持所有其他类型的器件。

- 作为 OTG 主机时，FX3S 支持 MSC 和 HID 等器件类别。

**注意：**当 USB 端口未被占用时，可禁用 PHY 和收发器以降低功耗。

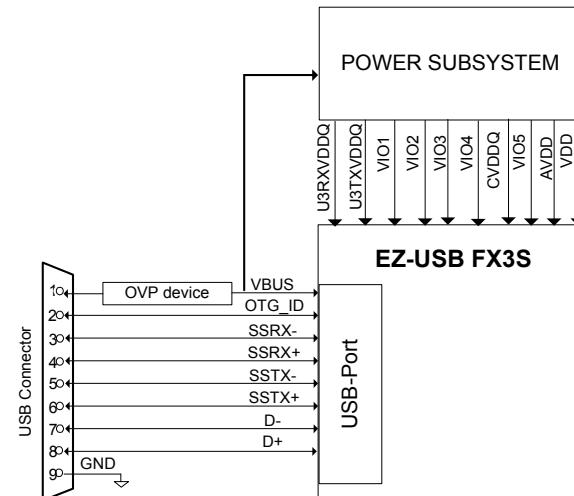

图 3. USB 接口信号

## OTG

FX3S 符合 OTG 规范版本 2.0。在 OTG 模式下，FX3S 支持 A 器件模式和 B 器件模式，并支持数据的控制传输、中断传输、批量传输和同步传输。

在 OTG A 器件模式下，FX3S 需要外部电荷泵（独立或 PMIC 集成）给 VBUS 供电。

实现 OTG 主机的目标外设类别列表中包括 MSC 和 HID 类器件。

FX3S 不支持连接检测协议 (ADP)

### OTG 连接

在 OTG 模式下，可以将 FX3S 配置为支持 A、B 或双角色器件。它可以与下面各项进行连接：

- ACA 器件

- 目标 USB 外设

- 具有 SRP 功能的 USB 外设

- 具有 HNP 功能的 USB 外设

- OTG 主机

- 具有 HNP 功能的主机

- OTG 器件

### 重新枚举

由于 FX3S 为软配置，因此一个芯片具有多个不同的 USB 器件特征。

首次插入 USB 时，FX3S 将自动枚举赛普拉斯供货商 ID (0x04B4)，并通过 USB 接口下载固件和 USB 描述符。下载的固件可执行电力断开和电力连接操作。之后，CX3 会作为下载信息定义的器件再次进行枚举。这个专有的两步流程，称作重新枚举，在器件插入时即时发生。

### EZ-Detect

FX3S 支持 USB 充电器和附件检测 (EZ-Detect)。充电器检测机制符合电池充电规范版本 1.1。除支持该规范版本之外，FX3S 还提供检验 ID 引脚电阻值的硬件支持。

FX3S 可以检测下面各电阻值的范围：

- 低于 10 Ω

- 低于 1 kΩ

- 65 kΩ 至 72 kΩ

- 35 kΩ 至 39 kΩ

- 99.96 kΩ 至 104.4 kΩ (102 kΩ ± 2%)

- 119 kΩ 至 132 kΩ

- 高于 220 kΩ

- 431.2 kΩ 至 448.8 kΩ (440 kΩ ± 2%)

EFX3S 的充电器检测特性可检测专用壁式充电器、主机 / 集线器充电器以及主机 / 集线器。

### VBUS 过电压保护

FX3S 的 VUSB 引脚上的最大输入电压为 6 V。在 VBUS 上，充电器可以提供高达 9 V 的电压。在此情况下，要求使用一个外部过电压保护 (OVP) 器件来防止在 VUSB 上损坏 FX3S。图 4 显示了 VBUS 上所用连接好的 OVP 器件的系统应用框图。请参见直流规范表，了解 VUSB 和 VBATT 的工作电压范围。

图 4. VBUS 所用 OVP 器件的系统图

### Carkit UART 模式

USB 接口支持 Carkit UART 模式 (D+/D- 上的 UART)，以实现非 USB 串行数据传输。该模式遵循 CEA-936A 规范。

在 Carkit UART 模式下，输出信号电压为 3.3 V。配置为 Carkit UART 模式时，UART 的 TXD (输出) 将映射到 D- 行，UART 的 RXD (输入) 将映射到 D+ 行。

在 Carkit UART 模式下，FX3S 将禁用 USB 收发器，而 D+ 和 D- 引脚将作为通过引脚连接至主机处理器的 UART 上。Carkit UART 信号可以连接到 GPIF II 接口，或连接到 GPIO[48] 和 GPIO[49]，如第 7 页上的图 5 中所示。

在该模式下，FX3S 支持高达 9600 bps 的数据速率。

图 5. Carkit UART Pass-through 框图

## 主机处理器接口（P 端口）

通过一个可配置接口，FX3S 可以同多种器件（如传感器、FPGA、主机处理器或桥接芯片）进行通信。FX3S 支持下述各 P 端口接口。

- GPIF II (16 位)

- 从设备 FIFO 接口

- 16 位异步 SRAM 接口

- 16 位异步地址 / 数据复用式 (ADMux) 接口

- 16 位同步地址 / 数据复用式 (ADMux) 接口

- 与 MMC 系统规范、MMCA 技术委员会标准版本 4.2 以及 eMMC 4.3 和 4.4 Pass-Through 引导相兼容的处理器 MMC 从设备接口

- 下面各节内容对这些 P 端口的接口进行了介绍。

### GPIF II

高性能的 GPIF II 接口与 FX2LP 的 GPIF 和从设备 FIFO 接口的功能相似，但其功能更先进。

GPIF II 是一种可编程状态机，其所启用的灵活接口可用作工业标准或专用接口中的主设备或从设备。并行和串行接口均可通过 GPIF II 实现。

下面列出的是 GPIF II 的特性：

- 可作为主设备和从设备使用

- 提供 256 种固件可编程状态

- 支持 8 位和 16 位的并行数据总线

- 接口的工作频率可高达 100 MHz

- 使用一个 16/8 位数据总线时，支持 16 个可配置控制引脚。所有控制引脚可作为输入 / 输出或双向引脚使用。

GPIF II 的状态切换根据控制输入信号发生。控制输出信号是 GPIF II 状态转换所得到的结果。INT# 输出信号可由 GPIF II 控制。请参考 GPIF II Designer 工具的信息。GPIF II 状态机的行为取决于 GPIF II 描述符。设计 GPIF II 描述符，使其符合所需接口的规范。大小为 8 kB 的存储器（独立于 512 kB 的嵌入式 SRAM）专用于 GPIF II 波形，其中 GPIF II 描述符以特殊规格被存储。

赛普拉斯的 GPIF II Designer 工具可实现 GPIF II 描述符的快速开发，并且包含了常用接口的示例。

GPIF II 的实现示例为异步和同步从设备 FIFO 接口。

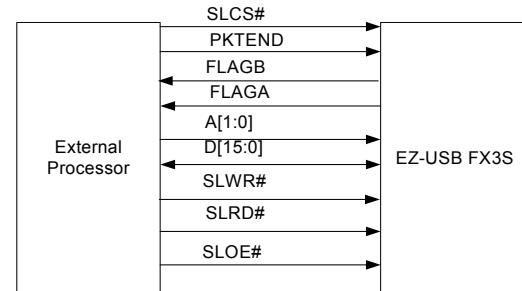

### 从设备 FIFO 接口

从设备 FIFO 接口信号如图 6 中所示。该接口允许外部处理器直接访问多达 4 个 FX3S 内部缓冲区。有关从设备 FIFO 接口的详细信息，请参阅第 33 页。

**注意：**本产品也支持通过从设备 FIFO 接口访问所有 32 个缓冲区。如想了解详细信息，请联系赛普拉斯应用支持。

### 图 6. 从设备 FIFO 接口

Note: Multiple Flags may be configured.

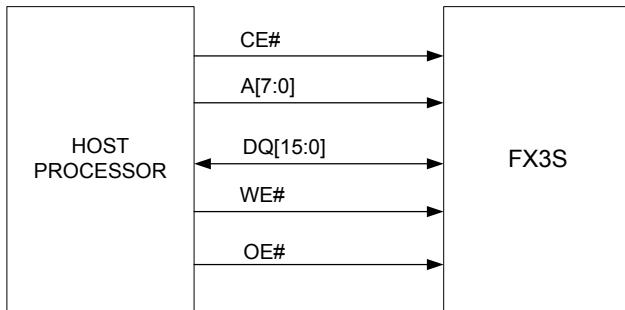

### 异步 SRAM

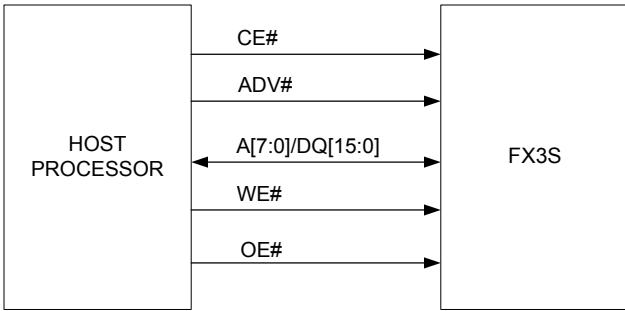

该接口包括了标准的异步 SRAM 接口信号，如第 8 页上的图 7 中所示。该接口用于访问 FX3S 的配置寄存器和缓冲存储器。异步接口信号支持单周期访问和突发访问。

通过最高有效地址位 A[7] 决定访问配置存储器还是访问缓冲存储器。当通过激活地址位 A[7] 来选择访问配置寄存器时，地址总线位 A[6:0] 会指向某个配置寄存器。当解除激活位 A[7] 时，缓冲存储器会按照 P 端口 DMA 传输寄存器所指示的内容进行访问，其传输大小是由 P 端口 DMA 传输大小寄存器指定的。

配有 DMA 控制器的应用处理器在 DMA 传输过程中使用了地址自动递增性能，通过将应用处理器的任何高阶地址线（如 A[15]/A[23]/A[31]）连接到 FX3S 的 A[7]，可以覆盖它。

在异步 SRAM 模式下，当读取缓冲存储器时，FX3S 可支持两个读取缓冲区中下一个数据的方法。在 OE# 的上升沿上读取下一个数据，也可以通过切换最低有效地址位 A[0] 来读取它。

在该模式下，P 端口接口以最小的 32.5 ns 访问周期运行，但是可提供数据速率高达 61.5 MB/s 的接口。

图 7. 异步 SRAM 接口

#### 异步地址 / 数据复用式接口

图 8 显示的是物理 ADMux 存储器接口所包括的各种信号。该接口支持处理器实现复用式地址 / 数据总线。

图 8. ADMux 存储器接口

FX3S 的 ADMux 接口支持 16 位分时复用式地址 / 数据 SRAM 总线。

进行读操作时，需要激活 CE# 和 OE#。

进行写操作时，则要激活 CE# 和 WE#。在写入操作（即写周期的地址和数据阶段）中，OE# 的状态无关紧要。在 WE# 或 CE# 上升沿上，先到的输入数据被锁存。在进行写操作前，通过切换地址有效位（ADV#）来锁存地址。在写操作的地址阶段中，激活地址有效位（ADV#），如第 28 页上的图 19 中所示。

在读 / 写操作的地址阶段内，必须将 ADV# 置于低电平。在读 / 写操作的数据阶段内，则必须将 ADV# 置于高电平，如第 28 页上的图 18 和图 19 中所示。

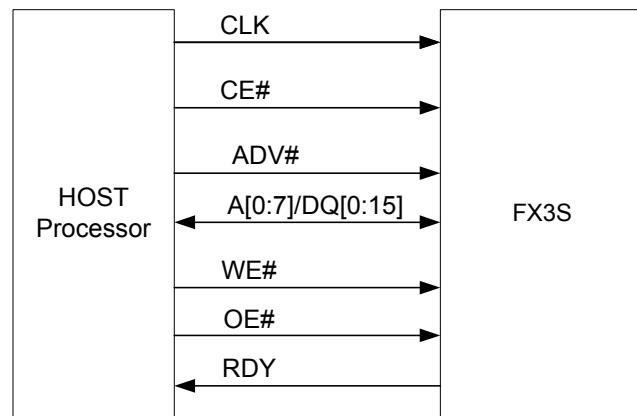

#### 同步 ADMux 接口

FX3S 的 P 端口支持异步地址 / 数据复用式接口。它的运行频率高达 100 MHz，并且支持 16 位数据总线。

来自 FX3S 器件的 RDY 输出信号表示数据已就绪进行读取传输，并且已得到确认，可对其进行写操作。

图 9. 同步 ADMux 接口

请参见 [同步 ADMux 接口](#) 时序图，了解详情。

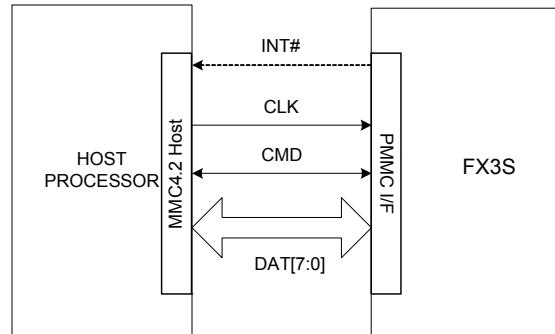

#### 处理器 MMC (PMMC) 从设备接口

FX3S 支持 P 端口上的 MMC 从设备接口。该接口被称为“PMMC”，用以同 S 端口上的 MMC 接口区分开来。

图 10 介绍了用于连接到主机处理器的信号。

PMMC 接口的 GO\_IRQ\_STATE 指令运行 FX3S 能够与异步事件进行通信，且不需要 INT# 信号。可选择是否使用 INT# 信号。

图 10. PMMC 接口配置

MMC 从设备接口的特性如下所述：

- 接口的操作与 MMC 系统规范、MMCA 技术委员会标准版本 4.2 相兼容。

- 支持从连接至 S 端口的 eMMC 器件引导。为 eMMC 器件提供该特性，可使它能在高达 52 MHz 的单倍数据速率 (SDR) 下运行。

- 支持 PMMC 接口在电压范围为 1.7 V ~ 1.95 V 和 2.7 V ~ 3.6 V 内运行。

- 支持 CMD 引脚上的开漏（驱动级接收开漏信号），允许将 GO\_IRQ\_STATE (CMD40) 应用于 PMMC。

- 接口的时钟频率范围为：0 ~ 52 MHz。

- 支持 1 位、4 位或 8 位的操作模式。这种配置取决于 MMC 初始化流程。

- FX3S 对 MMC 4.2 从设备特定的标准初始化阶段的指令做出响应。

- PMMC 模式 MMC 4.2 指令的类别包括 类 0 (基本)、类 2 (模块读取)、类 4 (模块写入)、类 9 (I/O)。

FX3S 支持下面各 PMMC 指令：

- 类 0：基本类型

CMD0、CMD1、CMD2、CMD3、CMD4、CMD6、CMD7、

CMD8、CMD9、CMD10、CMD12、CMD13、CMD15、

CMD19、CMD5 (唤醒支持)

- 类 2：模块读取

CMD16、CMD17、CMD18、CMD23

- 类 4：模块写入

CMD16、CMD23、CMD24、CMD25

- 类 9：I-O

CMD39、CMD40

## CPU

FX3S 配有一个片上 32 位 200 MHz ARM926EJ-S 的内核 CPU。该内核能直接访问 16 kB 指令紧密连接存储器 (TCM) 和 8 kB 数据 TCM。ARM926EJ-S 内核还为固件调试提供了 JTAG 接口。

FX3S 具有下面各优点：

- 集成了存储代码和数据的 512 kB 嵌入式 SRAM，以及 8 kB 的指令缓存和数据缓存。

- 能在多种外设（如 USB、GPIF II、I<sup>2</sup>S、SPI、UART）间实现高效灵活的 DMA 连接。固件只需配置外设间数据访问，这些外设随后由 DMA 结构进行管理。

- 适用于面向 ARM926EJ-S 的行业标准开发工具，可轻松开发应用。

赛普拉斯 EZ-USB FX3S 开发套件中包含 FX3S 固件示例。赛普拉斯 EZ-USB FX3S 软件开发套件中还有可移植到外部处理器的软件 API。

## 存储端口 (S 端口)

FX3S 具有两个独立的存储端口 (S0 端口和 S1 端口)。两个存储端口都支持下面规范：

- MMC 系统规范、MMCA 技术委员会，版本 4.41

- SD 规范，版本 3.0

- 符合 SDIO 规范版本 3.00 的 SDIO 主处理器

两个存储端口都支持下面特性：

### SD/MMC 时钟停止

如果接收来自 SD/MMC/SDIO 的数据时内部缓冲区已满，则 FX3S 允许停止时钟，这样可以节约功耗。

### SD\_CLK 输出时钟停止

传输数据过程中，可以使用内部流控制机制来使能（打开）或禁用（停止）SD\_CLK 时钟。

使用来自系统时钟的时钟分频器可以动态配置 SD\_CLK 输出频率。用户通过寄存器可选择时钟分频值。例如，可以配置得到下面各频率：

- 400 kHz – 适用于 SD/MMC 卡的初始化

- 20 MHz – 适用于频率为 0 ~ 20 MHz 的存储卡

- 24 MHz – 适用于频率为 0 ~ 26 MHz 的存储卡

- 48 MHz – 适用于频率为 0 ~ 52 MHz 的存储卡

(当输入到 FX3S 的时钟频率为 19.2 MHz 或 38.4 MHz 时，那么 SD\_CLK 时钟可支持 48 MHz 的频率)

- 52 MHz – 适用于频率为 0 ~ 52 MHz 的存储卡

(当输入到 FX3S 的时钟频率为 26 MHz 或 52 MHz 时，SD\_CLK 时钟上会支持 52 MHz 频率)

- 100 MHz – 适用于频率为 0 ~ 100 MHz 的存储卡

如果选中了 DDR 模式，则会在 SD 时钟的两个边沿上为数据提供时钟脉冲。DDR 时钟能以高达 52 MHz 的速度运行。

## 插入及移除存储卡检测

FX3S 支持双卡插入和移除检测机制。

- **SD\_D[3]** 数据的使用情况：在系统设计过程中，必须使该信号通过一个大小为  $470\text{ k}\Omega$  的下拉电阻输送给 **SD\_D[3]**。SD 卡具有一个大小为  $10\text{ k}\Omega$  的内部上拉电阻。从 SD/MMC 连接器插入或移除存储卡时，将改变 **SD\_D[3]** 引脚上的电压并触发 CPU 中断。早期 MMC 卡不支持该卡检测机制。

- **S0/S1\_INS** 引脚的使用情况：某些 SD/MMC 连接器为微动的开关提供便利条件，利于存储卡的插入 / 移除检测。该微动开关会连接到 **S0/S1\_INS**。当您从 SD/MMC 连接器插入或移除存储卡时，它将打开或关闭此微动开关。这样会使触发 CPU 中断的引脚上的电压电平发生变化。假设用于卡检测的微动开关极性和用于写检测的相同。如果电压变为低电平，则表示已经插入了存储卡。两个 S 端口共用 **S0/S1\_INS** 引脚。通过寄存器配置可确定将使用该引脚的端口。此引脚被映射到 **S1VDDQ** 电压；如果 **S0VDDQ** 和 **S1VDDQ** 的电压电平不同，此引脚不能作为 **S1\_INS** 引脚使用。

## 写保护 (WP)

使用 S 端口上的 **S0\_WP/S1\_WP** (SD 写保护) 连接至 SD/MMC 卡连接器的 WP 微动开关。该引脚被内连到 CPU 可访问的 GPIO 上，这样固件才能够检测 SD 卡的写保护。

## SDIO 中断

支持如 SDIO 规范版本 2.00 (2007 年 01 月 30 日) 中所指定的 SDIO 中断功能。

## SDIO 读取 - 等待特性

FX3S 支持 SDIO 规范版本 2.00 (2007 年 01 月 30 日) 中所定义的读取 - 等待以及挂起 - 恢复特性。

## JTAG 接口

FX3S 的 JTAG 接口包含一个标准的 5 引脚接口，用于连接 JTAG 调试器。该调试器可通过 CPU 内核的片上调试电路来调试固件。

ARM926EJ-S 内核的这些业界标准调试工具，可用于 FX3S 应用开发。

## 其他接口

FX3S 支持下列串行外设：

- **UART**

- **I<sup>2</sup>C**

- **I<sup>2</sup>S**

- **SPI**

SPI、UART 和 I<sup>2</sup>S 接口可复用到串行外设端口。

## UART 接口

FX3S 的 UART 接口支持全双工通信。其中包含表 1 中所说明的信号。

表 1. UART 接口信号

| 信号  | 说明   |

|-----|------|

| TX  | 输出信号 |

| RX  | 输入信号 |

| CTS | 流量控制 |

| RTS | 流量控制 |

UART 支持各种波特率，从 300 bps 到 4608 Kbps，可通过固件进行选择。如果使能了流控制，那么只有激活 CTS 输入时，FX3S 的 UART 才会发送数据。此外，当就绪接收数据时，FX3S 的 UART 会设置 RTS 输出信号。

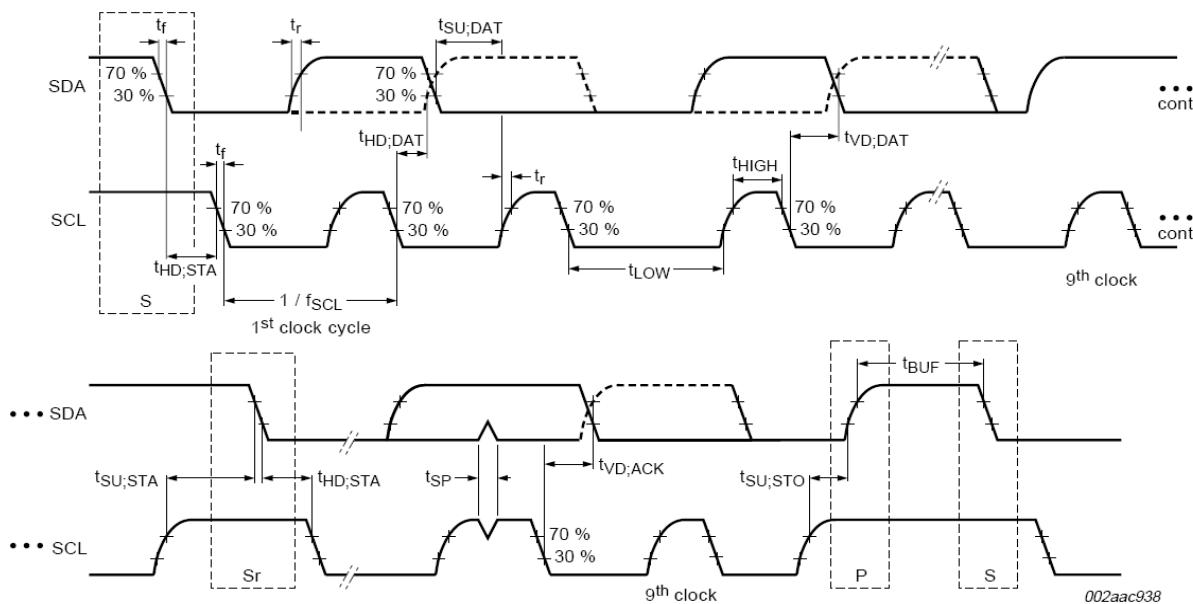

## I<sup>2</sup>C 接口

FX3S 的 I<sup>2</sup>C 接口符合 I<sup>2</sup>C 总线规范修版本 3。该 I<sup>2</sup>C 接口只能作为 I<sup>2</sup>C 主设备使用，因此，会使用它与其他 I<sup>2</sup>C 从设备进行通信。例如，FX3S 可从连接至 I<sup>2</sup>C 接口的 EEPROM 引导，它是可选的引导选项。

FX3S 的 I<sup>2</sup>C 主设备控制器也支持多主控模式功能。

I<sup>2</sup>C 接口采用 VIO5 供电，该电压独立于其他串行外设。这样，I<sup>2</sup>C 接口可以灵活地在不相同的电压下工作，这一点不同于其他串行接口。

I<sup>2</sup>C 控制器所支持的总线频率为 100 kHz、400 kHz 和 1 MHz。当 VIO5 为 1.2 V 时，受支持的最大工作频率为 100 kHz。当 VIO5 为 1.8 V、2.5 V 或 3.3 V 时，受支持的工作频率为 400 kHz 和 1 MHz。I<sup>2</sup>C 控制器支持时钟延长性能，从而允许较慢器件实现流控制。

I<sup>2</sup>C 接口的 SCL 和 SDA 信号都要求外部上拉电阻。上拉电阻必须连接到 VIO5。

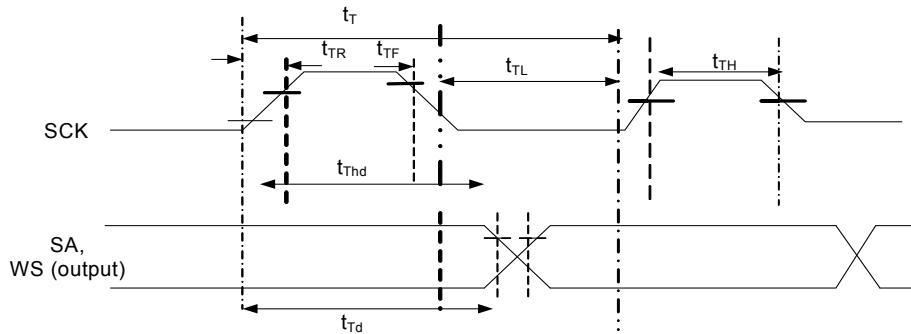

## I<sup>2</sup>S 接口

FX3S 具有 I<sup>2</sup>S 端口，用于支持外部音频解码器件。FX3S 可作为 I<sup>2</sup>S 主设备（仅作为发送器）。I<sup>2</sup>S 接口包括四种信号：时钟行 (I<sup>2</sup>S\_CLK)、串行数据行 (I<sup>2</sup>S\_SD)、单字选择行 (I<sup>2</sup>S\_WS) 和主控系统时钟 (I<sup>2</sup>S\_MCLK)。FX3S 可在 I<sup>2</sup>S\_MCLK 上生成系统时钟输出，或在 I<sup>2</sup>S\_MCLK 上接受外部系统时钟输入。

I<sup>2</sup>S 接口支持的采样频率为 32 kHz、44.1 kHz 和 48 kHz。

## SPI 接口

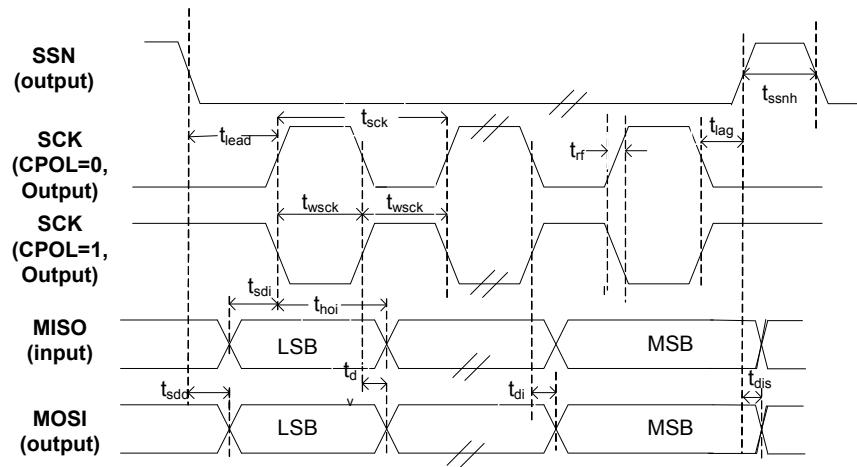

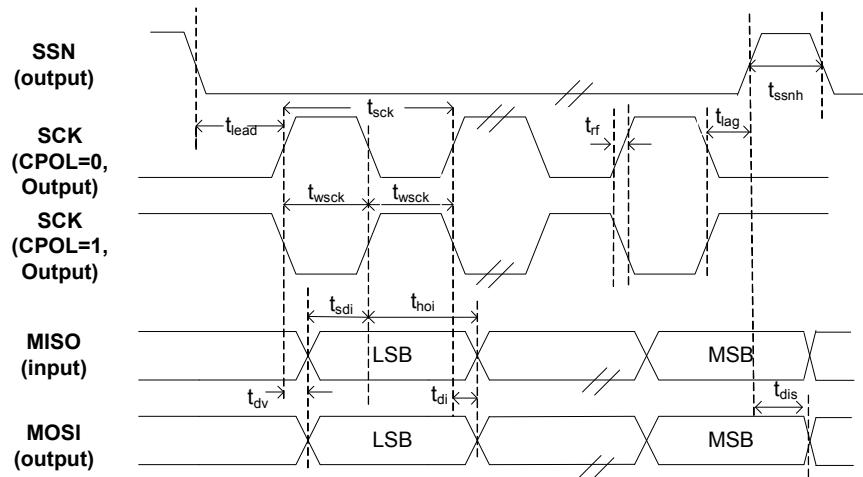

FX3S 支持串行外设端口上的 SPI 主设备接口。最高的工作频率为 33 MHz。

SPI 控制器支持四种使用启动 - 停止时钟信号的 SPI 通信模式（请参见第 45 页上的 SPI 时序规范，了解有关各模式的详细信息）。该控制器只能控制一个主设备，并具有自动控制单一 SSN 信号的性能。它支持从 4 位到 32 位大小的数据操作。

## 引导选项

FX3S 可从多个源加载引导镜像文件，源可通过 PMODE 引脚配置来选择。FX3S 引导选项如下：

- 从 USB 引导

- 从 I<sup>2</sup>C 引导

- 从 SPI（支持的 SPI 器件为 M25P16（16 Mbit）、M25P80（8 Mbit）和 M25P40（4 Mbit））或同类器件引导

- 从 eMMC（S0 端口）引导

- 从 GPIF II 异步 ADMux 模式引导

- 从 GPIF II 同步 ADMux 模式引导

- 从 GPIF II 异步 SRAM 模式引导

- 从 PMMC（P 端口）引导

**表 2. FX3S 引导选项**

| P MODE[2:0] <sup>[2]</sup> | 启动自                             |

|----------------------------|---------------------------------|

| F00                        | 同步 ADMux（16 位）                  |

| F01                        | 异步 ADMux（16 位）                  |

| F10                        | PMMC 旧版                         |

| F11                        | USB 引导                          |

| F0F                        | 异步 SRAM（16 位）                   |

| F1F                        | I <sup>2</sup> C，如失败，则使能 USB 引导 |

| 1FF                        | 仅使用 I <sup>2</sup> C            |

| 0F1                        | SPI，如失败，则使能 USB 引导              |

| 000                        | S0 端口（eMMC），如果失败，则使能 USB 引导     |

| 100                        | S0 端口（eMMC）                     |

## 复位

### 硬复位

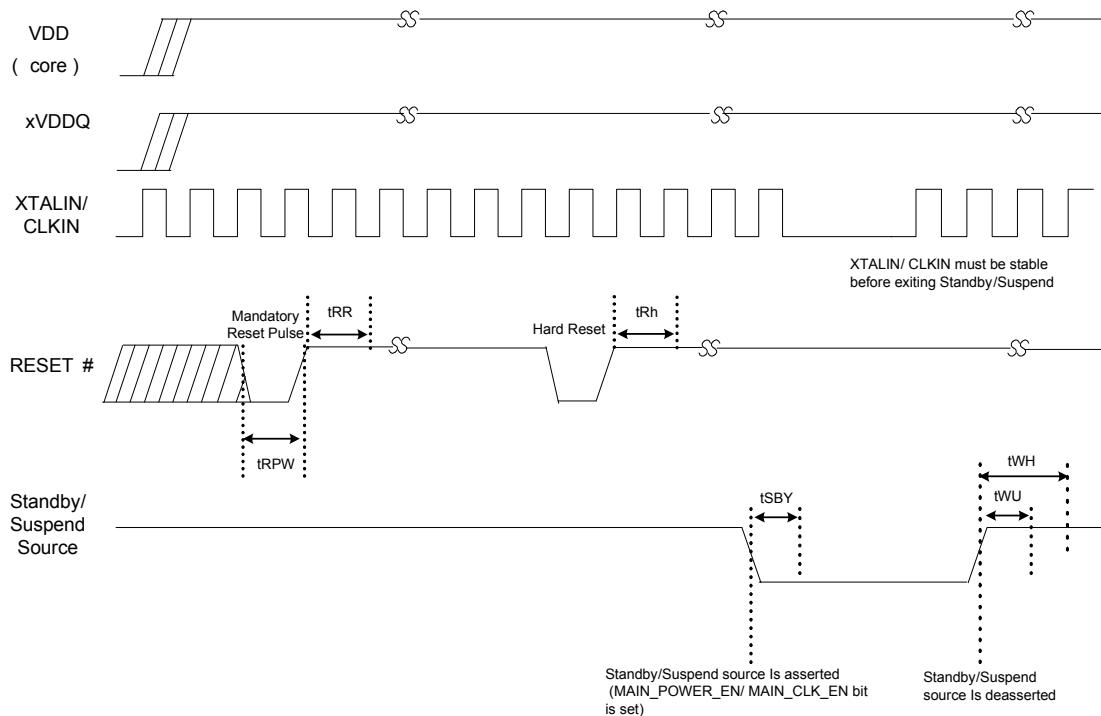

通过激活 FX3S 上的 RESET# 引脚来初始化硬复位。复位序列和时序的具体要求详见第 47 页上的图 31 和第 47 页上的表 18。在硬复位的时间内，所有的 I/O 均为三态的。

### 软复位

在软复位中，处理器将设置 PP\_INIT 控制寄存器中的相应位。软复位有两种类型：

- CPU 复位 — 复位 CPU 程序计数器。CPU 复位后无需重新加载固件。

- 全器件复位 — 该复位与硬复位相同。

- 全器件复位后必须重新加载固件。

## 时钟

FX3S 允许在 XTALIN 和 XTALOUT 引脚之间连接晶振，也允许在 CLKIN 引脚上连接外部时钟。如果没有使用 XTALIN、XTALOUT、CLKIN 和 CLKIN\_32 引脚，可以将它们设为无连接状态。

支持的晶振频率为 19.2 MHz，支持的外部时钟频率为 19.2、26、38.4 和 52 MHz。

FX3S 有一个使用外部 19.2 MHz ( $\pm 100 \text{ ppm}$ ) 晶振（使用晶振选项时）的片上振荡器电路。如果使用了晶振，则需要一个相应的负载电容。请参阅电容使用规范，以确定相应的负载电容。FSLC[2:0]引脚必须进行适当配置，以选择晶振或时钟频率选项。有关配置选项，请参见表 3。

向 FX3S 进行的时钟输入必须符合第 12 页上的表 4 中规定的具体的相位噪声和时序抖动要求。

输入时钟频率同 FX3S 内核或任何器件接口（包括 P 端口和 S 端口）的时钟和数据速率相独立。内部 PLL 按照输入频率使用相应的时钟倍频选项。

**表 3. 晶振 / 时钟频率选择**

| FSLC[2] | FSLC[1] | FSLC[0] | 晶振 / 时钟频率     |

|---------|---------|---------|---------------|

| 0       | 0       | 0       | 19.2 MHz 晶振   |

| 1       | 0       | 0       | 19.2 MHz 输入时钟 |

| 1       | 0       | 1       | 26 MHz 输入     |

| 1       | 1       | 0       | 38.4 MHz 输入时钟 |

| 1       | 1       | 1       | 52 MHz 输入时钟   |

### 注释：

2. F 表示悬空。

**表 4. FX3S 输入时钟规范**

| 参数          | 说明         | 规格  |      | 单位  |

|-------------|------------|-----|------|-----|

|             |            | 最小值 | 最大值  |     |

| 相位噪声        | 100 Hz 偏移  | —   | -75  | dB  |

|             | 1 kHz 偏移   | —   | -104 | dB  |

|             | 100 Hz 偏移  | —   | -120 | dB  |

|             | 100 kHz 偏移 | —   | -128 | dB  |

|             | 1 MHz 偏移   | —   | -130 | dB  |

| 最大频率偏差      |            | —   | 150  | ppm |

| 占空比         |            | 30  | 70   | %   |

| 过冲          |            | —   | 3    | %   |

| 下冲          |            | —   | -3   | %   |

| 上升时间 / 下降时间 |            | —   | 3    | ns  |

### 32 kHz 看门狗定时器时钟输入

FX3S 包含一个看门狗定时器。看门狗定时器可以用于中断 ARM926EJ-S 内核，自动唤醒待机模式下的 FX3S 和复位 ARM926EJ-S 内核。看门狗定时器运行一个 32 kHz 的时钟，该时钟可由专用 FX3S 引脚上的一个外部源选择性地提供。

可通过固件禁用看门狗定时器。

可选的 32 kHz 时钟的输入要求在表 5 中列出。

### 表 5. 32 kHz 时钟输入要求

| 参数          | 最小值 | 最大值       | 单位  |

|-------------|-----|-----------|-----|

| 占空比         | 40  | 60        | %   |

| 频率偏差        | —   | $\pm 200$ | ppm |

| 上升时间 / 下降时间 | —   | 200       | ns  |

## 电源

FX3S 具有下列供电区域。

■ **IO\_VDDQ:** 用于数字 I/O 的一组独立供电区域。这些电源的电压范围为 1.8 V ~ 3.3 V。FX3S 为下列数字 I/O 信号提供了 6 个独立的供电区域（请参考 第 16 页上的引脚说明，了解每个供电区域信号的详情）：

- VIO1: GPIO II I/O

- VIO2: S0 端口供电

- VIO3: S1 端口供电

- VIO4: S1 端口和低速外设（UART/SPI/I2S）供电

- VIO5: I<sup>2</sup>C 和 JTAG 供电（支持的电压范围为 1.2 V ~ 3.3 V）

- CVDDQ: 时钟

- V<sub>PP</sub>: 这是逻辑内核的供电电压。额定供电电压为 1.2 V。该供电区域为内核逻辑电路供电。下列各项也必须使用同样的供电：

- AVDD: 这是 PLL、晶体振荡器和其他内核模拟电路的 1.2 V 供电电压。

- U3TXVDDQ/U3RXVDDQ: 这些是 USB 3.0 接口的 1.2 V 供电电压。

- VBATT/VBUS: 这是 USB I/O 和模拟电路的 3.2 V ~ 6 V 电池供电电压。该供电区域通过 FX3S 的内部电压调节器向 USB 收发器供电。将 VBATT 内部调节为 3.3 V。

## 功耗模式

FX3S 支持下列各功耗模式：

- 正常模式：这是全功能的工作模式。在此模式下，内部 CPU 时钟和内部 PLL 都被使能。

- 正常工作功耗不会超过  $I_{CC}$  内核最高值和  $I_{CC}$  USB 最高值的总和（请参见直流规范表，以查看当前功耗规范）。

- 当相应接口未被使用时，可关闭 I/O 电源 VIO2、VIO3、VIO4 和 VIO5。而在应用程序使用 GPIO II 接口时，始终不能关闭 VIO1。

- 低功耗模式（请参见第 13 页上的表 6）：

- 启用 USB 3.0 PHY 的暂停模式（L1）

- 禁用 USB 3.0 PHY 的暂停模式（L2）

- 待机模式（L3）

- 内核断电模式（L4）

**表 6. 低功耗模式的进入和退出方法**

| 低功耗模式                     | 特性                                                                                                                                                                                                                                                                                                                                                                                                            | 进入方法                                                                                                                                                         | 退出方法                                                                                                                                                                                                                                            |

|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 启用 USB 3.0 PHY 的暂停模式 (L1) | <ul style="list-style-type: none"> <li>■ 此模式下的功耗不会超过 ISB<sub>1</sub></li> <li>■ USB 3.0 PHY 被使能，并处于 U3 模式（为 USB 3.0 规范中所定义的暂停模式之一）。其他时钟均关闭时，该模块可单独使用其内部时钟工作</li> <li>■ 所有 I/O 均维持先前的状态</li> <li>■ 必须保留源和内核的供电用于进行唤醒。所有其他电域都可独立开启 / 关闭</li> <li>■ 必须维持配置寄存器、缓冲存储器以及所有内部 RAM 的状态</li> <li>■ 全部数据操作必须在 FX3S 进入暂停模式前完成（未完成的数据操作的状态将不会得到保存）</li> <li>■ 由于程序计数器并不会复位，因此固件将恢复暂停前的操作（除非通过 RESET# 激活唤醒）</li> </ul>     | <ul style="list-style-type: none"> <li>■ ARM926EJ-S 内核上执行的固件可将 FX3S 置于暂停模式。例如，在 USB 暂停时，固件可使 FX3S 进入暂停模式</li> <li>■ 外部处理器可通过使用邮箱寄存器使 FX3S 进入暂停模式</li> </ul>  | <ul style="list-style-type: none"> <li>■ D+ 切换到低或高</li> <li>■ D- 切换到低或高</li> <li>■ OTG_ID 引脚上更改阻抗</li> <li>■ 恢复 SSRX± 上的状态</li> <li>■ 检测 VBUS</li> <li>■ UART_CTS 电平检测（可编程极性）</li> <li>■ 激活 CTL[0] 的 GPIO II 接口</li> <li>■ 激活 RESET#</li> </ul> |

| 禁用 USB 3.0 PHY 的暂停模式 (L2) | <ul style="list-style-type: none"> <li>■ 该模式下的功耗不会超过 ISB<sub>2</sub></li> <li>■ USB 3.0 PHY 被禁用，USB 接口进入暂停模式</li> <li>■ 时钟均被关闭。PLL 被禁用</li> <li>■ 所有 I/O 均维持先前的状态</li> <li>■ USB 接口维持先前的状态</li> <li>■ 必须保留源和内核的供电用于进行唤醒。所有其他电域都可独立开启 / 关闭</li> <li>■ 必须维持配置寄存器、缓冲存储器以及所有内部 RAM 的状态</li> <li>■ 全部数据操作必须在 FX3S 进入暂停模式前完成（未完成的数据操作的状态将不会得到保存）</li> <li>■ 由于程序计数器并不会复位，因此固件将恢复暂停前的操作（除非通过 RESET# 激活唤醒）</li> </ul> | <ul style="list-style-type: none"> <li>■ ARM926EJ-S 内核上执行的固件可将 FX3S 置于暂停模式。例如，在 USB 暂停时，固件可使 FX3S 进入暂停模式</li> <li>■ 外部处理器可通过使用邮箱寄存器，使 FX3S 进入暂停模式</li> </ul> | <ul style="list-style-type: none"> <li>■ D+ 切换到低或高</li> <li>■ D- 切换到低或高</li> <li>■ OTG_ID 引脚上更改阻抗</li> <li>■ 恢复 SSRX± 上的状态</li> <li>■ 检测 VBUS</li> <li>■ UART_CTS 电平检测（可编程极性）</li> <li>■ 激活 CTL[0] 的 GPIO II 接口</li> <li>■ 激活 RESET#</li> </ul> |

**表 6. 低功耗模式的进入和退出方法（续表）**

| 低功耗模式       | 特性                                                                                                                                                                                                                                                                                                                                                                                                                                       | 进入方法                                                                                    | 退出方法                                                                                                                                               |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| 待机模式 (L3)   | <ul style="list-style-type: none"> <li>■ 该模式下的功耗不会超过 <math>ISB_3</math></li> <li>■ 所有配置寄存器的设置以及程序 / 数据 RAM 的内容将会保留。但是，无法保证缓冲区和数据路径其他部分中的数据（如存在）。因此，应保证在使 FX3S 进入该待机模式前，由外部处理器负责读取所需的数据</li> <li>■ 从待机状态唤醒后，程序计数器将复位</li> <li>■ 通用 I/O 引脚维持其配置情况</li> <li>■ 关闭晶体振荡器</li> <li>■ 关闭内部 PLL</li> <li>■ 关闭 USB 收发器</li> <li>■ 断开供给 ARM926EJ-S 内核的电源。唤醒时，内核重新启动并运行存储在程序 / 数据 RAM 中的程序</li> <li>■ 必须保留源和内核的供电用于进行唤醒。所有其他电域都可独立开启 / 关闭</li> </ul> | <ul style="list-style-type: none"> <li>■ ARM926EJ-S 内核或外部处理器上所执行的固件将配置相应的寄存器</li> </ul> | <ul style="list-style-type: none"> <li>■ 检测 VBUS</li> <li>■ UART_CTS 电平检测（可编程极性）</li> <li>■ 激活 CTL[0] 的 GPIO II 接口</li> <li>■ 激活 RESET#</li> </ul> |

| 内核断电模式 (L4) | <ul style="list-style-type: none"> <li>■ 该模式下的功耗不会超过 <math>ISB_4</math></li> <li>■ 关闭内核电源</li> <li>■ 所有缓冲存储器、配置寄存器和程序 RAM 的状态将不会维持。退出该模式后，请重载固件</li> <li>■ 在该模式下，所有其他电域都可独立开启 / 关闭</li> </ul>                                                                                                                                                                                                                                            | <ul style="list-style-type: none"> <li>■ 关闭 <math>V_{DD}</math></li> </ul>              | <ul style="list-style-type: none"> <li>■ 再次实施 VDD</li> <li>■ 激活 RESET#</li> </ul>                                                                  |

## 配置选项

不同的配置选项用于特定的使用模型。请联系赛普拉斯应用或市场部获得详细信息。

## 数字 I/O

FX3S 在所有数字 I/O 引脚上提供由固件控制的内部上拉或下拉电阻。内部的  $50\text{ k}\Omega$  电阻将引脚上拉为高电平，而内部  $10\text{ k}\Omega$  电阻则将引脚下拉为低电平，以便阻止它们浮动。I/O 引脚可以有下面状态：

- 三态 (High-Z)

- 弱上拉 (通过内部  $50\text{ k}\Omega$  电阻)

- 下拉 (通过内部  $10\text{ k}\Omega$  电阻)

- 低功耗模式下保持 (I/O 值不变)

- JTAG TDI、TMC 和 TRST# 信号有固定的  $50\text{ k}\Omega$  内部上拉电阻，而 TCK 信号有固定的  $10\text{ k}\Omega$  下拉电阻。

应通过内部上拉电阻将所有未使用的 I/O 上拉为高电平。应保持所有的未使用输出为浮动状态。所有 I/O 的驱动强度可为全强度、四分之三的强度、半强度或四分之一的强度。为每个接口独立配置这些驱动强度。

## 通用输入 / 输出 (GPIO) 数目

EZ-USB 在 GPIF II 和串行外设接口上均可实现灵活的引脚配置。GPIF II 接口上任何未使用的控制引脚 (CTL[15] 除外) 都可作为

通用 I/O 使用。与之类似的是，串行外设接口上任何未使用的引脚均可配置为通用 I/O。请参阅 [第 16 页上的引脚说明](#) 部分，了解各引脚配置选项的内容。

所有 GPIF II 和 GPIO 引脚都支持每个引脚  $16\text{ pF}$  的外部负载。

## EMI

FX3S 符合 FCC 15B (美国) 和 EN55022 (欧洲) 电子消费品规定中的 EMI 要求。按照上列规定，FX3S 可承受由干扰源造成的合理 EMI，并继续按预期工作。

## 系统电平 ESD

FX3S 在 USB 接口的 D+、D- 和 GND 引脚上具有内置 ESD 保护。这些端口上的 ESD 保护电平分别为：

- 基于 JESD22-A114 规范的  $\pm 2.2\text{ KV}$  人体模型 (HBM)

- 基于 IEC61000-4-2 的 3A 级标准的  $\pm 6\text{ KV}$  接触放电和  $\pm 8\text{ KV}$  气隙放电

- 基于 IEC61000-4-2 的 4C 级标准的  $\pm 8\text{ KV}$  接触放电和  $\pm 15\text{ KV}$  气隙放电。

这种保护能确保器件在出现最高达到上述电平的 ESD 事件后继续工作。

SSRX+、SSRX-、SSTX+ 和 SSTX- 引脚只有最高为  $\pm 2.2\text{ KV}$  的人体模型 (HBM) 内部 ESD 保护。

图 11. FX3S 脚映射图 (顶视图)

|   | 1        | 2        | 3        | 4        | 5        | 6        | 7        | 8        | 9            | 10           | 11       |

|---|----------|----------|----------|----------|----------|----------|----------|----------|--------------|--------------|----------|

| A | U3VSSQ   | U3RXVDDQ | SSRXM    | SSRXP    | SSTXP    | SSTM     | AVDD     | VSS      | DP           | DM           | NC       |

| B | VIO4     | FSLC[0]  | R_USB3   | FSLC[1]  | U3TXVDDQ | CVDDQ    | AVSS     | VSS      | VSS          | VDD          | TRST#    |

| C | GPIO[54] | GPIO[55] | VDD      | GPIO[57] | RESET#   | XTALIN   | XTALOUT  | R_USB2   | OTG_ID       | TDO          | VIO5     |

| D | GPIO[50] | GPIO[51] | GPIO[52] | GPIO[53] | GPIO[56] | CLKIN_32 | CLKIN    | VSS      | I2C_GPIO[58] | I2C_GPIO[59] | O[60]    |

| E | GPIO[47] | VSS      | VIO3     | GPIO[49] | GPIO[48] | FSLC[2]  | TDI      | TMS      | VDD          | VBATT        | VBUS     |

| F | VIO2     | GPIO[45] | GPIO[44] | GPIO[41] | GPIO[46] | TCK      | GPIO[2]  | GPIO[5]  | GPIO[1]      | GPIO[0]      | VDD      |

| G | VSS      | GPIO[42] | GPIO[43] | GPIO[30] | GPIO[25] | GPIO[22] | GPIO[21] | GPIO[15] | GPIO[4]      | GPIO[3]      | VSS      |

| H | VDD      | GPIO[39] | GPIO[40] | GPIO[31] | GPIO[29] | GPIO[26] | GPIO[20] | GPIO[24] | GPIO[7]      | GPIO[6]      | VIO1     |

| J | GPIO[38] | GPIO[36] | GPIO[37] | GPIO[34] | GPIO[28] | GPIO[16] | GPIO[19] | GPIO[14] | GPIO[9]      | GPIO[8]      | VDD      |

| K | GPIO[35] | GPIO[33] | VSS      | VSS      | GPIO[27] | GPIO[23] | GPIO[18] | GPIO[17] | GPIO[13]     | GPIO[12]     | GPIO[10] |

| L | VSS      | VSS      | VSS      | GPIO[32] | VDD      | VSS      | VDD      | INT#     | VIO1         | GPIO[11]     | VSS      |

## 引脚说明

| FX3S 引脚说明 |          |     |          |              |                |                |          |              |              |

|-----------|----------|-----|----------|--------------|----------------|----------------|----------|--------------|--------------|

| 引脚        | 供电<br>引脚 | I/O | 名称       | P 端口         |                |                |          |              |              |

|           |          |     |          | GPIF II 接口   | 从设备 FIFO<br>接口 | PMMC           | 异步 SRAM  | 异步 ADMux     | 同步 ADMux     |

| F10       | VIO1     | I/O | GPIO[0]  | DQ[0]        | DQ[0]          | MMC_D0         | DQ[0]    | DQ[0]/A[0]   | DQ[0]/A[0]   |

| F9        | VIO1     | I/O | GPIO[1]  | DQ[1]        | DQ[1]          | MMC_D1         | DQ[1]    | DQ[1]/A[1]   | DQ[1]/A[1]   |

| F7        | VIO1     | I/O | GPIO[2]  | DQ[2]        | DQ[2]          | MMC_D2         | DQ[2]    | DQ[2]/A[2]   | DQ[2]/A[2]   |

| G10       | VIO1     | I/O | GPIO[3]  | DQ[3]        | DQ[3]          | MMC_D3         | DQ[3]    | DQ[3]/A[3]   | DQ[3]/A[3]   |

| G9        | VIO1     | I/O | GPIO[4]  | DQ[4]        | DQ[4]          | MMC_D4         | DQ[4]    | DQ[4]/A[4]   | DQ[4]/A[4]   |

| F8        | VIO1     | I/O | GPIO[5]  | DQ[5]        | DQ[5]          | MMC_D5         | DQ[5]    | DQ[5]/A[5]   | DQ[5]/A[5]   |

| H10       | VIO1     | I/O | GPIO[6]  | DQ[6]        | DQ[6]          | MMC_D6         | DQ[6]    | DQ[6]/A[6]   | DQ[6]/A[6]   |

| H9        | VIO1     | I/O | GPIO[7]  | DQ[7]        | DQ[7]          | MMC_D7         | DQ[7]    | DQ[7]/A[7]   | DQ[7]/A[7]   |

| J10       | VIO1     | I/O | GPIO[8]  | DQ[8]        | DQ[8]          | GPIO           | DQ[8]    | DQ[8]/A[8]   | DQ[8]/A[8]   |

| J9        | VIO1     | I/O | GPIO[9]  | DQ[9]        | DQ[9]          | GPIO           | DQ[9]    | DQ[9]/A[9]   | DQ[9]/A[9]   |

| K11       | VIO1     | I/O | GPIO[10] | DQ[10]       | DQ[10]         | GPIO           | DQ[10]   | DQ[10]/A[10] | DQ[10]/A[10] |

| L10       | VIO1     | I/O | GPIO[11] | DQ[11]       | DQ[11]         | GPIO           | DQ[11]   | DQ[11]/A[11] | DQ[11]/A[11] |

| K10       | VIO1     | I/O | GPIO[12] | DQ[12]       | DQ[12]         | GPIO           | DQ[12]   | DQ[12]/A[12] | DQ[12]/A[12] |

| K9        | VIO1     | I/O | GPIO[13] | DQ[13]       | DQ[13]         | GPIO           | DQ[13]   | DQ[13]/A[13] | DQ[13]/A[13] |

| J8        | VIO1     | I/O | GPIO[14] | DQ[14]       | DQ[14]         | GPIO           | DQ[14]   | DQ[14]/A[14] | DQ[14]/A[14] |

| G8        | VIO1     | I/O | GPIO[15] | DQ[15]       | DQ[15]         | GPIO           | DQ[15]   | DQ[15]/A[15] | DQ[15]/A[15] |

| J6        | VIO1     | I/O | GPIO[16] | PCLK         | CLK            | MMC_CLK        | CLK      | CLK          | CLK          |

| K8        | VIO1     | I/O | GPIO[17] | CTL[0]       | SLCS#          | GPIO           | CE#      | CE#          | CE#          |

| K7        | VIO1     | I/O | GPIO[18] | CTL[1]       | SLWR#          | MMC_CMD        | WE#      | WE#          | WE#          |

| J7        | VIO1     | I/O | GPIO[19] | CTL[2]       | SLOE#          | GPIO           | OE#      | OE#          | OE#          |

| H7        | VIO1     | I/O | GPIO[20] | CTL[3]       | SLRD#          | GPIO           | DACK#    | DACK#        | DACK#        |

| G7        | VIO1     | I/O | GPIO[21] | CTL[4]       | FLAGA          | GPIO           | DRQ#     | DRQ#         | DRQ#         |

| G6        | VIO1     | I/O | GPIO[22] | CTL[5]       | FLAGB          | GPIO           | A[7]     | GPIO         | GPIO         |

| K6        | VIO1     | I/O | GPIO[23] | CTL[6]       | GPIO           | GPIO           | A[6]     | GPIO         | RDY          |

| H8        | VIO1     | I/O | GPIO[24] | CTL[7]       | PKTEND#        | GPIO           | A[5]     | GPIO         | GPIO         |

| G5        | VIO1     | I/O | GPIO[25] | CTL[8]       | GPIO           | GPIO           | A[4]     | GPIO         | GPIO         |

| H6        | VIO1     | I/O | GPIO[26] | CTL[9]       | GPIO           | GPIO           | A[3]     | GPIO         | GPIO         |

| K5        | VIO1     | I/O | GPIO[27] | CTL[10]      | GPIO           | GPIO           | A[2]     | ADV#         | ADV#         |

| J5        | VIO1     | I/O | GPIO[28] | CTL[11]      | A1             | CARKIT_UART_RX | A[1]     | GPIO         | GPIO         |

| H5        | VIO1     | I/O | GPIO[29] | CTL[12]      | A0             | CARKIT_UART_TX | A[0]     | GPIO         | GPIO         |

| G4        | VIO1     | I/O | GPIO[30] | PMODE[0]     | PMODE[0]       | PMODE[0]       | PMODE[0] | PMODE[0]     | PMODE[0]     |

| H4        | VIO1     | I/O | GPIO[31] | PMODE[1]     | PMODE[1]       | PMODE[1]       | PMODE[1] | PMODE[1]     | PMODE[1]     |

| L4        | VIO1     | I/O | GPIO[32] | PMODE[2]     | PMODE[2]       | PMODE[2]       | PMODE[2] | PMODE[2]     | PMODE[2]     |

| L8        | VIO1     | I/O | INT#     | INT#/CTL[15] | CTL[15]        | INT#           | INT#     | INT#         | INT#         |

| C5        | CVDDQ    | I   | RESET#   | RESET#       | RESET#         | RESET#         | RESET#   | RESET#       | RESET#       |

| FX3S 引脚说明 |          |     |          |              |          |          |         |          |

|-----------|----------|-----|----------|--------------|----------|----------|---------|----------|

| 引脚        | 供电<br>引脚 | I/O | 名称       | S0 端口        |          |          |         |          |

|           |          |     |          | 8b MMC       | SD+GPIO  | GPIO     |         |          |

| K2        | VIO2     | I/O | GPIO[33] | S0_SD0       | S0_SD0   |          | GPIO    |          |

| J4        | VIO2     | I/O | GPIO[34] | S0_SD1       | S0_SD1   |          | GPIO    |          |

| K1        | VIO2     | I/O | GPIO[35] | S0_SD2       | S0_SD2   |          | GPIO    |          |

| J2        | VIO2     | I/O | GPIO[36] | S0_SD3       | S0_SD3   |          | GPIO    |          |

| J3        | VIO2     | I/O | GPIO[37] | S0_SD4       | GPIO     |          | GPIO    |          |

| J1        | VIO2     | I/O | GPIO[38] | S0_SD5       | GPIO     |          | GPIO    |          |

| H2        | VIO2     | I/O | GPIO[39] | S0_SD6       | GPIO     |          | GPIO    |          |

| H3        | VIO2     | I/O | GPIO[40] | S0_SD7       | GPIO     |          | GPIO    |          |

| F4        | VIO2     | I/O | GPIO[41] | S0_CMD       | S0_CMD   |          | GPIO    |          |

| G2        | VIO2     | I/O | GPIO[42] | S0_CLK       | S0_CLK   |          | GPIO    |          |

| G3        | VIO2     | I/O | GPIO[43] | S0_WP        | S0_WP    |          | GPIO    |          |

| F3        | VIO2     | I/O | GPIO[44] | S0S1_INS     | S0S1_INS |          | GPIO    |          |

| F2        | VIO2     | I/O | GPIO[45] | MMC0_RST_OUT | GPIO     |          | GPIO    |          |

| S1 端口     |          |     |          |              |          |          |         |          |

|           |          |     |          | 8b MMC       | SD+UART  | SD+SPI   | SD+GPIO | GPIO     |

| F5        | VIO3     | I/O | GPIO[46] | S1_SD0       | S1_SD0   | S1_SD0   | S1_SD0  | GPIO     |

| E1        | VIO3     | I/O | GPIO[47] | S1_SD1       | S1_SD1   | S1_SD1   | S1_SD1  | GPIO     |

| E5        | VIO3     | I/O | GPIO[48] | S1_SD2       | S1_SD2   | S1_SD2   | S1_SD2  | GPIO     |

| E4        | VIO3     | I/O | GPIO[49] | S1_SD3       | S1_SD3   | S1_SD3   | S1_SD3  | GPIO     |

| D1        | VIO3     | I/O | GPIO[50] | S1_CMD       | S1_CMD   | S1_CMD   | S1_CMD  | GPIO     |

| D2        | VIO3     | I/O | GPIO[51] | S1_CLK       | S1_CLK   | S1_CLK   | S1_CLK  | I2S_CLK  |

| D3        | VIO3     | I/O | GPIO[52] | S1_WP        | S1_WP    | S1_WP    | S1_WP   | I2S_WS   |

| D4        | VIO4     | I/O | GPIO[53] | S1_SD4       | UART_RTS | SPI_SCK  | GPIO    | GPIO     |

| C1        | VIO4     | I/O | GPIO[54] | S1_SD5       | UART_CTS | SPI_SSN  | GPIO    | GPIO     |

| C2        | VIO4     | I/O | GPIO[55] | S1_SD6       | UART_TX  | SPI_MISO | GPIO    | GPIO     |

| D5        | VIO4     | I/O | GPIO[56] | S1_SD7       | UART_RX  | SPI_MOSI | GPIO    | GPIO     |

| C4        | VIO4     | I/O | GPIO[57] | MMC1_RST_OUT | GPIO     | GPIO     | GPIO    | I2S_MCLK |

| FX3S 引脚说明 |                |     |                  |            |

|-----------|----------------|-----|------------------|------------|

| 引脚        | 供电<br>引脚       | I/O | 名称               | USB 端口     |

| C9        | VBUS/<br>VBATT | I   | OTG_ID           | OTG_ID     |

|           |                |     |                  |            |

| A3        | U3RX<br>VDDQ   | I   | SSRXM            | SSRX-      |

| A4        | U3RX<br>VDDQ   | I   | SSRXP            | SSRX+      |

| A6        | U3TX<br>VDDQ   | O   | SSTXM            | SSTX-      |

| A5        | U3TX<br>VDDQ   | O   | SSTXP            | SSTX+      |

|           |                |     |                  |            |

| A9        | VBUS/<br>VBATT | I/O | DP               | D+         |

| A10       | VBUS/<br>VBATT | I/O | DM               | D-         |

| A11       |                |     | NC               | 无连接        |

|           |                |     |                  | 晶振 / 时钟    |

| B2        | CVDDQ          | I   | FSLC[0]          | FSLC[0]    |

| C6        | AVDD           | I/O | XTALIN           | XTALIN     |

| C7        | AVDD           | I/O | XTALOUT          | XTALOUT    |

| B4        | CVDDQ          | I   | FSLC[1]          | FSLC[1]    |

| E6        | CVDDQ          | I   | FSLC[2]          | FSLC[2]    |

| D7        | CVDDQ          | I   | CLKIN            | CLKIN      |

| D6        | CVDDQ          | I   | CLKIN_32         | CLKIN_32   |

|           |                |     |                  | I2C 和 JTAG |

| D9        | VIO5           | I/O | I2C_GPIO[5<br>8] | I2C_SCL    |

| D10       | VIO5           | I/O | I2C_GPIO[5<br>9] | I2C_SDA    |

| E7        | VIO5           | I   | TDI              | TDI        |

| C10       | VIO5           | O   | TDO              | TDO        |

| B11       | VIO5           | I   | TRST#            | TRST#      |

| E8        | VIO5           | I   | TMS              | TMS        |

| F6        | VIO5           | I   | TCK              | TCK        |

| D11       | VIO5           | O   | O[60]            | 充电器检测输出    |

| FX3S 引脚说明 |                |     |          |                                                                       |

|-----------|----------------|-----|----------|-----------------------------------------------------------------------|

| 引脚        | 供电<br>引脚       | I/O | 名称       | 功耗                                                                    |

| E10       |                | PWR | VBATT    |                                                                       |

| B10       |                | PWR | VDD      |                                                                       |

| A1        |                | PWR | U3VSSQ   |                                                                       |

| E11       |                | PWR | VBUS     |                                                                       |

| D8        |                | PWR | VSS      |                                                                       |

| H11       |                | PWR | VIO1     |                                                                       |

| E2        |                | PWR | VSS      |                                                                       |

| L9        |                | PWR | VIO1     |                                                                       |

| G1        |                | PWR | VSS      |                                                                       |

| F1        |                | PWR | VIO2     |                                                                       |

| G11       |                | PWR | VSS      |                                                                       |

| E3        |                | PWR | VIO3     |                                                                       |

| L1        |                | PWR | VSS      |                                                                       |

| B1        |                | PWR | VIO4     |                                                                       |

| L6        |                | PWR | VSS      |                                                                       |

| B6        |                | PWR | CVDDQ    |                                                                       |

| B5        |                | PWR | U3TXVDDQ |                                                                       |

| A2        |                | PWR | U3RXVDDQ |                                                                       |

| C11       |                | PWR | VIO5     |                                                                       |

| L11       |                | PWR | VSS      |                                                                       |

| A7        |                | PWR | AVDD     |                                                                       |

| B7        |                | PWR | AVSS     |                                                                       |

| C3        |                | PWR | VDD      |                                                                       |

| B8        |                | PWR | VSS      |                                                                       |

| E9        |                | PWR | VDD      |                                                                       |

| B9        |                | PWR | VSS      |                                                                       |

| F11       |                | PWR | VDD      |                                                                       |

| H1        |                | PWR | VDD      |                                                                       |

| L7        |                | PWR | VDD      |                                                                       |

| J11       |                | PWR | VDD      |                                                                       |

| L5        |                | PWR | VDD      |                                                                       |

| K4        |                | PWR | VSS      |                                                                       |

| L3        |                | PWR | VSS      |                                                                       |

| K3        |                | PWR | VSS      |                                                                       |

| L2        |                | PWR | VSS      |                                                                       |

| A8        |                | PWR | VSS      |                                                                       |

|           |                |     |          | 高精度电阻                                                                 |

| C8        | VBUS/<br>VBATT | I/O | R_usb2   | 针对 USB 2.0 的高精度电阻（在该引脚和 GND 之间连接一个 $6.04\text{ k}\Omega \pm 1\%$ 的电阻） |

| B3        | U3TX<br>VDDQ   | I/O | R_usb3   | 针对 USB 3.0 的高精度电阻（在该引脚和 GND 之间连接一个 $200\text{ k}\Omega \pm 1\%$ 的电阻）  |

## 最大绝对额定值

超过最大额定值可能会缩短器件的使用寿命。

|                                                                                                |                                          |                               |

|------------------------------------------------------------------------------------------------|------------------------------------------|-------------------------------|

| 存放温度                                                                                           | .....                                    | -65 °C 到 +150 °C              |

| 供电 (工业级)                                                                                       | .....                                    |                               |

| 环境温度                                                                                           | .....                                    | -40 °C 到 +85 °C               |

| 接地电位的供电电压                                                                                      | V <sub>DD</sub> 、A <sub>VDDQ</sub> ..... | 1.25 V                        |

| V <sub>IO1</sub> 、V <sub>IO2</sub> 、V <sub>IO3</sub> 、V <sub>IO4</sub> 、V <sub>IO5</sub> ..... | 3.6 V                                    |                               |

| U3TX <sub>VDDQ</sub> 、U3RX <sub>VDDQ</sub> .....                                               | 1.25 V                                   |                               |

| 任何输入引脚的直流输入电压.....                                                                             | V <sub>CC</sub> + 0.3                    |                               |

| 应用于高阻态 (High Z) 下<br>的输出直流电压.....                                                              | V <sub>CC</sub> + 0.3                    | (V <sub>CC</sub> 是相应的 I/O 电压) |

| 静电放电电压 ESD 保护电平为:                                                                              |                                          |                               |

| ■ 基于 JESD22-A114 的 ±2.2 KV 人体模型 (HBM)                                                          |                                          |                               |

| ■ D+、D-、GND 引脚和串行外设引脚上的附加 ESD 保护电平                                                             |                                          |                               |

- 基于 IEC61000-4-2 的 3A 级标准的 ±6 KV 接触放电和 ±8 KV 气隙放电，基于 IEC61000-4-2 的 4C 级标准的 ±8 KV 接触放电和 ±15 KV 气隙放电

闩锁电流 ..... > 200 mA

所有 I/O 配置的

最大输出短路电流。 (V<sub>out</sub> = 0 V) ..... -100 mA

## 运行条件

T<sub>A</sub> (有偏差的环境温度)

工业级 ..... -40 °C 到 +85 °C

V<sub>DD</sub>、A<sub>VDDQ</sub>、U3TX<sub>VDDQ</sub>、U3RX<sub>VDDQ</sub>

供电电压 ..... 1.15 V 到 1.25 V

V<sub>BATT</sub> 供电电压 ..... 3.2 V 到 6 V

V<sub>IO1</sub>、V<sub>IO2</sub>、V<sub>IO3</sub>、V<sub>IO4</sub>、C<sub>VDDQ</sub>

供电电压 ..... 1.7 V 到 3.6 V

V<sub>IO5</sub> 供电电压 ..... 1.15 V 到 3.6 V

## 直流规范

| 参数                   | 说明                                     | 最小值                     | 最大值                    | 单位 | 注释                                                                                                                                        |

|----------------------|----------------------------------------|-------------------------|------------------------|----|-------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>DD</sub>      | 内核供电电压                                 | 1.15                    | 1.25                   | V  | 典型值 1.2 V                                                                                                                                 |

| A <sub>VDD</sub>     | 模拟供电电压                                 | 1.15                    | 1.25                   | V  | 典型值 1.2 V                                                                                                                                 |

| V <sub>IO1</sub>     | GPIF II 的 I/O 供电电域                     | 1.7                     | 3.6                    | V  | 典型值为 1.8、2.5 和 3.3 V                                                                                                                      |

| V <sub>IO2</sub>     | S0 端口供电电压范围                            | 1.7                     | 3.6                    | V  | 典型值为 1.8、2.5 和 3.3 V                                                                                                                      |

| V <sub>IO3</sub>     | S1 端口供电电压范围                            | 1.7                     | 3.6                    | V  | 典型值为 1.8、2.5 和 3.3 V                                                                                                                      |

| V <sub>IO4</sub>     | S1 端口和 UART/SPI/I2S 供电电<br>压范围         | 1.7                     | 3.6                    | V  | 典型值为 1.8、2.5 和 3.3 V                                                                                                                      |

| V <sub>BATT</sub>    | USB 供电电压                               | 3.2                     | 6                      | V  | 典型值为 3.7 V                                                                                                                                |

| V <sub>BUS</sub>     | USB 供电电压                               | 4.0                     | 6                      | V  | 典型值为 5 V                                                                                                                                  |

| U3TX <sub>VDDQ</sub> | USB 3.0 1.2 V 供电电压                     | 1.15                    | 1.25                   | V  | 典型值为 1.2 V。该电源需要安装一个大小为 22<br>μF 的旁路电容。                                                                                                   |

| U3RX <sub>VDDQ</sub> | USB 3.0 1.2 V 供电电压                     | 1.15                    | 1.25                   | V  | 典型值为 1.2 V。该电源需要安装一个大小为 22<br>μF 的旁路电容。                                                                                                   |

| C <sub>VDDQ</sub>    | 时钟供电电压                                 | 1.7                     | 3.6                    | V  | 典型值为 1.8 V 和 3.3 V                                                                                                                        |

| V <sub>IO5</sub>     | I <sup>2</sup> C 和 JTAG 的供电电压          | 1.15                    | 3.6                    | V  | 典型值为 1.2、1.8、2.5 和 3.3 V                                                                                                                  |

| V <sub>IH1</sub>     | 输入高电压 1                                | 0.625 × V <sub>CC</sub> | V <sub>CC</sub> + 0.3  | V  | 用于 2.0 V ≤ V <sub>CC</sub> ≤ 3.6 V 时的输入电压 (USB 端<br>口除外)。V <sub>CC</sub> 是相应的 I/O 供电电压。                                                   |

| V <sub>IH2</sub>     | 输入高电平电压 2                              | V <sub>CC</sub> - 0.4   | V <sub>CC</sub> + 0.3  | V  | 用于 1.7 V ≤ V <sub>CC</sub> ≤ 2.0 V<br>时的输入电压 (USB 端口除外)。V <sub>CC</sub> 是相应的<br>I/O 供电电压。                                                 |

| V <sub>IL</sub>      | 输入低电压                                  | -0.3                    | 0.25 × V <sub>CC</sub> | V  | V <sub>CC</sub> 是相应的 I/O 供电电压。                                                                                                            |

| V <sub>OH</sub>      | 输出高电压                                  | 0.9 × V <sub>CC</sub>   | -                      | V  | 以四分之一的驱动强度测试的 I <sub>OH</sub> (最大值) = -<br>100 μA。V <sub>CC</sub> 是相应的 I/O 供电电压。                                                          |

| V <sub>OL</sub>      | 输出低电压                                  | -                       | 0.1 × V <sub>CC</sub>  | V  | 以四分之一的驱动强度测试的 I <sub>OL</sub> (最小值) =<br>+100 μA。V <sub>CC</sub> 是相应的 I/O 供电电压。                                                           |

| I <sub>IX</sub>      | SSTXP/SSXM/SSRXP/SSRXM<br>除外的所有引脚输入漏电流 | -1                      | 1                      | μA | V <sub>DDQ</sub> 上保持的所有 I/O 信号<br>(用于已连接上拉 / 下拉电阻的 I/O, 漏电流以<br>V <sub>DDQ</sub> /R <sub>pu</sub> 或 V <sub>DDQ</sub> /R <sub>PD</sub> 增加) |

## 直流规范 (续表)

| 参数                  | 说明                                     | 最小值 | 最大值 | 单位      | 注释                                                                                                          |

|---------------------|----------------------------------------|-----|-----|---------|-------------------------------------------------------------------------------------------------------------|

| $I_{OZ}$            | SSTXP/SSXM/SSRXP/SSRXM 除外的所有引脚输出高阻态漏电流 | -1  | 1   | $\mu A$ | $V_{DDQ}$ 上保持的所有 I/O 信号                                                                                     |

| $I_{CC\text{ 内核}}$  | 内核和模拟电压工作电流                            | -   | 200 | mA      | 通过 $A_{VDD}$ 和 $V_{DD}$ 的总电流                                                                                |

| $I_{CC\text{ USB}}$ | USB 供电电压工作电流                           | -   | 60  | mA      |                                                                                                             |

| $I_{SB1}$           | 启用 USB 3.0 PHY 的暂停模式期间的总暂停电流 (L1)      | -   | -   | mA      | 内核电流: 1.5 mA<br>I/O 电流: 20 $\mu A$<br>USB 电流: 2 mA<br>用于典型 PVT (典型芯片, 所有电源均处于其各自的额定值, 温度为 25 °C。)           |

| $I_{SB2}$           | 禁用 USB 3.0 PHY 的暂停模式期间的总暂停电流 (L2)      | -   | -   | mA      | 内核电流: 250 $\mu A$<br>I/O 电流: 20 $\mu A$<br>USB 电流: 1.2 mA<br>用于典型 PVT (典型芯片, 所有电源均处于其各自的额定值, 温度为 25 °C。)    |

| $I_{SB3}$           | 待机模式期间的总待机电流 (L3)                      | -   | -   | $\mu A$ | 内核电流: 60 $\mu A$<br>I/O 电流: 20 $\mu A$<br>USB 电流: 40 $\mu A$<br>用于典型 PVT (典型芯片, 所有电源均处于其各自的额定值, 温度为 25 °C。) |

| $I_{SB4}$           | 内核断电模式期间的总待机电流 (L4)                    | -   | -   | $\mu A$ | 内核电流: 0 $\mu A$<br>I/O 电流: 20 $\mu A$<br>USB 电流: 40 $\mu A$<br>用于典型 PVT (典型芯片, 所有电源均处于其各自的额定值, 温度为 25 °C。)  |

| $V_{RAMP}$          | 内核和 I/O 供电的电压斜坡率                       | 0.2 | 50  | V/ms    | 电压斜坡必须是单调的                                                                                                  |

| $V_N$               | $V_{DD}$ 和 I/O 供电中允许的噪声级别              | -   | 100 | mV      | $A_{VDD}$ 除外的所有供电中允许的最大峰 - 峰噪声级别                                                                            |

| $V_{N\_AVDD}$       | $A_{VDD}$ 供电中允许的噪声级别                   | -   | 20  | mV      | $A_{VDD}$ 中允许的最大峰 - 峰噪声级别                                                                                   |

## 交流电时序参数

### GPIF II 时序

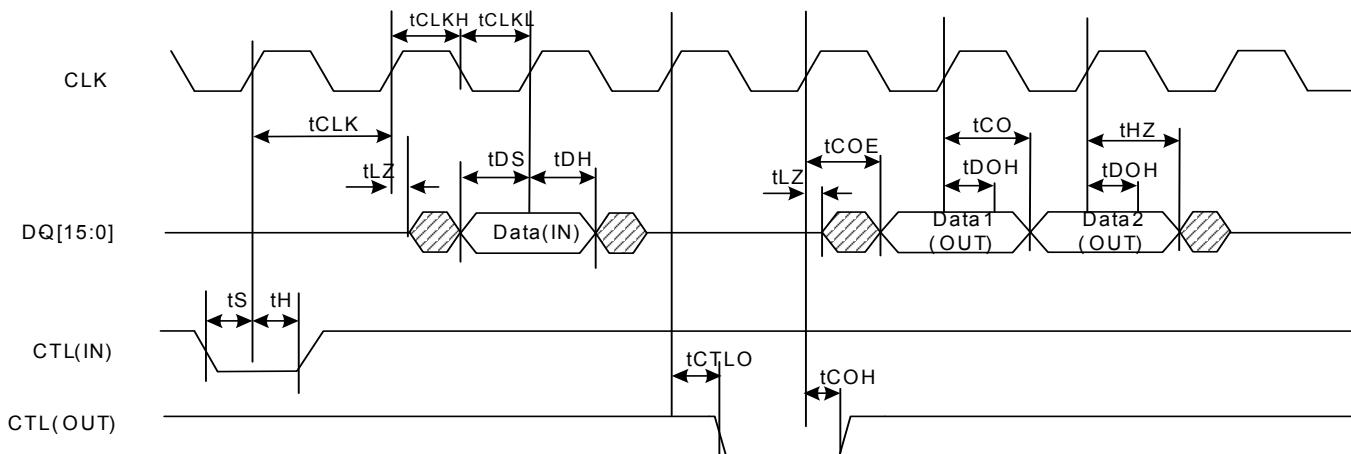

图 12. 同步模式中的 GPIF II 时序

表 7. 同步模式中 GPIF II 时序参数<sup>[3]</sup>

| 参数      | 说明                                                     | 最小值 | 最大值 | 单位  |

|---------|--------------------------------------------------------|-----|-----|-----|

| 频率      | 接口时钟频率                                                 | —   | 100 | MHz |

| tCLK    | 接口时钟周期                                                 | 10  | —   | ns  |

| tCLKH   | 时钟为高电平的时间                                              | 4   | —   | ns  |

| tCLKL   | 时钟为低电平的时间                                              | 4   | —   | ns  |

| tS      | 从 CTL 输入到时钟的建立时间<br>(同步速度 = 1)                         | 2   | —   | ns  |

| tH      | 从 CTL 输入到时钟的保持时间<br>(同步速度 = 1)                         | 0.5 | —   | ns  |

| tDS     | 从数据输入到时钟的建立时间<br>(同步速度 = 1)                            | 2   | —   | ns  |

| tDH     | 从数据输入到时钟保持时间<br>(同步速度 = 1)                             | 0.5 | —   | ns  |

| tCO     | DQ 总线输出时, 从时钟到数据输出的传输延迟 (同步速度 = 1)                     | —   | 8   | ns  |

| tCOE    | DQ 线从三态变更为输出以及 DQ 总线上存在有效数据时, 从时钟到数据输出的传输延迟 (同步速度 = 1) | —   | 9   |     |

| tCTLO   | 从时钟到 CTL 输出的传输延迟 (同步速度 = 1)                            | —   | 8   | ns  |

| tDOH    | 从时钟到数据输出的保持时间                                          | 2   | —   | ns  |

| tCOH    | 从时钟到 CTL 输出的保持时间                                       | 0   | —   | ns  |

| tHZ     | 从时钟到数据为高阻态的时间                                          | —   | 8   | ns  |

| tLZ     | 从时钟到数据位低阻态的时间 (同步速度 = 1)                               | 0   | —   | ns  |

| tS_ss0  | 从 CTL 输入 / 数据输入到时钟的建立时间 (同步速度 = 0)                     | 5   | —   | ns  |

| tH_ss0  | 从 CTL 输入 / 数据输入到时钟的保持时间 (同步速度 = 0)                     | 2.5 | —   | ns  |

| tCO_ss0 | 从时钟到数据输出 / CTL 输出的时间<br>传输延迟 (同步速度 = 0)                | —   | 15  | ns  |

| tLZ_ss0 | 从时钟到数据位低阻态的时间 (同步速度 = 0)                               | 2   | —   | ns  |

注释:

3. 所有参数均由设计保证，并通过特性化进行验证。

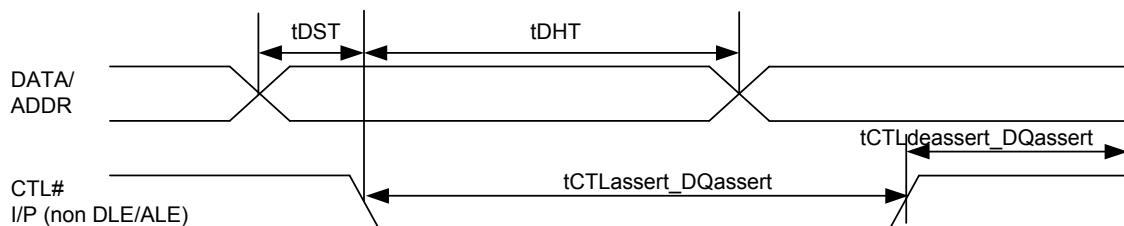

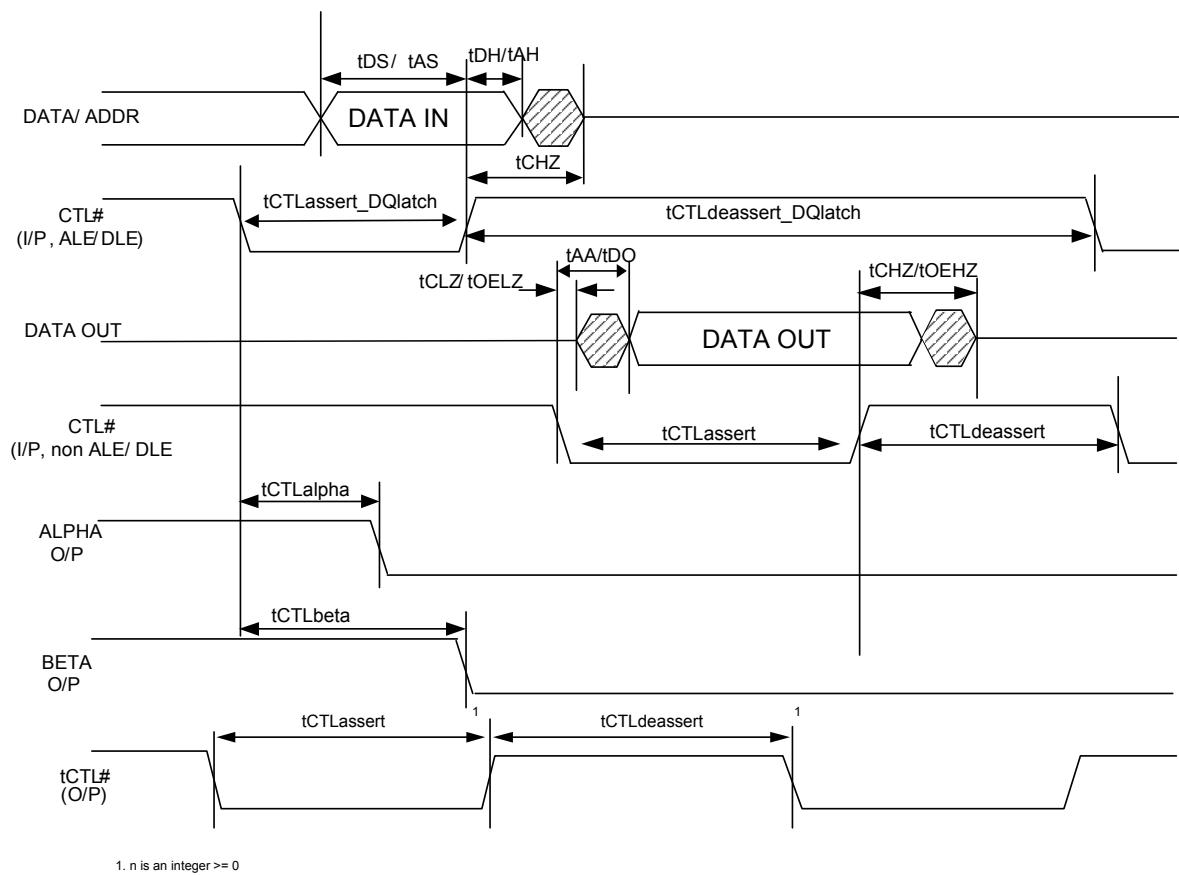

图 13. 异步模式中的 GPIF II 时序

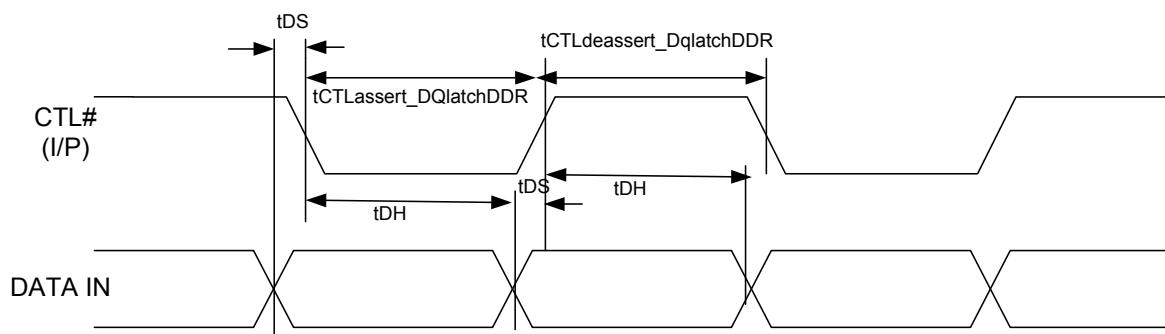

图 14. 异步 DDR 模式中的 GPIF II 时序

**表 8. 异步模式中的 GPIF II 时序<sup>[4]</sup>**

注意：下面各参数均假设了一个状态切换

| 参数                      | 说明                                                                                            | 最小值 | 最大值 | 单位 |

|-------------------------|-----------------------------------------------------------------------------------------------|-----|-----|----|

| tDS                     | 数据输入到 DLE 的建立时间。该参数在 DDR 异步模式下有效。                                                             | 2.3 | —   | ns |

| tDH                     | 数据输入到 DLE 的保持时间。在 DDR 异步模式中有效。                                                                | 2   | —   | ns |

| tAS                     | 地址输入到 ALE 的建立时间                                                                               | 2.3 | —   | ns |

| tAH                     | 地址输入到 ALE 的保持时间                                                                               | 2   | —   | ns |

| tCTLassert              | 用于无 DQ 输入关联性的 CTRL 输入以及输出的 CTL I/O 激活脉冲宽度。                                                    | 7   | —   | ns |

| tCTLdeassert            | 用于无 DQ 输入关联性的 CTRL 输入以及输出的 CTL I/O 解除激活脉冲宽度。                                                  | 7   | —   | ns |

| tCTLassert_DQassert     | 用于 CTL 输入的 CTL 激活脉冲宽度，其中 CTL 输入表明 DQ 输入在激活的边沿有效，但没有为此类 DQ 输入采用内置锁存器（ALE/DLE）。                 | 20  | —   | ns |

| tCTLdeassert_DQassert   | 用于 CTL 输入的 CTL 解除激活脉冲宽度，其中 CTL 输入表明 DQ 输入在激活的边沿有效，但没有为此类 DQ 输入采用内置锁存器（ALE/DLE）。               | 7   | —   | ns |

| tCTLassert_DQdeassert   | 用于 CTL 输入的 CTL 激活脉冲宽度，其中 CTL 输入表明 DQ 输入在解除激活的边沿有效，但没有为此类 DQ 输入采用内置锁存器（ALE/DLE）。               | 7   | —   | ns |

| tCTLdeassert_DQdeassert | 用于 CTL 输入的 CTL 解除激活脉冲宽度，其中 CTL 输入表明 DQ 输入在解除激活的边沿有效，但没有为此类 DQ 输入采用内置锁存器（ALE/DLE）。             | 20  | —   | ns |

| tCTLassert_DQlatch      | 用于 CTL 输入的 CTL 激活脉冲宽度，其中 CTL 输入采用内置锁存器（ALE/DLE）来锁存 DQ 输入。在该非 DDR 情况下，内置锁存器在解除激活的边沿始终保持关闭状态。   | 7   | —   | ns |

| tCTLdeassert_DQlatch    | 用于 CTL 输入的 CTL 解除激活脉冲宽度，其中 CTL 输入采用内置锁存器（ALE/DLE）来锁存 DQ 输入。在该非 DDR 情况下，内置锁存器在解除激活的边沿始终保持关闭状态。 | 10  | —   | ns |

| tCTLassert_DQlatchDDR   | 用于 CTL 输入的 CTL 激活脉冲宽度，其中 CTL 输入采用内置锁存器（DLE）以在 DDR 模式中锁存 DQ 输入。                                | 10  | —   | ns |

| tCTLdeassert_DQlatchDDR | 用于 CTL 输入的 CTL 解除激活脉冲宽度，其中 CTL 输入采用内置锁存器（DLE）以在 DDR 模式中锁存 Q 输入。                               | 10  | —   | ns |

| tAA                     | 当 DQ 变更或 CTL 变更需要进行检测且变更影响输入和输出 DQ 线的内部更新时，DQ/CTL 输入到 DQ 输出的时间。                               | —   | 30  | ns |

| tDO                     | 当 CTL 变更仅能使已建立数据的输出触发器更新时，CTL 到数据输出的时间。                                                       | —   | 25  | ns |

| tOEHZ                   | CTL 被指定为 OE 到低阻态的时间外部器件应停止驱动数据的时间。                                                            | 0   | —   | ns |

| tOEHZ                   | CTL 被指定为 OE 到高阻态的时间                                                                           | 8   | 8   | ns |

| tCLZ                    | 从 CTL（非 OE）到低阻态的时间。外部器件应停止驱动数据的时间。                                                            | 0   | —   | ns |

| tCHZ                    | CTL（非 OE）到高阻态的时间                                                                              | 30  | 30  | ns |

| tCTLalpha               | CTL 到 alpha 输出变更的时间                                                                           | —   | 25  | ns |

| tCTLbeta                | CTL 到 beta 输出变更的时间                                                                            | —   | 30  | ns |

| tDST                    | 不使用 DLE/ALE 时，地址 / 数据的建立时间                                                                    | 2   | —   | ns |

| tDHT                    | 不使用 DLE/ALE 时，地址 / 数据的保持时间                                                                    | 20  | —   | ns |

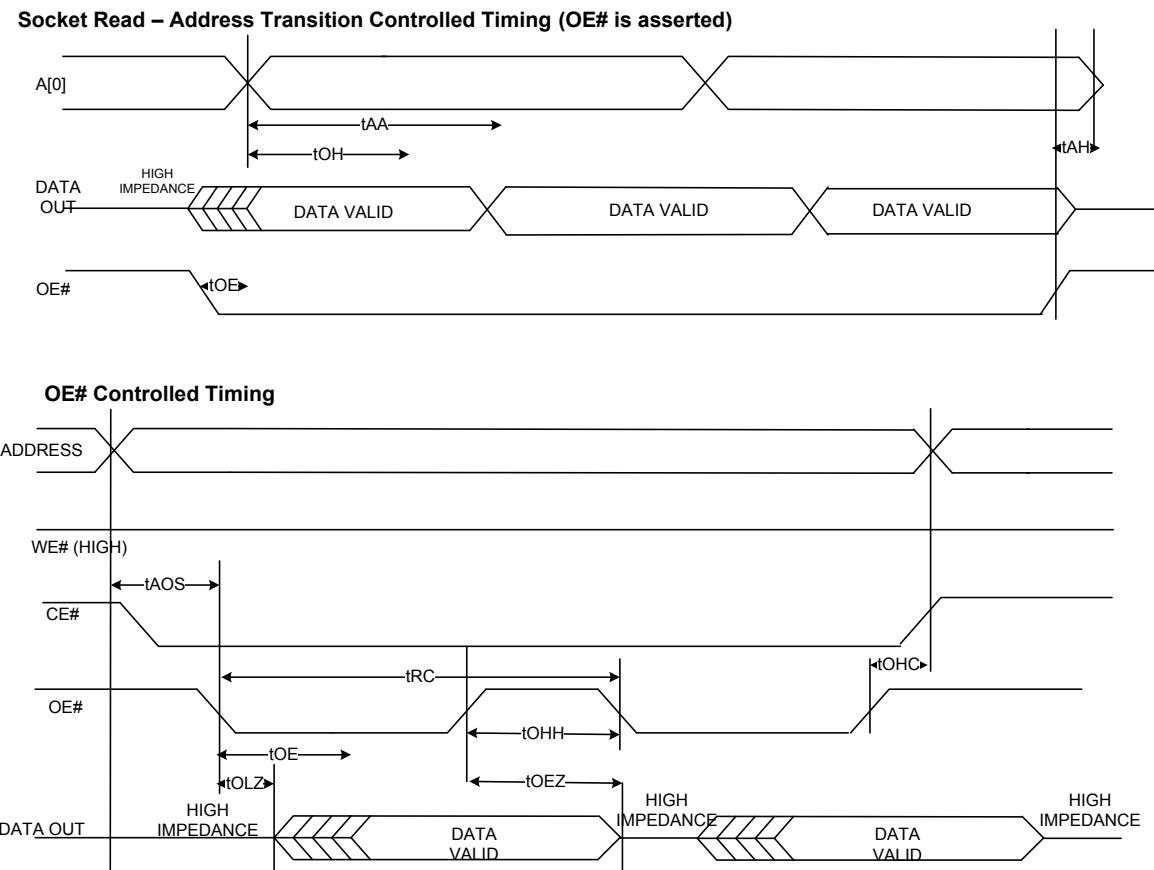

## 异步 SRAM 时序

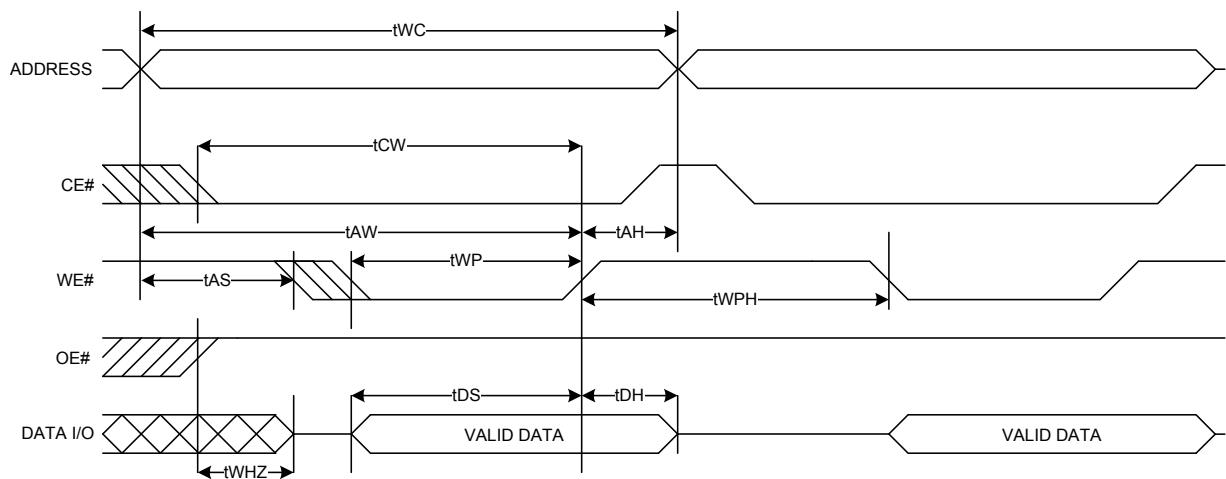

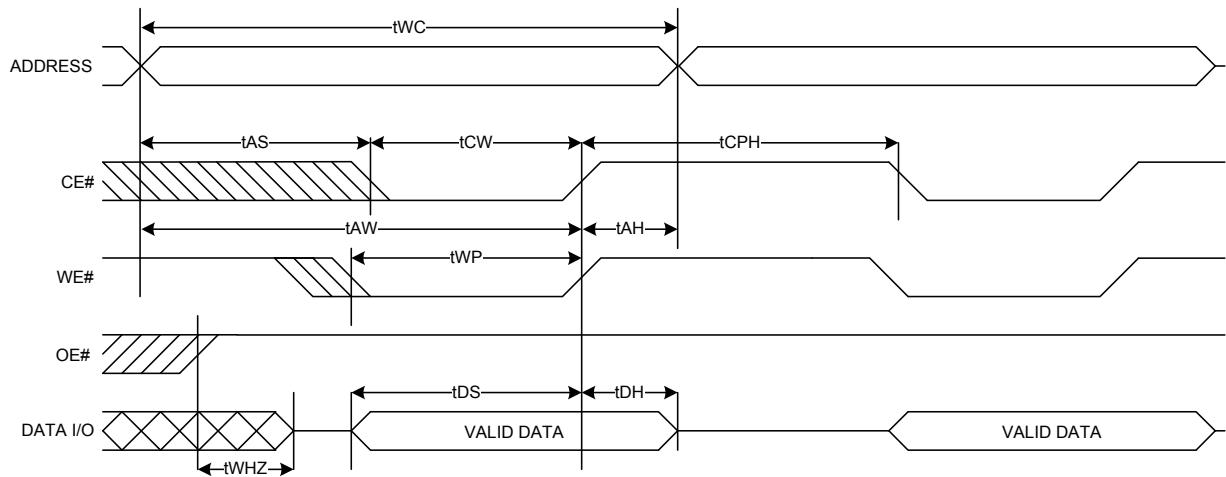

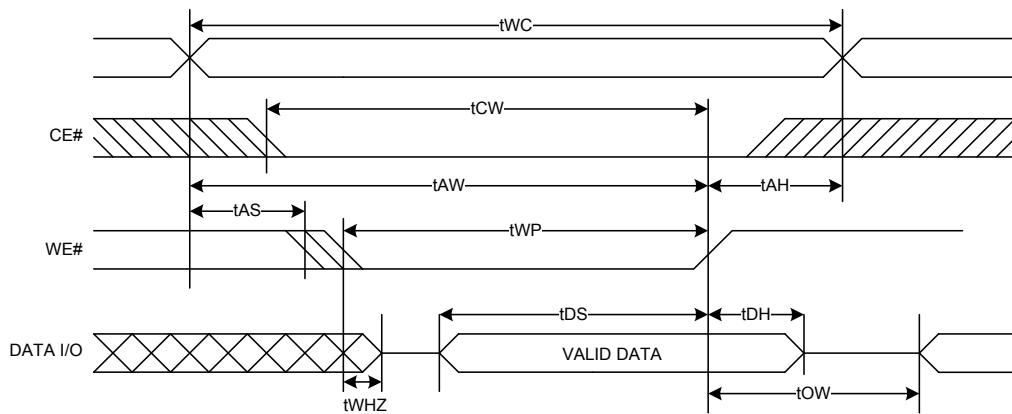

图 15. 非复用异步 SRAM 读取时序

**注释：**

4. 所有参数均由设计保证，并通过特性化进行验证。

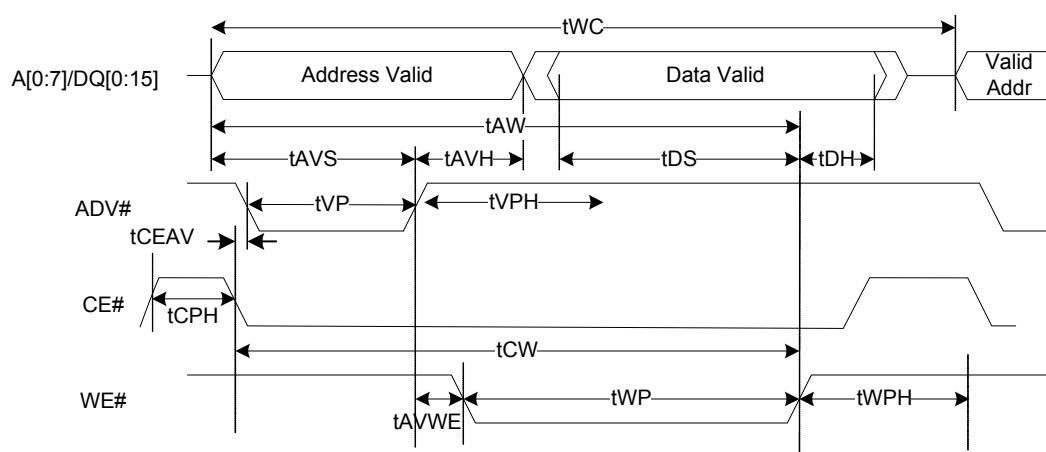

图 16. 非复用异步 SRAM 写入时序 (WE# 和 CE# 控制)

**Write Cycle 1 WE# Controlled, OE# High During Write**

**Write Cycle 2 CE# Controlled, OE# High During Write**

图 17. 非复用异步 SRAM 写入时序 (WE# 控制, OE# 为低电平)

Write Cycle 3 WE# Controlled. OE# Low

Note: tWP must be adjusted such that  $tWP > tWHZ + tDS$

表 9. 异步 SRAM 时序参数<sup>[5]</sup>

| 参数   | 说明                       | 最小值  | 最大值  | 单位   |

|------|--------------------------|------|------|------|

|      | SRAM 接口带宽                | —    | 61.5 | Mbps |

| tRC  | 读周期的时间                   | 32.5 | —    | ns   |

| tAA  | 从地址到数据生效的时间              | —    | 30   | ns   |

| tAOS | 从地址到 OE# 为低电平的建立时间       | 7    | —    | ns   |

| tOH  | 地址更改后的数据保持时间             | 3    | —    | ns   |

| tOHH | OE# 为高电平的保持时间            | 7.5  | —    | ns   |

| tOHC | 从 OE# 为高电平到 CE# 为高电平的时间  | 2    | —    | ns   |

| tOE  | 从 OE# 为低电平到数据生效的时间       | —    | 25   | ns   |

| tOLZ | 从 OE# 为低电平到数据为低阻态的时间     | 0    | —    | ns   |

| tWC  | 写周期的时间                   | 30   | —    | ns   |

| tCW  | CE# 为低电平到写周期结束的时间        | 30   | —    | ns   |

| tAW  | 从地址生效到写入结束的时间            | 30   | —    | ns   |

| tAS  | 地址建立到写周期开始的时间            | 7    | —    | ns   |

| tAH  | CE# 或 WE# 的地址保持时间        | 2    | —    | ns   |

| tWP  | WE# 脉冲宽度                 | 20   | —    | ns   |

| tWPH | WE# 为高电平的时间              | 10   | —    | ns   |

| tCPH | CE# 为高电平的时间              | 10   | —    | ns   |

| tDS  | 从数据建立到写周期结束的时间           | 7    | —    | ns   |

| tDH  | 从数据保持到写入结束的时间            | 2    | —    | ns   |

| tWHZ | 从 WE# 有效到 DQ 输出为高阻态的时间   | —    | 22.5 | ns   |

| tOEZ | 从 OE# 为高电平到 DQ 输出为高阻态的时间 | —    | 22.5 | ns   |

| tOW  | 从写入结束到输出为低阻态的时间          | 0    | —    | ns   |

注释:

5. 所有参数均由设计保证，并通过特性化进行验证。

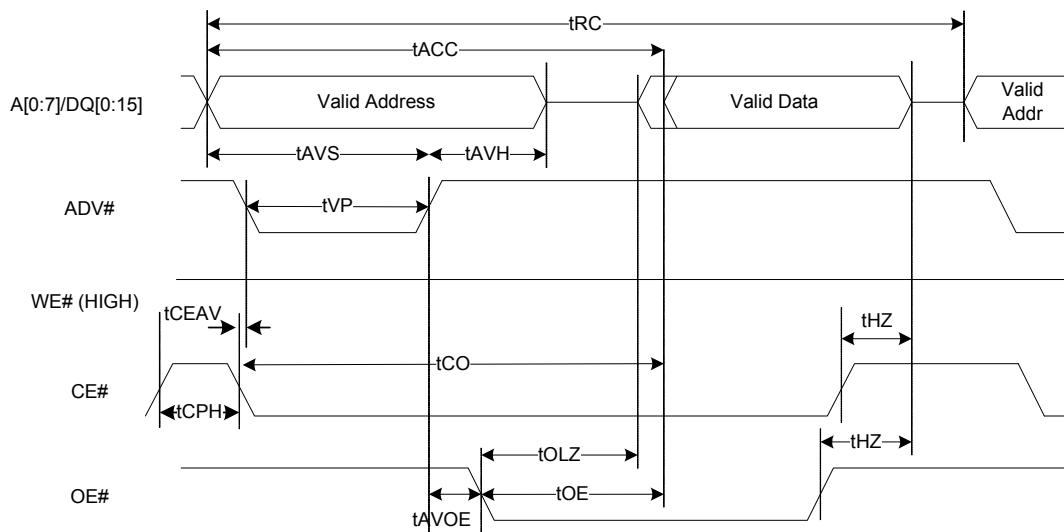

## 用于异步访问的 ADMux 时序

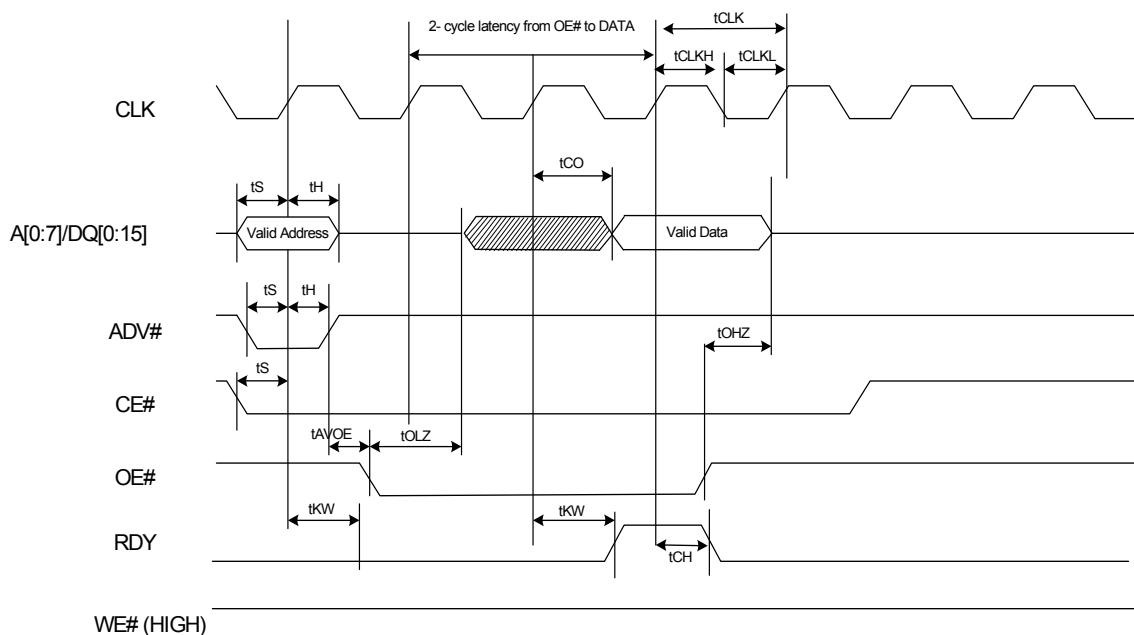

图 18. ADMux 异步随机读取

Note:

1. Multiple read cycles can be executed while keeping CE# low.

2. Read operation ends with either de-assertion of either OE# or CE#, whichever comes earlier.

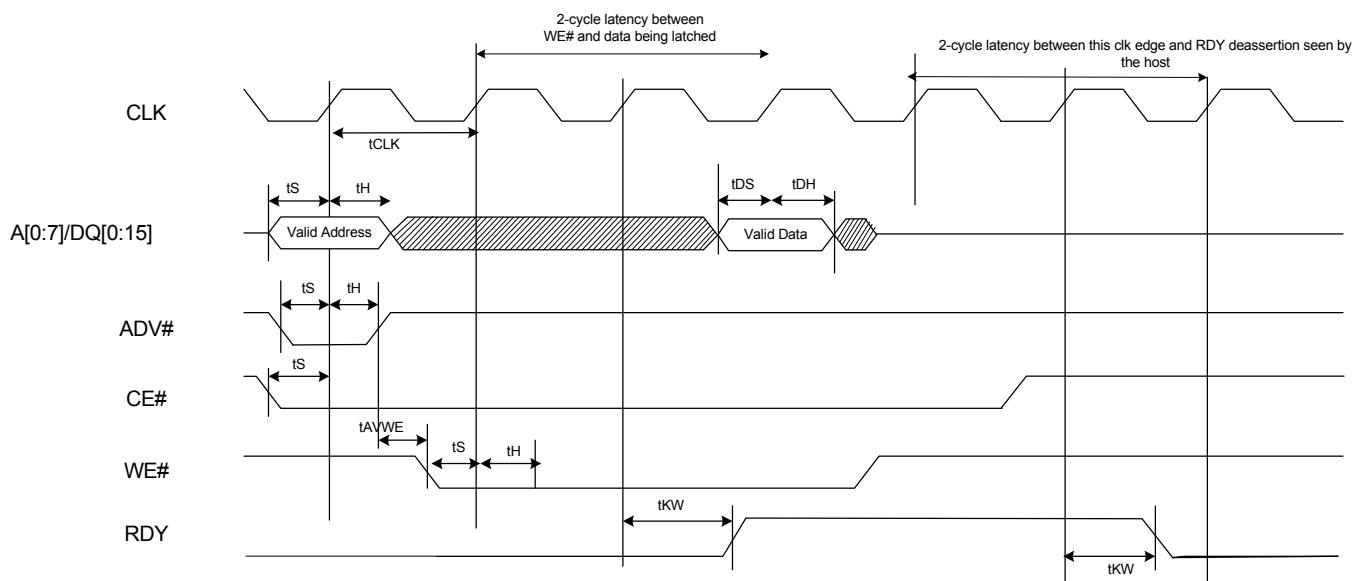

图 19. ADMux 异步随机写入

Note:

1. Multiple write cycles can be executed while keeping CE# low.

2. Write operation ends with de-assertion of either WE# or CE#, whichever comes earlier.

**表 10. 异步 ADMux 时序参数<sup>[6]</sup>**

| 参数                                           | 说明                          | 最小值  | 最大值  | 单位 | 注意                         |

|----------------------------------------------|-----------------------------|------|------|----|----------------------------|

| <b>ADMux 异步 READ (读取) 访问的时序参数</b>            |                             |      |      |    |                            |

| tRC                                          | 有效地址之间的读周期时间                | 54.5 | -    | ns | 该参数取决于 P 端口处理器取消激活 OE# 的时间 |

| tACC                                         | 从寻址到数据生效的时间                 | -    | 32   | ns |                            |

| tCO                                          | 从 CE# 激活到数据有效的时间            | -    | 34.5 | ns |                            |

| tAVOE                                        | 从 ADV# 取消激活到 OE# 激活的时间      | 2    | -    | ns |                            |

| tOLZ                                         | 从 OE# 激活到数据 LOW-Z (低阻态) 的时间 | 0    | -    | ns |                            |

| tOE                                          | 从 OE# 激活到数据有效的时间            | -    | 25   | ns |                            |

| tHZ                                          | 从读周期结束到数据为 HIGH-Z (高阻态) 的时间 | -    | 22.5 | ns |                            |

| <b>ADMux 异步 WRITE (写入) 访问的时序参数</b>           |                             |      |      |    |                            |

| tWC                                          | 有效地址之间的写周期时间                | -    | 52.5 | ns |                            |

| tAW                                          | 从地址生效到写入结束的时间               | 30   | -    | ns |                            |

| tCW                                          | 从 CE# 激活到写入结束的时间            | 30   | -    | ns |                            |

| tAVWE                                        | 从 ADV# 取消激活到 WE# 激活的时间      | 2    | -    | ns |                            |

| tWP                                          | WE# 为低脉冲宽度的时间               | 20   | -    | ns |                            |

| tWPH                                         | WE# 为高脉冲宽度的时间               | 10   | -    | ns |                            |

| tDS                                          | 从数据有效设置到 WE# 取消激活的时间        | 18   | -    | ns |                            |

| tDH                                          | 从 WE# 激活到数据有效的建立时间          | 2    | -    | ns |                            |

| <b>ADMux 异步通用 READ/WRITE (读 / 写) 访问的时序参数</b> |                             |      |      |    |                            |

| tAVS                                         | 从地址有效设置到 ADV# 取消激活的时间       | 5    | -    | ns |                            |

| tAVH                                         | 从 ADV# 取消激活到地址有效的时间         | 2    | -    | ns |                            |

| tVP                                          | ADV# 为低脉冲宽度的时间              | 7.5  | -    | ns |                            |

| tCPH                                         | CE# 为高脉冲宽度的时间               | 10   | -    | ns |                            |

| tVPH                                         | ADV# 为高脉冲宽度的时间              | 15   | -    | ns |                            |

| tCEAV                                        | 从 CE# 激活到 ADV# 激活的时间        | 0    | -    | ns |                            |

**注释：**

6. 所有参数均由设计保证，并通过特性化进行验证。

## 同步 ADMux 时序

图 20. 同步 ADMux 接口 — 读周期时序

Note:

- 1) External P-Port processor and FX3S operate on the same clock edge

- 2) External processor sees RDY assert 2 cycles after OE # asserts and sees RDY deassert a cycle after the data appears on the output

- 3) Valid output data appears 2 cycle after OE # asserted. The data is held until OE # deasserts

- 4) Two cycle latency is shown for 0-100 MHz operation. Latency can be reduced by 1 cycle for operations at less than 50 MHz (this 1 cycle latency is not supported by the bootloader)

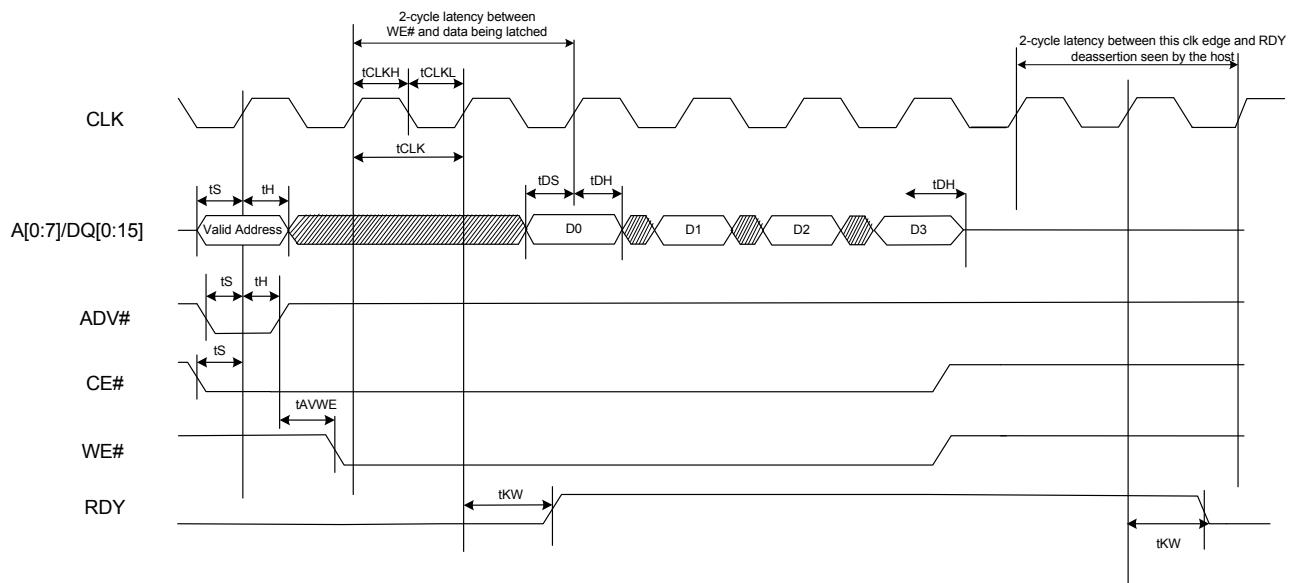

图 21. 同步 ADMux 接口 — 写周期时序

Note:

- 1) External P-Port processor and FX3S operate on the same clock edge

- 2) External processor sees RDY assert 2 cycles after WE # asserts and deassert 3 cycles after the edge sampling the data.

- 3) Two cycle latency is shown for 0-100 MHz operation. Latency can be reduced by 1 cycle for operations at less than 50 MHz (this 1 cycle latency is not supported by the bootloader)

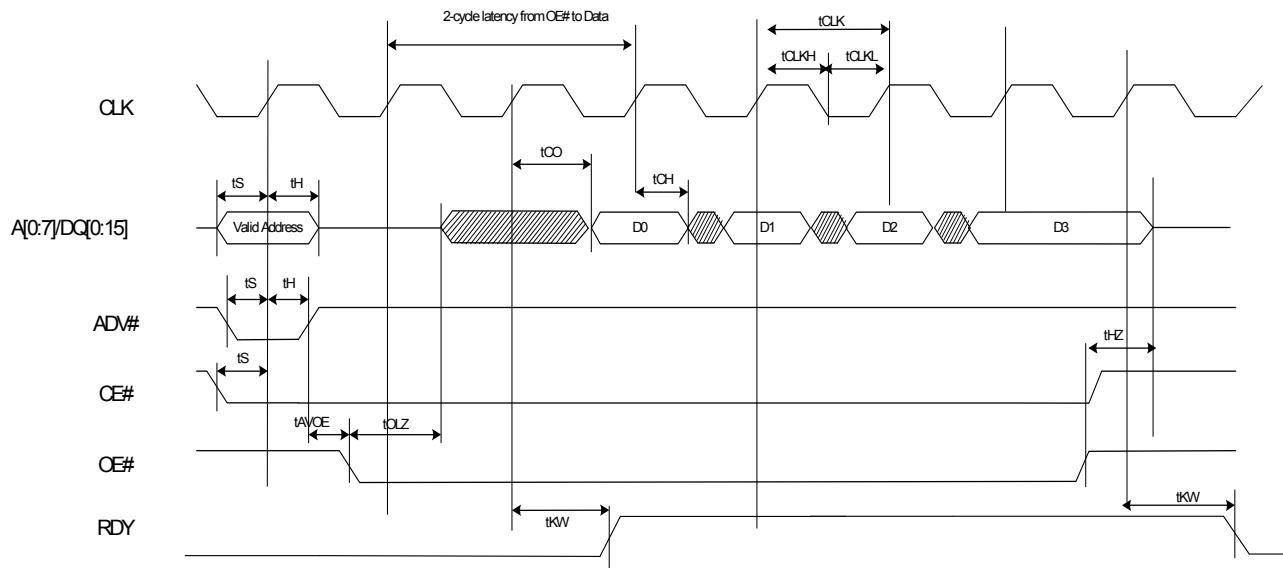

图 22. 同步 ADMux 接口 — 突发读取时序

Note:

- 1) External P-Port processor and FX3S work operate on the same clock edge

- 2) External processor sees RDY assert 2 cycles after OE # asserts and sees RDY deassert a cycle after the last burst data appears on the output

- 3) Valid output data appears 2 cycle after OE # asserted. The last burst data is held until OE # deasserts

- 4) Burst size of 4 is shown. Transfer size for the operation must be a multiple of burst size. Burst size is usually power of 2. RDY will not deassert in the middle of the burst.

- 5) External processor cannot deassert OE in the middle of a burst. If it does so, any bytes remaining in the burst packet could get lost.

- 6) Two cycle latency is shown for 0-100 MHz operation. Latency can be reduced by 1 cycle for operations at less than 50 MHz (this 1 cycle latency is not supported by the bootloader)

图 23. 同步 ADMux 接口 — 突发写入时序

Note:

- 1) External P-Port processor and FX3S operate on the same clock edge

- 2) External processor sees RDY assert 2 cycles after WE # asserts and deasserts 3 cycles after the edge sampling the last burst data.

- 3) Transfer size for the operation must be a multiple of burst size. Burst size is usually power of 2. RDY will not deassert in the middle of the burst. Burst size of 4 is shown

- 4) External processor cannot deassert WE in the middle of a burst. If it does so, any bytes remaining in the burst packet could get lost.

- 5) Two cycle latency is shown for 0-100 MHz operation. Latency can be reduced by 1 cycle for operations at less than 50 MHz (this 1 cycle latency is not supported by the bootloader)

**表 11. 同步 ADMux 时序参数<sup>[7]</sup>**

| 参数     | 说明                       | 最小值 | 最大值 | 单位  |

|--------|--------------------------|-----|-----|-----|

| FREQ   | 接口时钟频率                   | —   | 100 | MHz |

| tCLK   | 时钟周期                     | 10  | —   | ns  |

| tCLKH  | 时钟高电平时间                  | 4   | —   | ns  |

| tCLKL  | 时钟低电平时间                  | 4   | —   | ns  |

| tS     | CE#/WE#/DQ 的建立时间         | 2   | —   | ns  |

| tH     | CE#/WE#/DQ 的保持时间         | 0.5 | —   | ns  |

| tCH    | 从时钟到数据的保持时间              | 0   | —   | ns  |

| tDS    | 数据输入的建立时间                | 2   | —   | ns  |

| tDH    | 从时钟到数据输入的保持数据时间          | 0.5 | —   | ns  |

| tAVDOE | 从 ADV# 为高电平到 OE# 为低电平的时间 | 0   | —   | ns  |

| tAVDWE | 从 ADV# 为高电平到 WE# 为低电平的时间 | 0   | —   | ns  |

| tHZ    | 从 CE# 为高电平到数据为高阻态的时间     | —   | 8   | ns  |

| tOHZ   | 从 OE# 为高电平到数据为高阻态的时间     | —   | 8   | ns  |

| tOLZ   | 从 OE# 为低电平到数据为低阻态的时间     | 0   | —   | ns  |

| tKW    | 从时钟到 RDY 有效的时间           | —   | 8   | ns  |

**注释：**

7. 所有参数均由设计保证，并通过特性化进行验证。

## 从设备 FIFO 接口

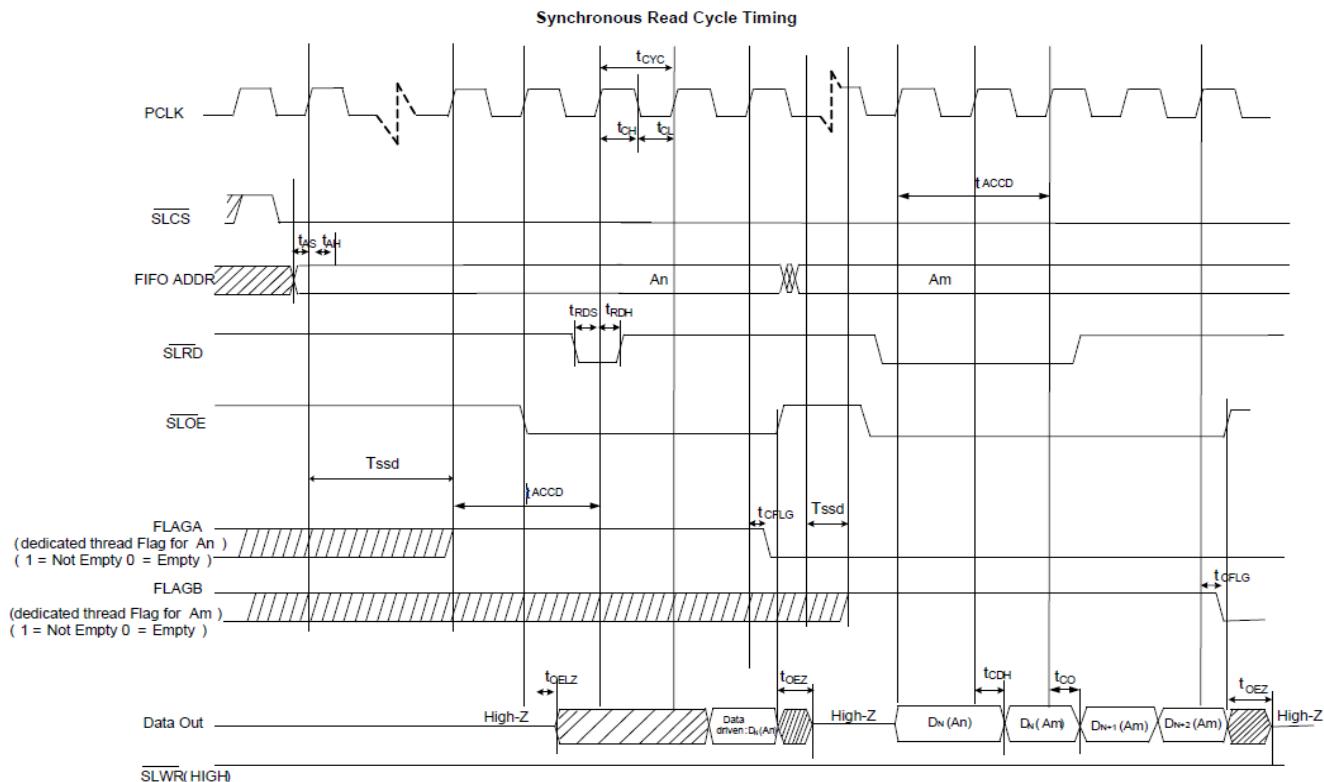

### 同步从设备 FIFO 序列说明

- FIFO 地址稳定，且 SLCS 被激活

- FLAG 表示 FIFO 不为空的状态

- SLOE 被激活。SLOE 仅是一个输出使能信号，其唯一功能是驱动数据总线。

- SLRD 被激活

- FIFO 指针在 PCLK 的上升沿上更新，同时 SLRD 被激活。这会启动从新寻址位置到数据总线之间的数据传输。经过  $t_{CO}$  传输延迟（从 PCLK 的上升沿测量）后即可提供新的数值。N 是自 FIFO 读取的第一个数值。要在 FIFO 数据总线上保留数据，还必须同时激活 SLOE。

突发读取时还会显示相同的事件序列。

### FLAG 使用：

通过外部处理器监视 FLAG 信号的流量控制。FLAG 信号是 FX3 的输出，可以配置为显示专用线程或当前正在寻址的线程的空状态，全状态或局部状态。

## 插座切换延迟 (Tssd)

插座切换延迟的测量时间范围是从 EPSWITCH# 被主机置位开始（通过新插座在地址总线上的地址），到 Current\_Thread\_Ready 被标志为止。对于生产者插座，当 DMA 缓存区准备好接收数据时，该标志会被置位。对于使用者插座，当 DMA 缓存区准备好将数据从中取出时，这个标志会被置位。对于同步从属 FIFO 接口，切换延迟是由 GPIF 接口的时钟周期数量来测量的；对于异步从属接口，是由 PIB 时钟周期测量的。这一规律仅适用于 5 位从属 FIFO 接口；由于使用了 GPIF II 状态机中的线程切换，FX3 的 2 位从属 FIFO 接口没有插座切换延迟。

**注意：**对于突发模式，在整个读取过程中持续激活 SLRD# 和 SLOE#。当 SLOE# 被激活时，将（利用来自之前已寻址的 FIFO 的数据）驱动数据总线。当 SLRD# 有效时，于每一个 PCLK 序列的上升沿，FIFO 指针会递增，且下一个数据值会被传输到数据总线上。

图 24. 同步从设备 FIFO 读取模式

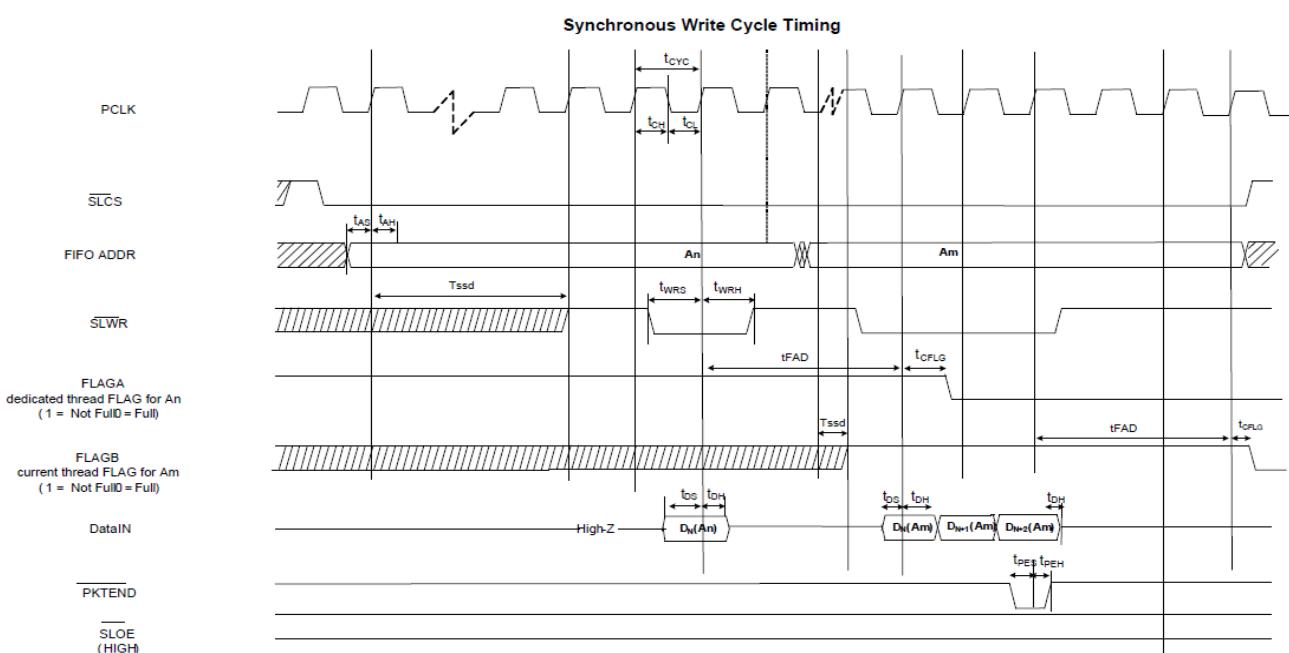

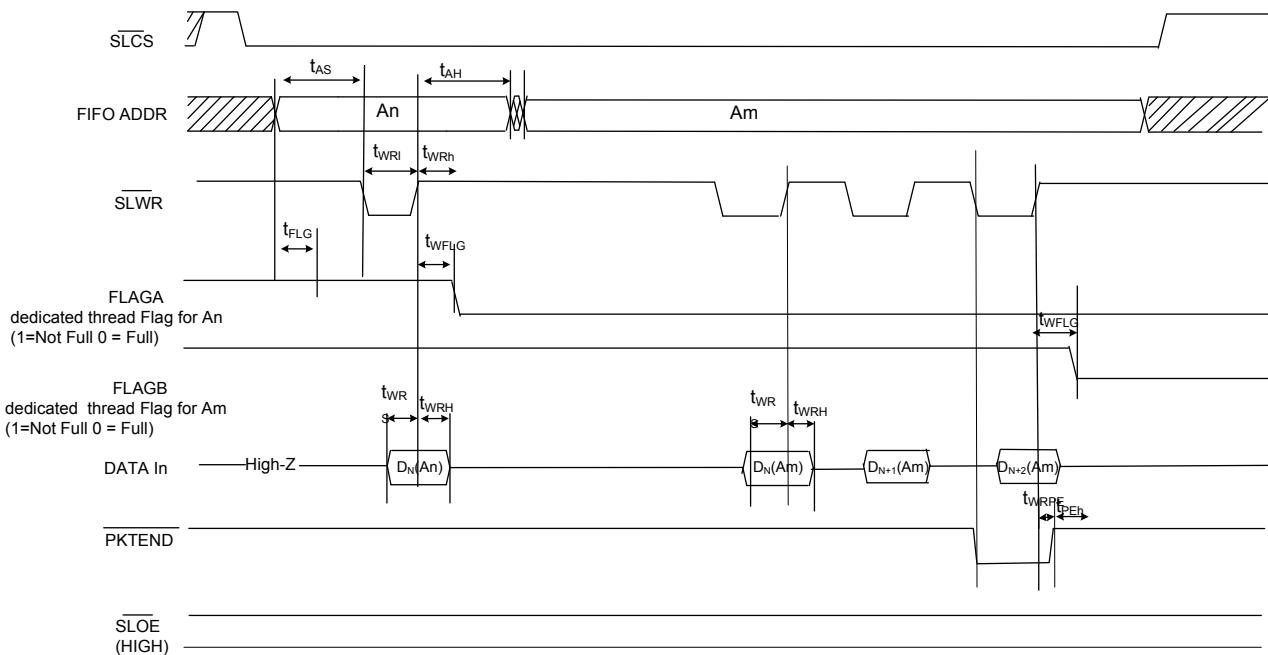

## 同步从设备 FIFO 写序列说明

- FIFO 地址稳定，且 SLCS# 信号被激活

- 外部主控或外设将数据输出到数据总线上。

- SLWR# 被激活

- 当 SLWR# 被激活时，将数据写入到 FIFO 和 PCLK 的上升沿上， FIFO 指针递增

- 从时钟的上升沿起，经过  $t_{WFLG}$  的延迟后， FIFO 标志将被更新。

- 突发写入时还会显示相同的事件序列

**注意:** 对于突发模式，SLWR# 和 SLCS# 在写入所有所需数据值的整个过程中保持激活状态。在突发写入模式下，SLWR# 被激活后，会在 PCLK 的每个上升沿上将 FIFO 数据总线上的数据写入到 FIFO 中。在 PCLK 的每个上升沿上更新 FIFO 指针。

**短数据包:** 通过 PKTEND# 信号可将某个短数据包发送到 USB 主机。需要设计外部器件或处理器，使之在最后数据字以及与该字相应的 SLWR# 脉冲时同时激活 PKTEND#，必须在激活 PKTEND# 过程中保持 FIFOADDR 不变。

**零长度数据包:** 通过激活 PKTEND#，而没有激活 SLWR#，外部器件或处理器可以轻松地将一个零长度数据包 (ZLP) 传输到 FX3S。必须按照图 25 的内容驱动 SLCS# 和地址。

图 25. 同步从设备 FIFO 写入模式

**表 12. 同步从设备 FIFO 参数<sup>[8]</sup>**

| 参数                           | 说明                     | 最小值 | 最大值 | 单位           |

|------------------------------|------------------------|-----|-----|--------------|

| FREQ                         | 接口时钟频率                 | —   | 100 | MHz          |

| tCYC                         | 时钟周期                   | 10  | —   | ns           |

| tCH                          | 时钟为高电平的时间              | 4   | —   | ns           |

| tCL                          | 时钟为低电平的时间              | 4   | —   | ns           |

| tRDS                         | 从 SLRD# 到 CLK 的建立时间    | 2   | —   | ns           |

| tRDH                         | 从 SLRD# 到 CLK 的保持时间    | 0.5 | —   | ns           |

| tWRS                         | 从 SLWR# 到 CLK 的建立时间    | 2   | —   | ns           |

| tWRH                         | 从 SLWR# 到 CLK 的保持时间    | 0.5 | —   | ns           |

| tCO                          | 从时钟到数据生效的时间            | —   | 8   | ns           |

| tDS                          | 数据输入的建立时间              | 2   | —   | ns           |

| tDH                          | 从时钟到数据输入的保持数据时间        | 0.5 | —   | ns           |

| tAS                          | 从地址到时钟的地址建立时间          | 2   | —   | ns           |

| tAH                          | 从 CLK 到地址的保持时间         | 0.5 | —   | ns           |

| tOELZ                        | 从 SLOE# 到数据变为低阻态的时间    | 0   | —   | ns           |

| tCFLG                        | 从时钟到标志输出的延迟            | —   | 8   | ns           |

| tOEZ                         | 从 SLOE# 解除激活到数据为高阻态的时间 | —   | 8   | ns           |

| tPES                         | 从 PKTEND# 到 CLK 的建立时间  | 2   | —   | ns           |

| tPEH                         | 从 CLK 到 PKTEND# 的保持时间  | 0.5 | —   | ns           |

| tCDH                         | 从 CLK 到数据输出的保持时间       | 2   | —   | ns           |

| tSSD                         | 插座切换延迟                 | 2   | 68  | Clock cycles |

| tACCD                        | 从 SLRD# 到 Data 延迟      | 2   | 2   | Clock cycles |

| tFAD                         | 从 SLWR# 到 FLAG 延迟      | 3   | 3   | Clock cycles |

| 注：从 ADDR 到 DATA/FLAGS 延迟三个周期 |                        |     |     |              |

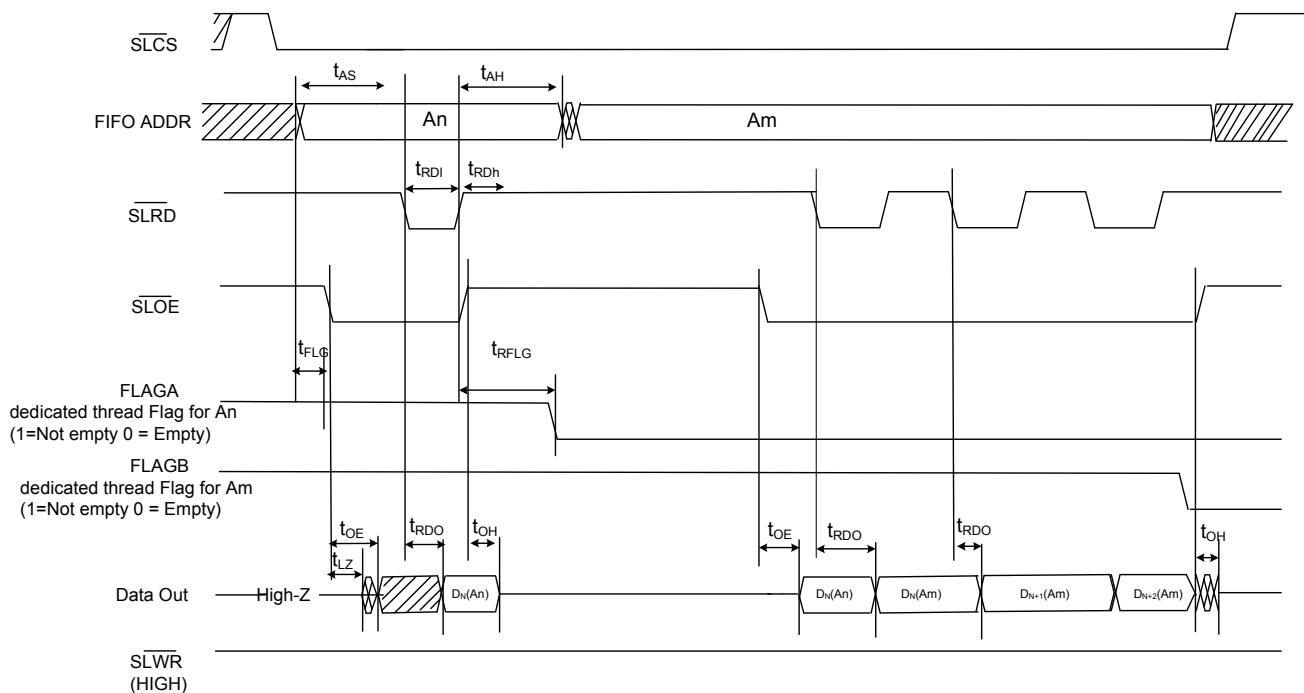

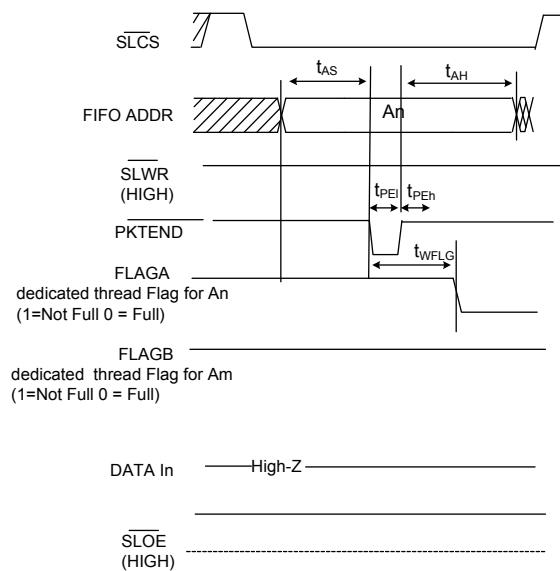

### 异步从设备 FIFO 读序列说明

- FIFO 地址稳定，且 SLCS# 信号被激活。

- SLOE# 被激活。这使得数据总线被驱动。

- SLRD# 被激活。

- SLRD# 激活后，开始驱动来自 FIFO 的数据。该数据将在从 SLRD# 下降沿的 tRDO 传输延迟后生效。

- FIFO 指针在 SLRD# 的解除激活后递增

在第 36 页上的图 26 中，数据 N 是从 FIFO 读取的第一个有效数据。要想在读周期内使数据在总线上出现，SLOE# 必须处于激活状态。SLRD# 和 SLOE# 也可绑定。

突发读取时还会显示相同的事件序列。

**注意：**在突发读取模式下，数据总线在 SLOE# 激活期间处于驱动状态（数据从之前已寻址的 FIFO 中启动）。SLRD# 激活后，在数据总线上驱动来 FIFO 的数据（也必须激活 SLOE#）。FIFO 指针在 SLRD# 的解除激活后递增。

#### 注释：

8. 所有参数均由设计保证，并通过特性化进行验证。

图 26. 异步从设备 FIFO 读取模式

### 异步从设备 FIFO 写序列说明

- FIFO 地址被驱动，且 SLCS# 被激活

- SLWR# 被激活。 SLCS# 必须与 SLWR# 同时激活，或先于 SLWR# 激活

- 在 SLWR# 边沿上解除激活前，数据必须显示在总线 tWRS 上

- 解除激活 SLWR# 会导致将数据从数据总线写入到 FIFO 内，然后 FIFO 指针递增

- 在 SLWR 边沿解除激活的 tWFLG 后，将更新 FIFO 标志。

- 突发写入时显示相同的事件序列。

请注意，在突发写入模式下，SLWR# 解除激活后，会将数据写入 FIFO 内，然后 FIFO 指针递增。

**短数据包：**通过 PKTEND# 信号可将某个短数据包发送到 USB 主机。需要设计外部器件或处理器，使之在最后数据字以及与该字相应的 SLWR# 脉冲时同时激活 PKTEND#，必须在激活 PKTEND# 过程中保持 FIFOADDR 不变。

**零长度数据包：**通过激活 PKTEND#，而没有激活 SLWR#，外部器件或处理器可以轻松地将一个零长度数据包（ZLP）传输到 FX3S。必须按照第 37 页上的图 27 的内容驱动 SLCS# 和地址。

**FLAG 用途：**外部处理器通过监控 FLAG 信号来实现流量控制。FLAG 信号由 FX3S 器件输出。配置该器件，可显示专用地址或当前地址的空、满和局部状态。

图 27. 异步从设备 FIFO 写入模式

**Asynchronous Write Cycle Timing**