# Single-Phase Voltage Regulator

# High Efficiency, Integrated Power MOSFETs

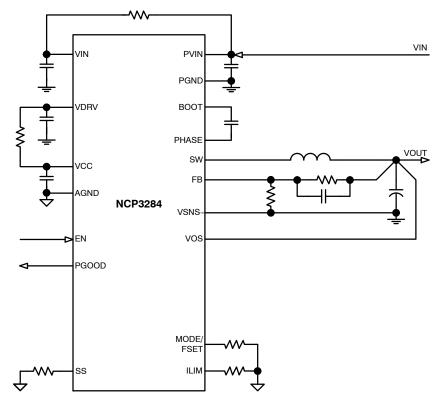

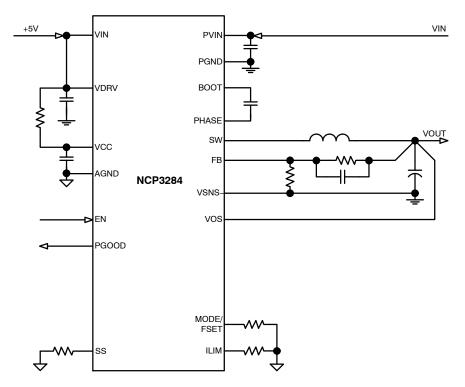

The NCP3284, a single-phase synchronous buck regulator, integrates power MOSFETs to provide a high-efficiency and compact-footprint power management solution. The NCP3284 is able to deliver up to 30 A TDC output current on a wide output voltage range. Operating in high switching frequency up to 1 MHz allows employing small size inductors and capacitors while maintaining high efficiency due to integrated solution with high performance power MOSFETs. It provides differential voltage sense, flexible soft-start programming, and comprehensive protections.

### Features

- Vin =  $4.5 \text{ V} \sim 18 \text{ V}$  with Input Feedforward

- Vout =  $0.8 \text{ V} \sim \text{Min} (0.85 \times \text{Vin}, 5.5 \text{ V})$  with Remote Voltage Sense

- Fsw = 500k/600k/800k/1 MHz Switching Frequency

- Up to 30 A Continuous Output Current and 45 A Pulse Current

- Integrated 5 V LDO or External 5 V Supply

- Enable with Programmable Vin UVLO

- Selectable Forced CCM and Auto DCM/CCM for High Efficiency at Light Load

- Programmable Soft Start

- Output Discharge in Shutdown

- Programmable Current Limit

- Under-Voltage Protection and Over-Voltage Protection

- Recoverable Thermal Shutdown Protection

- Selectable Protection Mode (Latch-off or Hiccup)

- Power Good Indicator

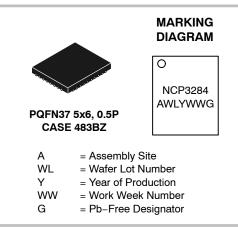

- PQFN37, 5x6 mm, 0.5 mm Pitch Package

- This Device is Pb-Free and is RoHS Compliant

#### **Typical Applications**

- Point of Load

- Telecom and Networking

- Server and Storage System

- Computing Applications

# **ON Semiconductor®**

www.onsemi.com

### **ORDERING INFORMATION**

| Device       | Package   | Shipping†          |

|--------------|-----------|--------------------|

| NCP3284MNTXG | PQFN37    | 2500 / Tape & Reel |

|              | (Pb-Free) |                    |

†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specification Brochure, BRD8011/D.

Figure 1. Typical Application Circuit with Single Input Power Supply (LDO Enabled)

Figure 2. Typical Application Circuit with External 5 V Supply for VCC (LDO Disabled)

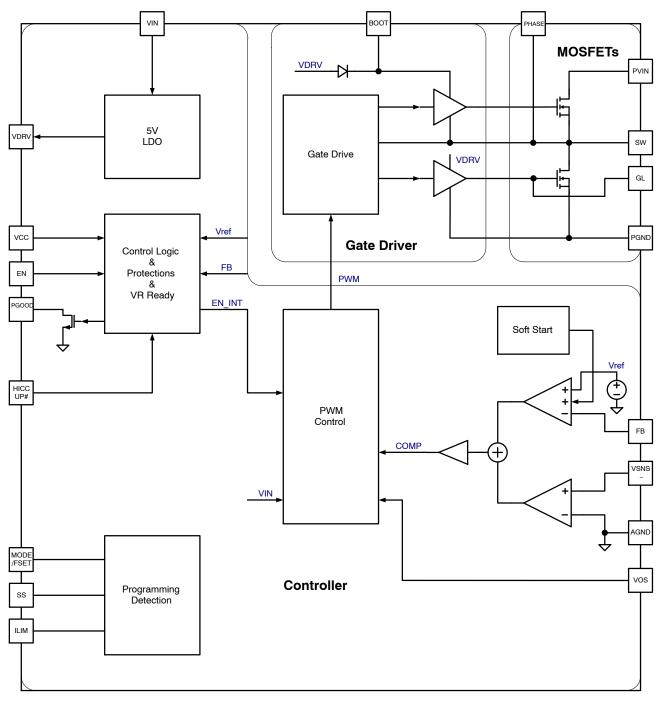

Figure 3. Functional Block Diagram

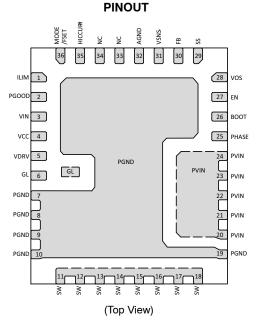

## PIN DESCRIPTION

| Pin     | Name      | Туре                   | Description                                                                                                                                                                                                                                                                                                                                                             |  |

|---------|-----------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1       | ILIM      | Analog Output          | Current Limit. A resistor between this pin and AGND to program current limit.                                                                                                                                                                                                                                                                                           |  |

| 2       | PGOOD     | Logic Output           | Power GOOD. Open-drain output. Provides a logic high valid power good output signal, indicating the regulator's output is in regulation window.                                                                                                                                                                                                                         |  |

| 3       | VIN       | Power Input            | Power Supply Input of LDO. Power supply input pin of internal 5 V LDO. A 1.0 $\mu F$ or more ceramic capacitors must bypass this input to power ground. The capacitors should be placed as close as possible to this pin. A direct short from this pin to VDRV (pin 5) disables the internal LDO for applications with an external 5 V supply as power of VDRV and VCC. |  |

| 4       | VCC       | Analog Power           | Supply Voltage Input of Controller. A 2.2 $\mu$ F or larger ceramic capacitor bypasses this input to GND. This capacitor should be placed as close as possible to this pin.                                                                                                                                                                                             |  |

| 5       | VDRV      | Analog Power           | Output of LDO and Supply Voltage Input of Gate Drivers. Output of integrated 5.0 V LDO and power supply input of gate drivers. A 4.7 $\mu$ F/25 V or larger ceramic capacitor bypasses this pin to PGND. The capacitor should be placed as close as possible to this pin.                                                                                               |  |

| 6       | GL        | Analog Output          | Gate of Low–Side MOSFET. Directly connected with the gate of the low–side power MOSFET.                                                                                                                                                                                                                                                                                 |  |

| 7~10,19 | PGND      | Power Ground           | Power Ground. These pins are the power supply ground pins of the device, which are connected to source of internal low-side power MOSFET. Must be connected to the system ground.                                                                                                                                                                                       |  |

| 11~18   | SW        | Power<br>Bidirectional | Switch Node. Pins to be connected to an external inductor. These pins are<br>interconnection between internal high-side MOSFET and low-side MOSFET                                                                                                                                                                                                                      |  |

| 20~24   | PVIN      | Power Input            | Power Supply Input. These pins are the power supply input pins of the device which are connected to drain of internal high-side power MOSFET. A 22 $\mu$ F o more ceramic capacitors must bypass this input to PGND. The capacitors sho be placed as close as possible to these pins.                                                                                   |  |

| 25      | PHASE     | Power Return           | Phase Node. Provides a return path for integrated high-side gate driver.<br>It is internally connected to source of high-side MOSFET.                                                                                                                                                                                                                                   |  |

| 26      | BOOT      | Power<br>Bidirectional | Bootstrap. Provides bootstrap voltage for high-side gate driver. A 0.22 $\mu$ F/25 V ceramic capacitor is required from this pin to PHASE (pin 25).                                                                                                                                                                                                                     |  |

| 27      | EN        | Logic Input            | Enable. Logic high enables controller while logic low disables controller. Input supply UVLO can be programmed at this pin.                                                                                                                                                                                                                                             |  |

| 28      | VOS       | Analog Input           | Voltage Sense. Direct voltage sense for output voltage feedforward.                                                                                                                                                                                                                                                                                                     |  |

| 29      | SS        | Analog Input           | Soft Start. A resistor between this pin and GND to program the soft-start slew rate and options.                                                                                                                                                                                                                                                                        |  |

| 30      | FB        | Analog Input           | Feedback. Inverting input to error amplifier.                                                                                                                                                                                                                                                                                                                           |  |

| 31      | VSNS-     | Analog Input           | Voltage Sense Negative Input. Connect this pin to remote voltage negative sen point.                                                                                                                                                                                                                                                                                    |  |

| 32      | AGND      | Analog Ground          | Analog Ground. Ground of controller. Must be connected to the system ground.                                                                                                                                                                                                                                                                                            |  |

| 33~34   | NC        | -                      | No Connection.                                                                                                                                                                                                                                                                                                                                                          |  |

| 35      | HICCUP#   | Analog Input           | Latch-Off / Hiccup#. Float this pin to enable latch-off mode in protections (OC UVP/OVP); Ground this pin to ground to enable hiccup mode in protections.                                                                                                                                                                                                               |  |

| 36      | MODE/FSET | Analog Input           | Mode and Frequency Set. A resistor between this pin and AGND to program operation mode and nominal switching frequency.                                                                                                                                                                                                                                                 |  |

#### MAXIMUM RATINGS

|                                                   |                                      | Value                |                   |      |  |

|---------------------------------------------------|--------------------------------------|----------------------|-------------------|------|--|

| Rating                                            | Symbol                               | MIN                  | МАХ               | Unit |  |

| Power Supply Voltage to PGND                      | V <sub>PVIN</sub> , V <sub>VIN</sub> |                      | 23                | V    |  |

| PHASE/SW to PGND                                  | V <sub>PHASE</sub> , V <sub>SW</sub> | −0.6<br>−5 (<50 ns)  | 23<br>25 (<10 ns) | V    |  |

| Driver Supply Voltage to PGND                     | V <sub>VDRV</sub>                    | -0.3                 | 5.5               | V    |  |

| Analog Supply Voltage to AGND                     | V <sub>VCC</sub>                     | -0.3                 | 6.5               | V    |  |

| BOOT to PGND                                      | BOOT_PGND                            | -0.3                 | 30<br>33 (<50 ns) | V    |  |

| BOOT to PHASE/SW                                  | BOOT_PHASE/SW                        | -0.3                 | 6.5               | V    |  |

| GL to PGND                                        | GL                                   | _0.3<br>_2 (<200 ns) | VDRV+0.3          | V    |  |

| VSNS- to AGND                                     | VSNS-                                | -0.2                 | 0.2               | V    |  |

| PGND to AGND                                      | PGND                                 | -0.3                 | 0.3               | V    |  |

| Other Pins                                        |                                      | -0.3                 | VCC+0.3           | V    |  |

| Human Body Model (HBM) ESD Rating are (Note 1)    | ESD HBM                              |                      | 2000              | V    |  |

| Charge Device Model (CDM) ESD Rating are (Note 1) | ESD CDM                              |                      | 2000              | V    |  |

| Latch up Current: (Note 2)                        | I <sub>LU</sub>                      | -100                 | 100               | mA   |  |

| Operating Junction Temperature Range              | TJ                                   | -40                  | 125               | °C   |  |

| Operating Ambient Temperature Range               | T <sub>A</sub>                       | -40                  | 100               | °C   |  |

| Storage Temperature Range                         | T <sub>STG</sub>                     | -55                  | 150               | °C   |  |

| Thermal Resistance Junction to Top Case(Note 3)   | $R_{\Psi JC}$                        | 0.8                  |                   | °C/W |  |

| Thermal Resistance Junction to Board (Note 3)     | $R_{\Psi JB}$                        | 0.9                  |                   | °C/W |  |

| Thermal Resistance Junction to Ambient (Note 3)   | $R_{	hetaJA}$                        | 26.7                 |                   | °C/W |  |

| Maximum Power Dissipation (Note 4)                | PD                                   | 3.                   | 75                | W    |  |

| Moisture Sensitivity Level (Note 5)               | MSL                                  | 1                    |                   | -    |  |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

This device is ESD sensitive. Handling precautions are needed to avoid damage or performance degradation.

Latch up Current per JEDEC standard: JESD78 class II.

3. The thermal resistance values are dependent of the internal losses split between devices and the PCB heat dissipation. This data is based on a typical operation condition with a 4-layer FR-4 PCB board, which has two, 1-ounce copper internal power and ground planes and 2-ounce copper traces on top and bottom layers with approximately 80% copper coverage. No airflow and no heat sink applied (reference EIA/JEDEC 51.7). It also does not account for other heat sources that may be present on the PCB next to the device in question (such as inductors, resistors etc.)

4. The maximum power dissipation (PD) is dependent on input voltage, output voltage, output current, external components selected, and PCB layout. The reference data is obtained based on  $T_{JMAX}$  = 125°C and  $T_A$  = 25°C.

5. Moisture Sensitivity Level (MSL): IPC/JEDEC standard: J-STD-020A.

| <b>ELECTRICAL CHARACTERISTICS</b> (V <sub>IN</sub> = 12 V, typical values are referenced to T <sub>A</sub> = T <sub>J</sub> = 25°C, Min and Max values are referenced |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| to $T_A = T_J = -40^{\circ}C$ to 125°C. unless other noted.)                                                                                                          |

| Characteristics                                            | Test Conditions                                                     |                                           | Symbol              | MIN  | TYP  | MAX  | UNITS |

|------------------------------------------------------------|---------------------------------------------------------------------|-------------------------------------------|---------------------|------|------|------|-------|

| SUPPLY VOLTAGE MONITO                                      | DR                                                                  |                                           | •                   | -    | -    | -    | -     |

| VCC Under-Voltage (UVLO)<br>Threshold                      | VCC falling                                                         |                                           | V <sub>DDUV-</sub>  | 4.0  |      |      | V     |

| VCC OK Threshold                                           | VCC rising                                                          |                                           | V <sub>DDOK</sub>   |      |      | 4.5  | V     |

| VCC UVLO Hysteresis                                        |                                                                     |                                           | V <sub>DDHYS</sub>  |      | 200  |      | mV    |

| SUPPLY CURRENT                                             | •                                                                   |                                           | •                   | •    | -    |      |       |

| PVIN Shutdown Current                                      | EN low                                                              |                                           | I <sub>SDPVIN</sub> | -    | 4.8  | 20   | μA    |

| V <sub>IN</sub> Quiescent Supply<br>Current                | EN high, no switching                                               | LDO enabled,<br>VIN = 18 V, VCC = VDRV    | I <sub>QVIN</sub>   | -    | 3.5  | 6.4  | mA    |

| (VCC Current Included)                                     |                                                                     | LDO disabled,<br>VIN = VDRV = VCC = 4.5 V |                     | -    | 3.5  | 6.4  |       |

| V <sub>IN</sub> Shutdown Current<br>(VCC Current Included) | EN low<br>T <sub>A</sub> = T <sub>J</sub> = 25 °C                   | LDO enabled,<br>VIN = 18 V, VCC = VDRV    | I <sub>SDVIN</sub>  | -    | 42   | 60   | μΑ    |

|                                                            |                                                                     | LDO disabled,<br>VIN = VDRV = VCC = 4.5 V |                     | -    | 63   | 150  | 1     |

| 5V Linear Regulator                                        |                                                                     |                                           |                     |      |      |      |       |

| Output Voltage                                             | 6V < VIN < 18 V, IDR\<br>EN high, no switching                      | / = 0 to 30 mA (External)                 | V <sub>DRV</sub>    | 4.8  | 5.07 | 5.4  | V     |

| Dropout Voltage                                            | VIN = 5 V, IDRV = 50<br>no switching                                | V <sub>DO</sub>                           |                     |      | 200  | mV   |       |

| PWM MODULATION                                             |                                                                     |                                           |                     |      |      |      |       |

| Minimum On Time                                            | (Note 6)                                                            |                                           | T <sub>on_min</sub> |      | 50   |      | ns    |

| Minimum Off Time                                           | (Note 6)                                                            | T <sub>off_min</sub>                      |                     | 150  |      | ns   |       |

| VOLTAGE REGULATION                                         |                                                                     |                                           |                     |      |      |      |       |

| Regulated Feedback Voltage                                 | FB to VSNS-                                                         |                                           | V <sub>FB</sub>     | 795  | 800  | 805  | mV    |

| VOLTAGE ERROR AMPLIFI                                      | ER                                                                  |                                           |                     |      |      |      |       |

| FB, VSNS- Bias Current                                     | $V_{FB} = V_{VSNS-} = 1.0 V$                                        |                                           | I <sub>FB</sub>     | -50  |      | 50   | nA    |

| CURRENT-SENSE AMPLIF                                       | IER                                                                 |                                           |                     |      |      |      |       |

| Closed-Loop DC Gain                                        |                                                                     |                                           | GAIN <sub>CA</sub>  |      | -10  |      | V/V   |

| -3 dB Gain Bandwidth                                       | (Note 6)                                                            |                                           | BW <sub>CA</sub>    |      | 10   |      | MHz   |

| Input Offset Voltage                                       | V <sub>osCS</sub> = V <sub>SW</sub> - V <sub>PGND</sub><br>(Note 6) |                                           | V <sub>osCS</sub>   | -500 | -    | 500  | μV    |

| ENABLE                                                     |                                                                     |                                           |                     |      |      |      |       |

| EN ON Threshold                                            |                                                                     |                                           | V <sub>EN_TH</sub>  | 1.32 | 1.43 | 1.54 | V     |

| Hysteresis Resistance                                      |                                                                     |                                           | R <sub>HYS</sub>    |      | 40   |      | kΩ    |

| Hysteresis Current                                         |                                                                     |                                           | I <sub>EN_HYS</sub> |      | 5.4  |      | μΑ    |

| EN Input Leakage Current                                   | EN = 5 V                                                            |                                           | I <sub>EN_LK</sub>  |      |      | 1.0  | μΑ    |

| SWITCHING FREQUNCY                                         |                                                                     |                                           |                     |      |      |      |       |

| Switching Frequency in                                     | 1% Resistor from<br>MODE/FSET Pin to<br>AGND,<br>Vout = 5 V         | 2.49k or 14.0k                            | 800                 | 1000 |      | kHz  |       |

| CCM                                                        |                                                                     | 12.1k or float                            |                     |      | 800  |      | -     |

|                                                            |                                                                     | 0 or 10.5k                                |                     |      | 600  |      |       |

|                                                            | (Note 6)                                                            | 4.99k or 7.50k                            |                     |      | 500  |      |       |

| Source Current from Mode/<br>FSET Pin                      |                                                                     |                                           | I <sub>FSET</sub>   | 45   | 50   | 55   | μΑ    |

| ELECTRICAL CHARACTERISTICS (VIN =                           | 12 V, typical values are referenced to T | $T_A = T_J = 25^{\circ}C$ , Min and Max values are referenced |

|-------------------------------------------------------------|------------------------------------------|---------------------------------------------------------------|

| to $T_A = T_J = -40^{\circ}C$ to 125°C. unless other noted. |                                          |                                                               |

| Characteristics                                      | Test Conditions                |                            | Symbol                | MIN  | TYP   | MAX  | UNITS  |

|------------------------------------------------------|--------------------------------|----------------------------|-----------------------|------|-------|------|--------|

| SOFT START                                           |                                |                            |                       |      |       |      |        |

| System Reset Time                                    | Measured from EN to            | start of soft start        | T <sub>RST</sub>      |      | 0.7   |      | ms     |

| Soft Start Time                                      | 1% Resistor from SS            | 0 or 4.53k                 | T <sub>SS</sub>       |      | 1     |      | ms     |

|                                                      | Pin to AGND                    | 1.5k or 5.76k              |                       |      | 2     |      |        |

|                                                      |                                | 12.1k or float             |                       |      | 4     |      |        |

|                                                      |                                | 3.48k or 8.87k             |                       |      | 8     |      |        |

| Source Current from SS Pin                           |                                | •                          | I <sub>SS</sub>       | 45   | 50    | 55   | μΑ     |

| PGOOD                                                |                                |                            |                       |      |       |      |        |

| PGOOD Shutdown Delay                                 | From EN to PGOOD c<br>(Note 6) | le-assertion               |                       |      | 1.0   |      | μs     |

| PGOOD Low Voltage                                    | I <sub>PGOOD</sub> = 4 mA Sink |                            | V <sub>IPGOOD</sub>   |      |       | 0.3  | V      |

| PGOOD Leakage Current                                | PGOOD = 5 V                    |                            | I <sub>lkgPGOOD</sub> |      |       | 1.0  | μΑ     |

| PROTECTIONS                                          |                                |                            | -                     |      | -     | -    | -      |

| Valley Current Limit                                 | $T_A = T_J = 25^{\circ}C$      | R <sub>LIM</sub> = 24.9 kΩ | loc                   |      | 39    |      | А      |

| Threshold                                            | (Note 6)                       | R <sub>LIM</sub> = 21.5 kΩ |                       |      | 33    |      |        |

|                                                      |                                | R <sub>LIM</sub> = 16.2 kΩ |                       |      | 26    |      |        |

|                                                      |                                | R <sub>LIM</sub> = 12.1 kΩ |                       |      | 19    |      |        |

| Current Limit Temperature<br>Coefficient             | (Note 6)                       |                            |                       |      | -5900 |      | ppm/°C |

| Fast Under Voltage<br>Protection (FUVP)<br>Threshold | FB to AGND                     |                            |                       | 0.15 | 0.2   | 0.25 | V      |

| Fast Under Voltage<br>Protection (FUVP) Delay        | (Note 6)                       |                            |                       |      | 1.0   |      | μs     |

| Slow Under Voltage<br>Protection (SUVP)<br>Threshold | COMP to GND (Note 6)           |                            |                       |      | 3.0   |      | V      |

| Slow Under Voltage<br>Protection (SUVP) Delay        | (Note 6)                       |                            |                       |      | 50    |      | μs     |

| Over Voltage Threshold                               | FB rising                      |                            |                       | 0.95 | 1.0   | 1.05 | V      |

| Over Voltage Protection<br>Hysteresis                | FB falling (Note 6)            |                            |                       |      | -10   |      | mV     |

| Over Voltage Debounce<br>Time                        | FB rising to GL high           |                            |                       |      | 1.0   |      | μs     |

| Hiccup Idle Time                                     | Pin 35 is grounded (Note 6)    |                            |                       |      | 32    |      | ms     |

| Thermal Shutdown (TSD)<br>Threshold                  | (Note 6)                       |                            | T <sub>sd</sub>       | 140  | 150   |      | °C     |

| Recovery Temperature<br>Threshold                    | (Note 6)                       |                            | T <sub>rec</sub>      |      | 125   |      | °C     |

| Thermal Shutdown (TSD)<br>Debounce Time              | (Note 6)                       |                            |                       |      | 50    |      | ns     |

|                                                      | 1                              |                            |                       |      |       |      | 1      |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.6. Guaranteed by design, not tested in production.

## **DETAILED DESCRIPTION**

### General

The NCP3284, a single-phase synchronous buck regulator, integrates power MOSFETs to provide a high-efficiency and compact-footprint power management solution. The NCP3284 is able to deliver up to 30 A TDC output current on a wide output voltage range. Operating in high switching frequency up to 1 MHz allows employing small size inductors and capacitors while maintaining high efficiency due to integrated solution with high performance power MOSFETs. It provides differential voltage sense, flexible soft-start programming, and comprehensive protections.

#### **Operation Modes**

Operation mode and switching frequency are programmed at MODE/FSET pin with a  $\pm 1\%$  tolerance resistor as shown in Table 1.

### Table 1. MODE AND SWITCHING FREQUENCY CONFIGURATION

| Resistance @ MODE/FSET Pin ( $\Omega, \pm 1\%$ ) | Frequency (kHz) | Operation Mode |

|--------------------------------------------------|-----------------|----------------|

| 0                                                | 600             | FCCM           |

| 2.49k                                            | 1000            | FCCM           |

| 4.99k                                            | 500             | Auto CCM/DCM   |

| 7.5k                                             | 500             | FCCM           |

| 10.5k                                            | 600             | Auto CCM/DCM   |

| 12.1k                                            | 800             | Auto CCM/DCM   |

| 14.0k                                            | 1000            | Auto CCM/DCM   |

| Float                                            | 800             | FCCM           |

#### **Current-Mode RPM Operation**

The NCP3284 operates with the current-mode Ramp-Pulse-Modulation (RPM) scheme. In Forced CCM mode, the inductor current is always continuous and the device operates in quasi-fixed switching frequency, which has a typical value programmed by users through a resistor at pin MODE/FSET. In Auto CCM/DCM mode, the inductor current is continuous and the device operates in quasi-fixed switching frequency in medium and heavy load range, while the inductor current becomes discontinuous and the device automatically operates in PFM mode with an adaptive fixed on time and variable switching frequency in light load range.

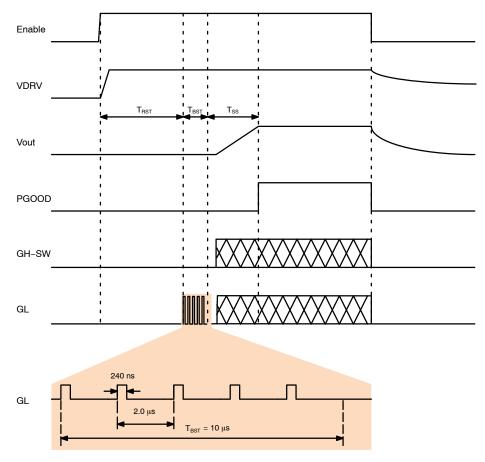

### Soft Start and Shut Down

The NCP3284 has a soft start function which also operates well under a pre-biased output condition. The NCP3284's soft start time is externally programmed at SS pins. The output starts to ramp up following a system reset period TRST, 0.7 ms typical, after the device is enabled. When the device is disabled or UVLO happens, the device shuts down immediately and both high–side and low–side MOSFETs are off. A timing diagram of power up/down is shown in Figure 4.

Figure 4. Timing Diagram of Power Up/Down Sequence

#### **Bootstrap Capacitor Voltage Refreshing**

In the NCP3284, a bootstrap circuit is employed to provide supply voltage for high-side gate driver. An external 0.22  $\mu$ F/25 V ceramic capacitor is connected between BOOT pin and PHASE pin to hold up the bootstrap voltage. In order to charge up this capacitor just before a soft start, 5 consecutive pulses are sent to GL, gate of the low-side MOSFET, as shown in Figure 4.

In forced CCM mode, the bootstrap voltage is refreshed cycle-by-cycle and always fully charged. However, a

special care needs to be taken in applications with Vout  $\geq$  1.8 V and auto DCM/CCM mode enabled. To make sure the bootstrap capacitor has an enough voltage level for proper operation of high-side gate driver, there is a minimum load requirement to limit the minimum switching frequency not to go below 2 kHz. For a typical 5 V output application with auto DCM/CCM mode enabled, the minimum load current may need to be higher than 2 mA.

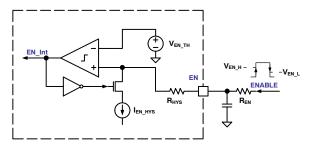

#### **Enable and Input UVLO**

The NCP3284 is enabled when the voltage at EN pin is higher than a summing voltage level of an internal threshold  $V_{EN_TH}$  and a hysteresis. The hysteresis can be programmed by an external resistor REN connected to EN pin as shown in Figure 5. The high threshold  $V_{EN_H}$  in ENABLE signal is

$$V_{\text{EN}_{H}} = V_{\text{EN}_{TH}} + V_{\text{EN}_{HYS}}$$

(eq. 1)

Figure 5. Enable and Hysteresis Programming

The low threshold  $V_{EN\ L}$  in ENABLE signal is

$$V_{\text{EN}_{L}} = V_{\text{EN}_{TH}}$$

(eq. 2)

The hysteresis V<sub>EN HYS</sub> is

$$V_{\text{EN}_{\text{HYS}}} = I_{\text{EN}_{\text{HYS}}} \times (R_{\text{HYS}} + R_{\text{EN}})$$

(eq. 3)

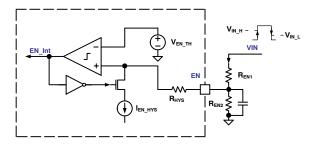

A UVLO function for input power supply can be implemented at EN pin. As shown in Figure 6, the UVLO threshold can be programmed by two external resistors. The low threshold  $V_{IN\ L}$  in  $V_{IN}$  signal is

$$V_{IN\_L} = \left(\frac{R_{EN1}}{R_{EN2}} + 1\right) \times V_{EN\_TH}$$

(eq. 4)

The high threshold  $V_{IN H}$  in  $V_{IN}$  signal is

V<sub>IN H</sub>

$$= V_{IN_L} + V_{IN_HYS}$$

(eq. 5)

The hysteresis V<sub>IN HYS</sub> is

$$V_{IN\_HYS} = I_{EN\_HYS} \times \left( R_{HYS} \left( 1 + \frac{R_{EN1}}{R_{EN2}} \right) + R_{EN1} \right)$$

(eq. 6)

Figure 6. Enable and Input Supply UVLO Circuit

To avoid undefined operation, EN pin should not be left float in applications.

#### **Over Current Protection (OCP)**

The NCP3284 protects converter from over current by a cycle–by–cycle current limitation. The average current limit

ILMT can be calculated from the programmed valley current limit ILMT\_Valley and inductor current ripple.

$$\begin{split} I_{LMT} &= I_{LMT\_Valley} + \frac{V_o \times (V_{IN} - V_o)}{2 \times V_{In} \times L \times F_{SW}} \\ &= 1.5412 \times R_{Ilim} + \frac{V_o \times (V_{IN} - V_o)}{2 \times V_{IN} \times L \times F_{SW}} \end{split} \tag{eq. 7}$$

where  $R_{Ilim}$  is resistance of the programming resistor at ILIM pin,  $V_{IN}$  is input voltage,  $V_O$  is output voltage, L is filter inductance, and  $F_{SW}$  is nominal switching frequency.

OCP detection starts from the beginning of soft-start time  $T_{SS}$ , and it ends in shutdown, latch-off, and hiccup idle time. The inductor current is monitored by voltage sensing between SW pin and PGND pin. If over current happens and lasts for more than 50  $\mu$ s, the device turns to either latch-off or hiccup. The device may enter into under voltage protection before OCP latch-off/hiccup happens if the output voltage drops down very fast.

#### **Under Voltage Protection (UVP)**

UVP detection starts when PGOOD delay  $T_{d\_PGOOD}$  is expired right after a soft start, and it ends in shutdown, latch-off, and hiccup idle time. The NCP3284 pulls PGOOD low and turns off both high-side and low-side MOSFETs once FB voltage drops below 0.2 V for more than 1.0  $\mu$ s.

#### **Over Voltage Protection (OVP)**

OVP detection starts from the beginning of soft-start time TSS, and it ends in shutdown, latch-off, and hiccup idle time. During normal operation the output voltage is monitored at FB pin. If FB voltage exceeds the OVP threshold for more than 1  $\mu$ s, OVP is triggered and PGOOD is pulled low. In the meanwhile, the high-side MOSFET is latched off and the low-side MOSFET is turned on. After the OVP trips, the DAC ramps slowly down to zero, having a negative slew rate as the same value of soft start to reduce negative output voltage spike. The low-side MOSFET toggles between on and off as the output voltage follows the DAC ramping down. After the DAC gets to zero, the high-side MOSFET holds off and the low-side MOSFET keeps on.

#### Latch–Off or Hiccup in Protections

The NCP3284 can be configured to have either latch-off mode or hiccup mode, for the protections (OCP, UVP, and OVP), by means of leaving pin 35 float or shorting it to ground.

To restart the device after latch-off, the system needs to have either VCC or EN toggled state and then a normal power-up sequence follows including system reset and auto calibration.

If hiccup mode is selected, the NCP3284 starts to count idle time of 32 ms once PGOOD is pulled low due to any of the protections. After the end of the hiccup idle time, a normal power up sequence happens including system reset and auto calibration.

## Thermal Shutdown (TSD)

The NCP3284 has an internal thermal shutdown protection to protect the device from overheating in an extreme case that the die temperature exceeds 150°C. TSD detection is activated when VCC and EN are valid. Once the thermal protection is triggered, the whole chip shuts down. If the temperature drops below 125°C, the system automatically recovers and a normal power–up sequence follows.

#### Power Good (PGOOD)

PGOOD is asserted in normal operation after soft start ends, and it is pulled low in protections and shutdown. PGOOD pin is an open-drain pin and its internal pull-down control circuit is powered by VCC. To avoid an invalid PGOOD indication when VCC is not ready, it is recommended to have the external pull-up resistor at PGOOD pin to be connected to either VCC or an external voltage source which always keeps not being higher than VCC level.

### LAYOUT GUIDELINES

#### **Electrical Layout Considerations**

Good electrical layout is a key to make sure proper operation, high efficiency, and noise reduction. Electrical layout guidelines are:

- *Power Paths*: Use wide and short traces for power paths (such as VIN, VOUT, SW, and PGND) to reduce parasitic inductance and high–frequency loop area. It is also good for efficiency improvement

- *Power Supply Decoupling*: The device should be well decoupled by input capacitors and input loop area should be as small as possible to reduce parasitic inductance, input voltage spike, and noise emission. Usually, a small low–ESL MLCC is placed very close to PVIN and PGND pins

- *VCC Decoupling*: Place decoupling caps as close as possible to the controller VCC and VDRV pins. The filter resistor at VCC pin should be not higher than 2.2  $\Omega$  to prevent large voltage drop

- *Switching Node*: SW node should be a copper pour, but compact because it is also a noise source

- *Bootstrap*: The bootstrap cap and an option resistor need to be very close and directly connected between pin 26 (BST) and pin 25 (PHASE). No need to externally connect pin 25 to SW node because it has been internally connected to other SW pins

- *Ground*: It would be good to have multiple ground planes. Directly connect the exposed PGND pad to ground plane through multiple vias. Connect AGND pin to ground planes through a via close to the pin

- *Voltage Sense*: Use Kelvin sense pair and arrange a "quiet" path for the differential output voltage sense. Keep the FB trace short to minimize its capacitance to ground

#### Thermal Layout Considerations

Good thermal layout helps high power dissipation from a small package with reduced temperature rise. Thermal layout guidelines are:

- The exposed pads must be well soldered on the board

- A four or more layers PCB board with solid ground planes is preferred for better heat dissipation

- More free vias are welcome to be around IC and underneath the exposed pads to connect the inner ground layers to reduce thermal impedance

- Use large area copper pour to help thermal conduction and radiation

- Do not put the inductor to be too close to the IC, thus the heat sources are distributed

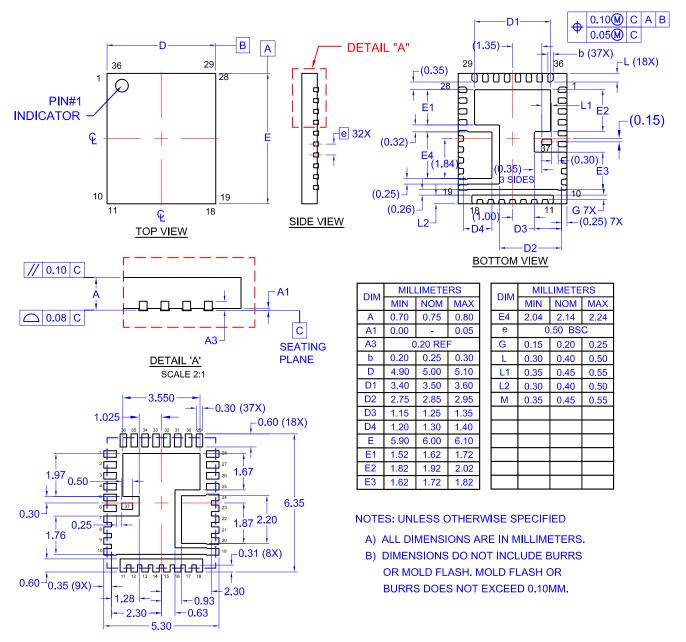

#### PACKAGE DIMENSIONS

PQFN37 5x6, 0.5P CASE 483BZ ISSUE O

DATE 13 DEC 2017

LAND PATTERN RECOMMENDATION

ON Semiconductor and are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at <u>www.onsemi.com/site/pdf/Patent-Marking.pdf</u>. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor has against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death ass

#### PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor 19521 E. 32nd Pkwy, Aurora, Colorado 80011 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800–282–9855 Toll Free USA/Canada Europe, Middle East and Africa Technical Support:

Europe, Middle East and Africa Technical Support: Order Li Phone: 421 33 790 2910

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative

$\diamond$