# X67BC8513.L12

## 1 General information

## 1.1 Other applicable documents

For additional and supplementary information, see the following documents.

## Other applicable documents

| Document name | Title                    |

|---------------|--------------------------|

| MAX67         | X67 system user's manual |

| MAEMV         | Installation / EMC guide |

## 1.2 Order data

| Order number  | Short description                                                                                                                                                                                                                                                       | Figure |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

|               | Bus controller modules                                                                                                                                                                                                                                                  |        |

| X67BC8513.L12 | X67 bus controller, 1 POWERLINK interface, X2X Link power supply 15 W, 12 digital channels configurable as inputs or outputs, 24 VDC, 0.5 A, configurable input filter, 1 event counters 50 kHz, 1 analog input 0 to 20 mA, 12-bit, M12 connectors, high-density module |        |

Table 1: X67BC8513.L12 - Order data

| Required accessories                                                                                  |

|-------------------------------------------------------------------------------------------------------|

| See "Required cables and connectors" on page 10.                                                      |

| For a general overview, see section "Accessories - General overview" in the X67 system user's manual. |

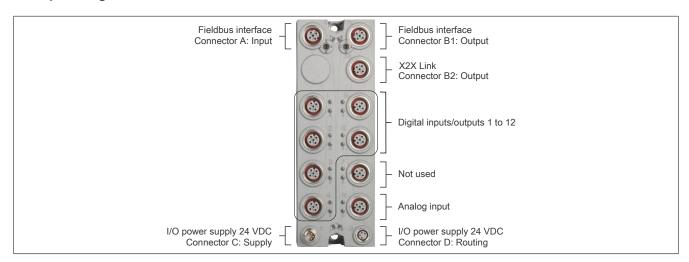

### 1.3 Module description

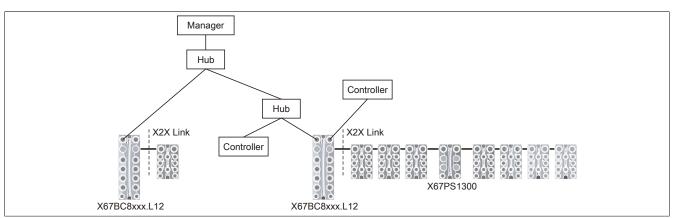

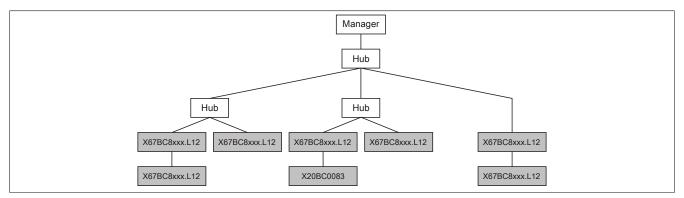

The bus controller makes it possible to connect X2X Link I/O nodes to POWERLINK. It is also possible to operate the X2X Link cycle synchronously 1:1 or synchronous to POWERLINK using a prescaler.

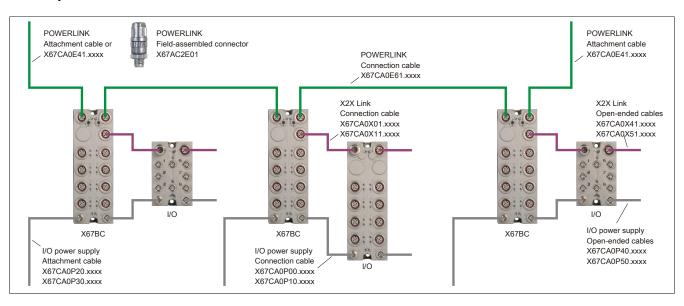

Additional X2X Link I/O nodes (X67 modules or other modules based on X2X Link) can be connected using the integrated X2X Link connection. Mechanically, POWERLINK is connected via an IP67-protected standard D-coded M12 Ethernet connector.

The interface is equipped with 2 connections. Both connections are connected to an integrated switch. This makes it easy to implement daisy chain cabling.

#### Functions:

- POWERLINK

- · Digital inputs

- · Event counter / Gate measurement

- Analog input

- · Digital outputs

- · Monitoring the input signal

### **POWERLINK**

POWERLINK is a standard protocol for Fast Ethernet equipped with hard real-time characteristics.

#### **Digital inputs**

The digital inputs are equipped with an input filter with a configurable input delay. The input states can also be latched if required.

#### **Event counter / Gate measurement**

The module has 1 counter channel that can be used either as an event counter or for gate measurement.

#### Analog input filter

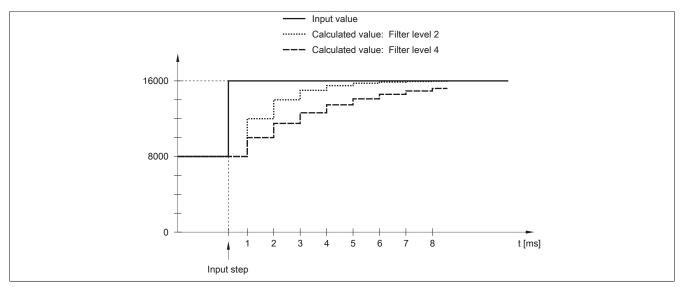

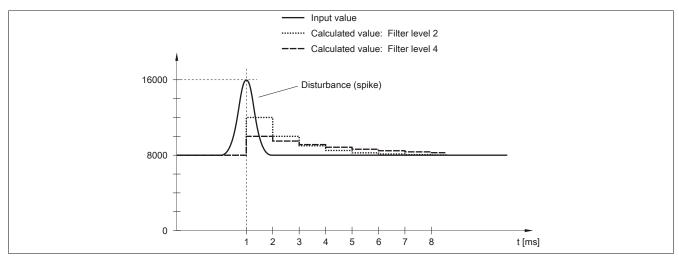

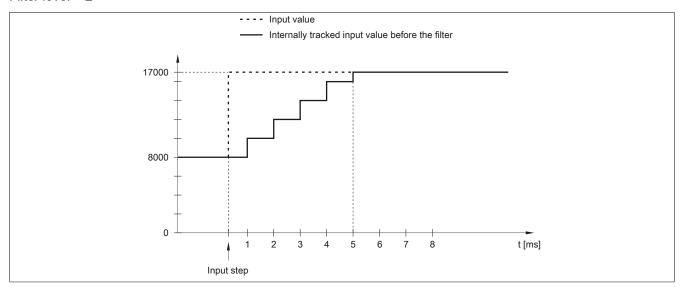

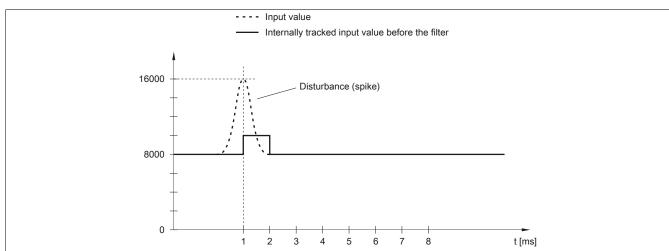

The module is equipped with 1 analog input with configurable input filter with input ramp limiting.

#### Monitoring status of the digital outputs

The output signal of the digital outputs is monitored for short circuit or overload.

## Monitoring the input signal

The input signal of the analog inputs is monitored against the upper and lower limit values. Other limit values can be defined if necessary.

# 2 Technical description

## 2.1 Technical data

| Order number                                       | X67BC8513.L12                                                                                                                  |  |

|----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|--|

| Short description                                  |                                                                                                                                |  |

| Bus controller                                     | POWERLINK (V1/V2) controlled node                                                                                              |  |

| General information                                |                                                                                                                                |  |

| Inputs/Outputs                                     | 12 digital channels (configurable as inputs or outputs using the software, inputs with additional functions), 1 analog channel |  |

| Insulation voltage between channel and bus         | 500 V <sub>eff</sub>                                                                                                           |  |

| Nominal voltage                                    | 24 VDC                                                                                                                         |  |

| B&R ID code                                        | 2.150                                                                                                                          |  |

| Bus controller                                     | 0xB3AC                                                                                                                         |  |

| Internal I/O module                                | 0xB3CD                                                                                                                         |  |

| Sensor/Actuator power supply                       | 0.5 A summation current                                                                                                        |  |

| Status indicators                                  | I/O function per channel, supply voltage, bus function                                                                         |  |

| Diagnostics                                        | 1/O function per charmer, supply voltage, bus function                                                                         |  |

| Outputs                                            | Voc. using LED status indicator and software                                                                                   |  |

| ·                                                  | Yes, using LED status indicator and software                                                                                   |  |

| I/O power supply                                   | Yes, using LED status indicator and software                                                                                   |  |

| Support                                            | V                                                                                                                              |  |

| Dynamic node allocation (DNA)                      | Yes                                                                                                                            |  |

| Connection type                                    |                                                                                                                                |  |

| Fieldbus                                           | M12, D-coded                                                                                                                   |  |

| X2X Link                                           | M12, B-coded                                                                                                                   |  |

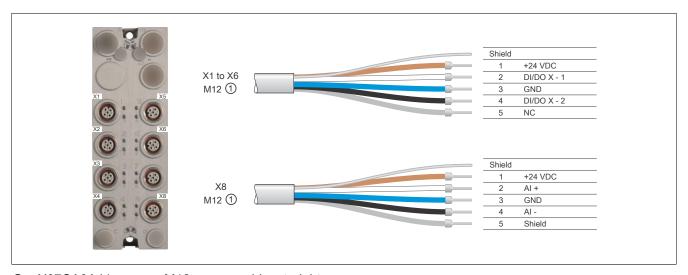

| Inputs/Outputs                                     | 8x M12, A-coded                                                                                                                |  |

| I/O power supply                                   | M8, 4-pin                                                                                                                      |  |

| Power output                                       | 15 W X2X Link power supply for I/O modules                                                                                     |  |

| Power consumption                                  |                                                                                                                                |  |

| Fieldbus                                           | 2.5 W                                                                                                                          |  |

| Internal I/O                                       | 0.6 W                                                                                                                          |  |

| X2X Link power supply                              | 17.25 W at maximum power output for connected I/O modules                                                                      |  |

| Certifications                                     | ·                                                                                                                              |  |

| CE                                                 | Yes                                                                                                                            |  |

| UKCA                                               | Yes                                                                                                                            |  |

| ATEX                                               | Zone 2, II 3G Ex nA IIA T5 Gc                                                                                                  |  |

| 71127                                              | IP67, Ta = 0 - Max. 60°C                                                                                                       |  |

|                                                    | TÜV 05 ATEX 7201X                                                                                                              |  |

| UL                                                 | cULus E115267                                                                                                                  |  |

|                                                    | Industrial control equipment                                                                                                   |  |

| HazLoc                                             | cCSAus 244665                                                                                                                  |  |

|                                                    | Process control equipment                                                                                                      |  |

|                                                    | for hazardous locations                                                                                                        |  |

|                                                    | Class I, Division 2, Groups ABCD, T5                                                                                           |  |

| EAC                                                | Yes                                                                                                                            |  |

| KC                                                 | Yes                                                                                                                            |  |

| Interfaces                                         |                                                                                                                                |  |

| Fieldbus                                           | POWERLINK (V1/V2) controlled node                                                                                              |  |

| Туре                                               | Type 2 1)                                                                                                                      |  |

| Variant                                            | 2x M12 interface (hub), 2x female connector on module                                                                          |  |

| Line length                                        | Max. 100 m between 2 stations (segment length)                                                                                 |  |

| Transfer rate                                      | 100 Mbit/s                                                                                                                     |  |

| Transfer                                           |                                                                                                                                |  |

| Physical layer                                     | 100BASE-TX                                                                                                                     |  |

| Half-duplex                                        | Yes                                                                                                                            |  |

| Full-duplex                                        | No                                                                                                                             |  |

| Autonegotiation                                    | Yes                                                                                                                            |  |

| Auto-MDI/MDIX                                      | Yes                                                                                                                            |  |

| Hub propagation delay                              | 0.96 to 1 μs                                                                                                                   |  |

| · · · ·                                            | υ. ου ιυ ι με                                                                                                                  |  |

| Min. cycle time 2)                                 | 000                                                                                                                            |  |

| Fieldbus                                           | 200 μs                                                                                                                         |  |

| X2X Link                                           | 200 μs                                                                                                                         |  |

| Synchronization between bus systems possible       | Yes                                                                                                                            |  |

| I/O power supply                                   |                                                                                                                                |  |

| Nominal voltage                                    | 24 VDC                                                                                                                         |  |

| Voltage range                                      | 18 to 30 VDC                                                                                                                   |  |

| Integrated protection                              | Reverse polarity protection                                                                                                    |  |

| Power consumption                                  |                                                                                                                                |  |

| Sensor/Actuator power supply                       | Max. 12 W <sup>3)</sup>                                                                                                        |  |

| Sensor/Actuator power supply                       |                                                                                                                                |  |

| Voltage                                            | I/O power supply minus voltage drop for short-circuit protection                                                               |  |

|                                                    |                                                                                                                                |  |

| Voltage drop for short-circuit protection at 0.5 A | Max. 2 VDC                                                                                                                     |  |

Table 2: X67BC8513.L12 - Technical data

| Order number                                                                                                                                                                                                                                                                                                                                            | X67BC8513.L12                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Short-circuit proof                                                                                                                                                                                                                                                                                                                                     | Yes                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| Digital inputs                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| Input characteristics per EN 61131-2                                                                                                                                                                                                                                                                                                                    | Type 1                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| Input voltage                                                                                                                                                                                                                                                                                                                                           | 18 to 30 VDC                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| Input current at 24 VDC                                                                                                                                                                                                                                                                                                                                 | Typ. 4 mA                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| Input circuit                                                                                                                                                                                                                                                                                                                                           | Sink                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| Input filter Hardware                                                                                                                                                                                                                                                                                                                                   | ≤10 µs (channels 1 to 4) / ≤70 µs (channels 5 to 12)                                                                                                                                                                                                                                                                                                                                                                  |  |

| Software                                                                                                                                                                                                                                                                                                                                                | Default 0 ms, configurable between 0 and 25 ms in 0.2 ms intervals                                                                                                                                                                                                                                                                                                                                                    |  |

| Input resistance                                                                                                                                                                                                                                                                                                                                        | Default 0 ms, configurable between 0 and 25 ms in 0.2 ms intervals  Typ. 6 kΩ                                                                                                                                                                                                                                                                                                                                         |  |

| Additional functions                                                                                                                                                                                                                                                                                                                                    | 50 kHz event counting, gate measurement                                                                                                                                                                                                                                                                                                                                                                               |  |

| Switching threshold                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| Low                                                                                                                                                                                                                                                                                                                                                     | <5 VDC                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| High                                                                                                                                                                                                                                                                                                                                                    | >15 VDC                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| Event counters                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| Quantity                                                                                                                                                                                                                                                                                                                                                | 1                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| Signal form Evaluation                                                                                                                                                                                                                                                                                                                                  | Square wave pulse                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| Input frequency                                                                                                                                                                                                                                                                                                                                         | Each negative edge, cyclic counter  Max. 50 kHz                                                                                                                                                                                                                                                                                                                                                                       |  |

| Counter 1                                                                                                                                                                                                                                                                                                                                               | Input 1                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| Counter frequency                                                                                                                                                                                                                                                                                                                                       | Max. 50 kHz                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| Counter size                                                                                                                                                                                                                                                                                                                                            | 16-bit                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| Gate measurement                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| Quantity                                                                                                                                                                                                                                                                                                                                                | 1                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| Signal form                                                                                                                                                                                                                                                                                                                                             | Square wave pulse                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| Evaluation                                                                                                                                                                                                                                                                                                                                              | Positive edge - Negative edge                                                                                                                                                                                                                                                                                                                                                                                         |  |

| Counter frequency                                                                                                                                                                                                                                                                                                                                       | (6.11)                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| Internal                                                                                                                                                                                                                                                                                                                                                | 48 MHz, 3 MHz, 187.5 kHz                                                                                                                                                                                                                                                                                                                                                                                              |  |

| Counter size                                                                                                                                                                                                                                                                                                                                            | 16-bit                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| Length of pause between pulses Pulse length                                                                                                                                                                                                                                                                                                             | ≥100 µs<br>≥20 µs                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| Supported inputs                                                                                                                                                                                                                                                                                                                                        | Input 2                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| Analog inputs                                                                                                                                                                                                                                                                                                                                           | 11put 2                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| Input                                                                                                                                                                                                                                                                                                                                                   | 0 to 20 mA                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| Input type                                                                                                                                                                                                                                                                                                                                              | Differential input                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| Digital converter resolution                                                                                                                                                                                                                                                                                                                            | 12-bit                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| Conversion time                                                                                                                                                                                                                                                                                                                                         | 200 μs                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| Output format                                                                                                                                                                                                                                                                                                                                           | INT                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| Output format                                                                                                                                                                                                                                                                                                                                           | 0.0000 0.7555/41.00 0.0000 4.000 4                                                                                                                                                                                                                                                                                                                                                                                    |  |

| Current<br>Load                                                                                                                                                                                                                                                                                                                                         | 0x0000 - 0x7FFF / 1 LSB = 0x0008 = 4.883 μA<br><300 Ω                                                                                                                                                                                                                                                                                                                                                                 |  |

| Input protection                                                                                                                                                                                                                                                                                                                                        | Protection against wiring with supply voltage                                                                                                                                                                                                                                                                                                                                                                         |  |

| Permissible input signal                                                                                                                                                                                                                                                                                                                                | Max. ±30 mA                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| Output of digital value during overload                                                                                                                                                                                                                                                                                                                 | Max. 200 Hill                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| Undershoot                                                                                                                                                                                                                                                                                                                                              | 0x0000                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| Overshoot                                                                                                                                                                                                                                                                                                                                               | 0x7FFF                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| Conversion procedure                                                                                                                                                                                                                                                                                                                                    | Successive approximation                                                                                                                                                                                                                                                                                                                                                                                              |  |

| Max. error                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| Gain                                                                                                                                                                                                                                                                                                                                                    | 0.1% 4)                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| Offset                                                                                                                                                                                                                                                                                                                                                  | 0.05% 5)                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| Max. gain drift                                                                                                                                                                                                                                                                                                                                         | 0.013 %/°C <sup>4)</sup>                                                                                                                                                                                                                                                                                                                                                                                              |  |

| Max. gain drift Max. offset drift                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| Max. gain drift Max. offset drift Common-mode rejection                                                                                                                                                                                                                                                                                                 | 0.013 %/°C <sup>4)</sup><br>0.02 %/°C <sup>5)</sup>                                                                                                                                                                                                                                                                                                                                                                   |  |

| Max. gain drift  Max. offset drift  Common-mode rejection  DC                                                                                                                                                                                                                                                                                           | 0.013 %/°C <sup>4)</sup> 0.02 %/°C <sup>5)</sup> >50 dB                                                                                                                                                                                                                                                                                                                                                               |  |

| Max. gain drift  Max. offset drift  Common-mode rejection  DC  50 Hz                                                                                                                                                                                                                                                                                    | 0.013 %/°C <sup>4)</sup><br>0.02 %/°C <sup>5)</sup>                                                                                                                                                                                                                                                                                                                                                                   |  |

| Max. gain drift  Max. offset drift  Common-mode rejection  DC                                                                                                                                                                                                                                                                                           | 0.013 %/°C <sup>4)</sup> 0.02 %/°C <sup>5)</sup> >50 dB >50 dB                                                                                                                                                                                                                                                                                                                                                        |  |

| Max. gain drift  Max. offset drift  Common-mode rejection  DC  50 Hz  Common-mode range                                                                                                                                                                                                                                                                 | 0.013 %/°C <sup>4)</sup> 0.02 %/°C <sup>5)</sup> >50 dB  >50 dB  ±2 V                                                                                                                                                                                                                                                                                                                                                 |  |

| Max. gain drift  Max. offset drift  Common-mode rejection  DC  50 Hz  Common-mode range  Crosstalk between channels                                                                                                                                                                                                                                     | 0.013 %/°C <sup>4)</sup> 0.02 %/°C <sup>5)</sup> >50 dB  >50 dB  ±2 V  >70 dB                                                                                                                                                                                                                                                                                                                                         |  |

| Max. gain drift  Max. offset drift  Common-mode rejection  DC  50 Hz  Common-mode range  Crosstalk between channels  Nonlinearity  Insulation voltage between input and bus  Voltage drop at 20 mA                                                                                                                                                      | 0.013 %/°C <sup>4)</sup> 0.02 %/°C <sup>5)</sup> >50 dB  >50 dB  ±2 V  >70 dB  <0.1% <sup>5)</sup>                                                                                                                                                                                                                                                                                                                    |  |

| Max. gain drift  Max. offset drift  Common-mode rejection  DC  50 Hz  Common-mode range  Crosstalk between channels  Nonlinearity  Insulation voltage between input and bus  Voltage drop at 20 mA  Input filter                                                                                                                                        | 0.013 %/°C <sup>4)</sup> 0.02 %/°C <sup>5)</sup> >50 dB >50 dB ±2 V >70 dB <0.1% <sup>5)</sup> 500 V <sub>eff</sub> Typ. 4.5 V                                                                                                                                                                                                                                                                                        |  |

| Max. gain drift  Max. offset drift  Common-mode rejection  DC  50 Hz  Common-mode range  Crosstalk between channels  Nonlinearity  Insulation voltage between input and bus  Voltage drop at 20 mA  Input filter  Cutoff frequency                                                                                                                      | 0.013 %/°C <sup>4)</sup> 0.02 %/°C <sup>5)</sup> >50 dB >50 dB  ±2 V >70 dB <0.1% <sup>5)</sup> 500 V <sub>eff</sub> Typ. 4.5 V                                                                                                                                                                                                                                                                                       |  |

| Max. gain drift  Max. offset drift  Common-mode rejection  DC  50 Hz  Common-mode range  Crosstalk between channels  Nonlinearity  Insulation voltage between input and bus  Voltage drop at 20 mA  Input filter  Cutoff frequency  Slope                                                                                                               | 0.013 %/°C <sup>4)</sup> 0.02 %/°C <sup>5)</sup> >50 dB >50 dB ±2 V >70 dB <0.1% <sup>5)</sup> 500 V <sub>eff</sub> Typ. 4.5 V                                                                                                                                                                                                                                                                                        |  |

| Max. gain drift  Max. offset drift  Common-mode rejection  DC  50 Hz  Common-mode range  Crosstalk between channels  Nonlinearity  Insulation voltage between input and bus  Voltage drop at 20 mA  Input filter  Cutoff frequency  Slope  Digital outputs                                                                                              | 0.013 %/°C 4) 0.02 %/°C 5)  >50 dB >50 dB  ±2 V >70 dB <0.1% 5) 500 V <sub>eff</sub> Typ. 4.5 V                                                                                                                                                                                                                                                                                                                       |  |

| Max. gain drift  Max. offset drift  Common-mode rejection  DC  50 Hz  Common-mode range  Crosstalk between channels  Nonlinearity  Insulation voltage between input and bus  Voltage drop at 20 mA  Input filter  Cutoff frequency  Slope  Digital outputs  Variant                                                                                     | 0.013 %/°C <sup>4)</sup> 0.02 %/°C <sup>5)</sup> >50 dB >50 dB ±2 V >70 dB <0.1% <sup>5)</sup> 500 V <sub>eff</sub> Typ. 4.5 V  1 kHz 40 dB  Current-sourcing FET                                                                                                                                                                                                                                                     |  |

| Max. gain drift  Max. offset drift  Common-mode rejection  DC  50 Hz  Common-mode range  Crosstalk between channels  Nonlinearity  Insulation voltage between input and bus  Voltage drop at 20 mA  Input filter  Cutoff frequency  Slope  Digital outputs  Variant  Switching voltage                                                                  | 0.013 %/°C <sup>4)</sup> 0.02 %/°C <sup>5)</sup> >50 dB >50 dB  ±2 V >70 dB <0.1% <sup>5)</sup> 500 V <sub>eff</sub> Typ. 4.5 V  1 kHz 40 dB  Current-sourcing FET I/O power supply minus residual voltage                                                                                                                                                                                                            |  |

| Max. gain drift  Max. offset drift  Common-mode rejection  DC  50 Hz  Common-mode range  Crosstalk between channels  Nonlinearity  Insulation voltage between input and bus  Voltage drop at 20 mA  Input filter  Cutoff frequency  Slope  Digital outputs  Variant  Switching voltage  Nominal output current                                          | 0.013 %/°C <sup>4)</sup> 0.02 %/°C <sup>5)</sup> >50 dB >50 dB  ±2 V >70 dB <0.1% <sup>5)</sup> 500 V <sub>eff</sub> Typ. 4.5 V  1 kHz 40 dB  Current-sourcing FET I/O power supply minus residual voltage 0.5 A                                                                                                                                                                                                      |  |

| Max. gain drift  Max. offset drift  Common-mode rejection  DC  50 Hz  Common-mode range  Crosstalk between channels  Nonlinearity  Insulation voltage between input and bus  Voltage drop at 20 mA  Input filter  Cutoff frequency  Slope  Digital outputs  Variant  Switching voltage  Nominal output current  Total nominal current                   | 0.013 %/°C <sup>4)</sup> 0.02 %/°C <sup>5)</sup> >50 dB >50 dB ±2 V >70 dB <0.1% <sup>5)</sup> 500 V <sub>eff</sub> Typ. 4.5 V  1 kHz 40 dB  Current-sourcing FET I/O power supply minus residual voltage 0.5 A 8 A                                                                                                                                                                                                   |  |

| Max. gain drift  Max. offset drift  Common-mode rejection  DC  50 Hz  Common-mode range  Crosstalk between channels  Nonlinearity  Insulation voltage between input and bus  Voltage drop at 20 mA  Input filter  Cutoff frequency  Slope  Digital outputs  Variant  Switching voltage  Nominal output current  Total nominal current  Output circuit   | 0.013 %/°C <sup>4)</sup> 0.02 %/°C <sup>5)</sup> >50 dB >50 dB  ±2 V >70 dB <0.1% <sup>5)</sup> 500 V <sub>eff</sub> Typ. 4.5 V  1 kHz 40 dB  Current-sourcing FET I/O power supply minus residual voltage 0.5 A 8 A Source                                                                                                                                                                                           |  |

| Max. gain drift  Max. offset drift  Common-mode rejection  DC  50 Hz  Common-mode range  Crosstalk between channels  Nonlinearity  Insulation voltage between input and bus  Voltage drop at 20 mA  Input filter  Cutoff frequency  Slope  Digital outputs  Variant  Switching voltage  Nominal output current  Total nominal current                   | 0.013 %/°C <sup>4)</sup> 0.02 %/°C <sup>5)</sup> >50 dB >50 dB ±2 V >70 dB <0.1% <sup>5)</sup> 500 V <sub>eff</sub> Typ. 4.5 V  1 kHz 40 dB  Current-sourcing FET I/O power supply minus residual voltage 0.5 A 8 A                                                                                                                                                                                                   |  |

| Max. gain drift  Max. offset drift  Common-mode rejection  DC  50 Hz  Common-mode range  Crosstalk between channels  Nonlinearity  Insulation voltage between input and bus  Voltage drop at 20 mA  Input filter  Cutoff frequency  Slope  Digital outputs  Variant  Switching voltage  Nominal output current  Total nominal current  Output circuit   | 0.013 %/°C 4) 0.02 %/°C 5)  >50 dB >50 dB  ±2 V >70 dB <0.1% 5) 500 V <sub>eff</sub> Typ. 4.5 V  1 kHz 40 dB  Current-sourcing FET  I/O power supply minus residual voltage 0.5 A 8 A Source  Thermal shutdown in the event of overcurrent or short circuit, integrated protection                                                                                                                                    |  |

| Max. gain drift  Max. offset drift  Common-mode rejection  DC  50 Hz  Common-mode range  Crosstalk between channels  Nonlinearity  Insulation voltage between input and bus  Voltage drop at 20 mA  Input filter  Cutoff frequency Slope  Digital outputs  Variant  Switching voltage  Nominal output current  Total nominal current  Output protection | 0.013 %/°C <sup>4)</sup> 0.02 %/°C <sup>5)</sup> >50 dB >50 dB  \$50 dB  \$2 V  >70 dB  <0.1% <sup>5)</sup> 500 V <sub>eff</sub> Typ. 4.5 V  1 kHz 40 dB  Current-sourcing FET  I/O power supply minus residual voltage  0.5 A 8 A Source  Thermal shutdown in the event of overcurrent or short circuit, integrated protection for switching inductive loads, reverse polarity protection of the output power supply |  |

Table 2: X67BC8513.L12 - Technical data

| Order number                                       | X67BC8513.L12                                                             |  |

|----------------------------------------------------|---------------------------------------------------------------------------|--|

| Switching on after overload shutdown               | Approx. 10 ms (depends on the module temperature)                         |  |

| R <sub>DS(on)</sub>                                | 150 mΩ                                                                    |  |

| Residual voltage                                   | < 0.3 V at 0.5 A nominal current                                          |  |

| Peak short-circuit current                         | <12 A                                                                     |  |

| Switching delay                                    |                                                                           |  |

| 0 → 1                                              | <400 µs                                                                   |  |

| 1 → 0                                              | <400 µs                                                                   |  |

| Switching frequency                                |                                                                           |  |

| Resistive load                                     | Max. 100 Hz                                                               |  |

| Inductive load                                     | See section "Switching inductive loads".                                  |  |

| Braking voltage when switching off inductive loads | 50 VDC                                                                    |  |

| Electrical properties                              |                                                                           |  |

| Electrical isolation                               | Bus isolated from POWERLINK and channel Channel not isolated from channel |  |

| Operating conditions                               |                                                                           |  |

| Mounting orientation                               |                                                                           |  |

| Any                                                | Yes                                                                       |  |

| Installation elevation above sea level             |                                                                           |  |

| 0 to 2000 m                                        | No limitation                                                             |  |

| >2000 m                                            | Reduction of ambient temperature by 0.5°C per 100 m                       |  |

| Degree of protection per EN 60529                  | IP67                                                                      |  |

| Ambient conditions                                 |                                                                           |  |

| Temperature                                        |                                                                           |  |

| Operation                                          | -25 to 60°C                                                               |  |

| Derating                                           | •                                                                         |  |

| Storage                                            | -40 to 85°C                                                               |  |

| Transport                                          | -40 to 85°C                                                               |  |

| Mechanical properties                              |                                                                           |  |

| Dimensions                                         |                                                                           |  |

| Width                                              | 53 mm                                                                     |  |

| Height                                             | 155 mm                                                                    |  |

| Depth                                              | 42 mm                                                                     |  |

| Weight                                             | 360 g                                                                     |  |

| Torque for connections                             |                                                                           |  |

| M8                                                 | Max. 0.4 Nm                                                               |  |

| M12                                                | Max. 0.6 Nm                                                               |  |

Table 2: X67BC8513.L12 - Technical data

- For additional information, see section "Communication / POWERLINK / General information / Hardware CN" in Automation Help. The minimum cycle time specifies how far the bus cycle can be reduced without communication errors occurring. 1) 2) 3)

- The power consumption of the sensors and actuators connected to the module is not permitted to exceed 12 W.

- Based on the current measured value.

- Based on the entire measurement range.

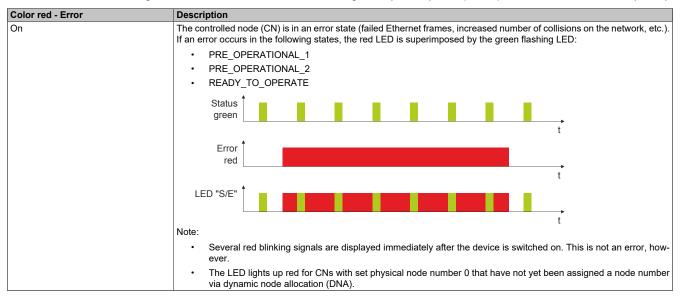

## 2.2 LED status indicators

| Figure                                         | LED                                                               | Color                 | Status            | Description                                                                                                      |

|------------------------------------------------|-------------------------------------------------------------------|-----------------------|-------------------|------------------------------------------------------------------------------------------------------------------|

|                                                | Status indicator 1: Status indicator for POWERLINK bus controller |                       |                   |                                                                                                                  |

| Status indicator 1:                            | L/A IF                                                            | Green                 | On                | The link to the remote station is established.                                                                   |

| Left: L/A IF1, Right: S/E                      | (Link/Active)                                                     |                       | Blinking          | The link to the remote station is established. The LED blinks if POWER-LINK activity is taking place on the bus. |

|                                                | S/E 1)<br>(Status/Error)                                          | Green/Red             |                   | LED states are described in section "Status/Error LED "S/E"" on page 6.                                          |

|                                                | I/O LEDs                                                          |                       |                   |                                                                                                                  |

|                                                | 1-1/2 to 6-1/2                                                    | Orange                | Input/Output s    | tate of the corresponding channel                                                                                |

| 1-1 5-1                                        | 7-1/2                                                             | Not used              |                   |                                                                                                                  |

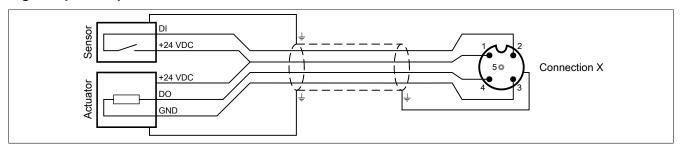

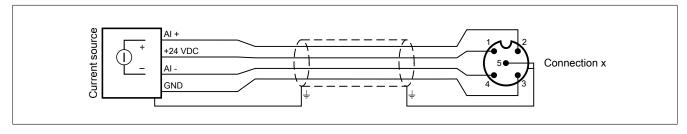

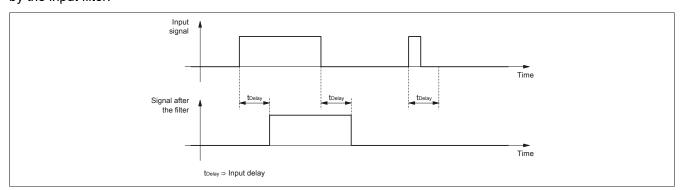

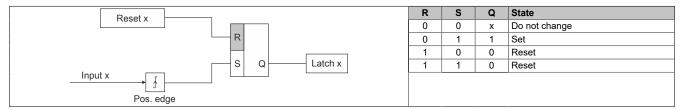

|                                                | 8-1                                                               | Green                 | On                | The analog-to-digital converter is running.                                                                      |