# **Advanced 1-Wire Master with Memory**

#### **General Description**

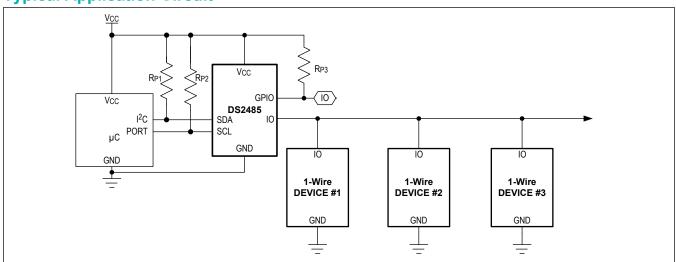

The DS2485 is a 1-Wire<sup>®</sup> master that performs protocol conversion between the I<sup>2</sup>C master and any attached 1-Wire slaves. For 1-Wire line driving, internal user-ad-justable timers relieve the system host processor from generating time-critical 1-Wire waveforms, supporting both standard and overdrive 1-Wire communication speeds. The 1-Wire master has selectable active or passive 1-Wire pullup. Strong pullup features support 1-Wire power delivery for 1-Wire devices that require this for EEPROMs and cryptographic computations.

### **Applications**

- Medical Instruments

- Industrial Sensors and Tools

- Limited-Use Consumables

- Printer Cartridge Identification

# Benefits and Features

- I<sup>2</sup>C Communication, up to 1MHz

- 1-Wire Standard and Overdrive Timing Communication Speeds

- 1-Wire Command Scripting Capability

- Adjustable 1-Wire Timing for t<sub>RSTL</sub>, t<sub>MSI</sub>, t<sub>MSP</sub>, t<sub>RSTH</sub>, t<sub>W0L</sub>, t<sub>W1L</sub>, t<sub>MSR</sub>, t<sub>REC</sub>, RPUP, and PDSLEW

- 0.75Kb of EEPROM for User Data

- One Open-Drain GPIO Pin

- Large 1-Wire Block Buffer (126 Bytes) for Efficient Data Transfer

- Operating Range: 2.97V to 3.63V, -40°C to +85°C

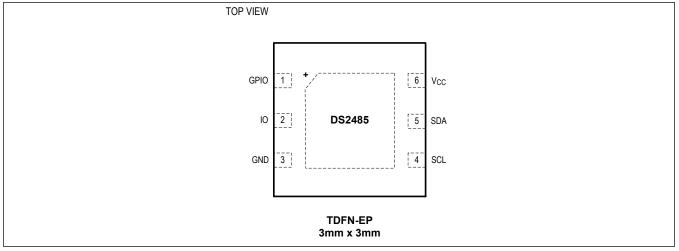

- 3mm x 3mm, 6-Pin TDFN-EP Package

Ordering Information appears at end of data sheet.

# **Typical Application Circuit**

# Advanced 1-Wire Master with Memory

### **Absolute Maximum Ratings**

| Voltage Range on Any Pin Relative to GND | 0.5V to 4.0V  |

|------------------------------------------|---------------|

| Maximum Current into Any Pin             | 20mA to 20mA  |

| Operating Temperature Range              | 40°C to +85°C |

| Junction Temperature                     | +150°C        |

| Storage Temperature Range         | 40°C to +125°C |

|-----------------------------------|----------------|

| Lead Temperature (soldering, 10s) | +300°C         |

| Soldering Temperature (reflow)    | +260°C         |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# **Package Information**

#### 6 TDFN-EP

| Package Code                            | T633+2         |  |

|-----------------------------------------|----------------|--|

| Outline Number                          | <u>21-0137</u> |  |

| Land Pattern Number                     | <u>90-0058</u> |  |

| Thermal Resistance, Single-Layer Board: |                |  |

| Junction to Ambient ( $\theta_{JA}$ )   | 55°C/W         |  |

| Junction to Case ( $\theta_{JC}$ )      | 9°C/W          |  |

| Thermal Resistance, Four-Layer Board:   |                |  |

| Junction to Ambient ( $\theta_{JA}$ )   | 42°C/W         |  |

| Junction to Case ( $\theta_{JC}$ )      | 9°C/W          |  |

For the latest package outline information and land patterns (footprints), go to <u>www.maximintegrated.com/packages</u>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <u>www.maximintegrated.com/thermal-tutorial</u>.

### **Electrical Characteristics**

(Limits are 100% production tested at  $T_A = +25$ °C and/or  $T_A = +85$ °C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization. Typical values are not guaranteed.)

| PARAMETER                          | SYMBOL           | CONDITIONS                                           | MIN                       | ТҮР                       | MAX  | UNITS |

|------------------------------------|------------------|------------------------------------------------------|---------------------------|---------------------------|------|-------|

| Supply Voltage                     | V <sub>CC</sub>  | ( <u>Note 1</u> )                                    | 2.97                      | 3.3                       | 3.63 | V     |

| Supply Current                     | laa              | Standby                                              |                           |                           | 400  | μA    |

|                                    | ICC              | Communicating/active (Note 2)                        |                           |                           | 10   | mA    |

|                                    |                  | Low configuration                                    | 0.6 x<br>V <sub>CC</sub>  |                           |      |       |

| 1-Wire Input High                  | V <sub>IH1</sub> | Medium configuration                                 | 0.6 x<br>V <sub>CC</sub>  |                           |      | V     |

|                                    |                  | High configuration                                   | 0.85 x<br>V <sub>CC</sub> |                           |      |       |

|                                    |                  | Low configuration ( <i>Note 3</i> , <i>Note 4</i> )  |                           | 0.25 x<br>V <sub>CC</sub> |      |       |

| Low-to-High Switching<br>Threshold | $V_{TH}$         | Medium configuration ( <i>Note 3, Note 4</i> )       |                           | 0.4V x<br>V <sub>CC</sub> |      | v     |

|                                    |                  | High configuration ( <i>Note 3</i> , <i>Note 4</i> ) |                           | 0.75 x<br>V <sub>CC</sub> |      |       |

# **Electrical Characteristics (continued)**

(Limits are 100% production tested at  $T_A = +25^{\circ}$ C and/or  $T_A = +85^{\circ}$ C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization. Typical values are not guaranteed.)

| PARAMETER                                    | SYMBOL            | CONDITIONS                                                  | MIN | TYP                       | MAX                       | UNITS |  |

|----------------------------------------------|-------------------|-------------------------------------------------------------|-----|---------------------------|---------------------------|-------|--|

|                                              |                   | Low configuration                                           |     |                           | 0.15 x<br>V <sub>CC</sub> |       |  |

| 1-Wire Input Low                             | V <sub>IL1</sub>  | Medium configuration                                        |     |                           | 0.3 x<br>V <sub>CC</sub>  | v     |  |

|                                              |                   | High configuration                                          |     |                           | 0.3 x<br>V <sub>CC</sub>  |       |  |

| High-to-Low Switching<br>Threshold           | V <sub>TL</sub>   | ( <u>Note 3, Note 5</u> )                                   |     | 0.65 x<br>V <sub>CC</sub> |                           | V     |  |

| Switching Hysteresis                         | V <sub>HY</sub>   | ( <u>Note 3, Note 6</u> )                                   |     | 0.3                       |                           | V     |  |

|                                              |                   | Ultra-low range                                             | 250 | 50 333 675                |                           |       |  |

| 1-Wire Weak Pullup                           | D                 | Low range                                                   | 375 | 500                       | 750                       | Ω     |  |

| Resistor (Notes 3, 7)                        | R <sub>WPU</sub>  | High range                                                  | 750 | 1000                      | 1400                      |       |  |

|                                              |                   | External high impedance                                     |     | 10M                       |                           |       |  |

| 1-Wire Output Low                            | V <sub>OL1</sub>  | V <sub>CC</sub> = 2.97V, 4mA sink current                   |     |                           | 0.28                      | V     |  |

|                                              |                   | Low configuration (Note 3)                                  |     | 0.25 x<br>V <sub>CC</sub> |                           |       |  |

| Active Pullup on<br>Threshold                | V <sub>IAPO</sub> | Medium configuration ( <i>Note 3</i> )                      |     | 0.4 x<br>V <sub>CC</sub>  |                           | v     |  |

|                                              |                   | High configuration ( <u>Note 3</u> )                        |     | 0.75 x<br>V <sub>CC</sub> |                           |       |  |

| Active Pullup on Time                        |                   | 1-Wire standard speed (default value)                       |     | 2.5                       |                           |       |  |

| (Notes 3, 8)                                 | t <sub>APU</sub>  | 1-Wire overdrive speed (default value)                      | 0.5 |                           | μs                        |       |  |

| Active Pullup<br>Impedance                   | R <sub>APU</sub>  | V <sub>CC</sub> = 2.97V, 10mA load ( <u><i>Note 3</i></u> ) | 50  |                           | Ω                         |       |  |

| IO PIN: 1-Wire TIMING (                      | lote 9            |                                                             | •   |                           |                           |       |  |

| 1-Wire Output Fall Time<br>( <u>Note 3</u> ) | t <sub>F</sub>    | Standard and overdrive                                      |     | Settable                  |                           | μs    |  |

| Reset Low Time                               | t <sub>RSTL</sub> | Standard and overdrive                                      | -5% | Settable                  | +5%                       | μs    |  |

| Reset High Time                              | t <sub>RSTH</sub> | Standard and overdrive (Note 10)                            | -5% | Settable                  | +5%                       | μs    |  |

| Presence-Detect<br>Sample Time               | t <sub>MSP</sub>  | Standard and overdrive                                      | -5% | Settable                  | +5%                       | μs    |  |

| Sampling for Short and Interrupt             | t <sub>MSI</sub>  | Standard and overdrive                                      | -5% | Settable                  | +5%                       | μs    |  |

| Write-One/Read Low<br>Time                   | t <sub>W1L</sub>  | Standard and overdrive                                      | -5% | Settable                  | +5%                       | μs    |  |

| Read Sample Time                             | t <sub>MSR</sub>  | Standard and overdrive                                      | -5% | Settable                  | +5%                       | μs    |  |

| Write-Zero Low Time                          | t <sub>WOL</sub>  | Standard and overdrive                                      | -5% | Settable                  | +5%                       | μs    |  |

| Recovery Time                                | t <sub>REC</sub>  | Standard and overdrive (Note 10)                            | -5% | Settable                  | +5%                       | μs    |  |

| 1-Wire Time Slot                             | t <sub>SLOT</sub> | Standard and overdrive     twoL +<br>tREC                   |     | μs                        |                           |       |  |

# **Electrical Characteristics (continued)**

(Limits are 100% production tested at  $T_A = +25^{\circ}$ C and/or  $T_A = +85^{\circ}$ C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization. Typical values are not guaranteed.)

| PARAMETER                                                                                            | SYMBOL               | CONDITIONS                                                 | MIN                      | TYP                       | MAX                       | UNITS |

|------------------------------------------------------------------------------------------------------|----------------------|------------------------------------------------------------|--------------------------|---------------------------|---------------------------|-------|

| 1-Wire FUNCTIONS                                                                                     |                      | -                                                          |                          |                           |                           |       |

| Operation Time                                                                                       | t <sub>OP</sub>      | ( <u>Note 3</u> )                                          |                          |                           | 400                       | μs    |

| Sequence Time                                                                                        | t <sub>SEQ</sub>     | ( <u>Note 3</u> )                                          |                          |                           | 10                        | μs    |

| EEPROM                                                                                               |                      |                                                            | ·                        |                           |                           |       |

| Read Memory                                                                                          | t <sub>RM</sub>      |                                                            |                          |                           | 50                        | ms    |

| Write Memory                                                                                         | t <sub>WM</sub>      |                                                            |                          |                           | 100                       | ms    |

| Write State                                                                                          | tws                  |                                                            |                          |                           | 15                        | ms    |

| Write/Erase Cycles<br>(Endurance)                                                                    | N <sub>CY</sub>      | T <sub>A</sub> = +85°C ( <u>Note 12</u> )                  | 100K                     |                           |                           |       |

| Data Retention                                                                                       | t <sub>DR</sub>      | T <sub>A</sub> = +85°C ( <u>Note 13</u> , <u>Note 14</u> ) | 10                       |                           |                           | years |

| GPIO PIN                                                                                             |                      |                                                            |                          |                           |                           |       |

| Output Low                                                                                           | GPIO V <sub>OL</sub> | GPIOI <sub>OL</sub> = 4mA ( <u>Note 15</u> )               |                          |                           | 0.4                       | V     |

| Input Low                                                                                            | GPIO V <sub>IL</sub> |                                                            | -0.3                     |                           | 0.2 x<br>V <sub>CC</sub>  | V     |

| Input High                                                                                           | GPIO V <sub>IH</sub> |                                                            | 0.7 x                    |                           | V <sub>CC</sub> +         | V     |

|                                                                                                      |                      |                                                            | V <sub>CC</sub>          |                           | 0.3                       | -     |

| Leakage Current                                                                                      | GPIO IL              |                                                            | -1                       |                           | +1                        | μA    |

| I <sup>2</sup> C SCL AND SDA PINS                                                                    | ( <u>Note 16</u> )   |                                                            |                          |                           |                           | 1     |

| Low-Level Input Voltage                                                                              | V <sub>IL</sub>      |                                                            | -0.3                     |                           | 0.2 ×<br>V <sub>CC</sub>  | V     |

| High-Level Input Voltage                                                                             | V <sub>IH</sub>      |                                                            | 0.7 ×<br>V <sub>CC</sub> |                           | V <sub>CC</sub> +<br>0.3V | V     |

| Hysteresis of Schmitt<br>Trigger Inputs                                                              | V <sub>HYS</sub>     | ( <u>Note 3</u> )                                          |                          | 0.05 ×<br>V <sub>CC</sub> |                           | v     |

| Low-Level Output<br>Voltage at 4mA Sink<br>Current                                                   | V <sub>OL</sub>      | ( <u>Note 15</u> )                                         |                          |                           | 0.4                       | v     |

| Output Fall Time from $V_{IH(MIN)}$ to $V_{IL(MAX)}$ with a Bus Capacitance from 10pF to 400pF       | tOF                  | ( <u>Note 3</u> )                                          |                          | 30                        |                           | ns    |

| Pulse Width of Spikes<br>That Are Suppressed by<br>the Input Filter                                  | t <sub>SP</sub>      | ( <u>Note 3</u> )                                          |                          |                           | 50                        | ns    |

| Input Current with an<br>Input Voltage Between<br>0.1V <sub>CCMAX</sub> and<br>0.9V <sub>CCMAX</sub> | lı                   | ( <u>Note 3, Note 17</u> )                                 | -1                       |                           | +1                        | μA    |

| Input Capacitance                                                                                    | Cl                   | ( <u>Note 3</u> )                                          |                          | 10                        |                           | pF    |

| SCL Clock Frequency                                                                                  | fSCL                 | ( <u>Note 1</u> )                                          | 0                        |                           | 1                         | MHz   |

| Hold Time (Repeated)<br>START Condition                                                              | <sup>t</sup> HD:STA  |                                                            | 0.45                     |                           |                           | μs    |

### **Electrical Characteristics (continued)**

(Limits are 100% production tested at  $T_A = +25^{\circ}$ C and/or  $T_A = +85^{\circ}$ C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization. Typical values are not guaranteed.)

| PARAMETER                                              | SYMBOL              | CONDITIONS                         | MIN  | TYP | MAX  | UNITS |

|--------------------------------------------------------|---------------------|------------------------------------|------|-----|------|-------|

| Low Period of the SCL<br>Clock                         | tLOW                | ( <u>Note 18</u> )                 | 0.65 |     |      | μs    |

| High Period of the SCL<br>Clock                        | <sup>t</sup> HIGH   | ( <u>Note 3</u> )                  | 0.35 |     |      | μs    |

| Setup Time for a<br>Repeated START<br>Condition        | <sup>t</sup> SU:STA | ( <u>Note 3</u> )                  | 0.35 |     |      | μs    |

| Data Hold Time                                         | t <sub>HD:DAT</sub> | (Note 3, Note 18, Note 19)         |      |     | 0.35 | μs    |

| Data Setup Time                                        | <sup>t</sup> SU:DAT | (Note 3, Note 18, Note 20)         | 100  |     |      | ns    |

| Setup Time for STOP<br>Condition                       | <sup>t</sup> su:sto | ( <u>Note 3</u> )                  | 0.35 |     |      | μs    |

| Bus Free Time Between<br>a STOP and START<br>Condition | <sup>t</sup> BUF    | ( <u>Note 3</u> )                  | 0.6  |     |      | μs    |

| Capacitive Load for<br>Each Bus Line                   | C <sub>B</sub>      | ( <u>Note 1, Note 21</u> )         |      |     | 400  | pF    |

| Warmup Time                                            | toscwup             | ( <u>Note 4</u> , <u>Note 22</u> ) |      |     | 1    | ms    |

Note 1: System requirement.

Note 2: Operating current with a 1-Wire write byte sequence followed by continuous write/read of the 1-Wire Block command at 1MHz in overdrive.

- Note 3: Guaranteed by design and/or characterization only. Not production tested.

- **Note 4:** Voltage above which, during a rising edge on IO, a logic 1 is detected.

- **Note 5:** Voltage below which, during a  $t_F$  on IO, a logic 0 is detected.

- Note 6: After V<sub>TH</sub> is crossed during a rising edge on IO for high configuration only, the voltage on IO must drop by at least V<sub>HY</sub> to be detected as logic 0.

- Note 7: Active pullup or resistive pullup and range are configurable.

- **Note 8:** The active pullup does not apply to the rising edge of a presence pulse outside of a 1-Wire reset cycle or during the recovery after a short on the 1-Wire line.

- Note 9: All 1-Wire timing specifications are derived from the same timing circuit.

- Note 10: Up to an additional 10µs of idle high time may occur between a 1-Wire reset cycle and the first time slot, or between each 1-Wire byte during a command sequence.

- Note 11: Current drawn from  $V_{CC}$  during the EEPROM programming interval or SHA-3 computation.

- Note 12: Write-cycle endurance is tested in compliance with JESD47G.

- **Note 13:** Not 100% production tested; guaranteed by reliability monitor sampling.

- Note 14: Data retention is tested in compliance with JESD47G.

- Note 15: The I-V characteristic is linear for voltages less than 1V.

- Note 16: All I<sup>2</sup>C timing values are referred to  $V_{IH(MIN)}$  and  $V_{IL(MAX)}$  levels.

- Note 17: The IO pins of the DS2485 do not obstruct the SDA and SCL lines if V<sub>CC</sub> is switched off.

- Note 18:  $t_{LOW}$  min =  $t_{HD:DAT}$  max + 200ns for rise or fall time +  $t_{SU:DAT}$  min. Values greater than these can be accommodated by extending  $t_{LOW}$  accordingly.

- Note 19: The DS2485 provides a hold time of at least 100ns for the SDA signal (referenced to the V<sub>IH(MIN)</sub> of the SCL signal) to bridge the undefined region of the falling edge of SCL.

- Note 20: The DS2485 can be used in a standard-mode l<sup>2</sup>C-bus system, but the requirement of  $t_{SU:DAT} \ge 250$ ns must then be met. Also, the acknowledge timing must meet this setup time (l<sup>2</sup>C bus specification Rev. 03, 19 June 2007).

- Note 21: C<sub>B</sub> = total capacitance of one bus line in pF. The maximum bus capacitance allowable may vary from this value depending on the actual operating voltage and frequency of the application (I<sup>2</sup>C bus specification Rev. 03, 19 June 2007).

# Advanced 1-Wire Master with Memory

Note 22: I<sup>2</sup>C communication should not take place for the max t<sub>OSCWUP</sub> time following a power-on reset.

# **Pin Configuration**

# **Pin Description**

| PIN | NAME            | FUNCTION                                                                                                                                                                                       |

|-----|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | GPIO            | Open-Drain, General-Purpose Input/Output. Requires external pullup resistor to $V_{CC}$ when used as an output.                                                                                |

| 2   | Ю               | 1-Wire Input/Output Driver. The 1-Wire line can be pulled up by an internal weak pullup ( $R_{WPU}$ ), an external pullup, or have both an external pullup and internal weak pullup.           |

| 3   | GND             | Ground                                                                                                                                                                                         |

| 4   | SCL             | I <sup>2</sup> C Serial Clock Input. Must be connected to $V_{CC}$ through a pullup resistor.                                                                                                  |

| 5   | SDA             | Open-Drain, $I^2C$ Serial Data Input/Output. Must be connected to $V_{CC}$ through a pullup resistor.                                                                                          |

| 6   | V <sub>CC</sub> | Power Supply Input                                                                                                                                                                             |

| _   | EP              | Exposed Pad (TDFN Only). Solder evenly to the board's ground plane for proper operation. Refer to <u>Application Note 3273: Exposed Pads: A Brief Introduction</u> for additional information. |

# Advanced 1-Wire Master with Memory

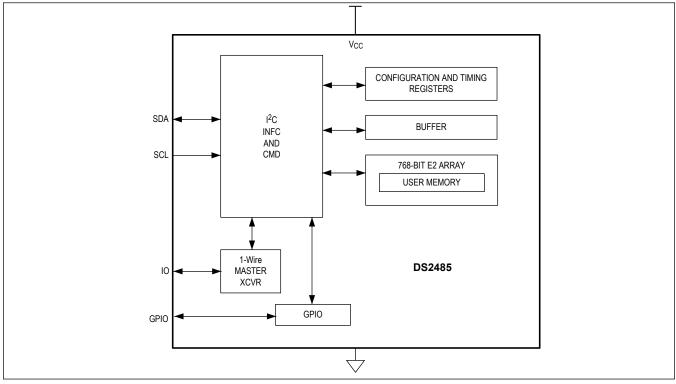

# **Functional Diagrams**

### Simplified Block Diagram

### **Detailed Description**

The DS2485 is a 1-Wire master that performs protocol conversion between the I<sup>2</sup>C master and any attached 1-Wire slaves. For 1-Wire line driving, internal user-adjustable timers relieve the system host processor from generating timecritical 1-Wire waveforms, supporting both standard and overdrive 1-Wire communication speeds. The advanced self-timed 1-Wire master has selectable active or passive 1-Wire pullup. Strong pullup features support 1-Wire power delivery for 1-Wire devices that require this for EEPROMs and cryptographic computations. Once supplied with a command and data, the input/output controller of the DS2485 performs time-critical 1-Wire communication functions such as reset/ presence-detect cycle, read-byte, write-byte, read-block, write-block, single-bit R/W, triplets for ROM Search, and full command sequences for 1-Wire authenticators without requiring interaction with the host processor. The GPIO pin can be independently operated under command control. Additionally, the DS2485 provides three pages of user memory. The DS2485 communicates with a host processor through its I<sup>2</sup>C bus interface in standard mode or in fast mode up to 1MHz. The DS2485 is not compatible with the DS2482/DS2483/DS2484 devices.

#### **Design Resource Overview**

Operation of the DS2485 involves configuring the 1-Wire master and then performing individual 1-Wire commands or grouping them into a series of primitive 1-Wire commands.

#### Memory

The DS2485 has a 0.75Kb EEPROM array of general-purpose, user-programmable memory organized into three pages of 32-bytes with even-numbered addresses. Odd-numbered pages are not available for use and are write protected. Each even-numbered page has optional protection modes.

| PAGE | REGION                                                                                                          | MEMORY TYPE    | DEFAULT PROTECTION | CONFIGURABLE PROTECTION            |  |  |

|------|-----------------------------------------------------------------------------------------------------------------|----------------|--------------------|------------------------------------|--|--|

| 0    | User Page                                                                                                       | EE             |                    |                                    |  |  |

| 1    | Reserved Page                                                                                                   | —              | WP                 |                                    |  |  |

| 2    | User Page                                                                                                       | EE             |                    | WP. NONE                           |  |  |

| 3    | Reserved Page                                                                                                   | —              | WP                 | WF, NONE                           |  |  |

| 4    | User Page                                                                                                       | EE             |                    |                                    |  |  |

| 5    | Reserved Page                                                                                                   | —              | WP                 |                                    |  |  |

|      | ROTECTION MODE<br>ABBREVIATION*                                                                                 |                | DESCRIPT           | ION                                |  |  |

|      | WP                                                                                                              | Write protect. | Write protect.     |                                    |  |  |

|      | NONE No protection on User Page. This locks the protection feature and does not allow any protection to be set. |                |                    | ion feature and does not allow any |  |  |

### Table 1. User Memory Map with Default Protections

\*Protection mode restrictions: Protection for a page can only be set once.

#### Open-Drain GPIO

A dedicated volatile memory region is used to control and/or read the open-drain GPIO pin. Upon power-up, the GPIO pin is high impedance.

#### 1-Wire Master

The 1-Wire master reports data and status from the 1-Wire side to the host processor.

#### **Transaction Sequence**

The protocol for accessing a connected slave device through the 1-Wire master is as follows:

Initialization

- ROM Function command

- Device Function command

- Transaction/data

#### Power-Up 1-Wire Bus

On power-up, the DS2485 1-Wire master defaults with the 1-Wire bus in the "float condition," per <u>Table 37</u>. After powerup, this setting must be changed for correct 1-Wire operation. Set register RPUP/BUF for correct 1-Wire operation. For most applications with only one 1-Wire slave device, the recommendation is to set the RPUP/BUF register to 6h, per <u>Table 34</u>. After setting RPUP/BUF, a 1-Wire reset must be performed with any command that can perform that operation.

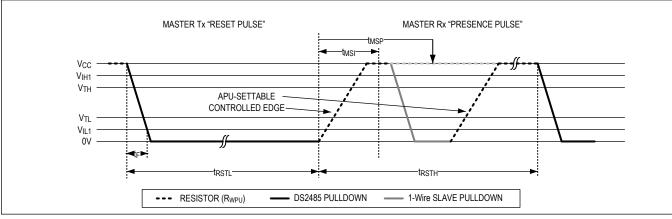

#### Initialization

All transactions on the 1-Wire bus begin with an initialization sequence. The initialization sequence consists of a reset pulse transmitted by the 1-Wire master, followed by a presence pulse(s) transmitted by the slave(s). The presence pulse lets the bus master know that the slave is on the bus and is ready to operate. For more details, see the <u>1-Wire Signaling</u> and <u>Timing</u> section.

#### 1-Wire Signaling and Timing

The 1-Wire protocol consists of four types of signaling on one line: reset sequence with reset pulse and presence pulse, write-zero, write-one, and read-data. Except for the presence pulse, the 1-Wire master initiates all falling edges. The 1-Wire master can communicate at two speeds: standard and overdrive. While in overdrive mode, the fast timing applies to all waveforms.

Figure 1 shows the initialization sequence required to begin any communication. A reset pulse followed by a presence pulse indicates that a slave is ready to receive data, given the correct ROM and device function command.

Figure 1. 1-Wire Reset/Presence-Detect Cycle

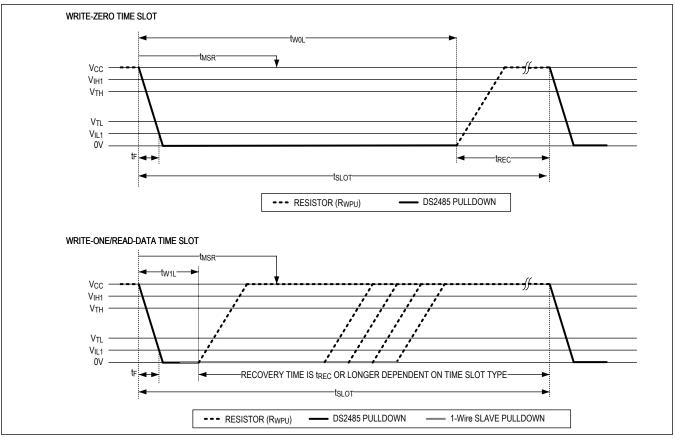

#### **Read/Write Time Slots**

Data communication on the 1-Wire bus takes place in time slots that carry a single bit each. Write time slots transport data from the 1-Wire master to a connected slave. Read time slots transfer data from the slave to the 1-Wire master. Figure 2 illustrates the definitions of the write and read time slots.

All communication begins with the master pulling the data line low. As the voltage on the 1-Wire line falls below the threshold  $V_{TL}$ , the slave starts its internal timing generator that determines when the data line is sampled during a write time slot and how long data is valid during a read time slot.

#### Master-to-Slave

For a write-one time slot, the voltage on the data line must have crossed the  $V_{TH}$  threshold before the write-one low time  $t_{W1LMAX}$  is expired. For a write-zero time slot, the voltage on the data line must stay below the  $V_{TH}$  threshold until

the write-zero low time  $t_{W0LMIN}$  is expired. For the most reliable communication, the voltage on the data line should not exceed  $V_{ILMAX}$  during the entire  $t_{W0L}$  or  $t_{W1L}$  window required by the slave. After the  $V_{TH}$  threshold has been crossed, the DS2485 needs a recovery time  $t_{REC}$  before it is ready for the next time slot.

#### Slave-to-Master

A read-data time slot begins like a write-one time slot. The voltage on the data line must remain below  $V_{TL}$  until the read low time ( $t_{RL}$ ) is expired. During the  $t_{RL}$  window, when responding with a 0, the slave starts pulling the data line low; its internal timing generator determines when this pulldown ends and the voltage starts rising again. When responding with a 1, the slave does not hold the data line low at all, and the voltage starts rising as soon as  $t_{RL}$  is over. Note that the slave  $t_{RL}$  during a logic 1 is adequately an approximation of the 1-Wire master  $t_{W1L}$  setting.

The slave  $t_{RL}$  plus the bus rise time on the near end and the internal timing generator of the slave on the far end define the 1-Wire master sampling window in which the 1-Wire master performs a read from the data line. After reading from the data line, the 1-Wire master waits until  $t_{SLOT}$  is expired. This guarantees sufficient recovery time ( $t_{REC}$ ) for the slave to get ready for the next time slot. Note that  $t_{REC}$ ; specified herein applies only to a single slave attached to a 1-Wire line. For multidevice configurations,  $t_{REC}$  must be extended to accommodate the additional 1-Wire device input capacitance.

Figure 2. Read/Write Timing Diagrams

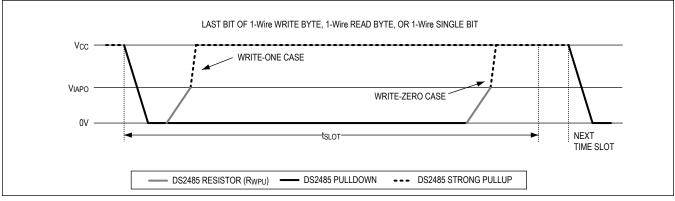

#### Strong Pullup

The strong pullup function can be activated prior to a 1-Wire Write Byte, 1-Wire Read Byte, 1-Wire Single Bit, 1-Wire Block, or 1-Wire Write Block command. Strong pullup is commonly used with 1-Wire EEPROM devices when copying buffer data to the main memory. The respective device data sheets specify the location in the communications protocol after which the strong pullup should be applied. The strong pullup can be enabled immediately prior to issuing the

# Advanced 1-Wire Master with Memory

command that puts the 1-Wire device into the state where it needs the extra power for primitive 1-Wire commands or as an integral part of advanced commands. The strong pullup uses the same internal pullup transistor as the active pullup feature. See the  $R_{APU}$  parameter in the *Electrical Characteristics* table to determine whether the voltage drop is low enough to maintain the required 1-Wire voltage at a given load current and supply voltage. If the strong pullup is enabled, the DS2485 treats the rising edge of the time slot in which the strong pullup starts as if the active pullup was activated. However, in contrast to the active pullup, the strong pullup (i.e., the internal pullup transistor) remains conducting, as shown in *Figure 3*, until the DS2485 receives a command that generates 1-Wire communication (the typical case), or until the strong pullup is disabled or the 1-Wire master is reset. When the strong pullup ends, it is automatically disabled. Using the strong pullup feature does not change the active pullup settings.

Figure 3. Strong Pullup Timing

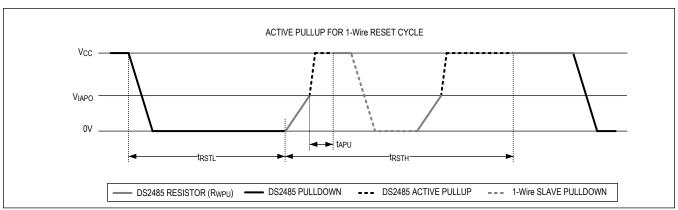

#### Active Pullup (APU)

The APU is a function that accelerates the rise time during a 1-Wire reset cycle, write time slot, or read time slot. The 1-Wire master triggering mechanism is always ready after the initial low time of a 1-Wire reset cycle or time slot completes. This rise-time acceleration is accomplished by an active pullup impedance ( $R_{APU}$ ) that begins driving once the active pullup on threshold ( $V_{IAPO}$ ) is crossed from low to high. APU does not apply to the rising edge of a recovery from a short on the line, a power-up presence pulse of a slave, or any other event outside of a 1-Wire reset cycle or a time slot. Enabling APU is generally recommended for best 1-Wire performance.

#### Active Pullup for 1-Wire Reset Cycle

<u>Figure 4</u> illustrates an active pullup for a 1-Wire reset cycle. A 1-Wire reset cycle begins by driving the line low for a  $t_{RSTL}$  period. When the  $t_{RSTL}$  expires, the APU triggering mechanism is on and triggers when the  $V_{IAPO}$  level is crossed from low to high. APU then remains on for a duration of  $t_{APU}$ . After the completion of  $t_{APU}$ , the APU trigger mechanism is reset to be on again and triggers when the  $V_{IAPO}$  level is crossed from low to high upon a presence pulse completing. APU then remains on until the duration of  $t_{RSTH}$  expires.

Figure 4. Active Pullup for a 1-Wire Reset Cycle

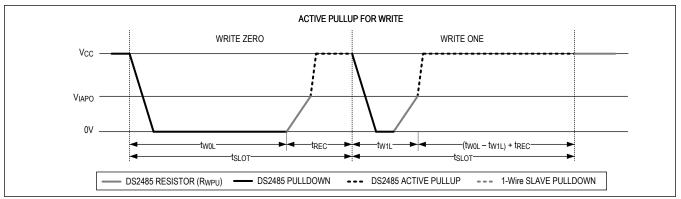

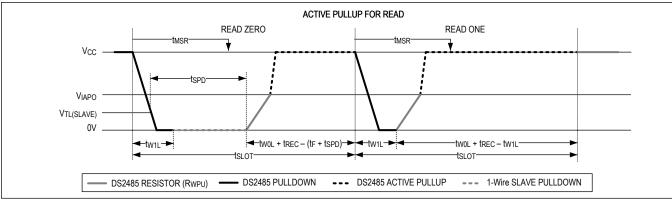

#### Active Pullup for Read/Write Time Slots

<u>Figure 5</u> illustrates an active pullup for a 1-Wire write-zero or write-one time slot. A write-zero time slot begins by the 1-Wire master driving the line low for a  $t_{W0L}$  period. When the  $t_{W0L}$  expires, the APU triggering mechanism is on and triggers when the  $V_{IAPO}$  level is crossed from low to high. APU then remains on until  $t_{REC}$  expires. A write-one time slot begins by the 1-Wire master driving the line low for a  $t_{W1L}$  period. When the  $t_{W1L}$  expires, the APU triggering mechanism is on and triggers when the  $V_{IAPO}$  level is crossed from low to high. Unlike the write-zero time slot, the write-one time slot has APU for a much longer recovery duration defined by ( $t_{W0L} - t_{W1L}$ ) +  $t_{REC}$ .

Figure 5. Active Pullup for 1-Wire Write Time Slot

<u>Figure 6</u> illustrates an active pullup for 1-Wire read time slots. On a 1-Wire read-zero time slot, the master pulls the line low. The slave detects the low, and takes over driving the line. At that point, both the master and slave are driving the line low until  $t_{W1L}$  expires. After  $t_{W1L}$ , the master turns on the normal pullup ( $R_{WPU}$ ), and enables the APU triggering mechanism. The master samples the read data at  $t_{MSR}$ . After the slave response time ( $t_{SPD}$ ) expires, the slave releases the line. The APU triggers when the  $V_{IAPO}$  level is crossed from low to high. The APU remains on until the end of the slot as defined in Figure 6. On a 1-Wire read-one time slot, the master turns on the normal pullup and enables the APU triggering mechanism. The APU triggers when the  $t_{W1L}$  expires, the master turns on the normal pullup and enables the APU triggering mechanism. The APU triggers when the  $t_{W1L}$  expires, the master turns on the normal pullup and enables the APU triggering mechanism. The APU triggers when the  $t_{W1L}$  expires, the master turns on the normal pullup and enables the APU triggering mechanism. The APU triggers when the  $V_{IAPO}$  level is crossed from low to high. The APU remains on until the end of the slot as defined by ( $t_{W0L} - t_{W1L}$ ) +  $t_{REC}$ . The read-one recovery time is longer than the read-zero case.

Figure 6. Active Pullup for 1-Wire Read Time Slot

### l<sup>2</sup>C

#### **General Characteristics**

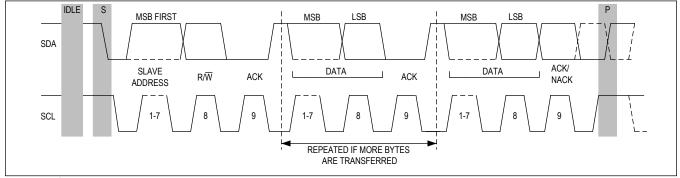

The I<sup>2</sup>C bus uses a data line (SDA) plus a clock signal (SCL) for communication. Both SDA and SCL are bidirectional lines, connected to a positive supply voltage through a pullup resistor. When there is no communication, both lines are high. The output stages of devices connected to the bus must have an open drain or open collector to perform the wired-AND function. Data on the I<sup>2</sup>C bus can be transferred at rates of up to 100kbps in standard mode and up to 400kbps in fast mode. The DS2485 works in both modes or up to a clock rate of 1MHz. A device that sends data on the bus is defined as a transmitter, and a device receiving data is defined as a receiver. The device that controls the communication is called a master. The devices that are controlled by the master are slaves. To be individually accessed, each device must have a slave address that does not conflict with other devices on the bus. Data transfers can be initiated only when the bus is not busy. The master generates the serial clock (SCL), controls the bus access, generates the START and STOP conditions, and determines the number of data bytes transferred between START and STOP (Figure 7). Data is transferred in bytes, with the most significant bit being transmitted first. After each byte follows an acknowledge bit to allow synchronization between master and slave.

Figure 7. I<sup>2</sup>C Protocol Overview

#### Slave Address

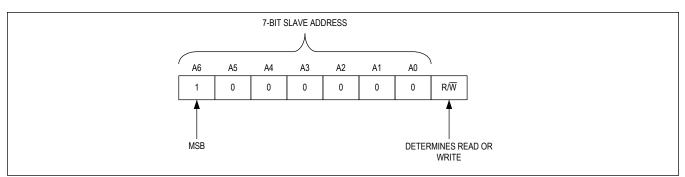

The slave address to which the DS2485 responds is shown by default in <u>Figure 8</u>. The slave address is part of the slave address/control byte. The last bit of the slave address/control byte (R/W) defines the data direction. When set to 0, subsequent data flows from the master to the slave (write access); when set to 1, data flows from the slave to the master (read access). The default address can be changed with the Set I2C Address command.

Figure 8. DS2485 I<sup>2</sup>C Slave Address

#### I<sup>2</sup>C Definitions

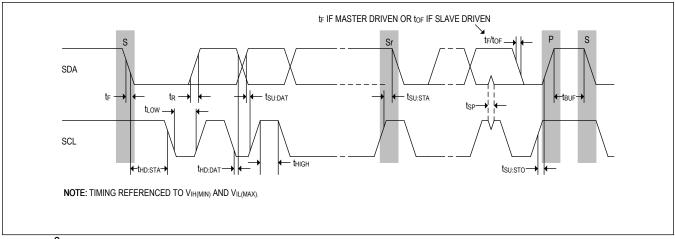

The following terminology is commonly used to describe  $I^2C$  data transfers. The timing references are defined in Figure 9.

#### **Bus Idle or Not Busy**

Both SDA and SCL are inactive and in their logic-high states.

#### **START Condition**

To initiate communication with a slave, the master must generate a START condition. A START condition is defined as a change in state of SDA from high to low while SCL remains high.

#### **STOP Condition**

To end communication with a slave, the master must generate a STOP condition. A STOP condition is defined as a change in state of SDA from low to high while SCL remains high.

#### **Repeated START Condition**

Repeated STARTs are commonly used for read accesses after having specified a memory address to read from in a preceding write access. The master can use a repeated START condition at the end of a data transfer to immediately initiate a new data transfer following the current one. A repeated START condition is generated the same way as a normal START condition, but without leaving the bus idle after a STOP condition.

#### **Data Valid**

With the exception of the START and STOP conditions, transitions of SDA can occur only during the low state of SCL. The data on SDA must remain valid and unchanged during the entire high pulse of SCL plus the required setup and hold time ( $t_{HD:DAT}$  after the falling edge of SCL and  $t_{SU:DAT}$  before the rising edge of SCL; see Figure 9). There is one clock pulse per bit of data. Data is shifted into the receiving device during the rising edge of the SCL pulse.

When finished with writing, the master must release the SDA line for a sufficient amount of setup time (minimum  $t_{SU:DAT}$ , +  $t_R$  in Figure 9) before the next rising edge of SCL to start reading. The slave shifts out each data bit on SDA at the falling edge of the previous SCL pulse, and the data bit is valid at the rising edge of the current SCL pulse. The master generates all SCL clock pulses, including those needed to read from a slave.

Figure 9. I<sup>2</sup>C Timing Diagram

### Commands

#### **Device Function Commands**

The DS2485 has 15 commands with four memory commands, four configuration commands, seven 1-Wire master commands, and a CRC16 command. <u>Table 2</u> lists these commands.

| Table 2. | Device | Function | Commands |

|----------|--------|----------|----------|

|----------|--------|----------|----------|

| COMMAND                  | CODE | DESCRIPTION                                                                   | TYPE          |

|--------------------------|------|-------------------------------------------------------------------------------|---------------|

| Write Memory             | 96h  | Write memory page                                                             | Memory        |

| Read Memory              | 44h  | Read memory page                                                              | Memory        |

| Set Page Protection      | C3h  | Set page protection of a memory page                                          | Memory        |

| Read Status              | AAh  | Read the protection for a memory page                                         | Memory        |

| Set I2C Address          | 75h  | Set the I2C address                                                           | Configuration |

| Read 1-Wire Port Config  | 52h  | Read all or one port configuration registers                                  | Configuration |

| Write 1-Wire Port Config | 99h  | Write to a 1-Wire port configuration register                                 | Configuration |

| Master Reset             | 62h  | Reset the 1-Wire master block and return to defaults                          | Configuration |

| 1-Wire Script*           | 88h  | Execute one or more 1-Wire primitive commands                                 | 1-Wire        |

| 1-Wire Block             | ABh  | Read and write 1-Wire data block (optional 1-Wire reset first and SPU at end) | 1-Wire        |

| 1-Wire Read Block        | 50h  | Read a block of 1-Wire data                                                   | 1-Wire        |

| 1-Wire Write Block       | 68h  | Write 1-Wire block of data (optional 1-Wire reset first and SPU at end)       | 1-Wire        |

| 1-Wire Search            | 11h  | Perform 1-Wire search algorithm                                               | 1-Wire        |

| Full Command Sequence    | 57h  | Performs a complete 1-Wire authenticator communication sequence               | 1-Wire        |

| Compute CRC16            | CCh  | Compute CRC16 over provided data                                              | CRC16         |

\*See <u>Table 42</u> for the complete list of 1-Wire primitives including reset, read bit, write bit, read byte, and write byte, along with GPIO, 1-Wire speed, and pullup commands.

#### I<sup>2</sup>C Communication Command Sequence

The generic command sequence is shown in <u>Table 3</u>. The write sequence begins with the master sending an I<sup>2</sup>C Start and write I<sup>2</sup>C address, then a command code from the listings in <u>Table 5</u> is issued. Optionally, if the command requires it, a command parameter(s) and write data byte(s) might be sent followed by an I<sup>2</sup>C Stop. After the sequence writes, a delay might also be needed to allow the command process to complete.

# Advanced 1-Wire Master with Memory

Next, the read sequence begins by sending an  $I^2C$  Start and read  $I^2C$  address. The first byte read after the address is the length to set the number of data bytes to read. When receiving the read information, a Result Byte is provided that expresses if the sequence was successful (with an AAh) or if an error has occurred (with an unlike value). After the Result Byte, all the data can be read and should be followed by an  $I^2C$  Stop.

# Table 3. Generic I<sup>2</sup>C Command Sequence

| <start></start>                                       |

|-------------------------------------------------------|

| Tx: Master sends I <sup>2</sup> C address (WRITE)     |

| Tx: Master sends Command Command                      |

| Tx: Master sends Write Length                         |

| Tx: Master sends Command Parameter(s)                 |

| Tx: Master sends Data Byte(s)                         |

| <stop></stop>                                         |

| <delay allow="" command="" complete="" to=""></delay> |

| <start></start>                                       |

| Tx: Master sends I <sup>2</sup> C address (READ)      |

| Rx: Master receives Rx Read Length                    |

| Rx: Master receives Result Byte                       |

| Rx: Master receives Data Byte(s)                      |

| <stop></stop>                                         |

### **Table 4. Communication Legend**

| Tx <start> <stop></stop></start> | Gray with white text denotes transmit, I <sup>2</sup> C start and stop   |

|----------------------------------|--------------------------------------------------------------------------|

| <delay></delay>                  | Orange with white text denotes delay waiting for completion of operation |

| Rx                               | Green denotes receiving data from DS2485                                 |

#### Write Memory (96h)

The Write Memory command is used to write a 32-byte page. The page can be any even-numbered user memory page (0 to 5). The page must not have WP protection (all odd-numbered pages have WP protection). If the page is protected, it fails with a 55h result byte. On success, the result byte is AAh. The 32-byte page data is provided after the parameter byte during the command sequence. All writes must be 32 bytes.

### Table 5. Write Memory

| Write Memory         |                                                                                                                           |

|----------------------|---------------------------------------------------------------------------------------------------------------------------|

| Command Code         | 96h                                                                                                                       |

| Parameter Byte(s)    | See Table 6                                                                                                               |

| Usage                | A write is done by page number and always has a write size of 32 bytes.                                                   |

| Command Restrictions | Page must not have WP protection.                                                                                         |

| Device Operation     | Verify that the destination page does not have WP protection set.<br>Write the data.<br>Set the result byte.              |

| Command Duration     | t <sub>WM</sub>                                                                                                           |

| Result Byte          | AAh = Success<br>55h = The command failed because destination page is protected (WP).<br>77h = Invalid input or parameter |

### **Table 6. Write Memory Parameter Byte**

| BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| 0     | 0     | 0     | 0     | 0     |       | PAGE# |       |

Bits 2:0: Memory Page Number (PAGE#). Page to write, 0 to 5 (odd values reference protected pages).

### Table 7. Write Memory Command Communication Sequence

| <start></start>                 |

|---------------------------------|

| Tx: I2C address (WRITE)         |

| Tx: Write Memory Command (96h)  |

| Tx: Write Length Byte (33)      |

| Tx: Parameter                   |

| Tx: Data to transmit (32 bytes) |

| <stop></stop>                   |

| <delay t<sub="">WM&gt;</delay>  |

| <start></start>                 |

| Tx: I2C address (READ)          |

| Rx: Length Byte (1)             |

| Rx: Result Byte                 |

| <stop></stop>                   |

# Advanced 1-Wire Master with Memory

#### Read Memory (44h)

The Read Memory command is used to read a 32-byte page. The page can be any user memory page. All reads are the full 32 bytes. On success, the result byte is AAh. If an invalid page number is specified, 32 bytes of FFh are returned with a result byte of 77h. Odd-numbered pages return variable data with a result byte of AAh.

### **Table 8. Read Memory**

| Read Memory          |                                                                         |  |  |  |

|----------------------|-------------------------------------------------------------------------|--|--|--|

| Command Code         | 44h                                                                     |  |  |  |

| Parameter Byte(s)    | Page number to read.                                                    |  |  |  |

| Usage                | Read a page of memory. This function can also read the special purpose. |  |  |  |

| Command Restrictions | This command is applicable to user memory pages.                        |  |  |  |

| Device Operation     | Read the data.                                                          |  |  |  |

| Command Duration     | t <sub>RM</sub>                                                         |  |  |  |

| Result Byte          | AAh = Success<br>77h = Invalid input or parameter                       |  |  |  |

### **Table 9. Read Memory Parameter Byte**

|       |       | -     | _     |       |       |       |       |

|-------|-------|-------|-------|-------|-------|-------|-------|

| BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

| 0     | 0     | 0     | 0     | 0     |       | PAGE# |       |

Bits 2:0: Memory Page Number (PAGE#). These bits select the page number to be read. Acceptable values are User Page (Page 0 through Page 5).

### Table 10. Read Memory Command Communication Sequence

| <start></start>                |

|--------------------------------|

| Tx: I2C address (WRITE)        |

| Tx: Read Memory Command (44h)  |

| Tx: Write Length Byte (1)      |

| Tx: Parameter (page)           |

| <stop></stop>                  |

| <delay t<sub="">RM&gt;</delay> |

| <start></start>                |

| Tx: I2C address (READ)         |

| Rx: Length Byte (33)           |

| Rx: Result Byte                |

| Rx: Data (32 bytes)            |

| <stop></stop>                  |

# Advanced 1-Wire Master with Memory

#### **Read Status (AAh)**

Read the status of the protection settings of each of the six user pages, manufacturer ID (MANID), or device version.

### **Table 11. Read Status Command**

| Read Status             |                                                                                                                                       |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| Command Code            | AAh                                                                                                                                   |

| Parameter Byte(s)       | See Table 12.                                                                                                                         |

| Usage                   | Read the page protection information for all pages Page 0 to Page 5 (6 bytes), MANID (2 bytes, MSB 1st), or device version (2 bytes). |

| Command<br>Restrictions | None.                                                                                                                                 |

| Device Operation        | Read parameters.<br>Read the page protection setting for all pages, MANID, or device version.                                         |

| Command<br>Duration     | t <sub>RM</sub>                                                                                                                       |

| Result Byte             | AAh = Success<br>77h = Invalid parameter                                                                                              |

#### **Table 12. Read Status Parameter Byte**

| BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1  | BIT 0  |

|-------|-------|-------|-------|-------|-------|--------|--------|

| 0     | 0     | 0     | 0     | 0     | 0     | OUTPUT | SELECT |

**Bit 1:0: Output selection (OUTPUT\_SELECT).** (00b) return protection bytes of pages 0 to 5, 6 bytes; (01b) return MANID, 2 bytes; (10b) return device version, 2 bytes

### **Table 13. Read Status Command Communication Sequence**

| <start></start>                                                                                     |

|-----------------------------------------------------------------------------------------------------|

| Tx: I2C address (WRITE)                                                                             |

| Tx: Read Status Command (AAh)                                                                       |

| Tx: Write Length Byte (1)                                                                           |

| Tx: Read Status parameter                                                                           |

| <stop></stop>                                                                                       |

| <delay t<sub="">RM&gt;</delay>                                                                      |

| <start></start>                                                                                     |

| Tx: I2C address (READ)                                                                              |

| Rx: Length Byte (7 or 3)                                                                            |

| Rx: Result Byte                                                                                     |

| Rx: Result data [Protection Bytes (6 bytes), MANID (2 bytes, MSB 1st), or device version (2 bytes)] |

| <stop></stop>                                                                                       |

### Table 14. Read Status Page Protection Result for Each Page

| BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| 0     | 0     | NONE  | 0     | 0     | 0     | WP    | 0     |

Bit 1: Write Protection (WP). (1b) permanently sets write protection; (0b) no write protection

Bit 5: None Protection (NONE). (1b) permanently sets no protection on page allowed and locks out any future attempts to add protection.

### Set I2C Address (75h)

This command sets the I2C address. By default, the I2C address used is displayed in Figure 3. This command changes this default in a write-once event.

### Table 15. Set I2C Address Command

| Set I2C Address      |                                                                                     |

|----------------------|-------------------------------------------------------------------------------------|

| Command Code         | 75h                                                                                 |

| Parameter Byte(s)    | New I2C address                                                                     |

| Usage                | Set the default I2C address.                                                        |

| Command Restrictions | Command can only be performed once.                                                 |

| Device Operation     | Verify the I2C address has not been written.<br>Write the default I2C address.      |

| Command Duration     | tws                                                                                 |

| Result Byte          | AAh = Success<br>55h = Command failed because the I2C address has already been set. |

### Table 16. New I2C Address Parameter

| BIT 7 | BIT 6    | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

|-------|----------|-------|-------|-------|-------|-------|-------|

|       | I2C_ADDR |       |       |       |       |       |       |

Bits 7:1: I2C Address (I2C\_ADDR). I2C address parameter.

# Table 17. Set I2C Address Command Communication Sequence

| <start></start>                   |

|-----------------------------------|

| Tx: I2C address (WRITE)           |

| Tx: Set I2C Address Command (75h) |

| Tx: Write Length Byte (1)         |

| Tx: New I2C Address               |

| <stop></stop>                     |

| <delay t<sub="">WS&gt;</delay>    |

| <start></start>                   |

| Tx: I2C address (READ)            |

| Rx: Length Byte (1)               |

| Rx: Result Byte                   |

| <stop></stop>                     |

#### Set Page Protection (C3h)

The Set Page Protection command sets the protection state of a single memory page. This is a one-time operation for each protection area. Attempting to set the protection of a page that is already protected (including all odd-numbered pages) results in an error 55h result byte. Attempting to set a protection combination on a protection area that is not valid results in a 77h error code. AAh is the result byte for a successful operation.

### **Table 18. Set Page Protection Command**

| Set Page Pro            | otection                                                                                                                                                                                                               |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Command<br>Code         | C3h                                                                                                                                                                                                                    |

| Parameter<br>Byte(s)    | Two parameters. Byte 1: page to set protection. Byte 2: protection options.                                                                                                                                            |

| Usage                   | Set protection. This is a one-time write of the page protection for each protection area. There are six protection areas: Page 0 to Page 5. All protection modes for the area needed must be set in one function call. |

| Command<br>Restrictions | This command is applicable to pages that have not yet had protection set.                                                                                                                                              |

| Device<br>Operation     | Verify that the destination page does not already have protection set.<br>Verify that the protection requested is valid for the page.<br>Write the protection.                                                         |

| Command<br>Duration     | t <sub>WS</sub>                                                                                                                                                                                                        |

| Result Byte             | AAh = Success<br>77h = Invalid parameter<br>55h = Command failed because the protection for the page has already been set.                                                                                             |

### Table 19. Set Page Protection Parameter (Byte 1)

|       |       |       | •     |       |       |       |       |

|-------|-------|-------|-------|-------|-------|-------|-------|

| BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

| 0     | 0     | 0     | 0     | 0     | PAGE# |       |       |

Bits 3:0: Memory Page Number (PAGE#). These bits select the page number to be protected. Acceptable values are from Page 0 to Page 5, but odd-numbered pages are already protected.

### Table 20. Set Page Protection Parameter (Byte 2)

| ſ | BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

|---|-------|-------|-------|-------|-------|-------|-------|-------|

|   | 0     | 0     | NONE  | 0     | 0     | 0     | WP    | 0     |

Bit 1: Write Protection (WP). (1b) permanently sets write protection; (0b) no write protection

Bit 5: None Protection (NONE). (1b) permanently sets no protection on page allowed and locks out any future attempts to add protection.

# Table 21. Set Page Protection Command Communication Sequence

| <start></start>                       |

|---------------------------------------|

| Tx: I2C address (WRITE)               |

| Tx: Set Page Protection Command (C3h) |

| Tx: Write Length Byte (2)             |

| Tx: Parameter (page)                  |

| Tx: Parameter (protection)            |

| <stop></stop>                         |

| <delay t<sub="">WS&gt;</delay>        |

| <start></start>                       |

| Tx: I2C address (READ)                |

| Rx: Length Byte (1)                   |

| Rx: Result Byte                       |

| <stop></stop>                         |

#### Read 1-Wire Port Configuration (52h)

Read one or all of the 1-Wire port configuration settings.

### Table 22. Read 1-Wire Port Configuration Command

| Read 1-Wire Port Configuration |                                                         |

|--------------------------------|---------------------------------------------------------|

| Command Code                   | 52h                                                     |

| Parameter Byte(s)              | Register to read.                                       |

| Usage                          | Read one or all configuration registers.                |

| Command Restrictions           | None.                                                   |

| Device Operation               | Read configuration register(s).<br>Set the result byte. |

| Command Duration               | top                                                     |

| Result Byte                    | AAh = Success                                           |

### **Table 23. 1-Wire Port Configuration Register Parameter**

| BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| REG   |       |       |       |       |       |       |       |

**Bits 7:0: Register (REG).** Register number 0-13h; any value > 13h results in all registers read. If the value is 0-13h, then select the desired register from <u>Table 24</u>. The returned value is in the same format as the 1-Wire Write Port Config "1-Wire Master New Configuration Value."

### Table 24. Port Configuration Registers

| REGISTER # | CONFIGURATION REGISTER            | DEFAULT |

|------------|-----------------------------------|---------|

| 0h         | Master Configuration              | 0000h   |

| 1h         | Standard Speed t <sub>RSTL</sub>  | 0006h   |

| 2h         | Standard Speed t <sub>MSI</sub>   | 0006h   |

| 3h         | Standard Speed t <sub>MSP</sub>   | 0006h   |

| 4h         | Standard Speed t <sub>RSTH</sub>  | 0006h   |

| 5h         | Standard Speed t <sub>W0L</sub>   | 0006h   |

| 6h         | Standard Speed t <sub>W1L</sub>   | 0006h   |

| 7h         | Standard Speed t <sub>MSR</sub>   | 0006h   |

| 8h         | Standard Speed t <sub>REC</sub>   | 0006h   |

| 9h         | Overdrive Speed t <sub>RSTL</sub> | 0006h   |

| Ah         | Overdrive Speed t <sub>MSI</sub>  | 0006h   |

| Bh         | Overdrive Speed t <sub>MSP</sub>  | 0006h   |

| Ch         | Overdrive Speed t <sub>RSTH</sub> | 0006h   |

| Dh         | Overdrive Speed t <sub>W0L</sub>  | 0006h   |

| Eh         | Overdrive Speed t <sub>W1L</sub>  | 0006h   |

| Fh         | Overdrive Speed t <sub>MSR</sub>  | 0006h   |

| 10h        | Overdrive Speed t <sub>REC</sub>  | 0006h   |

| 11h        | RPUP/BUF                          | 803Ch   |

| 12h        | PDSLEW                            | 0006h   |

| 13h        | Reserved                          | 5828h   |

# Advanced 1-Wire Master with Memory

# Table 25. Read 1-Wire Port Configuration Command Communication Sequence

| <start></start>                                  |

|--------------------------------------------------|

| Tx: I2C address (WRITE)                          |

| Tx: Read 1-Wire Port Configuration Command (52h) |

| Tx: Write Length Byte (1)                        |

| Tx: Parameter                                    |

| <stop></stop>                                    |

| <delay t<sub="">OP&gt;</delay>                   |

| <start></start>                                  |

| Tx: I2C address (READ)                           |

| Rx: Read Length Byte (3) or (41)                 |

| Rx: Result Byte                                  |

| Rx: Register data (2 or 40 bytes)                |

| <stop></stop>                                    |

### Write 1-Wire Port Configuration (99h)

Write a 1-Wire port configuration register to change 1-Wire timing.

### Table 26. Write 1-Wire Port Configuration Command

| Write 1-Wire            | Port Configuration                                                                                                                                                                                                     |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Command<br>Code         | 99h                                                                                                                                                                                                                    |

| Parameter<br>Byte(s)    | Parameter indicating which register to set (1 byte) and the new value (2 byte, LSB first).                                                                                                                             |

| Usage                   | Write a 1-Wire configuration register.                                                                                                                                                                                 |

| Command<br>Restrictions | If writing "custom timing" for 1-Wire timing, values shorter than the shortest predefined timings ( <u>Table 32</u> and <u>Table</u> <u>33</u> ) might not work as expected and can require adjusting RPUP and PDSLEW. |

| Device<br>Operation     | Verify the register.<br>Write the register.<br>Set the result byte.                                                                                                                                                    |

| Command<br>Duration     | t <sub>OP</sub>                                                                                                                                                                                                        |

| Result Byte             | AAh = Success<br>77h = Invalid parameter                                                                                                                                                                               |

### Table 27. 1-Wire Port Configuration Register Parameter

| BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| 0     | 0     | 0     |       |       | REG#  |       |       |

Bits 5:0: Resister (REG#). Register number 0-13h. Select the desired register from Table 24.

# Advanced 1-Wire Master with Memory

| REGISTER # | CONFIGURATION REGISTER            |

|------------|-----------------------------------|

| Oh         | Master Configuration              |

| 1h         | Standard Speed t <sub>RSTL</sub>  |

| 2h         | Standard Speed t <sub>MSI</sub>   |

| 3h         | Standard Speed t <sub>MSP</sub>   |

| 4h         | Standard Speed t <sub>RSTH</sub>  |

| 5h         | Standard Speed t <sub>W0L</sub>   |

| 6h         | Standard Speed t <sub>W1L</sub>   |

| 7h         | Standard Speed t <sub>MSR</sub>   |

| 8h         | Standard Speed t <sub>REC</sub>   |

| 9h         | Overdrive Speed t <sub>RSTL</sub> |

| Ah         | Overdrive Speed t <sub>MSI</sub>  |

| Bh         | Overdrive Speed t <sub>MSP</sub>  |

| Ch         | Overdrive Speed t <sub>RSTH</sub> |

| Dh         | Overdrive Speed t <sub>W0L</sub>  |

| Eh         | Overdrive Speed t <sub>W1L</sub>  |

| Fh         | Overdrive Speed t <sub>MSR</sub>  |

| 10h        | Overdrive Speed t <sub>REC</sub>  |

| 11h        | RPUP/BUF                          |

| 12h        | PDSLEW                            |

| 13h        | *Reserved                         |

### Table 28. Port Configuration Registers

\*Reserved must not be written to.

### Table 29. 1-Wire Master Configuration Bit Assignment (Register 0)

| BIT 15 | BIT 14 | BIT 13 | BIT 12 | BIT 11 | BIT 10 | BIT 9 | BIT 8 |

|--------|--------|--------|--------|--------|--------|-------|-------|

| 1WS    | PDN    | SPU    | APU    | X      | X      | X     | Х     |

|        |        |        |        |        |        |       |       |

| BIT 7  | BIT 6  | BIT 5  | BIT 4  | BIT 3  | BIT 2  | BIT 1 | BIT 0 |

| X      | Х      | Х      | Х      | Х      | Х      | Х     | Х     |

**Bit 12: Active Pullup (APU).** The APU bit controls whether an active pullup (low-impedance transistor) or a passive pullup (RWPU resistor) is used to drive a 1-Wire line from low to high. When APU = 0, active pullup is disabled (resistor mode). Enabling active pullup is generally recommended for best 1-Wire performance. The active pullup does not apply to the rising edge of a recovery after a short on the 1 Wire line. (Default 0)

**Bit 13: Strong Pullup (SPU).** The SPU bit, when set to 1, is used to activate the strong pullup function prior to a 1-Wire Write Byte, 1-Wire Read Byte, or 1-Wire Write Bit, 1-Wire Read Bit command. When 0, the strong pullup function is disabled. (Default 0)

**Bit 14: Power-Down (PDN).** The PDN bit is used to remove power from the 1-Wire port, e.g., to force a 1-Wire slave to perform a power-on reset. The default state of PDN is 0, enabling normal operation. When PDN is changed to 1, no 1-Wire communication is possible. To end the 1-Wire power-down state, the PDN bit must be changed to 0. (Default 0)

**Bit 15: 1-Wire Speed (1WS).** The 1WS bit determines the timing of any 1-Wire communication generated by the master. Writing to the 1-Wire Master Configuration register with the 1WS bit as 0 sets the speed to standard speed (default). 1WS = 1 sets the speed to overdrive. (Default 0)

# Advanced 1-Wire Master with Memory

#### BIT 14 **BIT 12** BIT 11 BIT 9 BIT 8 **BIT 15 BIT 13 BIT 10** CUSTOM Х VALUE[13:8] BIT 6 BIT 1 BIT 7 BIT 5 BIT 4 BIT 3 BIT 2 BIT 0

VALUE[7:0]

### Table 30. 1-Wire Master New Configuration Value Bit Assignment (Registers 1 to 18)

Bits 13:0: Value Assignment (VALUE). Predefined register value 0-Fh or custom timing value.

Warning: When using custom timing values, 1-Wire communication failure can occur if the value chosen is outside the specification of the 1-Wire slave.