## Zero-Drift, 65V High-Side Current Sense Amplifier

## **Features**

- · Single Amplifier: MCP6C02

- · Bidirectional or Unidirectional

- Input (Common-mode) Voltages:

- +3.0V to +65V, specified

- +2.8V to +68V, operating

- -0.3V to +70V, survival

- · Power Supply:

- 2.0V to 5.5V

- Single or Dual (Split) Supplies

- · High DC Precision

- V<sub>OS</sub>: ±1.65 μV (typical)

- CMRR: 154 dB (typical)

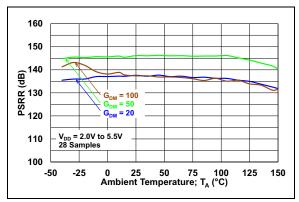

- PSRR: 138 dB (typical)

- Gain Error: ±0.1% (typical)

- Preset Gains: 20, 50 and 100 V/V

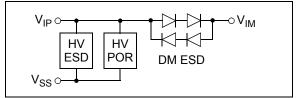

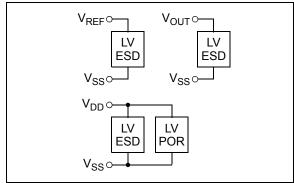

- · POR Protection

- HV POR for  $V_{IP} V_{SS}$

- LV POR for V<sub>DD</sub> V<sub>SS</sub>

- · Bandwidth: 500 kHz (typical)

- Supply Current: 490 µA (typical)

- · Enhanced EMI Protection:

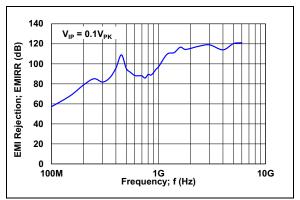

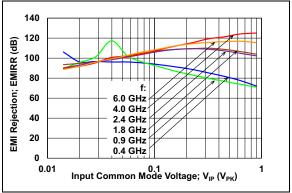

- EMIRR: 118 dB at 2.4 GHz (typical)

- Extended Temperature Range (E-Temp):

- -40°C to +125°C

## **Typical Applications**

- Motor Control

- · Analog Level Shifter

- · Industrial Computing

- · Battery Monitor/Tester

## **General Description**

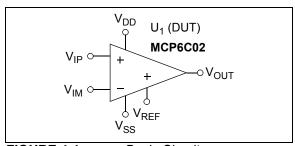

The Microchip Technology Inc. MCP6C02 high-side current sense amplifier is offered with preset gains of 20, 50 and 100 V/V. The Common-mode input range ( $V_{IP}$ ) is +3V to +65V. The differential-mode input range ( $V_{DM} = V_{IP} - V_{IM}$ ) supports unidirectional and bidirectional applications.

The power supply can be set between 2.0V and 5.5V. This device is specified from -40°C to +125°C (E-Temp) and is provided in the SOT-23 package.

The Zero-Drift architecture supports very low input errors, which allow a design to use shunt resistors of lower value (and lower power dissipation).

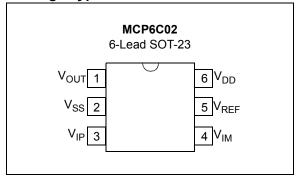

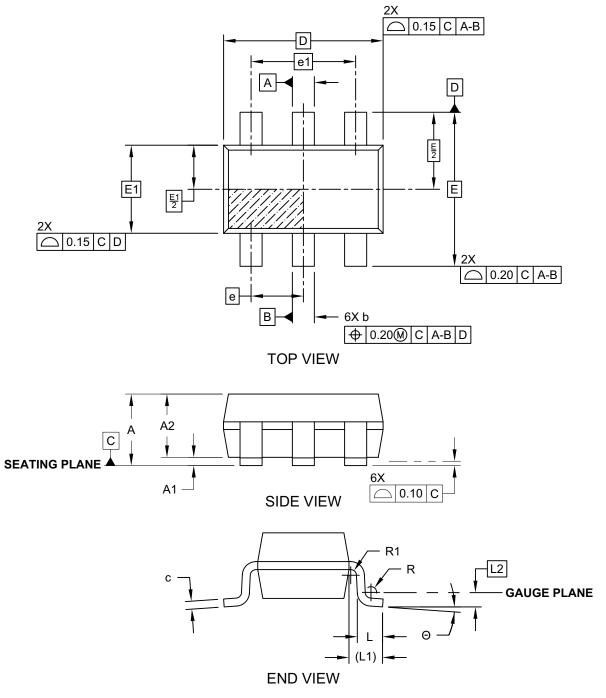

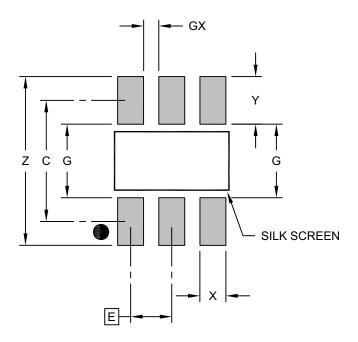

## **Package Types**

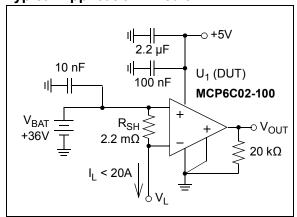

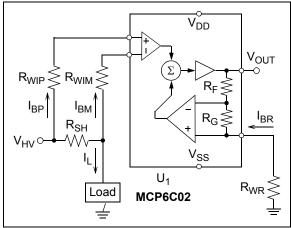

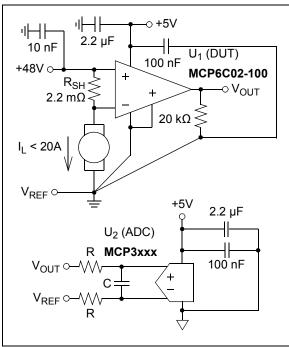

## Typical Application Circuit

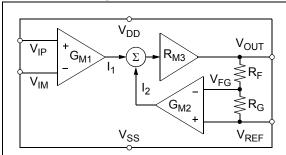

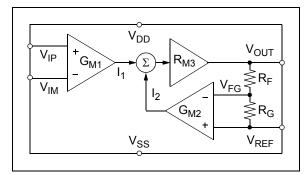

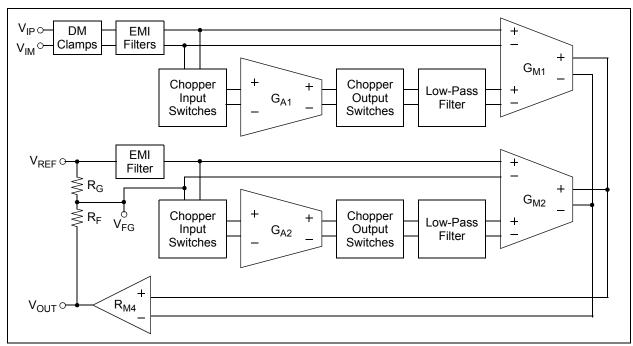

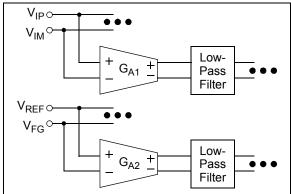

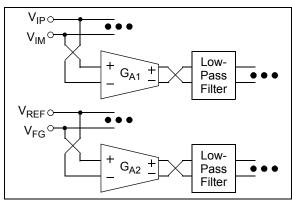

## **Functional Diagram**

## **Gain Options**

Table 1 shows key specifications that differentiate between the three different differential gain  $(G_{DM})$  options. See Section 1.0 "Electrical Characteristics", Section 6.0 "Packaging Information" and Product Identification System for further information on the GDM options available.

TABLE 1: KEY DIFFERENTIATING SPECIFICATIONS

| Part No.    | G <sub>DM</sub><br>(V/V)<br>Nom. | V <sub>OS</sub><br>(± μV)<br>Max. | TC <sub>1</sub><br>(± nV/°C)<br>Max. | CMRR<br>(dB)<br>Min. | PSRR<br>(dB)<br>Min. | V <sub>DMH</sub><br>(V)<br>Min. | BW<br>(kHz)<br>Typ. | E <sub>ni</sub><br>(μV <sub>p-p</sub> )<br>Typ. | e <sub>ni</sub><br>(nV/√Hz)<br>Typ. |

|-------------|----------------------------------|-----------------------------------|--------------------------------------|----------------------|----------------------|---------------------------------|---------------------|-------------------------------------------------|-------------------------------------|

| MCP6C02-020 | 20                               | 16                                | 90                                   | 132                  | 109                  | 0.265                           | 500                 | 1.54                                            | 74                                  |

| MCP6C02-050 | 50                               | 14                                | 70                                   | 138                  | 115                  | 0.106                           |                     | 0.95                                            | 46                                  |

| MCP6C02-100 | 100                              | 12                                | 65                                   |                      | 116                  | 0.053                           | 390                 | 0.92                                            | 44                                  |

**Note 1:** V<sub>OS</sub> and TC<sub>1</sub> limits are by design and characterization only.

**2:**  $TC_1$  covers the Extended Temperature Range (-40°C to +125°C).

3: CMRR is at  $V_{DD} = 5.5V$ .

**4:**  $E_{ni}$  is at f = 0.1 Hz to 10 Hz.  $e_{ni}$  is at f < 500 Hz.

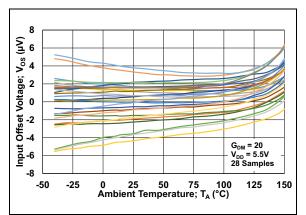

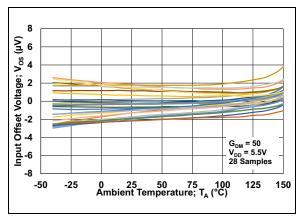

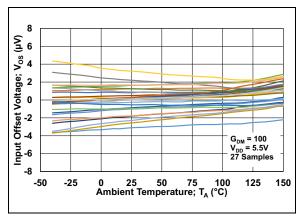

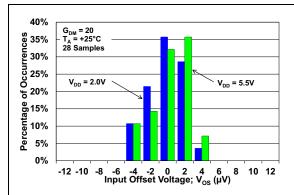

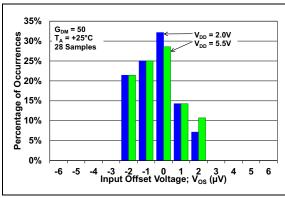

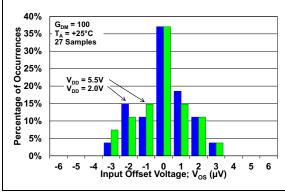

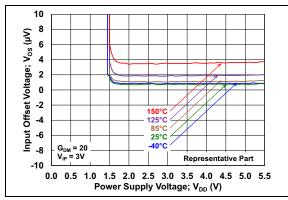

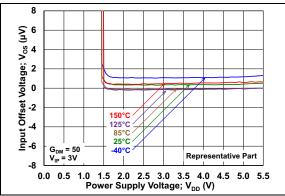

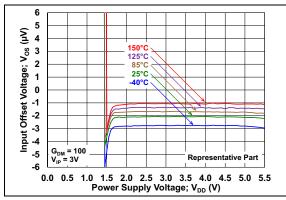

Figure 1, Figure 2 and Figure 3 show input offset voltage versus temperature for the three gain options ( $G_{DM}$  = 20, 50 and 100 V/V).

**FIGURE 1:** Input Offset Voltage vs. Temperature,  $G_{DM} = 20 \text{ V/V}$ .

**FIGURE 2:** Input Offset Voltage vs. Temperature,  $G_{DM} = 50 \text{ V/V}$ .

**FIGURE 3:** Input Offset Voltage vs. Temperature,  $G_{DM} = 100 \text{ V/V}$ .

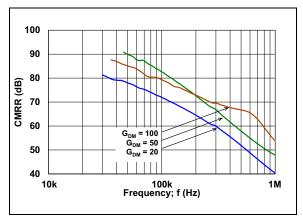

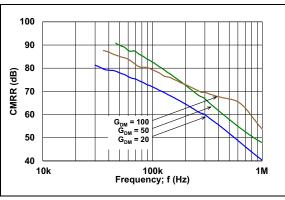

The MCP6C02's CMRR supports applications in noisy environments. Figure 4 shows how CMRR is high, even for frequencies near 100 kHz.

FIGURE 4: CMRR vs. Frequency.

NOTES:

## 1.0 ELECTRICAL CHARACTERISTICS

## 1.1 Absolute Maximum Ratings †

| V <sub>DD</sub> – V <sub>SS</sub>                             | 0.3V to +5.5V                      |

|---------------------------------------------------------------|------------------------------------|

| Current at Input Pins (Note 1)                                | ±2 mA                              |

| Analog Inputs (V <sub>IP</sub> and V <sub>IM</sub> ) (Note 1) | 0.3V to +70V                       |

| All Other Inputs and Outputs                                  | $V_{SS} - 0.3V$ to $V_{DD} + 0.3V$ |

| Input Difference Voltage (V <sub>DM</sub> )                   | ±1.2V                              |

| Output Short-Circuit Current                                  | Continuous                         |

| Current at Output and Supply Pins                             | ±30 mA                             |

| Storage Temperature                                           | 65°C to +150°C                     |

| Maximum Junction Temperature                                  | +155°C                             |

| ESD protection pins (HBM, CDM, MM)                            | ≥ 2 kV, 2 kV, 300V                 |

<sup>†</sup> **Notice:** Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operational sections of this specification is not intended. Exposure to maximum rating conditions for extended periods may affect device reliability.

Note 1: These voltage and current ratings are physically independent; both conditions must be enforced by the user.

## 1.2 Voltage and Temperature Ranges

The various voltage and temperature ranges are listed in Table 1-1.

TABLE 1-1: VOLTAGE AND TEMPERATURE RANGES

| Parameter                | Units  | G (VA)                | Comment                          |      |                     | Ra         | nge      |                |

|--------------------------|--------|-----------------------|----------------------------------|------|---------------------|------------|----------|----------------|

| Parameter                | Ullits | G <sub>DM</sub> (V/V) | Comment                          | Туре | Sym.                | Spec.      | Oper.    | Abs. Min./Max. |

| V <sub>DD</sub> (Note 2) | V      | All                   | V <sub>DD</sub> ↑<br>(LV POR on) | Min. | $V_{DDL}$           | 2.0        | 1.7      | -0.3           |

|                          |        |                       | V <sub>DD</sub> ↓<br>(LV POR on) |      | $V_{\mathrm{DDLD}}$ | 1.05       | _        | _              |

|                          |        |                       | LV POR<br>Hysteresis             |      | $V_{DDLH}$          | 0.1        |          |                |

|                          |        |                       | _                                | Тур. | _                   | 2.0 to 5.5 | _        | _              |

|                          |        |                       |                                  | Max. | $V_{DDH}$           | 5.5        | 5.5      | 5.5            |

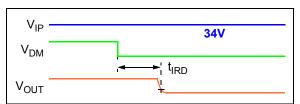

| V <sub>IP</sub> (Note 2) | V      | All                   | V <sub>IP</sub> ↑<br>(HV POR on) | Min. | $V_{IPL}$           | 3.0        | 2.8      | -0.3           |

|                          |        |                       | V <sub>IP</sub> ↓<br>(HV POR on) |      | V <sub>IPLD</sub>   | 2.8        | 2.6      |                |

|                          |        |                       | HV POR<br>Hysteresis             |      | V <sub>IPLH</sub>   | 0.2 Typ.   | 0.2 Typ. |                |

|                          |        |                       | _                                | Тур. | _                   | 34         | _        | _              |

|                          |        |                       |                                  | Max. | $V_{IPH}$           | 65         | 68       | 70             |

Note 1: All of this table's limits are set by design and characterization.

<sup>2:</sup> The HV POR is triggered by  $V_{IP}$ , with hysteresis. The LV POR is triggered by  $V_{DD}$ , with hysteresis.

<sup>3:</sup>  $V_{DM} = V_{IP} - V_{IM}$ .  $V_{IM}$  is in its range when both  $V_{IP}$  and  $V_{DM}$  are in their ranges.

**<sup>4:</sup>** Allowing the ambient temperature (T<sub>A</sub>) to exceed the Maximum Ambient Temperature limit (T<sub>AH</sub>) may cause parameters to exceed their specified limits. See **Section 1.1 "Absolute Maximum Ratings †"** for the Absolute Maximum Junction Temperature and Storage Temperature limits.

<sup>5:</sup>  $V_{OL}$  and  $V_{OH}$  are at  $R_L = 1 \text{ k}\Omega$ .

TABLE 1-1: VOLTAGE AND TEMPERATURE RANGES (CONTINUED)

|                  |       |                       |         |      |                 | Pa                            | nge                    |                       |

|------------------|-------|-----------------------|---------|------|-----------------|-------------------------------|------------------------|-----------------------|

| Parameter        | Units | G <sub>DM</sub> (V/V) | Comment |      |                 | Na                            | iige                   |                       |

| - urumotor       | Onno  | ODINI (*/*/           | Commont | Type | Sym.            | Spec.                         | Oper.                  | Abs. Min./Max.        |

| $V_{REF}$        | V     | All                   | _       | Min. | $V_{RL}$        | 0                             | 0                      | -0.3                  |

|                  |       |                       |         | Тур. |                 | V <sub>DD</sub> /4            |                        | _                     |

|                  |       |                       |         | Max. | $V_{RH}$        | V <sub>DD</sub> – 1.25        | V <sub>DD</sub> – 1.15 | V <sub>DD</sub> + 0.3 |

| V <sub>OUT</sub> | V     | All                   | _       | Min. | $V_{OL}$        | 0.06 Max                      | 0                      | -0.3                  |

| (Note 5)         |       |                       |         | Тур. | _               | V <sub>DD</sub> /2            | _                      | _                     |

|                  |       |                       |         | Max. | V <sub>OH</sub> | V <sub>DD</sub> – 0.13<br>Min | V <sub>DD</sub>        | V <sub>DD</sub> + 0.3 |

| $V_{DM}$         | V     | 20                    | _       | Min. | $V_{DML}$       | -3/G <sub>DM</sub>            | -4.25/G <sub>DM</sub>  | -1.2                  |

|                  |       | 50, 100               |         |      |                 | -4.05/G <sub>DM</sub>         |                        |                       |

|                  |       | All                   |         | Тур. | _               | 0                             | _                      | _                     |

|                  |       |                       |         | Max. | $V_{DMH}$       | 5.3/G <sub>DM</sub>           | 5.5/G <sub>DM</sub>    | +1.2                  |

| T <sub>A</sub>   | °C    | All                   | _       | Min. | T <sub>AL</sub> | -40                           | -40                    | -40                   |

|                  |       |                       |         | Тур. |                 | 25                            |                        | _                     |

|                  |       |                       | E-Temp  | Max. | T <sub>AH</sub> | +125                          | +150                   | +150                  |

Note 1: All of this table's limits are set by design and characterization.

<sup>2:</sup> The HV POR is triggered by  $V_{IP}$ , with hysteresis. The LV POR is triggered by  $V_{DD}$ , with hysteresis.

<sup>3:</sup>  $V_{DM} = V_{IP} - V_{IM}$ .  $V_{IM}$  is in its range when both  $V_{IP}$  and  $V_{DM}$  are in their ranges.

**<sup>4:</sup>** Allowing the ambient temperature (T<sub>A</sub>) to exceed the Maximum Ambient Temperature limit (T<sub>AH</sub>) may cause parameters to exceed their specified limits. See **Section 1.1 "Absolute Maximum Ratings †"** for the Absolute Maximum Junction Temperature and Storage Temperature limits.

<sup>5:</sup>  $V_{OL}$  and  $V_{OH}$  are at  $R_L = 1 \text{ k}\Omega$ .

## 1.3 Specifications

TABLE 1-2: DC ELECTRICAL CHARACTERISTICS

Electrical Characteristics: Unless otherwise indicated,  $T_A$  = +25°C,  $V_{DD}$  = 2.0V to 5.5V,  $V_{SS}$  = GND,  $V_{IP}$  = 34V,  $V_{DM}$  = 0V,  $V_{REF}$  =  $V_{DD}/4$ ,  $V_L$  =  $V_{DD}/2$  and  $R_L$  = 10 kΩ to  $V_L$ ; see Figure 1-9 and Figure 1-10.

| $v_{DM} = 0V$ , $v_{REF} = v_{DD}/4$ , $v_L = v_{DD}/2$ and $R_L = 10 \text{ k}\Omega$ to $v_L$ ; see Figure 1-9 and Figure 1-10. |                         |                       |       |      |                    |      |                                                 |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------|-------------------------|-----------------------|-------|------|--------------------|------|-------------------------------------------------|--|--|--|

| Parameter                                                                                                                         | Sym.                    | Min.                  | Тур.  | Max. | Units              | Gain | Conditions                                      |  |  |  |

| Input Offset (V <sub>IP</sub> and V <sub>IM</sub> )                                                                               | (Note 1)                |                       |       |      |                    |      |                                                 |  |  |  |

| Input Offset Voltage                                                                                                              | Vos                     | -16                   | ±1.9  | +16  | μV                 | 20   | Note 2                                          |  |  |  |

|                                                                                                                                   |                         | -14                   | ±1.65 | +14  |                    | 50   |                                                 |  |  |  |

|                                                                                                                                   |                         | -12                   | ±1.5  | +12  |                    | 100  |                                                 |  |  |  |

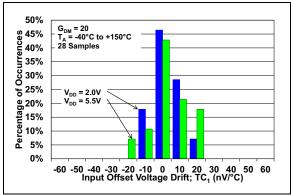

| V <sub>OS</sub> Drift,                                                                                                            | TC <sub>1</sub>         | -90                   | ±10   | +90  | nV/°C              | 20   | $T_A = -40^{\circ}C \text{ to } +125^{\circ}C,$ |  |  |  |

| Linear Temp. Co.                                                                                                                  |                         | -70                   | ±8    | +70  |                    | 50   | for E-Temp parts                                |  |  |  |

|                                                                                                                                   |                         | -65                   | ±7    | +65  |                    | 100  | (Note 2, Note 3)                                |  |  |  |

| V <sub>OS</sub> Drift,                                                                                                            | TC <sub>2</sub>         | _                     | ±60   | _    | pV/°C <sup>2</sup> | 20   |                                                 |  |  |  |

| Quadratic Temp. Co.                                                                                                               |                         |                       | ±95   |      |                    | 50   |                                                 |  |  |  |

|                                                                                                                                   |                         |                       | ±105  |      |                    | 100  |                                                 |  |  |  |

| V <sub>OS</sub> Drift,                                                                                                            | TC <sub>X</sub>         | _                     | 1.8   | _    | μV                 | 20   |                                                 |  |  |  |

| Exponential Temp. Co.                                                                                                             |                         |                       | 0.31  |      |                    | 50   |                                                 |  |  |  |

|                                                                                                                                   |                         |                       | 0.10  |      |                    | 100  |                                                 |  |  |  |

| Input Offset (V <sub>IP</sub> and V <sub>IM</sub> )                                                                               | – Contini               | ued (Note 1           | )     |      |                    |      |                                                 |  |  |  |

| V <sub>OS</sub> Aging                                                                                                             | $\Delta V_{OS}$         | _                     | ±0.18 | _    | μV                 | 20   | 108 hr at +150°C                                |  |  |  |

|                                                                                                                                   |                         |                       | ±0.11 |      |                    | 50   | (changes measured at +25°C)                     |  |  |  |

|                                                                                                                                   |                         |                       | ±0.09 |      |                    | 100  |                                                 |  |  |  |

| TC <sub>1</sub> Aging                                                                                                             | $\Delta TC_1$           | _                     | ±1.9  | _    | nV/°C              | 20   |                                                 |  |  |  |

|                                                                                                                                   |                         |                       | ±1.1  |      |                    | 50   |                                                 |  |  |  |

|                                                                                                                                   |                         |                       | ±1.0  |      |                    | 100  |                                                 |  |  |  |

| Power Supply Rejection                                                                                                            | PSRR                    | 109                   | 134   | _    | dB                 | 20   | V <sub>DD</sub> = 2.0V to 5.5V                  |  |  |  |

| Ratio                                                                                                                             |                         | 115                   | 138   |      |                    | 50   |                                                 |  |  |  |

|                                                                                                                                   |                         | 116                   | 140   |      |                    | 100  |                                                 |  |  |  |

| Input Current and Imped                                                                                                           | ance (V <sub>IP</sub> a | and V <sub>IM</sub> ) |       |      |                    |      |                                                 |  |  |  |

| V <sub>IP</sub> 's Input Bias Current                                                                                             | $I_{BP}$                | 120                   | 170   | 215  | μΑ                 | All  | V <sub>DD</sub> = 2.0V to 5.5V                  |  |  |  |

| V <sub>IM</sub> 's Input Bias Current                                                                                             | I <sub>BM</sub>         | _                     | ±0.2  | _    | nA                 |      | V <sub>DD</sub> = 5.5V                          |  |  |  |

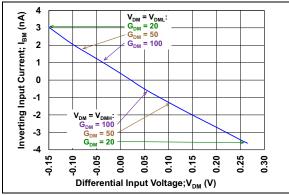

|                                                                                                                                   | I <sub>BM2</sub>        |                       | 3     |      |                    |      | $V_{DD}$ = 5.5V, $V_{DM}$ = $V_{DML}$           |  |  |  |

|                                                                                                                                   | I <sub>BM3</sub>        |                       | -2    |      |                    |      | $V_{DD}$ = 5.5V, $V_{DM}$ = $V_{DMH}$           |  |  |  |

| Capacitance at V <sub>IP</sub>                                                                                                    | $C_{VIP}$               | _                     | 40    | _    | pF                 |      |                                                 |  |  |  |

| Capacitance at V <sub>IM</sub>                                                                                                    | $C_{VIM}$               |                       | 11    |      |                    |      |                                                 |  |  |  |

| Capacitance across V <sub>DM</sub>                                                                                                | C <sub>VDM</sub>        |                       | 12    |      |                    |      |                                                 |  |  |  |

| Nists 4 The Medical Con-                                                                                                          |                         |                       |       |      | C . OME            |      | () ( ) ( )                                      |  |  |  |

- **Note 1:** The  $V_{IP}$  input is treated as the Common-mode input (e.g., for CMRR).  $V_{DM} = (V_{IP} V_{IM})$ .

- 2: Set by design and characterization. V<sub>OS</sub> is screened in production (see Appendix B: "Offset Test Screens").

- 3: See the discussion in **Section 1.6.2, Input Offset Related Errors**.

- 4: See Section 1.6, Explanation of DC Error Specifications.

TABLE 1-2: DC ELECTRICAL CHARACTERISTICS (CONTINUED)

Electrical Characteristics: Unless otherwise indicated,  $T_A$  = +25°C,  $V_{DD}$  = 2.0V to 5.5V,  $V_{SS}$  = GND,  $V_{IP}$  = 34V,  $V_{DM}$  = 0V,  $V_{REF}$  =  $V_{DD}/4$ ,  $V_L$  =  $V_{DD}/2$  and  $V_L$  = 10 kΩ to  $V_L$ ; see Figure 1-9 and Figure 1-10.

| $v_{DM} = vv$ , $v_{REF} = v_{DD}/4$ , $v_L = v_{DD}/2$ and $R_L = 10 \text{ k}\Omega$ to $v_L$ ; see Figure 1-9 and Figure 1-10. |                          |                       |        |                     |       |            |                                                                             |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------|--------------------------|-----------------------|--------|---------------------|-------|------------|-----------------------------------------------------------------------------|--|--|--|

| Parameter                                                                                                                         | Sym.                     | Min.                  | Тур.   | Max.                | Units | Gain       | Conditions                                                                  |  |  |  |

| Input Common-Mode Vo                                                                                                              | Itage (V <sub>IP</sub> ) |                       |        |                     |       |            |                                                                             |  |  |  |

| V <sub>IP</sub> 's Voltage Range Low                                                                                              | $V_{IPL}$                | _                     | 2.4    | 3.0                 | V     | All        | V <sub>IP</sub> ↑                                                           |  |  |  |

|                                                                                                                                   | V <sub>IPLD</sub>        |                       | 2.15   | 2.8                 |       |            | $V_{IP}\downarrow$                                                          |  |  |  |

|                                                                                                                                   | V <sub>IPLH</sub>        |                       | 0.2    | _                   |       |            | V <sub>IPLH</sub> = V <sub>IPL</sub> – V <sub>IPLD</sub>                    |  |  |  |

| V <sub>IP</sub> 's Voltage Range High                                                                                             | V <sub>IPH</sub>         | 65                    | _      | _                   |       |            |                                                                             |  |  |  |

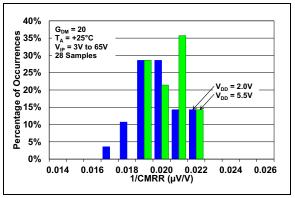

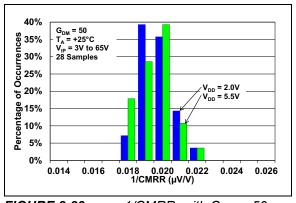

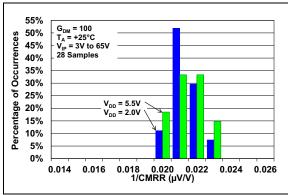

| Common-Mode Rejection                                                                                                             | CMRR                     | 132                   | 159    | _                   | dB    | 20         | V <sub>DD</sub> = 2.0V to 5.5V,                                             |  |  |  |

| Ratio                                                                                                                             |                          | 138                   | 163    |                     |       | 50         | V <sub>IP</sub> = 3V to 65V                                                 |  |  |  |

|                                                                                                                                   |                          |                       | 165    |                     |       | 100        |                                                                             |  |  |  |

| Common-Mode<br>Nonlinearity (Note 4)                                                                                              | INL <sub>CM</sub>        | _                     | ±0.006 | _                   | ppm   | All        | $V_{DD}$ = 5.5V, $V_{IP}$ = 3V to 65V                                       |  |  |  |

| Reference Voltage (V <sub>REF</sub> )                                                                                             | )                        |                       |        |                     |       |            |                                                                             |  |  |  |

| Reference Voltage                                                                                                                 | $V_{RL}$                 | _                     |        | 0                   | V     | All        | See Section 5.1.5, Setting                                                  |  |  |  |

| Range (Note 2)                                                                                                                    | $V_{RH}$                 | V <sub>DD</sub> −1.25 | _      | _                   |       |            | the Voltage at VREF                                                         |  |  |  |

| Gain Resistance                                                                                                                   | $R_F + R_G$              | _                     | 175    | _                   | kΩ    | 20         |                                                                             |  |  |  |

|                                                                                                                                   |                          |                       | 185    |                     |       | 50         |                                                                             |  |  |  |

|                                                                                                                                   |                          |                       | 240    |                     |       | 100        |                                                                             |  |  |  |

| V <sub>REF</sub> Input Capacitance                                                                                                | C <sub>REF</sub>         | _                     | 11     | _                   | pF    | All        |                                                                             |  |  |  |

| Differential Input (V <sub>DM</sub> ) (I                                                                                          | Note 1)                  |                       |        |                     |       |            |                                                                             |  |  |  |

| Differential Gain                                                                                                                 | $G_DM$                   |                       | 20     |                     | V/V   | 20         | MCP6C02-020                                                                 |  |  |  |

|                                                                                                                                   |                          |                       | 50     |                     |       | 50         | MCP6C02-050                                                                 |  |  |  |

|                                                                                                                                   |                          |                       | 100    |                     |       | 100        | MCP6C02-100                                                                 |  |  |  |

| Differential Input (V <sub>DM</sub> ) -                                                                                           | Continue                 |                       |        |                     |       |            |                                                                             |  |  |  |

| Differential Input Voltage                                                                                                        | $V_{DML}$                | -3/G <sub>DM</sub>    |        | _                   | V     | 20         | $V_{DD} = 5.5V, V_{REF} = 4.1V,$                                            |  |  |  |

| Range                                                                                                                             |                          | -4.05/G <sub>DM</sub> |        |                     |       | 50,        | $V_L = 0V$                                                                  |  |  |  |

|                                                                                                                                   | .,                       |                       |        | 5.0/0               |       | 100        |                                                                             |  |  |  |

|                                                                                                                                   | V <sub>DMH</sub>         | _                     |        | 5.3/G <sub>DM</sub> |       | All        | $V_{DD}$ = 5.5V, $V_{REF}$ = 0V, $V_{L}$ = $V_{DD}$                         |  |  |  |

| Differential Gain Error                                                                                                           | 9E                       | _                     | ±0.1   | _                   | %     |            | $V_{DD} = 2.0V, V_{REF} = 0.5V,$<br>$G_{DM}V_{DM} = -0.4V \text{ to } 1.4V$ |  |  |  |

|                                                                                                                                   |                          | -1.6                  | ±0.1   | +1.6                |       |            | $V_{DD}$ = 5.5V, $V_{REF}$ = 2.75V, $G_{DM}V_{DM}$ = -2.65V to 2.65V        |  |  |  |

|                                                                                                                                   |                          | _                     | ±0.1   | _                   |       |            | $V_{DD} = 5.5V, V_{REF} = 0V,$<br>$G_{DM}V_{DM} = 0.2V \text{ to } 5.3V$    |  |  |  |

|                                                                                                                                   |                          |                       | ±0.1   |                     |       | 20         | $V_{DD}$ = 5.5V, $V_{REF}$ = 4.25V, $G_{DM}V_{DM}$ = -3V to 1.3V            |  |  |  |

|                                                                                                                                   |                          |                       | ±0.1   |                     |       | 50,<br>100 | $V_{DD}$ = 5.5V, $V_{REF}$ = 4.25V, $G_{DM}V_{DM}$ = -4V to 1.3V            |  |  |  |

**Note 1:** The  $V_{IP}$  input is treated as the Common-mode input (e.g., for CMRR).  $V_{DM} = (V_{IP} - V_{IM})$ .

<sup>2:</sup> Set by design and characterization. V<sub>OS</sub> is screened in production (see Appendix B: "Offset Test Screens").

<sup>3:</sup> See the discussion in **Section 1.6.2, Input Offset Related Errors**.

<sup>4:</sup> See Section 1.6, Explanation of DC Error Specifications.

TABLE 1-2: DC ELECTRICAL CHARACTERISTICS (CONTINUED)

**Electrical Characteristics**: Unless otherwise indicated,  $T_A = +25^{\circ}C$ ,  $V_{DD} = 2.0V$  to 5.5V,  $V_{SS} = GND$ ,  $V_{IP} = 34V$ ,  $V_{DM} = 0V$ ,  $V_{REF} = V_{DD}/4$ ,  $V_L = V_{DD}/2$  and  $R_L = 10$  k $\Omega$  to  $V_L$ ; see Figure 1-9 and Figure 1-10.

| Parameter                                        | Sym.                                 | Min. | Тур.                  | Max.         | Units  | Gain | Conditions                                                                                                                                                 |

|--------------------------------------------------|--------------------------------------|------|-----------------------|--------------|--------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Differential Gain Drift                          | $\Delta g_E/\Delta T_A$              | _    | ±5                    | _            | ppm/°C | All  | $V_{DD} = 2.0V, V_{REF} = 0.5V,$<br>$G_{DM}V_{DM} = -0.4V \text{ to } 1.4V$                                                                                |

|                                                  |                                      | _    | ±5                    | _            |        |      | $V_{DD}$ = 5.5V, $V_{REF}$ = 2.75V, $G_{DM}V_{DM}$ = -2.65V to 2.65V                                                                                       |

| g <sub>E</sub> Aging                             | Δg <sub>E</sub>                      | _    | ±0.15                 | _            | %      |      | 408 hr at +150°C,<br>V <sub>DD</sub> = 5.5V, V <sub>REF</sub> = 2.75V,<br>G <sub>DM</sub> V <sub>DM</sub> = -2.65V to 2.65V,<br>(change measured at +25°C) |

| Differential Nonlinearity (Note 4)               | INL <sub>DM</sub>                    | _    | ±50                   | _            | ppm    |      | $V_{DD} = 2.0V, V_{REF} = 0.5V,$<br>$G_{DM}V_{DM} = -0.4V \text{ to } 1.4V$                                                                                |

|                                                  |                                      |      | ±100                  |              |        |      | $V_{DD} = 5.5V, V_{REF} = 2.75V,$<br>$G_{DM}V_{DM} = -2.65V \text{ to } 2.65V$                                                                             |

| Output (V <sub>OUT</sub> )                       |                                      |      |                       |              |        |      |                                                                                                                                                            |

| Minimum Output<br>Voltage Swing                  | V <sub>OL</sub>                      | _    | 3                     | _            | mV     | All  | $V_{DD}$ = 2.0V, $V_{REF}$ = 0V<br>$V_{DM}$ = -0.5V/ $G_{DM}$                                                                                              |

|                                                  |                                      |      | 5                     |              |        |      | $V_{DD}$ = 5.5V, $V_{REF}$ = 0V<br>$V_{DM}$ = -0.5V/ $G_{DM}$                                                                                              |

|                                                  |                                      |      | 20                    | 60           |        |      | $V_{DD}$ = 5.5V, $V_{REF}$ = 0V<br>$V_{DM}$ = -0.5V/ $G_{DM}$ , $R_{L}$ = 1 k $\Omega$                                                                     |

|                                                  |                                      |      | 3                     | _            |        |      | $V_{DD}$ = 5.5V, $V_{REF}$ = 0V<br>$V_{DM}$ = -0.5V/ $G_{DM}$ , $V_{L}$ = 0V                                                                               |

| Output (V <sub>OUT</sub> ) - Continue            | ed                                   |      |                       |              |        |      |                                                                                                                                                            |

| Maximum Output<br>Voltage Swing                  | V <sub>DD</sub> –<br>V <sub>OH</sub> | _    | 6                     | _            | mV     | All  | $V_{DD}$ = 2.0V, $V_{REF}$ = 0.75V<br>$V_{DM}$ = 1.75V/ $G_{DM}$                                                                                           |

|                                                  |                                      |      | 10                    |              |        |      | $V_{DD}$ = 5.5V, $V_{REF}$ = 4.25V $V_{DM}$ = -1.75V/ $G_{DM}$                                                                                             |

|                                                  |                                      |      | 40                    | 130          |        |      | $V_{DD}$ = 5.5V, $V_{REF}$ = 4.25V<br>$V_{DM}$ = 1.75V/ $G_{DM}$ , $R_{L}$ = 1 k $\Omega$                                                                  |

|                                                  |                                      |      | 5                     | <del>-</del> |        |      | $V_{DD}$ = 5.5V, $V_{REF}$ = 0V<br>$V_{DM}$ = 1.75V/ $G_{DM}$ , $V_{L}$ = $V_{DD}$                                                                         |

| Output Short Circuit<br>Current                  | I <sub>SCP</sub>                     | _    | +12<br>+20            | _            |        |      | $V_{DD} = 2.0V, G_{DM}V_{DM} = 1.0V$<br>$V_{DD} = 5.5V, G_{DM}V_{DM} = 2.75V$                                                                              |

|                                                  | I <sub>SCM</sub>                     | _    | -12<br>-20            | _            |        |      | $V_{DD} = 2.0V, G_{DM}V_{DM} = 0V$<br>$V_{DD} = 5.5V, G_{DM}V_{DM} = 0V$                                                                                   |

| Power Supplies (V <sub>DD</sub> , V <sub>S</sub> | e and V <sub>IP</sub> )              |      |                       |              | l      |      | ואוט ואוט ואוט אייי טט ן                                                                                                                                   |

| Low Supply Voltage                               | V <sub>DD</sub>                      | 2.0  |                       | 5.5          | V      | All  |                                                                                                                                                            |

| High Supply Voltage                              | V <sub>IP</sub>                      |      | e V <sub>IP</sub> spe |              |        |      |                                                                                                                                                            |

| Quiescent Current at V <sub>SS</sub>             | I <sub>SS</sub>                      |      | -660                  | _            | μA     |      | I <sub>O</sub> = 0A                                                                                                                                        |

| Quiescent Current at V <sub>DD</sub>             | I <sub>DD</sub>                      | 300  | 490                   | 725          |        |      |                                                                                                                                                            |

| Quiescent Current at V <sub>IP</sub>             | $I_{BP}$                             | (00) | e I <sub>BP</sub> spe | c)           |        |      |                                                                                                                                                            |

- **Note 1:** The  $V_{IP}$  input is treated as the Common-mode input (e.g., for CMRR).  $V_{DM} = (V_{IP} V_{IM})$ .

- 2: Set by design and characterization. V<sub>OS</sub> is screened in production (see Appendix B: "Offset Test Screens").

- 3: See the discussion in Section 1.6.2, Input Offset Related Errors.

- 4: See Section 1.6, Explanation of DC Error Specifications.

## TABLE 1-2: DC ELECTRICAL CHARACTERISTICS (CONTINUED)

**Electrical Characteristics**: Unless otherwise indicated,  $T_A = +25^{\circ}C$ ,  $V_{DD} = 2.0V$  to 5.5V,  $V_{SS} = GND$ ,  $V_{IP} = 34V$ ,  $V_{DM} = 0V$ ,  $V_{REF} = V_{DD}/4$ ,  $V_L = V_{DD}/2$  and  $R_L = 10$  k $\Omega$  to  $V_L$ ; see Figure 1-9 and Figure 1-10.

| 2 112. 22                                          |                  |      |      | <u>-                                      </u> |       |      |                                                                                                              |

|----------------------------------------------------|------------------|------|------|------------------------------------------------|-------|------|--------------------------------------------------------------------------------------------------------------|

| Parameter                                          | Sym.             | Min. | Тур. | Max.                                           | Units | Gain | Conditions                                                                                                   |

| POR Trip Voltages,<br>Low-Side (V <sub>DD</sub> )  | V <sub>PLL</sub> | 1.05 | 1.35 | _                                              | V     | All  | LV POR turns off $(V_{DD} \downarrow)$ ,<br>$V_{L} = 0V$ , $V_{IP} = 3V$ , $V_{REF} = 0V$                    |

|                                                    | V <sub>PLH</sub> | _    | 1.45 | 1.7                                            |       |      | LV POR turns on $(V_{DD} \uparrow)$ ,<br>$V_{L} = 0V$ , $V_{IP} = 3V$ , $V_{REF} = 0V$                       |

| POR Trip Voltages,<br>High-Side (V <sub>IP</sub> ) | V <sub>PHL</sub> | 1.7  | 1.95 | _                                              |       |      | HV POR turns off ( $V_{IP} \downarrow$ ),<br>R <sub>L</sub> = open, $V_{DD}$ = 5.5V<br>(change in $I_{SS}$ ) |

|                                                    | V <sub>PHH</sub> | _    | 2.05 | 2.6                                            |       |      | HV POR turns on $(V_{IP} \uparrow)$ ,<br>$R_L$ = open, $V_{DD}$ = 5.5V<br>(change in $I_{SS}$ )              |

- **Note 1:** The  $V_{IP}$  input is treated as the Common-mode input (e.g., for CMRR).  $V_{DM} = (V_{IP} V_{IM})$ .

- 2: Set by design and characterization. V<sub>OS</sub> is screened in production (see Appendix B: "Offset Test Screens").

- 3: See the discussion in Section 1.6.2, Input Offset Related Errors.

- 4: See Section 1.6, Explanation of DC Error Specifications.

## TABLE 1-3: AC ELECTRICAL CHARACTERISTICS

| <b>Electrical Characteristics</b> : Unless otherwise indicated, $T_A = +25^{\circ}C$ , $V_{DD} = 2.0V$ to 5.5V, $V_{SS} = GND$ , $V_{IP} = 34V$ , $V_{DM} = 0V$ , $V_{RFF} = V_{DD}/4$ , $V_{I} = V_{DD}/2$ , $V_{I} = 10$ kΩ to $V_{I}$ and $V_{I} = 60$ pF; see Figure 1-11. |                   |                             |        |       |       |         |                                                                                                         |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-----------------------------|--------|-------|-------|---------|---------------------------------------------------------------------------------------------------------|--|--|--|

| Parameter                                                                                                                                                                                                                                                                      | Sym.              | <u>-</u>                    | l .    | Max.  | Units | Gain    | Conditions                                                                                              |  |  |  |

| AC Response                                                                                                                                                                                                                                                                    |                   |                             |        |       |       |         |                                                                                                         |  |  |  |

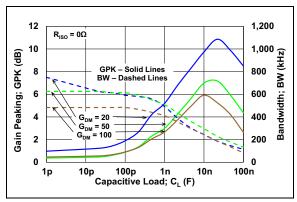

| Bandwidth                                                                                                                                                                                                                                                                      | BW                | _                           | 500    | _     | kHz   | 20, 50  | $G_{DM}V_{DM} = 0.1V_{p-p}$                                                                             |  |  |  |

|                                                                                                                                                                                                                                                                                |                   |                             | 390    |       |       | 100     |                                                                                                         |  |  |  |

| Gain Peaking                                                                                                                                                                                                                                                                   | GPK               | _                           | 0      | _     | dB    | All     |                                                                                                         |  |  |  |

| Step Response                                                                                                                                                                                                                                                                  |                   |                             |        |       |       |         |                                                                                                         |  |  |  |

| V <sub>DM</sub> Slew Rate                                                                                                                                                                                                                                                      | SR                | (                           | Note 1 | )     | V/µs  | All     | $G_{DM}V_{DM}$ Step = $V_{DD} - 0.5V$                                                                   |  |  |  |

| V <sub>DM</sub> Step Overshoot                                                                                                                                                                                                                                                 | OS <sub>DM</sub>  | _                           | 4      | _     | %     |         | $G_{DM}V_{DM}$ Step = 0.1V, $t_{r_in}$ = 0.2 µs                                                         |  |  |  |

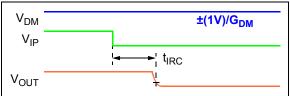

| Overdrive Recovery,<br>Input Differential Mode                                                                                                                                                                                                                                 | t <sub>IRDL</sub> | _                           | 3      | _     | μs    | 20      | $V_{DD}$ = 5.5V, $V_{REF}$ = 4V,<br>$G_{DM}V_{DM}$ = -3.5V to -1.25V Step,<br>90% of $V_{OUT}$ change   |  |  |  |

|                                                                                                                                                                                                                                                                                |                   | (see t <sub>ORL</sub> Spec) |        | Spec) |       | 50, 100 | (Note 2)                                                                                                |  |  |  |

|                                                                                                                                                                                                                                                                                | t <sub>IRDH</sub> |                             | 3      | _     |       | All     | $V_{DD}$ = 5.5V, $V_{REF}$ = 0.5V,<br>$G_{DM}V_{DM}$ = +4.5V to +2.25V Step,<br>90% of $V_{OUT}$ change |  |  |  |

- Note 1: SR is limited by GBWP; the large signal step response is dominated by the small signal bandwidth.

- 2: At these gains, we cannot distinguish between overdriving V<sub>DM</sub> or V<sub>OUT</sub>.

- **3:** See Figure 2-57 for the noise density over a wider frequency range.

TABLE 1-3: AC ELECTRICAL CHARACTERISTICS (CONTINUED)

**Electrical Characteristics**: Unless otherwise indicated,  $T_A$  = +25°C,  $V_{DD}$  = 2.0V to 5.5V,  $V_{SS}$  = GND,  $V_{IP}$  = 34V,  $V_{DM}$  = 0V,  $V_{REF}$  =  $V_{DD}/4$ ,  $V_L$  =  $V_{DD}/2$ ,  $R_L$  = 10 kΩ to  $V_L$  and  $C_L$  = 60 pF; see Figure 1-11.

| V <sub>DM</sub> = UV, V <sub>REF</sub> = V <sub>DD</sub> /4, V |                   |      |      | 1    |               |      |                                                                                                         |

|----------------------------------------------------------------|-------------------|------|------|------|---------------|------|---------------------------------------------------------------------------------------------------------|

| Parameter                                                      | Sym.              | Min. | Тур. | Max. | Units         | Gain | Conditions                                                                                              |

| Overdrive Recovery, Output                                     | t <sub>ORL</sub>  | _    | 1.5  | _    | μs            | All  | $V_{DD}$ = 2.0V, $V_{REF}$ = 0V,<br>$G_{DM}V_{DM}$ = -0.5V to +1V Step,<br>90% of $V_{OUT}$ change      |

|                                                                |                   |      | 1.5  |      |               |      | $V_{DD}$ = 5.5V, $V_{REF}$ = 0V,<br>$G_{DM}V_{DM}$ = -0.5V to +2.75V Step,<br>90% of $V_{OUT}$ change   |

|                                                                | t <sub>ORH</sub>  | _    | 1.5  | _    |               |      | $V_{DD}$ = 2.0V, $V_{REF}$ = 0.6V, $G_{DM}V_{DM}$ = +1.9V to +0.4V Step, 90% of $V_{OUT}$ change        |

|                                                                |                   |      | 1.5  |      |               |      | $V_{DD}$ = 5.5V, $V_{REF}$ = 4.1V,<br>$G_{DM}V_{DM}$ = +1.9V to -1.35V Step,<br>90% of $V_{OUT}$ change |

| Noise                                                          |                   |      |      |      |               |      |                                                                                                         |

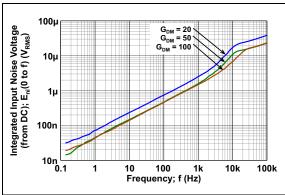

| Input Noise Voltage                                            | E <sub>ni</sub>   | _    | 0.48 | _    | $\mu V_{p-p}$ | 20   | f = 0.01 Hz to 1 Hz                                                                                     |

|                                                                |                   |      | 0.30 |      |               | 50   |                                                                                                         |

|                                                                |                   |      | 0.29 |      |               | 100  |                                                                                                         |

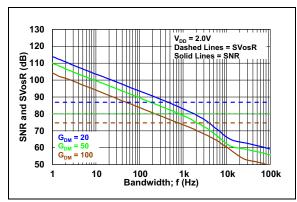

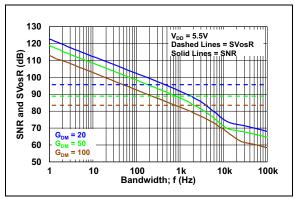

|                                                                |                   | _    | 1.54 | _    |               | 20   | f = 0.1 Hz to 10 Hz                                                                                     |

|                                                                |                   |      | 0.95 |      |               | 50   |                                                                                                         |

|                                                                |                   |      | 0.92 |      |               | 100  |                                                                                                         |

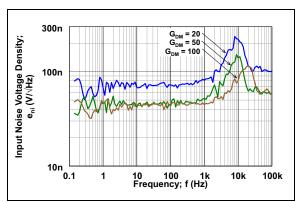

| Input Noise Voltage                                            | e <sub>ni</sub>   | _    | 74   | _    | nV/√Hz        | 20   | f < 500 Hz                                                                                              |

| Density (Note 3)                                               |                   |      | 46   |      |               | 50   |                                                                                                         |

|                                                                |                   |      | 44   |      |               | 100  | f < 1 kHz                                                                                               |

| Input Current Noise<br>Density – At V <sub>IP</sub>            | i <sub>nip</sub>  | _    | 10   |      | pA/√Hz        | All  | f = 1 kHz                                                                                               |

| Input Current Noise                                            | i <sub>nim</sub>  | _    | 8    | _    | fA/√Hz        |      | $f = 1 \text{ kHz}, V_{DM} = 0V$                                                                        |

| Density – At V <sub>IM</sub>                                   |                   |      | 33   |      |               |      | f = 1 kHz, V <sub>DM</sub> = 0.15V                                                                      |

| EMI Protection                                                 |                   |      |      |      |               |      |                                                                                                         |

| EMI Rejection Ratio                                            | EMIRR             |      | 96   | _    | dB            | All  | $V_{IN} = 0.1 V_{PK}$ , f = 400 MHz                                                                     |

|                                                                |                   |      | 91   |      |               |      | $V_{IN} = 0.1V_{PK}, f = 900 \text{ MHz}$                                                               |

|                                                                |                   |      | 114  |      |               |      | V <sub>IN</sub> = 0.1V <sub>PK</sub> , f = 1800 MHz                                                     |

|                                                                |                   |      | 118  |      |               |      | V <sub>IN</sub> = 0.1V <sub>PK</sub> , f = 2400 MHz                                                     |

|                                                                |                   |      | 121  |      |               |      | $V_{IN} = 0.1 V_{PK}$ , f = 6000 MHz                                                                    |

| Power Up/Down                                                  |                   |      |      |      |               |      | ,                                                                                                       |

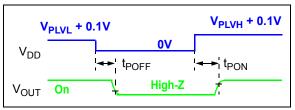

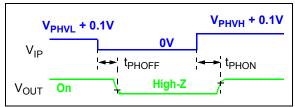

| Power On Time (V <sub>DD</sub> ↑),<br>V <sub>OUT</sub> Settles | t <sub>PON</sub>  | -    | 65   | _    | μs            | All  | $V_{DD}$ = 0V to 2.0V, $V_{L}$ = 0V, 90% of $V_{OUT}$ change                                            |

|                                                                |                   |      | 140  |      |               |      | $V_{DD}$ = 0V to 5.5V, $V_{L}$ = 0V, 90% of $V_{OUT}$ change                                            |

| Power Off Time $(V_{DD} \downarrow)$ , $V_{OUT}$ Settles       | t <sub>POFF</sub> | _    | 8    | _    |               |      | $V_{\rm DD}$ = 2.0V to 0V, $V_{\rm L}$ = 0V, 90% of $V_{\rm OUT}$ change                                |

|                                                                |                   |      | 5.5  |      |               |      | $V_{DD}$ = 5.5V to 0V, $V_{L}$ = 0V, 90% of $V_{OUT}$ change                                            |

Note 1: SR is limited by GBWP; the large signal step response is dominated by the small signal bandwidth.

<sup>2:</sup> At these gains, we cannot distinguish between overdriving  $V_{DM}$  or  $V_{OUT}$ .

**<sup>3:</sup>** See Figure 2-57 for the noise density over a wider frequency range.

### TABLE 1-4: TEMPERATURE SPECIFICATIONS

| <b>Electrical Characteristics</b> : Unless otherwise indicated, $T_A = +25^{\circ}C$ , $V_{DD} = 2.0V$ to 5.5V, $V_{SS} = GND$ and $V_{IP} = 34V$ . |                |      |      |      |       |            |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|----------------|------|------|------|-------|------------|--|--|

| Parameters                                                                                                                                          | Sym.           | Min. | Тур. | Max. | Units | Conditions |  |  |

| Specified Temperature Range                                                                                                                         | T <sub>A</sub> | -40  | _    | +125 | °C    |            |  |  |

| Operating Temperature Range                                                                                                                         |                | -40  | _    | +150 |       | Note 1     |  |  |

| Storage Temperature Range                                                                                                                           |                | -60  | _    | +150 |       | No power   |  |  |

| Thermal Resistance, 6L-SOT-23                                                                                                                       | $\theta_{JA}$  | _    | 191  |      | °C/W  |            |  |  |

**Note 1:** Operation must not cause T<sub>J</sub> to exceed the Absolute Maximum Junction Temperature specification, which is 155°C. See **Section 4.1.5, Temperature Performance** for design tips.

## 1.4 Simplified Diagrams

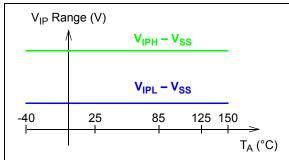

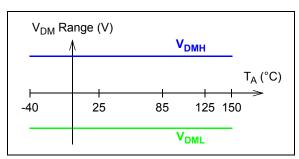

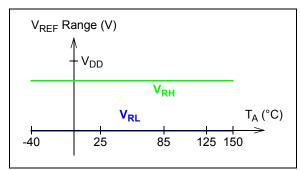

#### 1.4.1 VOLTAGE RANGE DIAGRAMS

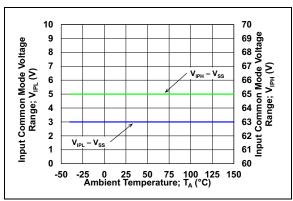

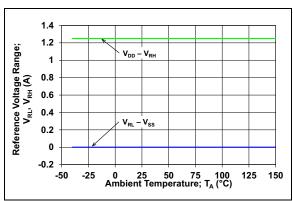

These ranges are constant across temperature.

FIGURE 1-1: Common-Mode Input Voltage Range vs. Temperature.

**FIGURE 1-2:** Differential Input Voltage Range vs. Temperature.

**FIGURE 1-3:** Reference Voltage Range vs. Temperature.

### 1.4.2 TIMING DIAGRAMS

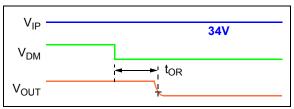

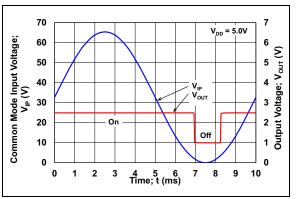

FIGURE 1-4: Common-Mode Input Overdrive Recovery Timing Diagram.

**FIGURE 1-5:** Differential-Mode Input Overdrive Recovery Timing Diagram.

**FIGURE 1-6:** Output Overdrive Recovery Timing Diagram.

**FIGURE 1-7:**  $V_{OUT}$  Power On/Off Timing Diagram, Low-Side.

**FIGURE 1-8:** V<sub>OUT</sub> Power On/Off Timing Diagram, High-Side.

## 1.5 Simplified Test Circuits

## 1.5.1 V<sub>OS</sub> TEST CIRCUIT

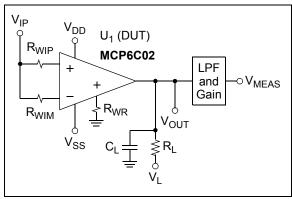

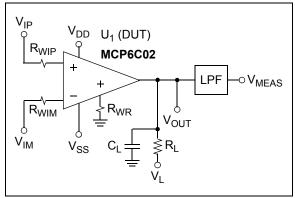

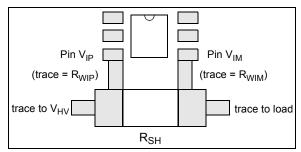

Figure 1-9 tests the MCP6C02's input offset errors ( $V_{OS}$ , 1/CMRR, 1/CMRR2 and 1/PSRR, etc.).  $R_{WIP}$  is set very low, so  $I_{BP}$  does not affect the result.  $V_{OUT}$  is filtered and amplified, before measuring the result.

FIGURE 1-9: Input Offset Test Circuit for the MCP6C02.

When MCP6C02 is in its normal range of operation, the DC output voltages are ( $V_E$  is the sum of input offset errors and  $g_E$  is the gain error):

#### **EQUATION 1-1:**

$$\begin{split} G_{DM} &= \text{DM Gain} \\ V_{OUT} &= G_{DM}(1+g_E)V_E + V_{REF} \\ V_{MEAS} &= G_{PA}V_{OUT} \end{split}$$

The resistances at the Device Under Test (DUT) need to be small enough for accuracy (see Figure 1-10). These resistances include wires, traces, vias, etc.

## **EQUATION 1-2:**

$$R_{WIP} \le 4 \ m\Omega$$

$R_{WIM} \le 0.1\Omega$

$R_{WR} \le 1\Omega$

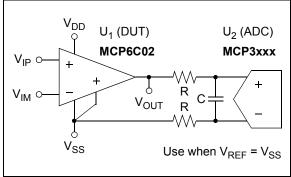

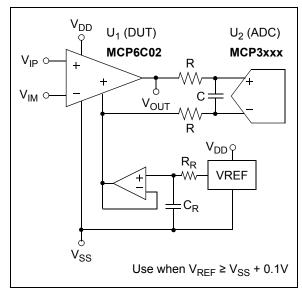

## 1.5.2 DC DIFFERENTIAL GAIN TEST CIRCUIT

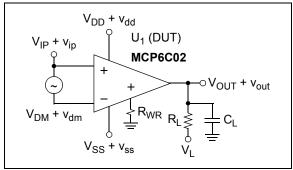

Figure 1-10 is used for testing the differential gain error, nonlinearity and input voltage range ( $g_E$ , INL $_{DM}$ ,  $V_{DML}$  and  $V_{DMH}$ ). We compare  $V_{MEAS}$  with the ideal  $V_{OUT}$ , then extract the above parameters.

FIGURE 1-10: Differential Gain Test Circuit.

When measuring the differential input range, all of the voltages must be in range except  $V_{DM}$ .

When measuring differential errors (g<sub>E</sub>,  $\Delta$ g<sub>E</sub>/ $\Delta$ T<sub>A</sub> and INL<sub>DM</sub>), all voltages are held constant, except V<sub>DM</sub>.

For accuracy, the wiring resistances at the DUT need to be very small (see Equation 1-2).

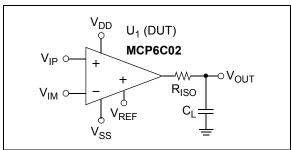

#### 1.5.3 AC GAINS TEST CIRCUIT

Figure 1-11 is used for testing the INA's different AC gains. The AC voltages are:

- · vout is the AC output

- v<sub>ip</sub> is the AC Common-mode input, used for CMRR plots

- v<sub>dm</sub> is the AC differential input, used for G<sub>DM</sub> plots (also for CMRR and PSRR)

- v<sub>dd</sub> and v<sub>ss</sub> are the AC supply inputs, used for PSRR plots (including PSRR+ and PSRR-)

FIGURE 1-11: AC Gain Test Circuit.

The impedance at  $V_{REF}$  (shown here as  $R_{WR}$ ) needs to have a magnitude less than  $1\Omega$ , for gain accuracy in the signal bandwidth. The magnitude needs to be <  $50\Omega$ , when f < 1 MHz, to maintain good stability.

# 1.6 Explanation of DC Error Specifications

### 1.6.1 LINEAR RESPONSE MODEL

When the inputs and the output are in their normal ranges, and the nonlinear errors are negligible, the output voltage ( $V_{OUT}$ ) is:

### **EQUATION 1-3:**

$$V_{OUT} = V_{REF} + G_{DM}(1 + g_E)(V_{DM} + V_E)$$

$V_{DM}$  is the input voltage.  $V_E$  is the sum of input offset errors (due to  $V_{OS}$ , PSRR, CMRR, CMRR2,  $TC_1$ ,  $TC_2$ , etc.).  $g_E$  is the gain error ( $G_{DM}$  is the nominal gain).

### 1.6.2 INPUT OFFSET RELATED ERRORS

When  $V_{DM}$  = 0V, the linear response model for  $V_{OUT}$  becomes:

### **EQUATION 1-4:**

$$V_{OUT} = V_{REF} + G_{DM}(1 + g_E)V_E$$

The input offset error  $(V_E)$  is extracted from input offset measurements (see Section 1.5.1 "VOS Test Circuit"):

#### **EQUATION 1-5:**

$$V_E = \frac{V_{OUT} - V_{REF}}{G_{DM}(1 + g_E)}$$

We usually assume  $g_E = 0$ , in Equation 1-5, when extracting  $V_E$ . The result is accurate enough, since  $g_E$  is so low.

$V_E$  has several terms, which assume a linear response to changes in  $V_{DD},\,V_{SS},\,V_{IP}$  and  $V_{REF}$

$V_{OS}$ 's dependence on temperature  $(T_A)$  is quadratic plus exponential  $(V_{OS},\,TC_1,\,TC_2$  and  $TC_X). The aging specs <math display="inline">(\Delta V_{OS}\,\mbox{and}\,\Delta TC_1)$  are not included, for simplicity.

The exponential factor in Equation 1-6 decreases at colder temperatures  $(T_A)$ . This table gives an indication of this relationship.

TABLE 1-5: EXPONENTIAL TERM

| T <sub>A</sub> (°C) | 2 <sup>((T<sub>A</sub> - 150°C)/(10°C))</sup> |

|---------------------|-----------------------------------------------|

| ≤ 65                | ≤ 0.003                                       |

| +85                 | 0.011                                         |

| +105                | 0.044                                         |

| +125                | 0.177                                         |

| +150                | 1.000                                         |

## **EQUATION 1-6:**

$$V_E = V_{OS} + \frac{\Delta V_{DD} - \Delta V_{SS}}{PSRR} + \frac{\Delta V_{IP}}{CMRR} + \frac{\Delta V_{REF}}{CMRR2} + \Delta T_A TC_1 + \Delta T_A^2 TC_2 + TC_X 2 \frac{((T_A - 150\, ^\circ \text{C})/(10\, ^\circ \text{C}))}{(T_A - 150\, ^\circ \text{C})/(10\, ^\circ \text{C})}$$

Where:

PSRR, CMRR and CMRR2 are in units of V/V  $\Delta T_A$  is in units of °C  $V_{DM}$  = 0

## 1.6.3 INPUT OFFSET'S COMMON-MODE VOLTAGE NONLINEARITY

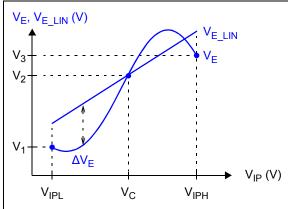

The input offset error ( $V_E$ ) changes nonlinearly with  $V_{IP}$ . Figure 1-12 shows the MCP6C02's  $V_E$  vs.  $V_{IP}$ , as well as a linear fit line ( $V_E$ <sub>LIN</sub>), that goes through the center point ( $V_C$ ,  $V_2$ ) and has the same slope as the end points.

FIGURE 1-12: Input Offset Error vs. Common-Mode Input Voltage.

The part is in standard conditions ( $\Delta V_{OUT} = 0$ ,  $V_{DM} = 0$ , etc.).  $V_{IP}$  sweeps from  $V_{IPL}$  to  $V_{IPH}$ . The test circuit is in **Section 1.5.1, VOS Test Circuit**. Calculate  $V_E$  at each point with Equation 1-5.

Based on the measured  $V_{\text{E}}$  data, we obtain the following linear fit:

#### **EQUATION 1-7:**

$$V_{E\_LIN} = V_2 + (V_{IP} - V_C) / CMRR$$

Where:

$$V_C = (V_{IPL} + V_{IPH}) / 2$$

$$1 / CMRR = (V_3 - V_1) / (V_{IPH} - V_{IPL})$$

The remaining error  $(\Delta V_E)$  is described by the Common-mode Nonlinearity spec:

#### **EQUATION 1-8:**

$$\begin{split} INL_{CMH} &= \max(\Delta V_E) / (V_{IPH} - V_{IPL}) \\ INL_{CML} &= \min(\Delta V_E) / (V_{IPH} - V_{IPL}) \\ INL_{CM} &= INL_{CMH}, \quad |INL_{CMH}| \geq |INL_{CML}| \\ &= INL_{CML}, \quad \text{otherwise} \\ \\ \text{Where:} \\ \Delta V_E &= V_E - V_{E\_LIN} \end{split}$$

## 1.6.4 DIFFERENTIAL GAIN ERROR AND NONLINEARITY

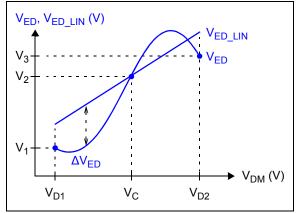

The differential errors are extracted from differential gain measurements (see Section 1.5.2, DC Differential Gain Test Circuit), based on Equation 1-3. These errors are then split into the differential gain error ( $g_E$ ) and the input nonlinearity error INL $_{DM}$ .

The error  $V_{ED}$  is calculated by subtracting the ideal output from  $V_{OUT}$ , then dividing by the ideal gain  $G_{DM}$ .

#### **EQUATION 1-9:**

$$V_{ED} = (V_{OUT} - (V_{REF} + G_{DM} \cdot V_{DM}))/G_{DM}$$

Figure 1-13 shows  $V_{ED}$  vs.  $V_{DM}$ , as well as a linear fit line ( $V_{ED\_LIN}$ ) based on  $V_{DM}$  and  $g_E$ . The amplifier is in one of the standard condition sets. The linear fit line ( $V_{ED\_LIN}$ ) goes through the center point ( $V_C$ ,  $V_2$ ) and has the same slope as the end points.

**FIGURE 1-13:** Differential Input Error vs. Differential Input Voltage.

Based on the measured  $V_{\text{ED}}$  data, we obtain the following linear fit:

#### **EQUATION 1-10:**

$$V_{ED\_LIN} = V_2 + (V_{DM} - V_C)g_E$$

Where:

$$V_C = (V_{DI} + V_{D2})/2$$

$$g_E = (V_3 - V_I)/(V_{D2} - V_{DI})$$

The remaining error ( $\Delta V_{ED}$ ) is described by the Differential Nonlinearity spec:

### **EQUATION 1-11:**

$$\begin{split} INL_{DMH} &= \max(\Delta V_{ED})/(V_{D2} - V_{D1}) \\ INL_{DML} &= \min(\Delta V_{ED})/(V_{D2} - V_{D1}) \\ INL_{DM} &= INL_{DMH}, \quad \left|INL_{DMH}\right| \geq \left|INL_{DML}\right| \\ &= INL_{DML}, \quad \text{otherwise} \\ \\ \text{Where:} \\ \Delta V_{ED} &= V_{ED} - V_{ED\_LIN} \end{split}$$

The aging spec  $\Delta g_E$  is not included here, for simplicity.  $V_{DM}$  sweeps are not always centered on  $V_{DM}$  = 0V; the INL<sub>DM</sub> spec will interact with the  $V_{OS}$  spec.

NOTES:

## 2.0 TYPICAL PERFORMANCE CURVES

**Note:** The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore outside the warranted range.

Note: Unless otherwise indicated,  $T_A = +25^{\circ}C$ ,  $V_{DD} = 2.0V$  to 5.5V,  $V_{SS} = GND$ ,  $V_{IP} = 34V$ ,  $V_{DM} = 0V$ ,  $V_{REF} = V_{DD}/4$ ,  $V_L = V_{DD}/2$ ,  $R_L = 10$  k $\Omega$  to  $V_L$  and  $C_L = 60$  pF; see Figure 1-9, Figure 1-10 and Figure 1-11.

## 2.1 DC Precision

FIGURE 2-1: Input Offset Voltage, G<sub>DM</sub> = 20.

**FIGURE 2-2:** Input Offset Voltage,  $G_{DM} = 50$ .

FIGURE 2-3: Input Offset Voltage,  $G_{DM} = 100$ .

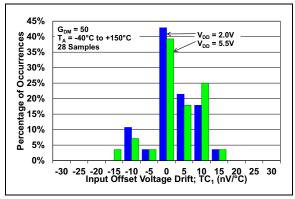

**FIGURE 2-4:** Linear Input Offset Voltage Drift,  $G_{DM} = 20$ .

**FIGURE 2-5:** Linear Input Offset Voltage Drift,  $G_{DM} = 50$ .

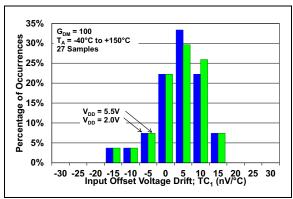

**FIGURE 2-6:** Linear Input Offset Voltage Drift,  $G_{DM} = 100$ .

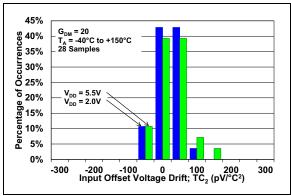

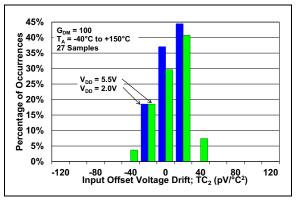

**FIGURE 2-7:** Quadratic Input Offset Voltage Drift,  $G_{DM} = 20$ .

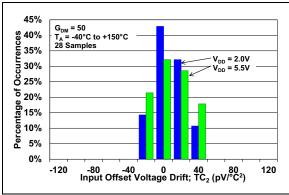

**FIGURE 2-8:** Quadratic Input Offset Voltage Drift,  $G_{DM} = 50$ .

**FIGURE 2-9:** Quadratic Input Offset Voltage Drift,  $G_{DM} = 100$ .

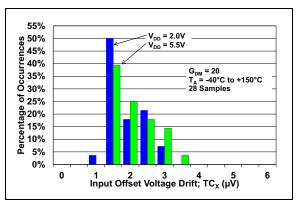

**FIGURE 2-10:** Exponential Input Offset Voltage Drift,  $G_{DM} = 20$ .

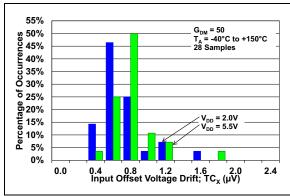

**FIGURE 2-11:** Exponential Input Offset Voltage Drift,  $G_{DM} = 50$ .

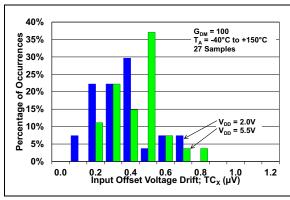

**FIGURE 2-12:** Exponential Input Offset Voltage Drift,  $G_{DM} = 100$ .

**FIGURE 2-13:** Input Offset Voltage vs. Power Supply Voltage, with  $G_{DM} = 20$ .

**FIGURE 2-14:** Input Offset Voltage vs. Power Supply Voltage, with  $G_{DM} = 50$ .

**FIGURE 2-15:** Input Offset Voltage vs. Power Supply Voltage, with  $G_{DM} = 100$ .

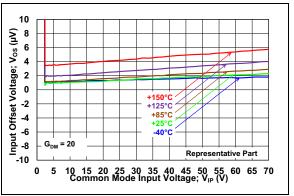

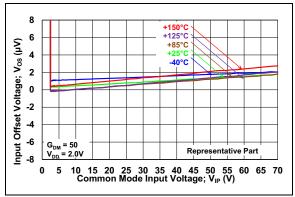

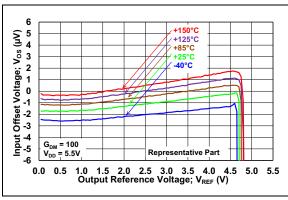

**FIGURE 2-16:** Input Offset Voltage vs. Common-Mode Input Voltage, with  $G_{DM} = 20$ .

**FIGURE 2-17:** Input Offset Voltage vs. Common-Mode Input Voltage, with  $G_{DM} = 50$ .

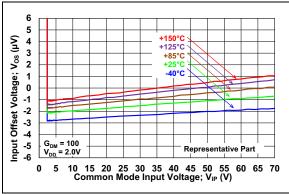

**FIGURE 2-18:** Input Offset Voltage vs. Common-Mode Input Voltage, with  $G_{DM} = 100$ .

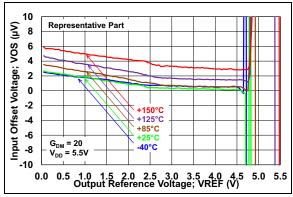

**FIGURE 2-19:** Input Offset Voltage vs. Reference Voltage, with  $G_{DM} = 20$ .

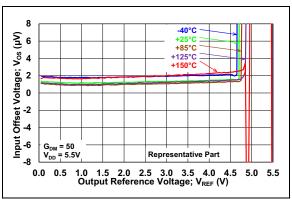

**FIGURE 2-20:** Input Offset Voltage vs. Reference Voltage, with  $G_{DM} = 50$ .

**FIGURE 2-21:** Input Offset Voltage vs. Reference Voltage, with  $G_{DM} = 100$ .

**FIGURE 2-22:** 1/CMRR, with  $G_{DM} = 20$ .

FIGURE 2-23: 1/CMRR, with  $G_{DM} = 50$ .

**FIGURE 2-24:** 1/CMRR, with  $G_{DM} = 100$ .

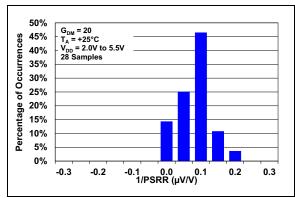

**FIGURE 2-25:** 1/PSRR, with  $G_{DM} = 20$ .

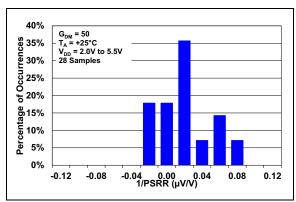

**FIGURE 2-26:** 1/PSRR, with  $G_{DM} = 50$ .

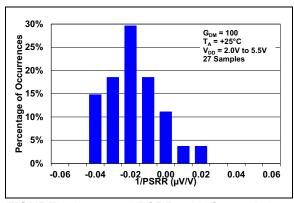

**FIGURE 2-27:** 1/PSRR, with  $G_{DM} = 100$ .

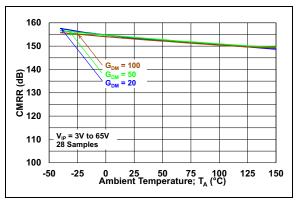

**FIGURE 2-28:** CMRR vs. Ambient Temperature.

**FIGURE 2-29:** PSRR vs. Ambient Temperature.

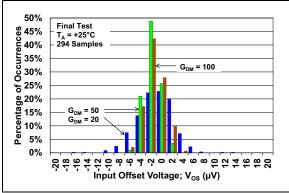

FIGURE 2-30: Input Offset Voltage - Final Test Results.

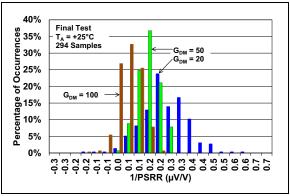

FIGURE 2-31: PSRR - Final Test Results.

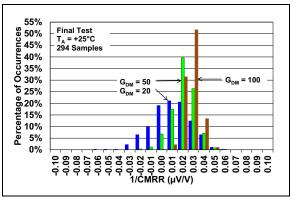

FIGURE 2-32: CMRR - Final Test Results.

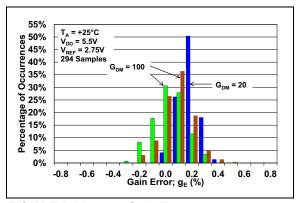

FIGURE 2-33: Gain Error.

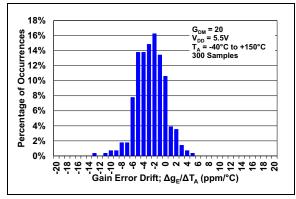

**FIGURE 2-34:** Gain Error Temperature Drift.

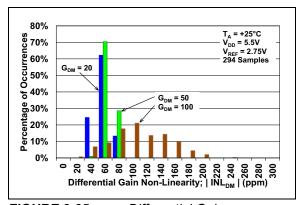

**FIGURE 2-35:** Differential Gain Nonlinearity.

## 2.2 Other DC Voltages and Currents

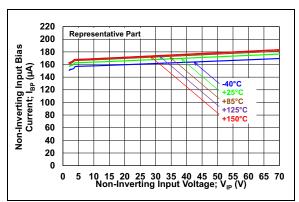

**FIGURE 2-36:**  $V_{IP}$  Pin Input Bias Current vs. Input Common-Mode Voltage.

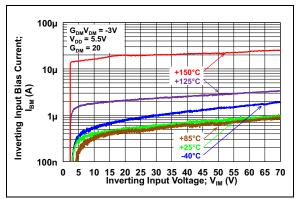

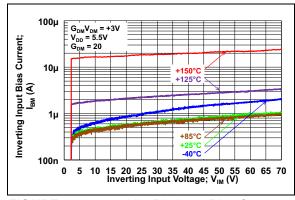

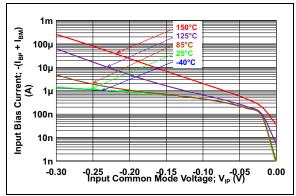

**FIGURE 2-37:**  $V_{IM}$  Pin Input Bias Current vs. Input Common-Mode Voltage,  $V_{DM} = V_{DML}$ .

**FIGURE 2-38:**  $V_{IM}$  Pin Input Bias Current vs. Input Common-Mode Voltage,  $V_{DM} = V_{DMH}$ .

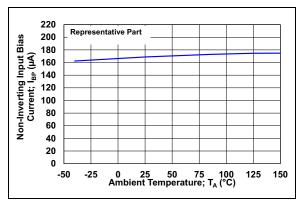

**FIGURE 2-39:**  $V_{IP}$  Pin Input Bias Current vs. Ambient Temperature.

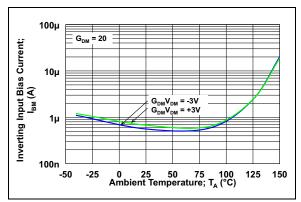

**FIGURE 2-40:**  $V_{IM}$  Pin Input Bias Current vs. Ambient Temperature.

**FIGURE 2-41:**  $V_{IM}$  Pin Input Bias Current vs. Differential Input Voltage.

**FIGURE 2-42:** Input Bias Current vs. Input Common-Mode Voltage (below  $V_{SS}$ ).

**FIGURE 2-43:** Common-Mode Input Range vs. Ambient Temperature.

**FIGURE 2-44:** Reference Voltage Range vs. Ambient Temperature.

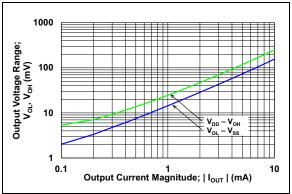

**FIGURE 2-45:** Output Voltage Range vs. Output Current.

**FIGURE 2-46:** Output Voltage Range vs. Ambient Temperature.

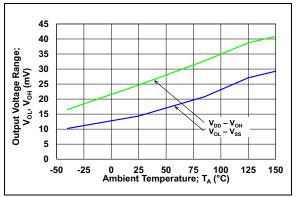

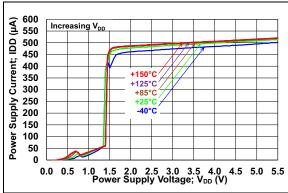

FIGURE 2-47: Supply Current vs. Power Supply Voltage.

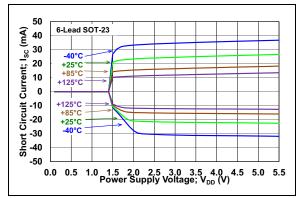

**FIGURE 2-48:** Output Short Circuit Current vs. Power Supply Voltage.

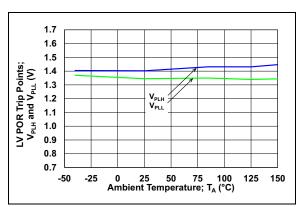

**FIGURE 2-49:** LV POR (for  $V_{DD}$ ) Trip Points vs. Ambient Temperature.

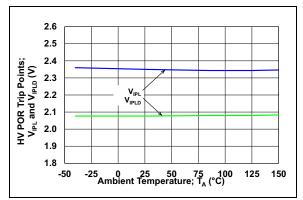

**FIGURE 2-50:** HV POR (for  $V_{IP}$ ) Trip Points vs. Ambient Temperature.

## 2.3 Frequency Response

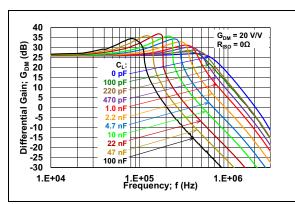

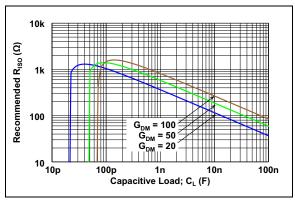

**FIGURE 2-51:** Gain vs. Frequency, with Capacitive Load.

FIGURE 2-52: CMRR vs. Frequency.

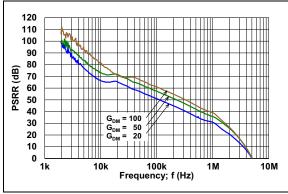

FIGURE 2-53: PSRR vs. Frequency.

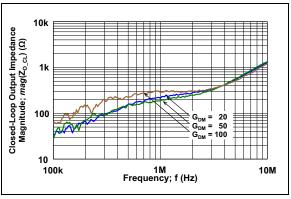

**FIGURE 2-54:** Closed-Loop Output Impedance Magnitude vs. Frequency.

**FIGURE 2-55:** EMI Rejection Ratio vs. Frequency.

**FIGURE 2-56:** EMI Rejection Ratio vs. Signal Strength.

## 2.4 Noise and Intermodulation Distortion

**FIGURE 2-57:** Input Noise Voltage Density vs. Frequency.

FIGURE 2-58: Input Noise Voltage vs. Frequency.

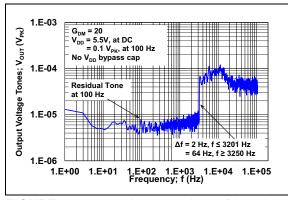

**FIGURE 2-59:** Intermodulation Distortion vs. Frequency, with  $V_{DD}$  Disturbance.

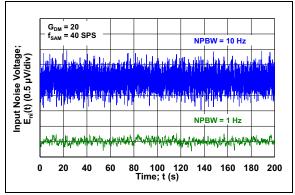

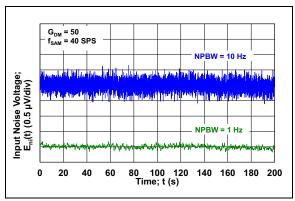

**FIGURE 2-60:** Input Noise Voltage vs. Time,  $G_{DM} = 20$ .

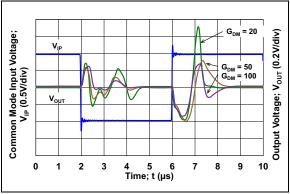

**FIGURE 2-61:** Input Noise Voltage vs. Time,  $G_{DM} = 50$ .

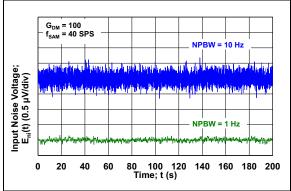

**FIGURE 2-62:** Input Noise Voltage vs. Time,  $G_{DM} = 100$ .

## 2.5 Time Response

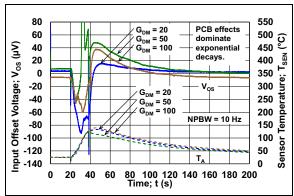

**FIGURE 2-63:** Input Offset Voltage vs. Time, with Temperature Change.

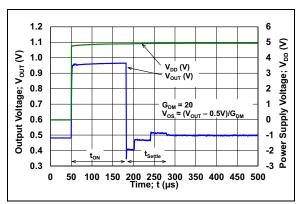

**FIGURE 2-64:** Input Offset Voltage vs. Time, at Power-Up.

**FIGURE 2-65:** The MCP6C02 Shows No Phase Reversal vs. Differential Input Overdrive.

**FIGURE 2-66:** The MCP6C02 Shows No Phase Reversal vs. Input Common-Mode Overdrive.

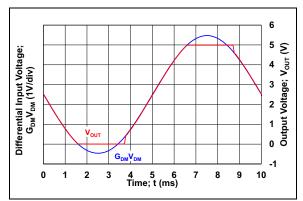

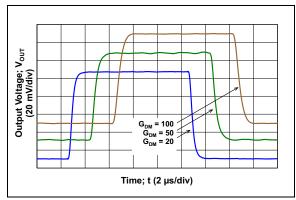

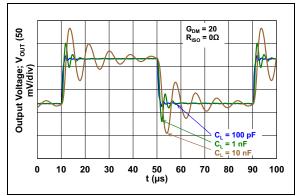

**FIGURE 2-67:** Small Signal Step Response to Differential Input Voltage.

**FIGURE 2-68:** Small Signal Step Response to Common-Mode Input Voltage.

**FIGURE 2-69:** Small Signal Step Response to Differential Input Voltage, with Capacitive Load  $(C_1)$ .

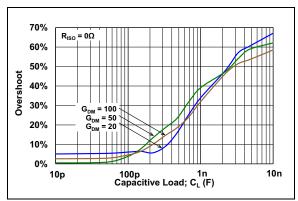

**FIGURE 2-70:** Small Signal Step Response Overshoot, with Capacitive Load  $(C_1)$ .

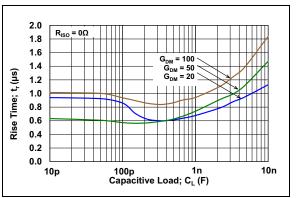

**FIGURE 2-71:** Small Signal Step Response Rise Time, with Capacitive Load  $(C_1)$ .

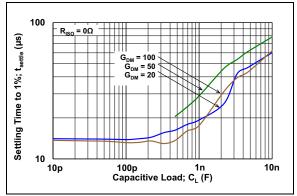

**FIGURE 2-72:** Small Signal Step Response Settling Time, with Capacitive Load  $(C_1)$ .

NOTES:

### 3.0 PIN DESCRIPTIONS

The descriptions of the pins are listed in Table 3-1.

TABLE 3-1: PIN FUNCTION TABLE

| MCP6C02<br>SOT-23 | Symbol           | Description                                                                           |

|-------------------|------------------|---------------------------------------------------------------------------------------|

| 1                 | V <sub>OUT</sub> | Output voltage                                                                        |

| 2                 | $V_{SS}$         | Negative power supply                                                                 |

| 3                 | V <sub>IP</sub>  | Noninverting input (at load's R <sub>SH</sub> ) and positive (high-side) power supply |