## PSoC® Programmable System-on-Chip™

### 特長

- 1つのPSoC®デバイスグループにおいて様々なリソースオプションあり

- 处理能力の高いハーバードアーキテクチャプロセッサ

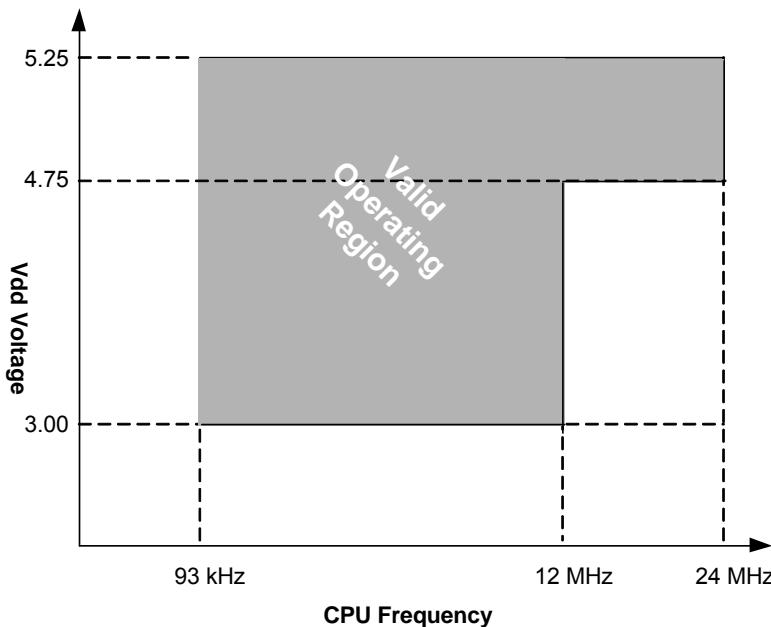

- 最大 24MHz のクロックで動作する M8C プロセッサ

- 8 × 8 乗算、32 ビット加算器

- 高速で低消費電力

- 動作電圧 : 3.0V ~ 5.25V

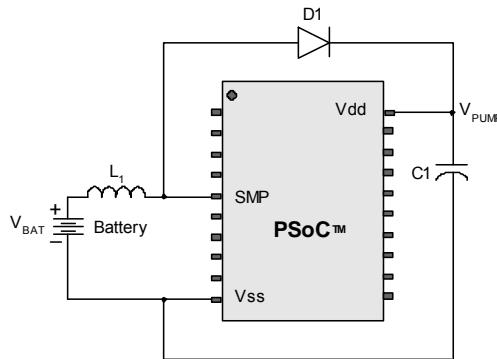

- オンチップスイッチドモードポンプ (SMP) を使用して動作電圧を 1.5V まで低下可能

- 産業用途向け温度範囲 : -40°C ~ +85°C

- 高度で再コンフィギュレーション可能なペリフェラル (PSoC ブロック)

- 最大 12 個の Rail to Rail アナログ PSoC ブロックの特長 :

- 最大 14 ビットの ADC

- 最大 9 ビットの DAC

- プログラム可能なゲインアンプ

- プログラム可能なフィルターとコンパレータ

- 複数の ADC コンフィギュレーション

- 専用の SAR ADC、最大 142ksps でサンプルおよびホールド付き

- 高度な用途向けの最大 4 個の同期型または独立型のデルタシグマ ADC

- 最大 4 個の制約付き Type-E アナログ ブロックの特長 :

- デュアル チャンネルの静電容量センシング機能

- プログラム可能な DAC リファレンスによるコンパレータ

- 最大 10 ビットのシングル スロープ ADC

- 最大 12 個のデジタル PSoC ブロックの特長 :

- 8 ~ 32 ビット タイマーおよびカウンター、8 ビットと 16 ビットのパルス幅変調器 (PWM)

- シフトレジスタ、CRC、PRS モジュール

- 最大 3 個の全二重 UART

- 最大 6 個の半二重 UART

- 複数の可変データ長 SPI™ マスターまたはスレーブ

- すべての GPIO に接続可能

- ブロックの組み合わせで構成する複雑なペリフェラル

- プログラム可能な高精度クロック供給

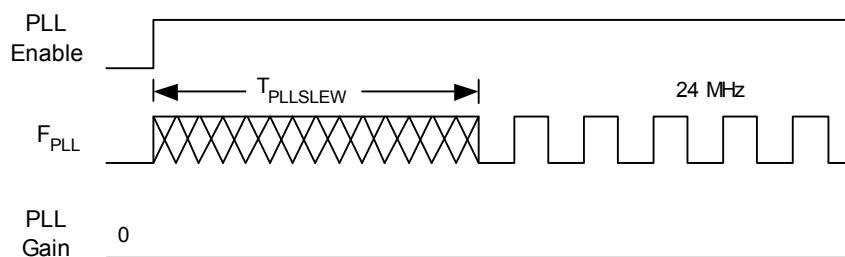

- ±2.5% の精度を持つ 24MHz または 48MHz の内部主振動子

- 高精度オンチップクロック向けの任意の 32.768kHz 水晶振動子

- 任意の最大 24MHz の外部振動子に対応

- ウォッチドッグおよびスリープ機能用の内部低速低消費電力振動子

- 柔軟性のある内蔵メモリ

- 50,000 回の消去と書き込みサイクルが可能な 16KB のフラッシュプログラムストレージ

- 1KB の SRAM データストレージ

- インシステムシリアルプログラミング (ISSP™)

- フラッシュメモリの部分的な書き換えに対応

- 柔軟性のある保護モード

- フラッシュメモリによる EEPROM のエミュレーション

- プログラム可能なピンコンフィギュレーション

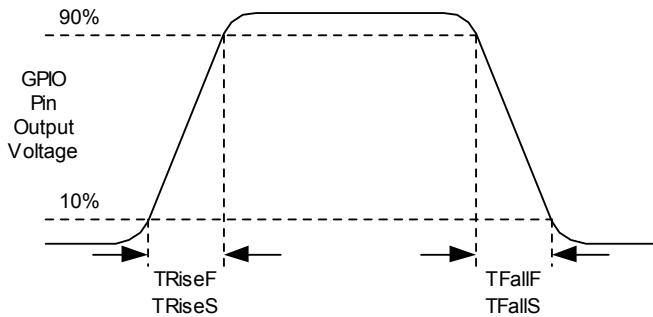

- すべての GPIO で 25mA のシンクと 10mA の駆動能力を実現

- すべての GPIO でプルアップ、プルダウン、High-Z、ストロング、オープンドレインの各駆動モードに対応

- すべての GPIO でアナログ入力に対応

- GPIO で 30mA のアナログ出力を実現

- すべての GPIO でコンフィギュレーション可能な割り込み

- 追加システムリソース

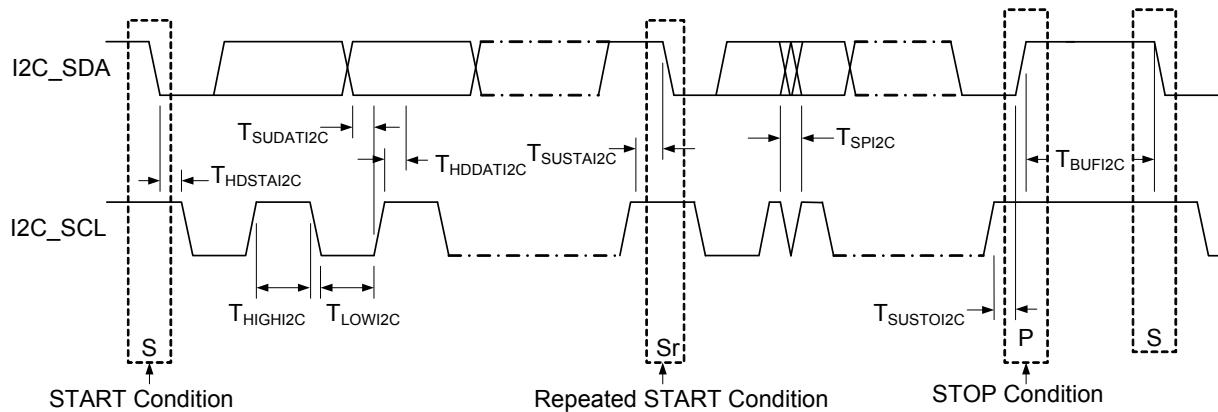

- 最大 2 個のハードウェア I²C リソース

- 各リソースにスレーブ、マスター、またはマルチマスターのモードを実装

- 0 ~ 400kHz で動作

- ウォッチドッグタイマーおよびスリープタイマー

- ユーザーによりコンフィギュレーション可能な低電圧検出

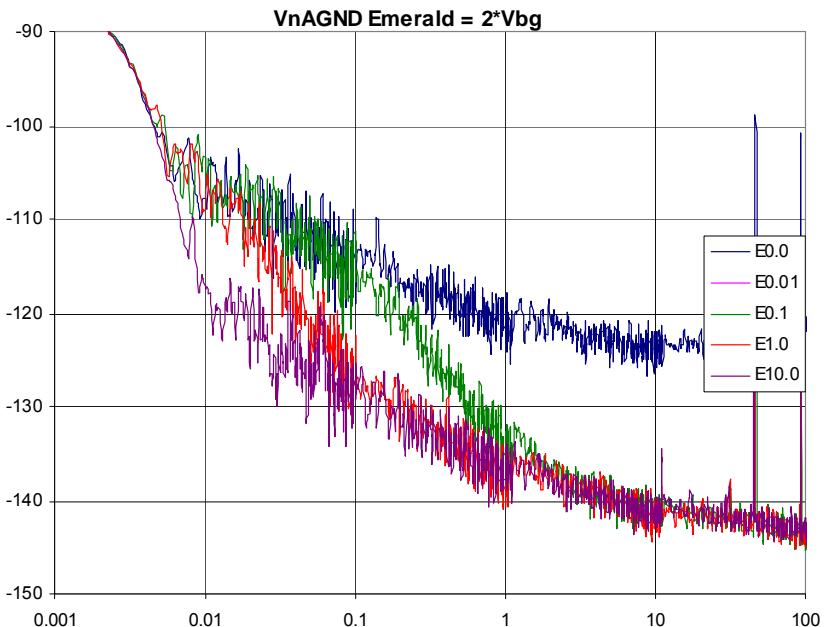

- 柔軟性のある内部リファレンス電圧

- 内蔵の監視回路

- 高精度のオンチップリファレンス電圧

- 完全な開発ツール

- 無償の開発ソフトウェア (PSoC Designer™)

- 必要な機能を網羅したインサーキットエミュレータ、およびプログラマ

- フルスピードのエミュレーション

- 柔軟性のある機能的なブレークポイント構造

- 128KB のトレースメモリ

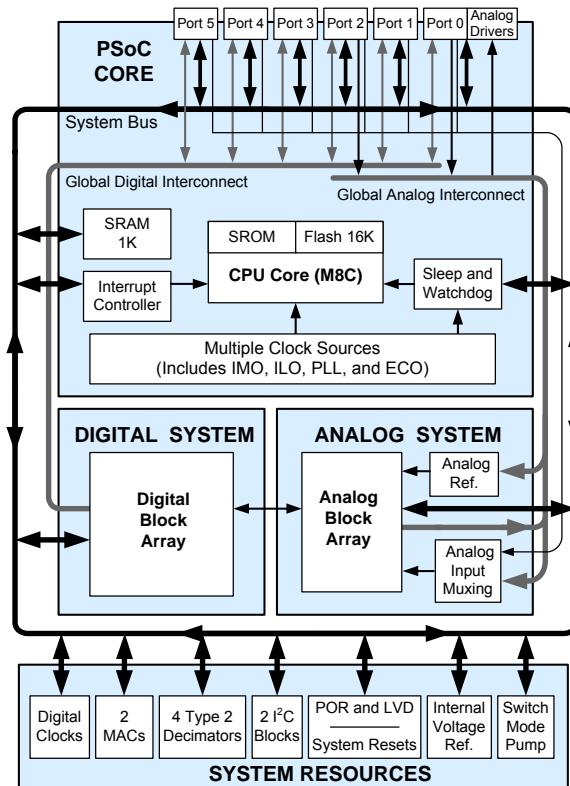

### 論理ブロック図

## 目次

|                             |    |                            |    |

|-----------------------------|----|----------------------------|----|

| <b>詳細情報</b>                 | 3  | 熱インピーダンス                   | 72 |

| <b>PSoC Designer</b>        | 3  | 水晶振動子ピンの静電容量               | 72 |

| <b>PSoC の機能概要</b>           | 4  | はんだリフローの仕様                 | 72 |

| PSoC コア                     | 4  | <b>開発ツールの選択</b>            | 73 |

| デジタル システム                   | 4  | ソフトウェア                     | 73 |

| アナログ システム                   | 5  | 開発キット                      | 73 |

| システム リソース                   | 8  | 評価ツール                      | 73 |

| PSoC デバイスの特性                | 8  | デバイス プログラマ                 | 74 |

| <b>開発ツール</b>                | 10 | アクセサリ (エミュレーションおよびプログラミング) | 74 |

| PSoC Designer ソフトウェア サブシステム | 10 |                            |    |

| <b>PSoC Designer による設計</b>  | 11 | <b>注文情報</b>                | 75 |

| ユーザー モジュールの選択               | 11 | 注文コードの定義                   | 76 |

| ユーザー モジュールをコンフィギュレーション      | 11 | <b>略語</b>                  | 77 |

| 構成および接続                     | 11 | 使用する略語                     | 77 |

| 生成、検証、およびデバッグ               | 11 | <b>参考資料</b>                | 78 |

| <b>ピン配置</b>                 | 12 | <b>本書の表記法</b>              | 79 |

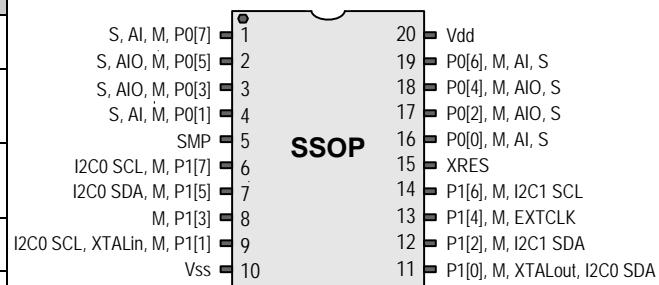

| 20 ピン製品のピン配置                | 12 | 測定単位                       | 79 |

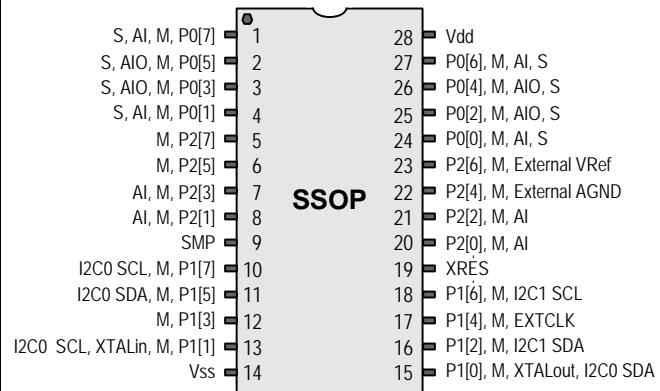

| 28 ピン製品のピン配置                | 13 | 数値の表記                      | 79 |

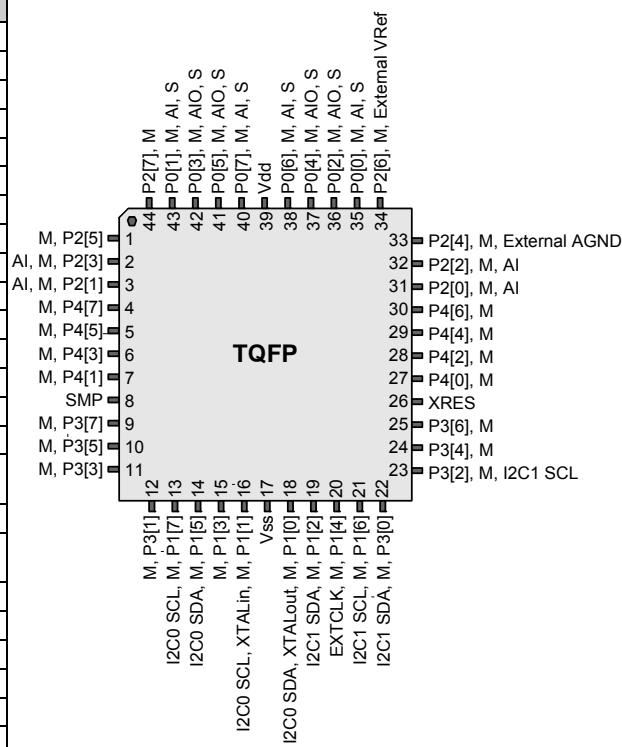

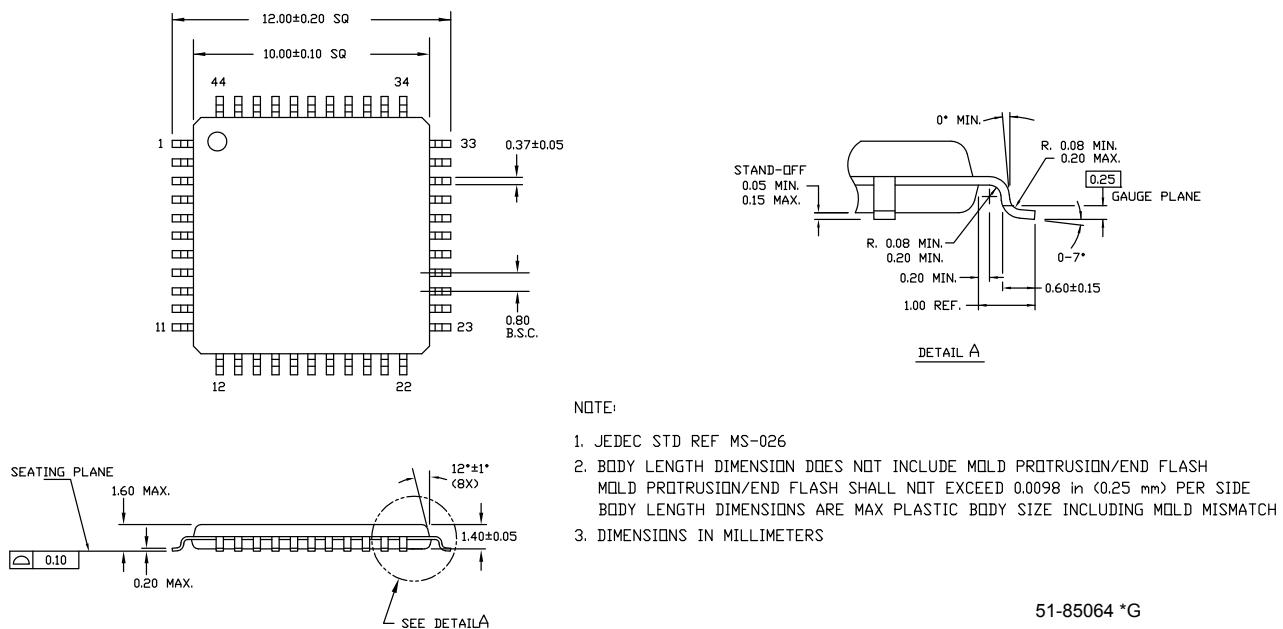

| 44 ピン製品のピン配置                | 14 | <b>用語集</b>                 | 79 |

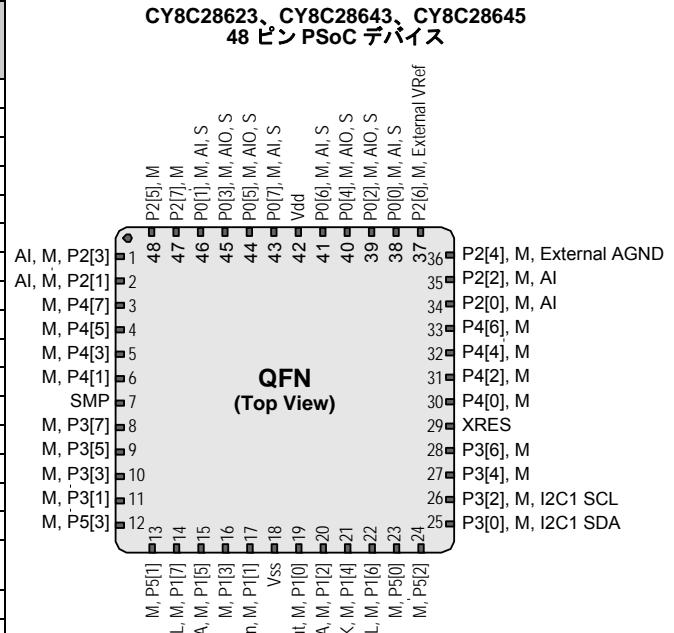

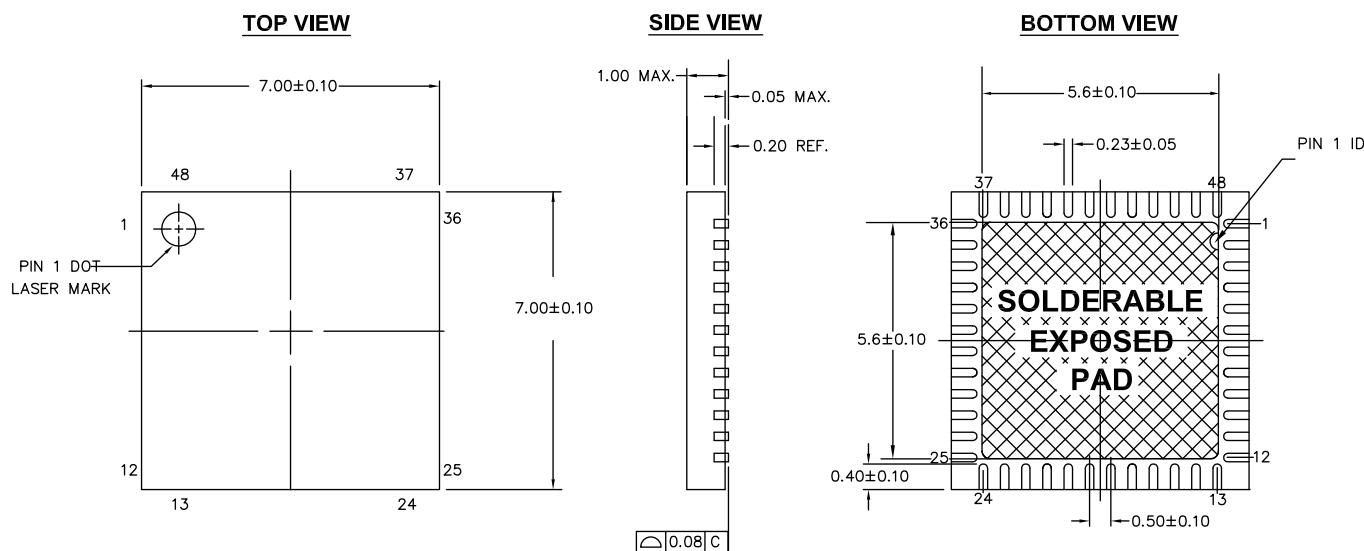

| 48 ピン製品のピン配置                | 15 | <b>エラッタ</b>                | 84 |

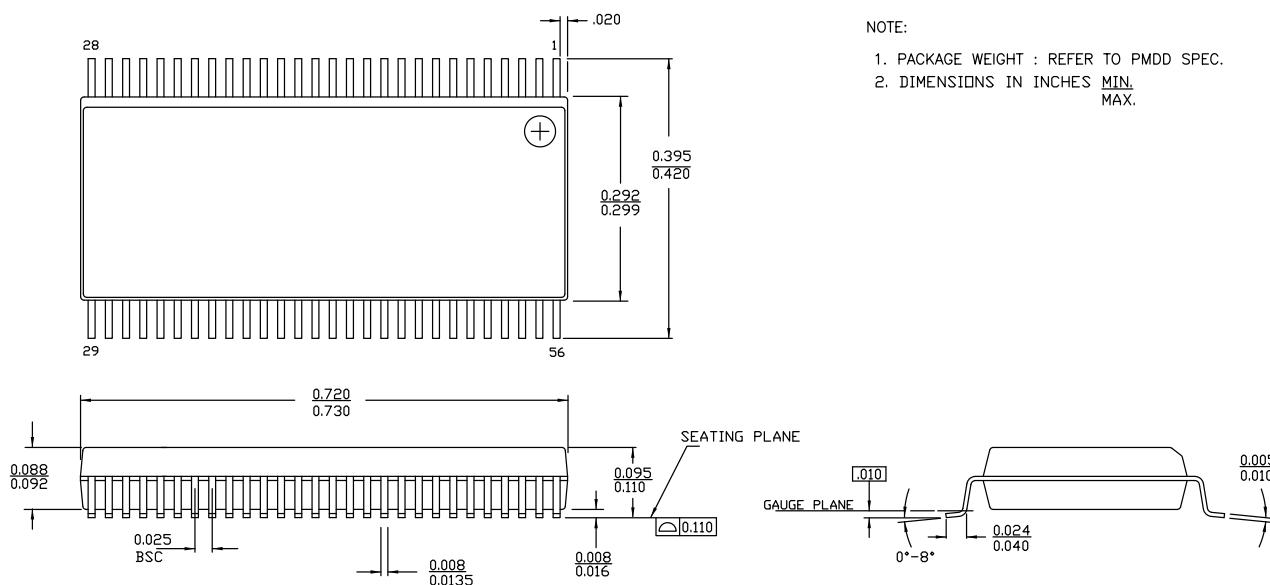

| 56 ピン製品のピン配置                | 16 | 影響を受ける製品番号                 | 84 |

| <b>レジスタ リファレンス</b>          | 18 | 認定状態                       | 84 |

| レジスタの表記法                    | 18 | エラッタのまとめ                   | 84 |

| レジスタ マップ表                   | 18 | <b>改訂履歴</b>                | 86 |

| <b>電気的仕様</b>                | 33 | <b>セールス、ソリューションおよび法律情報</b> | 87 |

| 絶対最大定格                      | 34 | ワールドワイドな販売と設計サポート          | 87 |

| 動作温度                        | 34 | 製品                         | 87 |

| DC 電気的特性                    | 35 | PSoC® ソリューション              | 87 |

| AC 電気的特性                    | 55 | サイプレス開発者コミュニティ             | 87 |

| <b>パッケージ情報</b>              | 68 | テクニカル サポート                 | 87 |

| パッケージの寸法                    | 68 |                            |    |

## 詳細情報

サイプレスは、[www.cypress.com](http://www.cypress.com) に大量のデータを掲載しており、ユーザーがデザインに適切な PSoC デバイスを選択し、デバイスをデザインに迅速で効果的に統合する手助けをしています。リソースの総合リストについては、知識ベース記事「[How to Design with PSoC® 1, PowerPSoC®, and PLC – KBA88292](#)」を参照してください。以下は PSoC 1 の要約です。

- **概要** : PSoC ポートフォリオ、PSoC ロードマップ

- **製品セレクタ** : [PSoC 1](#)、[PSoC 3](#)、[PSoC 4](#)、[PSoC 5LP](#)

- さらに、PSoC Designer にはデバイス選択ツールが含まれています。

- **アプリケーションノート** : サイプレスは、基本レベルから高度なレベルまでの様々なトピックに触れる大量の PSoC アプリケーションノートを提供しています。以下は PSoC 1 入門用の推薦アプリケーションノートです。

- [Getting Started with PSoC® 1 – AN75320](#)

- [PSoC® 1 - Getting Started with GPIO – AN2094](#)

- [PSoC® 1 Analog Structure and Configuration – AN74170](#)

- [PSoC® 1 Switched Capacitor Analog Blocks – AN2041](#)

- [Selecting Analog Ground and Reference – AN2219](#)

- 注: CY8C28xxx デバイスに関するアプリケーションノートについては、[ここ](#)をクリックしてください。

- **開発キット** :

- [CY3210-PSoCEval1](#) は、CY8C25/26xxx デバイスを除いて、車載用デバイスを含むすべての PSoC 1 混在信号アレイファミリに対応しています。このキットには、LCD モジュールやポテンショメーター、LED、ブレッドボードが含まれています。

- [CY3214-PSoCEvalUSB](#) は、CY8C24x94 PSoC デバイスの開発用基板を備えています。この基板の特殊な特長には、USB および CapSense 開発とデバッグ サポートが含まれています。

- 注: CY8C28xxx デバイスに関する開発キットについては、[ここ](#)をクリックしてください。

[MiniProg1](#) および [MiniProg3](#) デバイスは、フラッシュ メモリのプログラミングとデバッグ用のインターフェースを提供します。

## PSoC Designer

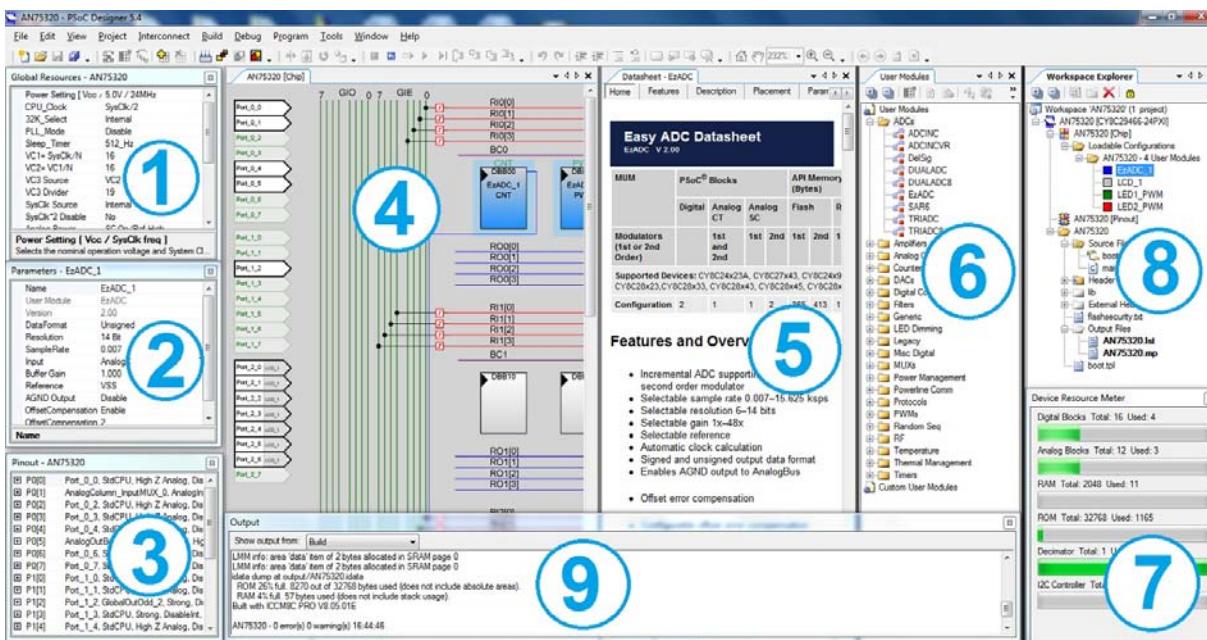

PSoC Designer は無償の Windows ベースの統合設計環境 (IDE) です。アプリケーション開発は、ドラッグ & ドロップの設計環境で特性化済みのアナログおよびデジタル ペリフェラルのライブラリを使用して行われます。また、API ライブラリの動的生成が行えるコードを活用して、設計をカスタマイズすることも可能です。図 1 に PSoC Designer ウィンドウを示します。注: これはデフォルト画面ではありません。

1. **グローバル リソース** –すべてのデバイス ハードウェアの設定

2. **パラメーター** – 選択したユーザー モジュールのパラメーター

3. **ピン配置** – デバイスのピンに関する情報

4. **チップ レベル エディター** – 選択したチップで使用可能リソースの図

5. **データシート** – 選択したユーザー モジュールのデータシート

6. **ユーザー モジュール** – 選択したデバイスのすべての使用可能なユーザー モジュール

7. **デバイス リソース メーター** – 現時点のプロジェクトのコンフィギュレーション用のデバイス リソースの使用率

8. **ワークスペース** – ツリー レベル図で表示されるプロジェクトに関するファイル

9. **出力** – プロジェクト ビルドおよびデバッグ処理からの出力

- 注: PSoC Designer の詳細情報については、[PSoC® Designer > Help > Documentation > Designer Specific Documents > IDE User Guide](#) を順に選択して情報をご覧ください。

図 1. PSoC Designer のレイアウト

## PSoC の機能概要

PSoC ファミリは、オンチップコントローラーを備えた多くのデバイスから成ります。これらのデバイスは、従来の複数の MCU ベースシステム部品を低成本でプログラマブルなシングルチップで置き換えることを目的としています。PSoC デバイスは、コンフィギュレーション可能なアナログ ブロックとデジタル ブロックおよび相互接続を備えています。このアーキテクチャによって、個々のアプリケーションの要件に合わせたペリフェラル コンフィギュレーションのカスタマイズが可能となります。さらに、高速 CPU、フラッシュ プログラム メモリ、SRAM データ メモリ、およびコンフィギュレーション可能な I/O が、幅広い便利なピン配置とパッケージで提供されています。

本データシートで説明する CY8C28xxx グループの PSoC デバイスでは、複数のリソース コンフィギュレーション オプションが使用可能です。したがって、本データシートで説明するリソースはすべて CY8C28xxx サブグループで使用可能とはなりません。CY8C28x45 サブグループは、ここで説明するすべてのリソースの機能セットをすべて備えています。さらに 6 つの細分化したグループがあり、特定の用途に必要なリソースと機能のみを持つデバイスを設計段階で使用できます。CY8C28xxx の各サブ グループで使用可能なリソースについては、[9 ページの表 2](#) を参照してください。同様の情報は[注文情報](#)でも詳しく説明します。

論理ブロック図に示すように、この PSoC デバイスファミリのアーキテクチャは 4 つの主要な領域で構成されます：PSoC コア、デジタルシステム、アナログシステム、システムリソース。コンフィギュレーション可能なグローバル バスにより、すべてのデバイス リソースを組み合わせて完全なカスタム システムを構築できます。PSoC CY8C28xxx ファミリでは、グローバル デジタルとアナログの相互接続に接続する最大 6 個の I/O ポートが用意されており、最大 12 個のデジタル ブロックと最大 16 個のアナログ ブロックへのアクセスが可能です。

## PSoC コア

PSoC コアは充実した機能セットを持つ高性能なエンジンです。このコアは CPU、メモリ、クロック、およびコンフィギュレーション可能な汎用 I/O (GPIO) を備えています。M8C CPU コアは最高 24MHz で動作する高性能プロセッサで、4MIPS 性能を持つ 8 ビットハーバード アーキテクチャのマイクロコントローラーを内蔵しています。

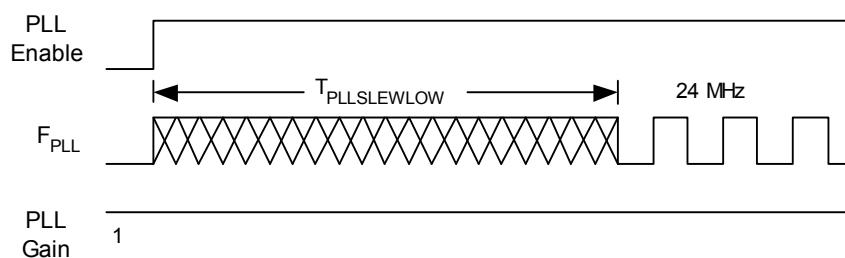

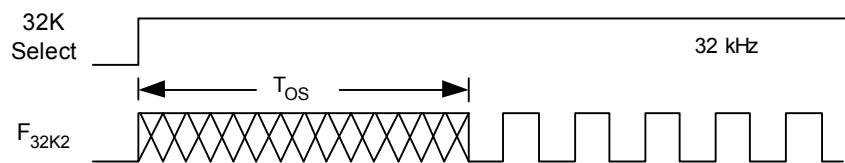

メモリは、プログラムストレージ用の 16K バイト フラッシュと、データストレージ用の 1K バイト SRAM です。PSoC デバイスは、柔軟性のある各種内部クロック ジェネレータを備えています。ジェネレータの一つは、広い範囲の温度と電圧にわたって  $\pm 2.5\%$  の精度を発揮する 24MHz 内部主振動子 (IMO) です。スリープ タイマーおよびウォッチドッグ タイマー (WDT) 用に低消費電力の 32kHz 内部低速振動子 (ILO) が用意されています。32.768kHz の外部水晶振動子 (ECO) をリアルタイムクロック (RTC) として使用できるほか、必要に応じ、PLL を使用して水晶精度の高い 24MHz システムクロックを生成できます。

PSoC の GPIO は、CPU への接続、およびデジタルリソースとアナログリソースへの接続を提供します。各ピンの駆動モードは 8 つのオプションから選択でき、外部とのインターフェースを非常に柔軟に設定できます。また各ピンには、HIGH レベル、LOW レベル、および前回読み出し時からの変化に基づいてシステム割り込みを発生する機能もあります。

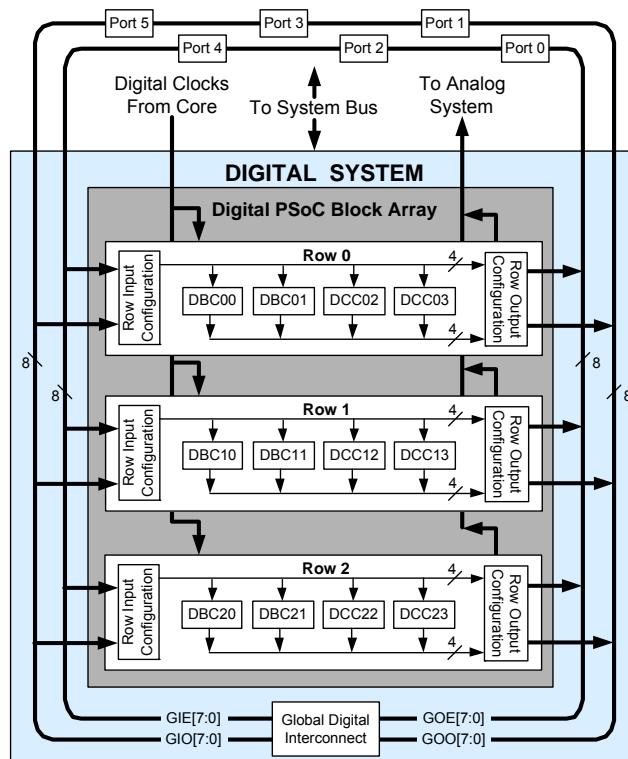

## デジタルシステム

デジタルシステムは、最大 12 個のコンフィギュレーション可能なデジタル PSoC ブロックから構成されます。各ブロックは 8 ビットのリソースであり、単独で使用できるほか、他のブロックと組み合わせ、ユーザー モジュールという 8 ビット、16 ビット

### 注

1. CY8C28x52 デバイスには、デジタル ブロック行 2 がありません。このデバイスには 2 本のデジタル行があり、デジタル ブロックは合計で 8 個です。

ト、24 ビット、および 32 ビットのペリフェラルを構成することができます。任意のピンに任意の信号を送ることができます。グローバル バスを介して、どの GPIO にもデジタル ブロックを接続できます。

図 2. デジタルシステムのブロック図<sup>[1]</sup>

デジタル ペリフェラルのコンフィギュレーションには次のようなものがあります。

- PWM (8 ビット、16 ビット、ワンショットおよびマルチショット機能)

- デッドバンドとキル機能を備えた PWM (8 ビット、16 ビット)

- カウンター (8 ~ 32 ビット)

- タイマー (8 ~ 32 ビット)

- 選択可能なパリティを備えた全二重 8 ビット UART (最大 3 個)

- 選択可能なパリティを備えた半二重 8 ビット UART (最大 6 個)

- 可変長の SPI スレーブおよび SPI マスター

- 最大で合計 6 個のスレーブおよびマスター (8 ビット)

- 8 ~ 16 ビット演算のサポート

- I<sup>2</sup>C にスレーブ、マスター、またはマルチマスター (システムリソースとして最大 2 個が可能)

- IrDA (最大 3 個)

- 疑似乱数列発生器 (8 ~ 32 ビット)

- CRC チェッカー/ジェネレータ (16 ビット)

- シフト レジスタ (2 ~ 32 ビット)

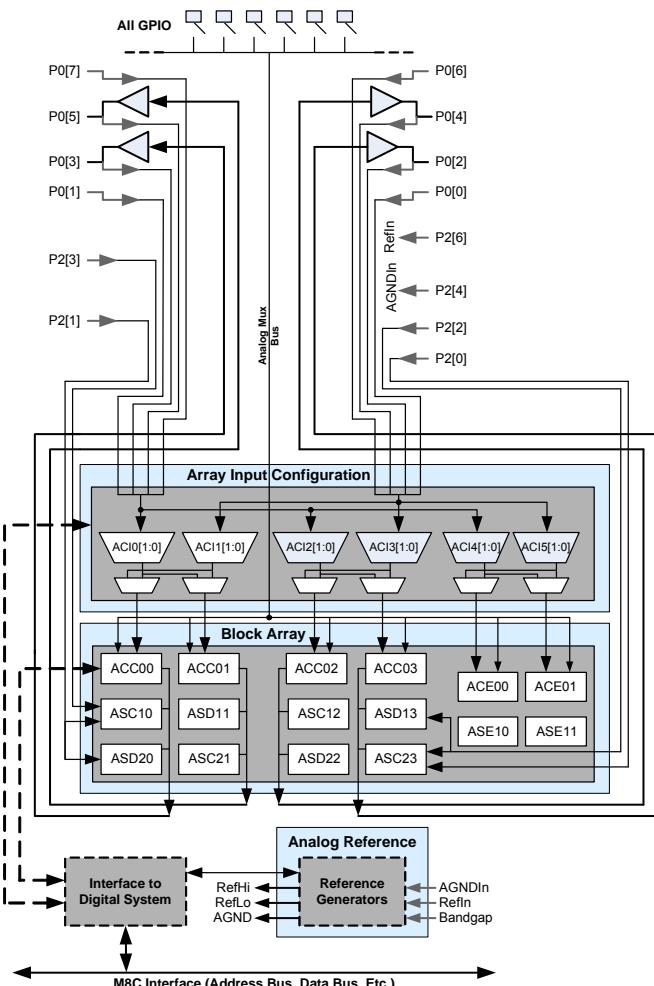

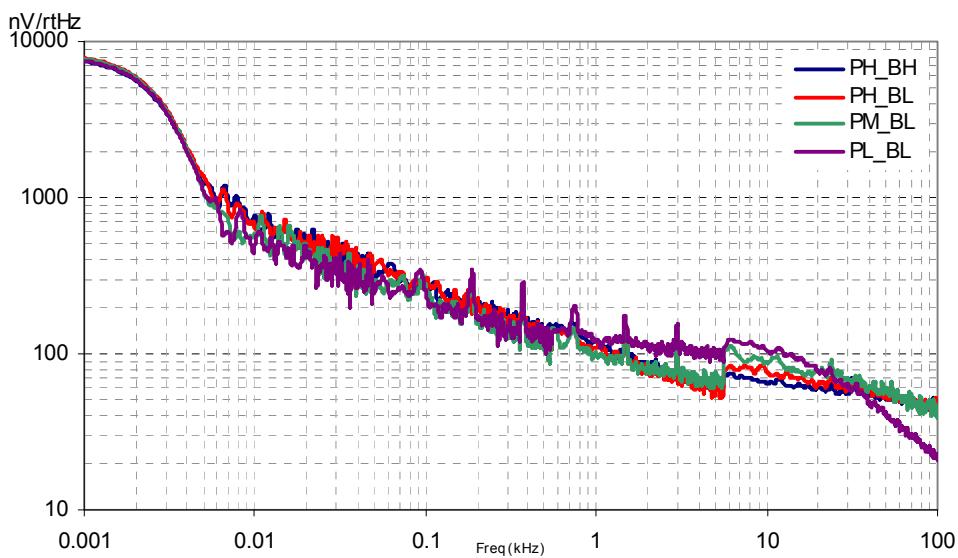

## アナログ システム

アナログ システムは最大 16 個のコンフィギュレーション可能なアナログ ブロックで構成されます。アナログ ブロックごとにオペアンプ回路を持っており、複雑なアナログ信号フローを構築できます。この PSoC ファミリのデバイスの中には、どの GPIO ピンにも接続可能なアナログマルチブレクサバスを持つものがあります。このバスをアナログ システムに接続し、コンパレータおよびアナログ - デジタル変換器による解析を行うこともできます。このバスを 2 個のセクションに分割してデュアル チャネルの同時処理が可能です。

一般的な PSoC アナログ機能として、以下のものがあります（ほとんどはユーザー モジュールとして提供されます）。

- アナログ-デジタル変換器（6～14 ビットの分解能で最大4個。インクリメンタルまたはデルタ シグマを選択可能）

- 専用の 10 ビット SAR ADC。サンプリング速度最大 142ksps

- 同期型同時サンプリング デルタ シグマ ADC（最大 4 個）

- フィルター（2～8 ポールのバンドパス、ローパス、およびノットチ）

- アンプ（最大 4 個、48x までのゲインを選択可能）

- 計装用アンプ（最大 2 個、93x までのゲインを選択可能）

- コンパレータ（最大 6 個、16 の閾値を選択可能）

- DAC（最大 4 個、6～9 ビットの分解能）

- 乗算型 DAC（最大 4 個、6～9 ビットの分解能）

- 大電流出力ドライバー（30mA 駆動能力で最大 4 個）

- 1.3V リファレンス電圧（システム リソースとして可能）

- DTMF ダイヤラー

- 変調器

- 相関器

- ピーク検出器

- 他に多数のトポロジが可能

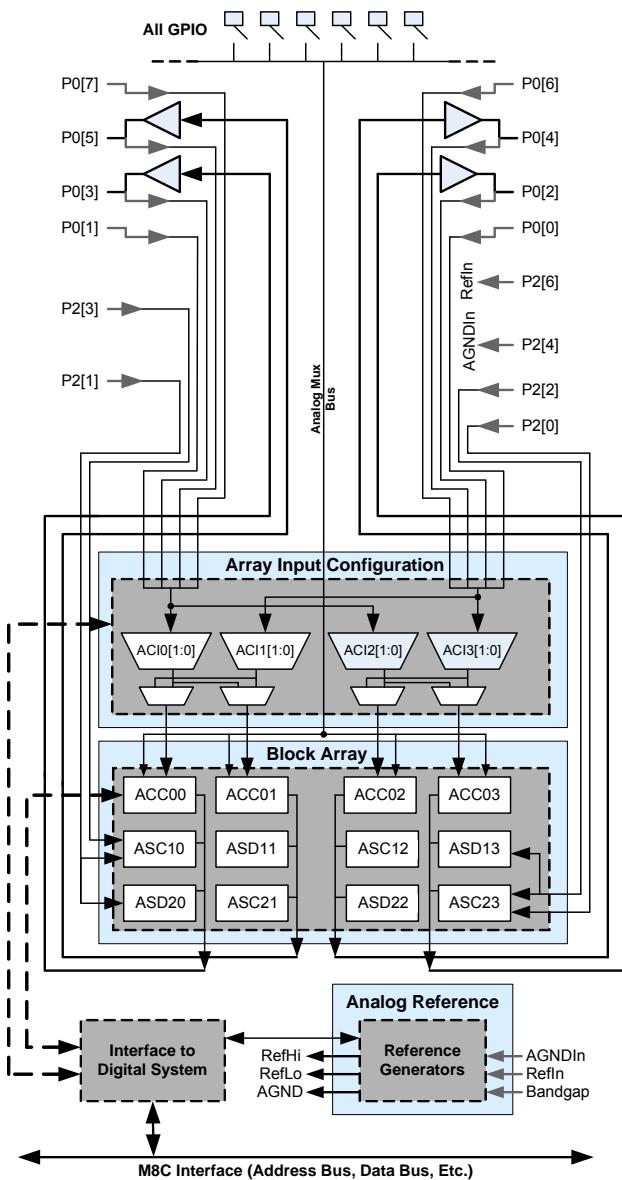

図 3. CY8C28x45 デバイスおよび CY8C28x52 デバイスのアナログ システム ブロック図

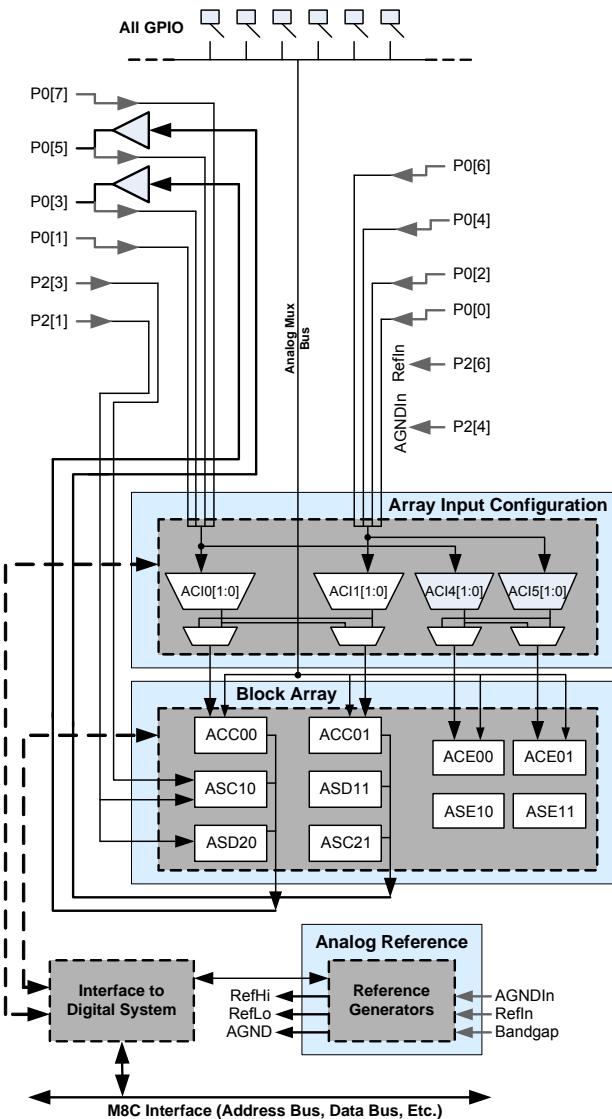

図4. CY8C28x43 デバイスのアナログ システム ブロック図

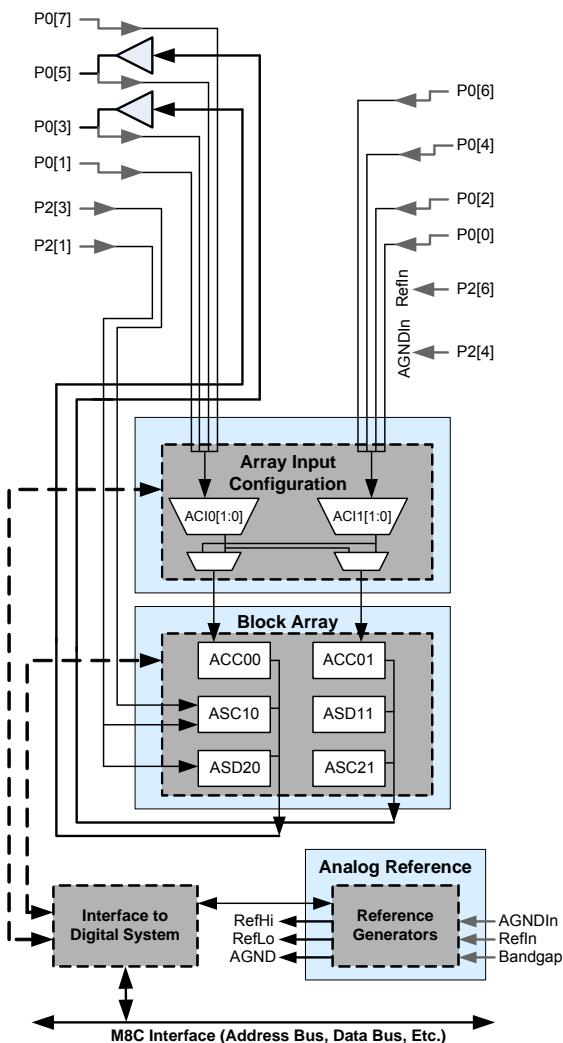

図5. CY8C28x33 デバイスのアナログ システム ブロック図

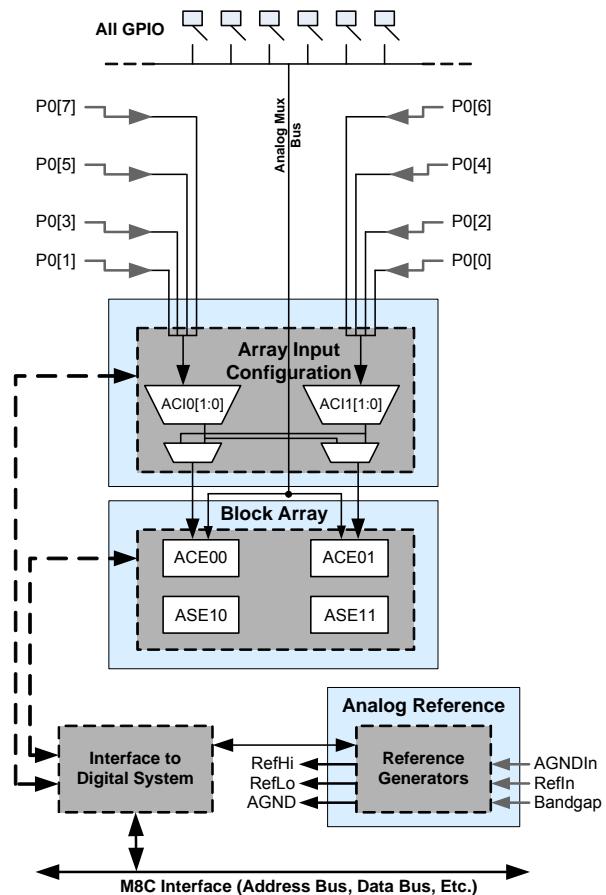

**図6. CY8C28x23 デバイスのアナログ システム ブロック図**

**図7. CY8C28x13 デバイスのアナログ システム ブロック図**

## システム リソース

システム リソースは、システムの構築に効果的な追加機能を提供します。一部のシステム リソースについては前の節でリストアップしました。この他の追加リソースとして、乗算器、複数のデシメータ、スイッチ モード ポンプ、低電圧検出、パワー オン リセットなどがあります。ここでは、各システム リソースの利点について説明します。

- デジタル クロック分周器は、各種用途向けにカスタマイズ可能な 3 種類のクロック周波数を提供します。このクロックは、デジタルとアナログ両方のシステムで使用できます。デジタル PSOC ブロックをクロック分周器として使用することで、さらに別のクロックを生成できます。

- 積和演算器 (MAC) は、高速 8 ビット乗算器および 32 ビット加算器から成り、一般的な数学演算とデジタル フィルターの実行に使用すると効果的です。

## PSoC デバイスの特性

PSoC デバイスの特性に応じて、デジタル システムとアナログ システムは 16 個、8 個、または 4 個のデジタル ブロックと 12 個、6 個、または 4 個のアナログ ブロックを持つことができます。表 1 は、特定の PSoC デバイス グループで使用可能なリソースの一覧を示します。本データ シートで説明されている PSoC デバイスはこの表でグレーの背景で表示されています。

表 1. PSoC デバイスの特性

| PSoC 製品番号  | デジタル I/O 数 | デジタル 行数 | デジタル ブロック数 | アナログ 入力数 | アナログ 出力数 | アナログ カラム数 | アナログ ブロック数                  | SRAM サイズ | フラッシュ メモリサイズ |

|------------|------------|---------|------------|----------|----------|-----------|-----------------------------|----------|--------------|

| CY8C29x66  | 最大 64      | 4       | 16         | 最大 12    | 4        | 4         | 12                          | 2K       | 32K          |

| CY8C28xxx  | 最大 44      | 最大 3    | 最大 12      | 最大 44    | 最大 4     | 最大 6      | 最大<br>12 + 4 <sup>[2]</sup> | 1K       | 16K          |

| CY8C27x43  | 最大 44      | 2       | 8          | 最大 12    | 4        | 4         |                             | 256      | 16K          |

| CY8C24x94  | 最大 56      | 1       | 4          | 最大 48    | 2        | 2         | 6                           | 1K       | 16K          |

| CY8C24x23A | 最大 24      | 1       | 4          | 最大 12    | 2        | 2         | 6                           | 256      | 4K           |

| CY8C23x33  | 最大 26      | 1       | 4          | 最大 12    | 2        | 2         | 4                           | 256      | 8K           |

| CY8C22x45  | 最大 38      | 2       | 8          | 最大 38    | 0        | 4         | 6 <sup>[2]</sup>            | 1K       | 16K          |

| CY8C21x45  | 最大 24      | 1       | 4          | 最大 24    | 0        | 4         | 6 <sup>[2]</sup>            | 512      | 8K           |

| CY8C21x34  | 最大 28      | 1       | 4          | 最大 28    | 0        | 2         | 4 <sup>[2]</sup>            | 512      | 8K           |

| CY8C21x23  | 最大 16      | 1       | 4          | 最大 8     | 0        | 2         | 4 <sup>[2]</sup>            | 256      | 4K           |

| CY8C20x34  | 最大 28      | 0       | 0          | 最大 28    | 0        | 0         | 3 <sup>[2, 3]</sup>         | 512      | 8K           |

| CY8C20xx6  | 最大 36      | 0       | 0          | 最大 36    | 0        | 0         | 3 <sup>[2, 3]</sup>         | 最大 2K    | 最大 32K       |

### 注

- アナログ機能に制約あり。

- 2 個のアナログ ブロックと 1 個の CapSense®。

本データシートの対象となっているすべてのデバイスは、アーキテクチャ、仕様、および定格が同一です。ただし、ハードウェアリソースの中には、グループ内のデバイスによって数量が異なるものもあります。次の表に、このデータシートの対象となっている各デバイス サブグループで使用可能なリソース数を示します。

**表 2. CY8C28xxx デバイスの特性**

| PSoC 製品番号 | CapSense | デジタル ブロック数 | 通常 アナログ ブロック数 | 制約付き アナログ ブロック数 | HW I <sup>2</sup> C 数 | デシメータ数 | デジタル I/O 数 | アナログ 入力数 | アナログ 出力数 | アナログ マルチプレクサ バス数 |

|-----------|----------|------------|---------------|-----------------|-----------------------|--------|------------|----------|----------|------------------|

| CY8C28x03 | 無        | 12         | 0             | 0               | 2                     | 0      | 最大 24      | 最大 8     | 0        | 0                |

| CY8C28x13 | 有        | 12         | 0             | 4               | 1                     | 2      | 最大 40      | 最大 40    | 0        | 2                |

| CY8C28x23 | 無        | 12         | 6             | 0               | 2                     | 2      | 最大 44      | 最大 10    | 2        | 0                |

| CY8C28x33 | 有        | 12         | 6             | 4               | 1                     | 4      | 最大 40      | 最大 40    | 2        | 2                |

| CY8C28x43 | 無        | 12         | 12            | 0               | 2                     | 4      | 最大 44      | 最大 44    | 4        | 2                |

| CY8C28x45 | 有        | 12         | 12            | 4               | 2                     | 4      | 最大 44      | 最大 44    | 4        | 2                |

| CY8C28x52 | 有        | 8          | 12            | 4               | 1                     | 4      | 最大 24      | 最大 24    | 4        | 2                |

## 開発ツール

PSoC Designer™ は画期的な統合設計環境 (IDE) であり、特定のアプリケーション要件を満たすよう PSoC をカスタマイズすることが可能になります。PSoC Designer ソフトウェアは、システム設計や市場投入までの時間を早めるお手伝いをいたします。ユーザー モジュールと呼ばれる予め用意されたアナログ ペリフェラルやデジタル ペリフェラルのライブラリを、ドラッグ & ドロップによる設計環境内で利用して独自のアプリケーションを開発できます。また、動的に生成されるアプリケーションプログラミング インターフェース (API) のコード ライブラリを活用しながら、設計をカスタマイズすることも可能です。そして、設計のデバッグおよびテストは、回路内エミュレーションや標準ソフトウェア デバッグ機能などを備えた統合デバッグ環境で行います。PSoC Designer には以下が含まれます。

- デバイス、ユーザー モジュール コンフィギュレーションおよびダイナミック リコンフィギュレーション向けのアプリケーション エディター グラフィカル ユーザー インターフェース (GUI)

### ■ 広範なユーザー モジュール カタログ

- 統合ソース コード エディター (C およびアセンブリ言語)

- サイズ制限や使用期限のない無償の C コンパイラ

### ■ 内蔵デバッガ

### ■ インサーキット エミュレータ

- 通信インターフェースの組み込みサポート機能は以下の通りです。

- ハードウェアおよびソフトウェア I<sup>2</sup>C スレーブとマスター

- フルスピード USB 2.0

- 最大 4 個の全二重汎用非同期レシーバー／トランスマッター (UART)、SPI マスターと SPI スレーブ、およびワイヤレス

PSoC Designer は、PSoC 1 デバイスの全ライブラリをサポートしており、Windows XP、Windows Vista、Windows 7 上で動作します。

## PSoC Designer ソフトウェア サブシステム

### デザイン エントリ

まず、チップレベル ビューで対象の基本デバイスを選択します。次に、PSoC ブロックを使用するアナログとデジタルの各種オンボードコンポーネント (ユーザー モジュール) を選択します。ユーザー モジュールの例として、アナログ - デジタル変換器 (ADC)、デジタル - アナログ変換器 (DAC)、アンプ、フィルターがあります。選択したアプリケーション向けにユーザー モジュールをコンフィギュレーションし、他のユーザー モジュールや適切なピンに接続します。その後、プロジェクトを生成します。それにより、アプリケーションのプログラミングに使用できる API とライブラリがプロジェクトに事前設定されます。

またこのツールを使用すると、マルチ コンフィギュレーションやダイナミック リコンフィギュレーション開発が容易になります。ダイナミック リコンフィギュレーションにより、実行中にコンフィギュレーションを変更できます。基本的に、この機能によって、1 つのアプリケーションで 100% 以上の PSoC リソースを使用することができます。

### コード生成ツール

コード生成ツールは、PSoC Designer のインターフェースでシームレスに動作し、さまざまなデバッグ ツールでテスト済みです。C 言語、アセンブリ言語、または両方の組み合わせで設計を開発できます。

**アセンブリ**：アセンブリでは、アセンブリ コードを C コードとシームレスに組み合わせることができます。リンク ライブラリでは、自動的に絶対アドレス指定を使用できるほか、相対モードでコンパイルしたうえで他のソフトウェア モジュールとリンクし、絶対アドレス指定を取得することもできます。

**C 言語コンパイラ**：PSoC ファミリのデバイスをサポートする C 言語コンパイラを利用できます。これらの製品を使用することで、PSoC ファミリ デバイス向けに完成した C プログラムを作成できます。これらの最適化 C コンパイラは、PSoC のアーキテクチャに合わせて設定した C 言語のすべての機能を提供します。コンパイラには、ポートとバスの動作、標準のキーパッドとディスプレイのサポート、および拡張演算機能を提供する組み込みライブラリが付属しています。

### デバッガ

PSoC Designer はハードウェアによる回路内のエミュレーション機能を提供するデバッグ環境を備えており、PSoC デバイスの内部状態を観察しながら実システムでプログラムに対してテストを行うことができます。デバッガ コマンドを使用して、データ メモリの読み出しとプログラム、データ メモリの読み書き、I/O レジスタの読み書きが可能です。また、CPU レジスターの読み書き、ブレークポイントの設定と消去、プログラムの実行、停止、およびステップ制御が可能です。また、調査対象のレジスタとメモリ位置のトレース バッファをデバッガで作成することもできます。

### オンライン ヘルプ システム

オンライン ヘルプ システムでは、オンラインで状況に応じたヘルプが表示されます。それぞれの機能のサブシステムには固有状況に応じたヘルプがあり、操作手順のヘルプやクイック リファレンスとして使用できます。また、このヘルプ システムは設計者を支援するためのチュートリアル、FAQ とオンライン サポート フォーラムへのリンクを提供しています。

### インサーキット エミュレータ

コストの低く、機能性の高いインサーキット エミュレータ (ICE) が開発作業をサポートするために用意されています。このハードウェアは単独のデバイスをプログラムできます。

エミュレータは、USB ポートを介して PC に接続する 1 つの基本ユニットで構成されています。この基本ユニットは汎用型で、すべての PSoC デバイスで動作します。各デバイス ファミリのエミュレーション ポッドは、それぞれ別々に用意されています。エミュレーション ポッドは、作業対象の基板上の PSoC デバイスと置き換わり、全速 (24MHz) で動作します。

## PSoC Designer による設計

PSoC デバイスの開発プロセスは、従来の機能固定のマイクロプロセッサの開発プロセスとは異なります。コンフィギュレーション可能なアナログとデジタル ハードウェア ブロックは PSoC アーキテクチャに独特の柔軟性をもたらし、開発時の仕様変更の管理や在庫費用の削減に役立ちます。これらのコンフィギュレーション可能なリソースは PSoC ブロックと呼ばれ、ユーザーが選択可能なさまざまな機能を実装できます。PSoC 開発プロセスは次の通りです。

1. ユーザー モジュールの選択

2. ユーザー モジュールのコンフィギュレーション

3. 構成および接続

4. 生成、検証、およびデバッグ

### ユーザー モジュールの選択

PSoC Designer は、あらかじめ構築され、テスト済みのハードウェア周辺コンポーネント（ユーザー モジュールと呼ばれる）のライブラリを備えています。ユーザー モジュールにより、アナログとデジタル両方の周辺デバイスの選択と実装を簡素化できます。

### ユーザー モジュールをコンフィギュレーション

選択した各ユーザー モジュールにより、選択した機能を実装する基本的なレジスタ設定を確立できます。また、コンポーネントの適格なコンフィギュレーションを特定のアプリケーションに合わせるようにするパラメーターとプロパティも提供されます。例えば PWM ユーザー モジュールでは、1 個以上のデジタル PSoC ブロックをそれぞれが 8 ビット分解能を持つようコンフィギュレーションします。これらのパラメーターを使って、パルス幅とデューティ比を設定できます。選択したアプリケーションに対応するようパラメーターとプロパティをコンフィギュレーションします。値は直接入力することも、ドロップダウン メニューから選択することもできます。すべてのユーザー モジュールはデータシートに文書化され、PSoC Designer またはサイプレスのウェブサイトで直接確認できます。[ユーザー モジュール データシート](#)には、ユーザー モジュールの内部動作に関する説明と性能仕様が記載されています。また、各データ

シートにはユーザー モジュールの各パラメーターの使用方法や、デザインを適切に実装するために必要なその他の情報もまとめられています。

### 構成および接続

ユーザー モジュールを他のモジュールおよび I/O ピンに相互接続することによって、チップ レベルで信号チェーンを構築することができます。すべてのオンチップ リソースを完全に制御できるように、選択、コンフィギュレーション、およびルーティングを行います。

### 生成、検証、およびデバッグ

ハードウェアのコンフィギュレーションのテスト、またはプロジェクトのコード開発の準備ができたら、「コンフィギュレーション ファイルの生成」手順を実行します。このステップで PSoC Designer によって生成されるソース コードは、仕様に合わせてデバイスを自動的にコンフィギュレーションし、システム用のソフトウェアを提供します。生成されたコードは、実行時に発生するハードウェア イベントの制御とそれに対する応答を実現する高レベル API、および必要に応じて修正して使用できる割り込みサービス ルーチンを提供します。

高い完成度のコード開発環境により、C、アセンブリ、または両方の言語を使用したアプリケーションの開発とカスタマイズが可能です。

開発プロセスの最後のステップは、PSoC Designer のデバッガ内で進めます (Connect アイコンをクリックしてアクセスします)。PSoC Designer によって HEX イメージが ICE にダウンロードされ、フルスピードで実行されます。PSoC Designer のデバッグ機能は、何倍も高価なデバッグ システムの機能に匹敵します。デバッグ インターフェースは、シングル ステップ実行、ブレークポイントまでの実行、変数値の追跡などの従来からの機能のほか、大容量のトレース バッファを備えています。アドレスとデータ バス値の監視、メモリ位置の監視、外部信号の監視などの複雑なブレークポイント イベントを定義できます。

## ピン配置

本節では、CY8C28xxx PSoC デバイスのピン一覧およびピン配置について、表と図と共に説明します。

CY8C28xxx PSoC デバイスは様々なパッケージで提供しています。各パッケージについては次の表に示します。すべてのポートピン（「P」というラベルが付けられた）は、デジタル I/O 機能を備えています。しかし、V<sub>SS</sub>、V<sub>DD</sub>、SMP および XRES はデジタル I/O 機能を備えていません。

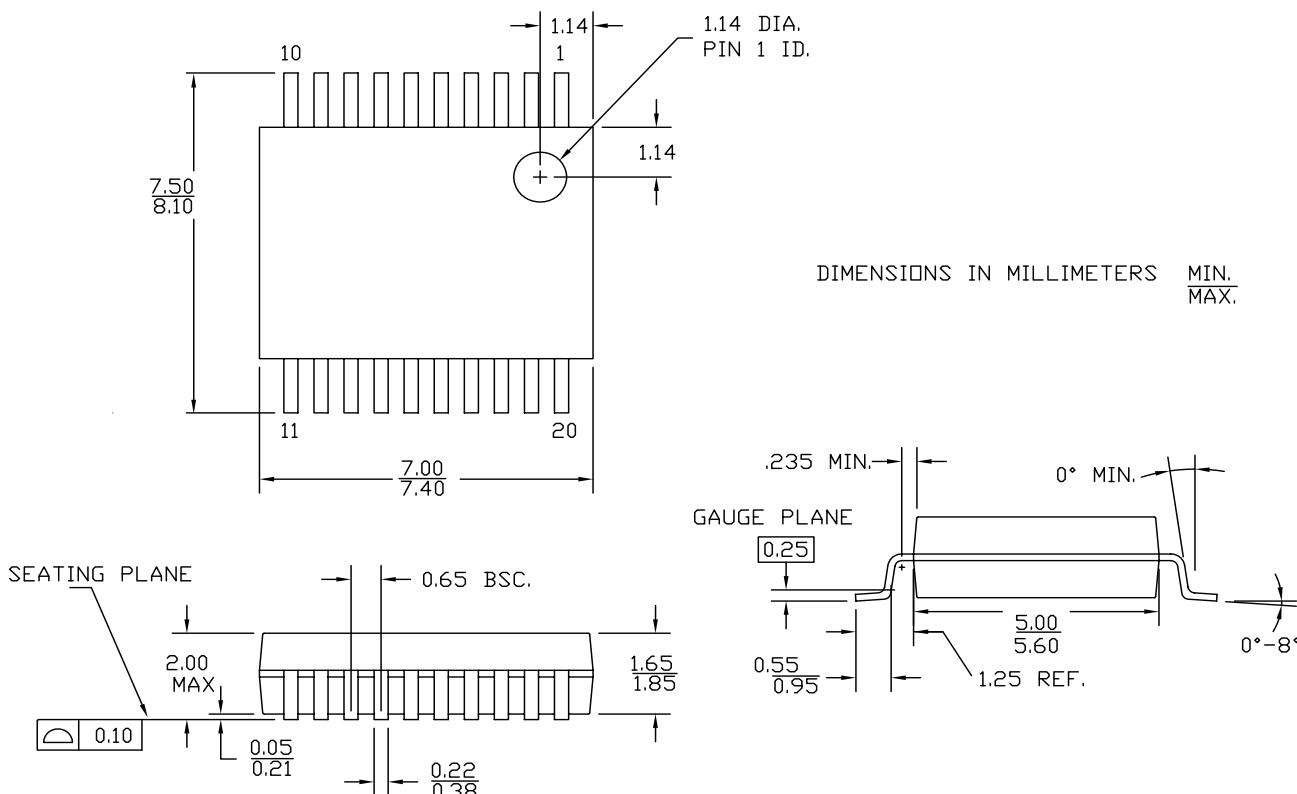

### 20 ピン製品のピン配置

表 3. 20 ピン製品 (SSOP) のピン配置

| ピン番号 | タイプ  |         | ピン名             | 説明                                                              |

|------|------|---------|-----------------|-----------------------------------------------------------------|

|      | デジタル | アナログ    |                 |                                                                 |

| 1    | I/O  | I、M、S   | P0[7]           | アナログ カラム マルチプレクサおよび SAR ADC 入力 <sup>[5]</sup>                   |

| 2    | I/O  | I/O、M、S | P0[5]           | アナログ カラム マルチプレクサおよび SAR ADC 入力。アナログ カラム出力 <sup>[5, 6]</sup>     |

| 3    | I/O  | I/O、M、S | P0[3]           | アナログ カラム マルチプレクサおよび SAR ADC 入力。アナログ カラム出力 <sup>[5, 6]</sup>     |

| 4    | I/O  | I、M、S   | P0[1]           | アナログ カラム マルチプレクサおよび SAR ADC 入力 <sup>[5]</sup>                   |

| 5    | 出力   |         | SMP             | 外部部品に接続するスイッチ モード ポンプ (SMP)                                     |

| 6    | I/O  | M       | P1[7]           | I2C0 シリアル クロック (SCL)                                            |

| 7    | I/O  | M       | P1[5]           | I2C0 シリアル データ (SDA)                                             |

| 8    | I/O  | M       | P1[3]           |                                                                 |

| 9    | I/O  | M       | P1[1]           | 水晶振動子入力 (XTALin)、I2C0 シリアル クロック (SCL)、ISSP-SCLK <sup>[4]</sup>  |

| 10   | 電源   |         | V <sub>SS</sub> | グランドに接続                                                         |

| 11   | I/O  | M       | P1[0]           | 水晶振動子出力 (XTALout)、I2C0 シリアル データ (SDA)、ISSP-SDATA <sup>[4]</sup> |

| 12   | I/O  | M       | P1[2]           | I2C1 シリアル データ (SDA) <sup>[7]</sup>                              |

| 13   | I/O  | M       | P1[4]           | オプションの外部クロック入力 (EXTCLK)                                         |

| 14   | I/O  | M       | P1[6]           | I2C1 シリアル クロック (SCL) <sup>[7]</sup>                             |

| 15   | 入力   |         | XRES            | 内部でプルダウンされている、アクティブ HIGH の外部リセット                                |

| 16   | I/O  | I、M、S   | P0[0]           | アナログ カラム マルチプレクサおよび SAR ADC 入力 <sup>[5]</sup>                   |

| 17   | I/O  | I/O、M、S | P0[2]           | アナログ カラム マルチプレクサおよび SAR ADC 入力。アナログ カラム出力 <sup>[5, 8]</sup>     |

| 18   | I/O  | I/O、M、S | P0[4]           | アナログ カラム マルチプレクサおよび SAR ADC 入力。アナログ カラム出力 <sup>[5, 8]</sup>     |

| 19   | I/O  | I、M、S   | P0[6]           | アナログ カラム マルチプレクサおよび SAR ADC 入力 <sup>[5]</sup>                   |

| 20   | 電源   |         | V <sub>DD</sub> | 電源電圧                                                            |

凡例 : A = アナログ、I = 入力、O = 出力、S = SAR ADC 入力、M = アナログ マルチプレクサ バス入力。

CY8C28243 20 ピン PSoC デバイス

#### 注

4. これらは ISSP ピンであり、POR (パワーオン リセット) の時に High-Z なりません。詳細については、CY8C28xxx PSoC デバイスの PSoC テクニカル リファレンス マニュアルを参照してください。

5. CY8C28x52 と CY8C28x23 デバイスは SAR ADC を備えていません。したがって、このピンは、これらのデバイスでは SAR ADC 入力としては機能しません。

6. CY8C28x13 および CY8C28x03 デバイスは、どのアナログ出力バッファも備えていません。したがって、このピンは、これらのデバイスではアナログ列出力として機能しません。

7. CY8C28x52、CY8C28x13 および CY8C28x03 デバイスは、1 個のみの I2C ブロックを備えています。したがって、この GPIO は、これらのデバイスでは I2C ピンとして機能しません。

8. CY8C28x33、CY8C28x23、CY8C28x13、および CY8C28x03 デバイスは、このピン用のアナログ出力バッファを持っています。したがって、このピンは、これらのデバイスではアナログ カラム出力として機能しません。

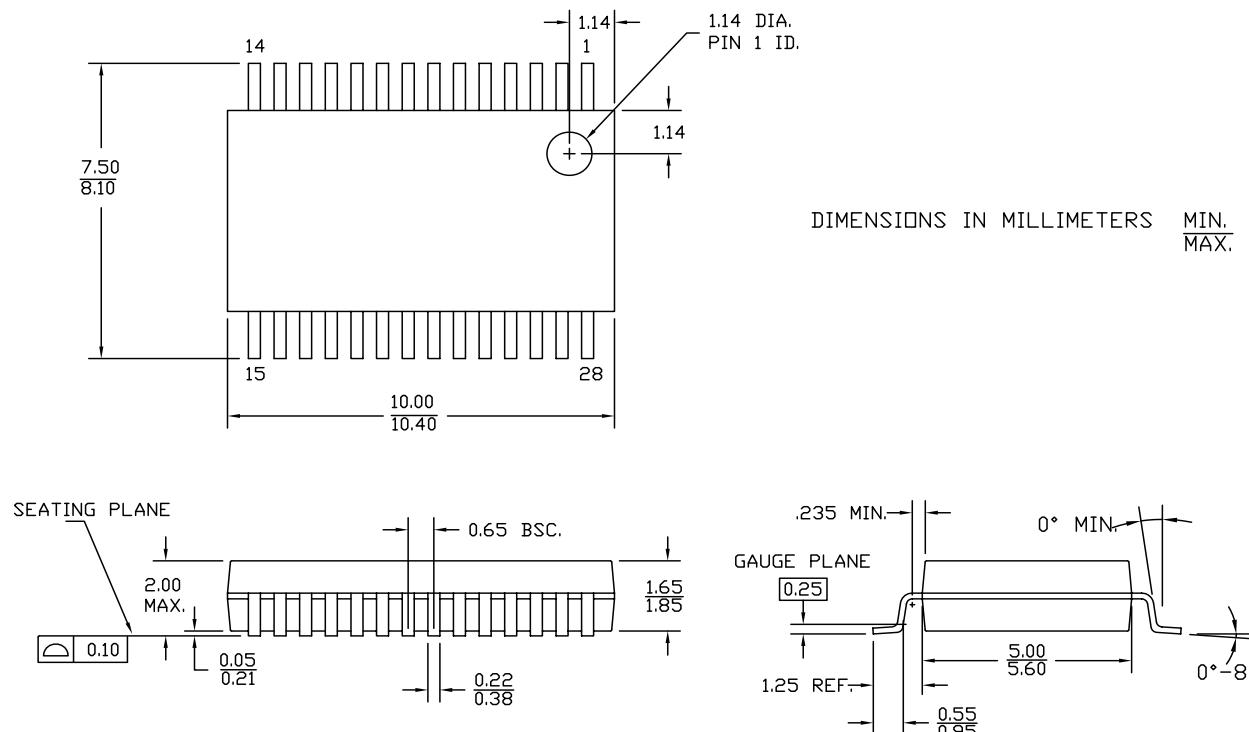

## 28 ピン製品のピン配置

表 4. 28 ピン製品 (SSOP) のピン配置

| ピン番号 | タイプ  |         | ピン名             | 説明                                                              |

|------|------|---------|-----------------|-----------------------------------------------------------------|

|      | デジタル | アナログ    |                 |                                                                 |

| 1    | I/O  | I、M、S   | P0[7]           | アナログ カラム マルチプレクサおよび SAR ADC 入力 <sup>[5]</sup>                   |

| 2    | I/O  | I/O、M、S | P0[5]           | アナログ カラム マルチプレクサおよび SAR ADC 入力。アナログ カラム出力 <sup>[5, 6]</sup>     |

| 3    | I/O  | I/O、M、S | P0[3]           | アナログ カラム マルチプレクサおよび SAR ADC 入力。アナログ カラム出力 <sup>[5, 6]</sup>     |

| 4    | I/O  | I、M、S   | P0[1]           | アナログ カラム マルチプレクサおよび SAR ADC 入力 <sup>[5]</sup>                   |

| 5    | I/O  | M       | P2[7]           |                                                                 |

| 6    | I/O  | M       | P2[5]           |                                                                 |

| 7    | I/O  | I、M     | P2[3]           | スイッチトキャパシタ ブロックの直接入力 <sup>[9]</sup>                             |

| 8    | I/O  | I、M     | P2[1]           | スイッチトキャパシタ ブロックの直接入力 <sup>[9]</sup>                             |

| 9    | 出力   |         | SMP             | 外部部品に接続するスイッチ モード ポンプ (SMP)                                     |

| 10   | I/O  | M       | P1[7]           | I2C0 シリアル クロック (SCL)                                            |

| 11   | I/O  | M       | P1[5]           | I2C0 シリアル データ (SDA)                                             |

| 12   | I/O  | M       | P1[3]           |                                                                 |

| 13   | I/O  | M       | P1[1]           | 水晶振動子入力 (XTALin)、I2C0 シリアル クロック (SCL)、ISSP-SCLK <sup>[4]</sup>  |

| 14   | 電源   |         | V <sub>SS</sub> | グランドに接続                                                         |

| 15   | I/O  | M       | P1[0]           | 水晶振動子出力 (XTALout)、I2C0 シリアル データ (SDA)、ISSP-SDATA <sup>[4]</sup> |

| 16   | I/O  | M       | P1[2]           | I2C1 シリアル データ (SDA) <sup>[7]</sup>                              |

| 17   | I/O  | M       | P1[4]           | オプションの外部クロック入力 (EXTCLK)                                         |

| 18   | I/O  | M       | P1[6]           | I2C1 シリアル クロック (SCL) <sup>[7]</sup>                             |

| 19   | 入力   |         | XRES            | 内部でプルダウンされている、アクティブ HIGH の外部リセット                                |

| 20   | I/O  | I、M     | P2[0]           | スイッチトキャパシタ ブロックの直接入力 <sup>[10]</sup>                            |

| 21   | I/O  | I、M     | P2[2]           | スイッチトキャパシタ ブロックの直接入力 <sup>[10]</sup>                            |

| 22   | I/O  | M       | P2[4]           | 外部アナログ グランド (AGND)                                              |

| 23   | I/O  | M       | P2[6]           | 外部リファレンス電圧 (VRef)                                               |

| 24   | I/O  | I、M、S   | P0[0]           | アナログ カラム マルチプレクサおよび SAR ADC 入力 <sup>[5]</sup>                   |

| 25   | I/O  | I/O、M、S | P0[2]           | アナログ カラム マルチプレクサおよび SAR ADC 入力。アナログ カラム出力 <sup>[5, 8]</sup>     |

| 26   | I/O  | I/O、M、S | P0[4]           | アナログ カラム マルチプレクサおよび SAR ADC 入力。アナログ カラム出力 <sup>[5, 8]</sup>     |

| 27   | I/O  | I、M、S   | P0[6]           | アナログ カラム マルチプレクサおよび SAR ADC 入力 <sup>[5]</sup>                   |

| 28   | 電源   |         | V <sub>DD</sub> | 電源電圧                                                            |

凡例: A = アナログ、I = 入力、O = 出力、S = SAR ADC 入力、M = アナログ マルチプレクサ バス入力。

### 注

9. このピンは、CY8C28x03 および CY8C28x13 デバイスでは、スイッチトキャパシタ ブロックの直接アナログ入力ではありません。

10. このピンは、CY8C28x03、CY8C28x13、CY8C28x23 および CY8C28x33 デバイスでは、スイッチトキャパシタ ブロックの直接アナログ入力ではありません。

**CY8C28403、CY8C28413、CY8C28433、CY8C28445、CY8C28452 28 ピン PSoC デバイス**

#### 44 ピン製品のピン配置

表 5. 44 ピン製品 (TQFP) のピン配置

| ピン番号 | タイプ  |           | ピン名             | 説明                                                              |

|------|------|-----------|-----------------|-----------------------------------------------------------------|

|      | デジタル | アナログ      |                 |                                                                 |

| 1    | I/O  | M         | P2[5]           |                                                                 |

| 2    | I/O  | I, M      | P2[3]           | スイッチトキャパシタ ブロックの直接入力 <sup>[9]</sup>                             |

| 3    | I/O  | I, M      | P2[1]           | スイッチトキャパシタ ブロックの直接入力 <sup>[9]</sup>                             |

| 4    | I/O  | M         | P4[7]           |                                                                 |

| 5    | I/O  | M         | P4[5]           |                                                                 |

| 6    | I/O  | M         | P4[3]           |                                                                 |

| 7    | I/O  | M         | P4[1]           |                                                                 |

| 8    | 出力   |           | SMP             | 外部部品に接続するスイッチ モード ポンプ (SMP)                                     |

| 9    | I/O  | M         | P3[7]           |                                                                 |

| 10   | I/O  | M         | P3[5]           |                                                                 |

| 11   | I/O  | M         | P3[3]           |                                                                 |

| 12   | I/O  | M         | P3[1]           |                                                                 |

| 13   | I/O  | M         | P1[7]           | I2C0 シリアル クロック (SCL)                                            |

| 14   | I/O  | M         | P1[5]           | I2C0 シリアル データ (SDA)                                             |

| 15   | I/O  | M         | P1[3]           |                                                                 |

| 16   | I/O  | M         | P1[1]           | 水晶振動子入力 (XTALin)、I2C0 シリアル クロック (SCL)、ISSP-SCLK <sup>[4]</sup>  |

| 17   | 電源   |           | V <sub>SS</sub> | グランドに接続                                                         |

| 18   | I/O  | M         | P1[0]           | 水晶振動子出力 (XTALout)、I2C0 シリアル データ (SDA)、ISSP-SDATA <sup>[4]</sup> |

| 19   | I/O  | M         | P1[2]           | I2C1 シリアル データ (SDA) <sup>[7]</sup>                              |

| 20   | I/O  | M         | P1[4]           | オプションの外部クロック入力 (EXTCLK)                                         |

| 21   | I/O  | M         | P1[6]           | I2C1 シリアル クロック (SCL) <sup>[7]</sup>                             |

| 22   | I/O  | M         | P3[0]           | I2C1 シリアル データ (SDA) <sup>[7]</sup>                              |

| 23   | I/O  | M         | P3[2]           | I2C1 シリアル クロック (SCL) <sup>[7]</sup>                             |

| 24   | I/O  | M         | P3[4]           |                                                                 |

| 25   | I/O  | M         | P3[6]           |                                                                 |

| 26   | 入力   |           | XRES            | 内部でプルダウンされている、アクティブ HIGH の外部リセット                                |

| 27   | I/O  | M         | P4[0]           |                                                                 |

| 28   | I/O  | M         | P4[2]           |                                                                 |

| 29   | I/O  | M         | P4[4]           |                                                                 |

| 30   | I/O  | M         | P4[6]           |                                                                 |

| 31   | I/O  | I, M      | P2[0]           | スイッチトキャパシタ ブロックの直接入力 <sup>[10]</sup>                            |

| 32   | I/O  | I, M      | P2[2]           | スイッチトキャパシタ ブロックの直接入力 <sup>[10]</sup>                            |

| 33   | I/O  | M         | P2[4]           | 外部アナログ グランド (AGND)                                              |

| 34   | I/O  | M         | P2[6]           | 外部リファレンス電圧 (VRef)                                               |

| 35   | I/O  | I, M, S   | P0[0]           | アナログ カラム マルチプレクサおよび SAR ADC 入力 <sup>[5]</sup>                   |

| 36   | I/O  | I/O, M, S | P0[2]           | アナログ カラム マルチプレクサおよび SAR ADC 入力。アナログ カラム出力 <sup>[5, 8]</sup>     |

| 37   | I/O  | I/O, M, S | P0[4]           | アナログ カラム マルチプレクサおよび SAR ADC 入力。アナログ カラム出力 <sup>[5, 8]</sup>     |

| 38   | I/O  | I, M, S   | P0[6]           | アナログ カラム マルチプレクサおよび SAR ADC 入力 <sup>[5]</sup>                   |

| 39   | 電源   |           | V <sub>DD</sub> | 電源電圧                                                            |

| 40   | I/O  | I, M, S   | P0[7]           | アナログ カラム マルチプレクサおよび SAR ADC 入力 <sup>[5]</sup>                   |

| 41   | I/O  | I/O, M, S | P0[5]           | アナログ カラム マルチプレクサおよび SAR ADC 入力。アナログ カラム出力 <sup>[5, 6]</sup>     |

| 42   | I/O  | I/O, M, S | P0[3]           | アナログ カラム マルチプレクサおよび SAR ADC 入力。アナログ カラム出力 <sup>[5, 6]</sup>     |

| 43   | I/O  | I, M, S   | P0[1]           | アナログ カラム マルチプレクサおよび SAR ADC 入力 <sup>[5]</sup>                   |

| 44   | I/O  |           | P2[7]           |                                                                 |

## CY8C28513 および CY8C28545 48 ピン PSoC デバイス

凡例: A = アナログ、I = 入力、O = 出力、S = SAR ADC 入力、M = アナログ マルチプレクサ バス入力。

## 48 ピン製品のピン配置

表 6. 48 ピン製品 (QFN<sup>[11]</sup>) のピン配置

| ピン番号 | タイプ  | ピン名             | 説明                               |

|------|------|-----------------|----------------------------------|

| デジタル | アナログ |                 |                                  |

| 1    | I/O  | I, M            | P2[3]                            |

| 2    | I/O  | I, M            | P2[1]                            |

| 3    | I/O  | M               | P4[7]                            |

| 4    | I/O  | M               | P4[5]                            |

| 5    | I/O  | M               | P4[3]                            |

| 6    | I/O  | M               | P4[1]                            |

| 7    | 出力   | SMP             | 外部部品に接続するスイッチ モード ポンプ (SMP)      |

| 8    | I/O  | M               | P3[7]                            |

| 9    | I/O  | M               | P3[5]                            |

| 10   | I/O  | M               | P3[3]                            |

| 11   | I/O  | M               | P3[1]                            |

| 12   | I/O  | M               | P5[3]                            |

| 13   | I/O  | M               | P5[1]                            |

| 14   | I/O  | M               | P1[7]                            |

| 15   | I/O  | M               | P1[5]                            |

| 16   | I/O  | M               | P1[3]                            |

| 17   | I/O  | M               | P1[1]                            |

| 18   | 電源   | V <sub>SS</sub> | グランドに接続                          |

| 19   | I/O  | M               | P1[0]                            |

| 20   | I/O  | M               | P1[2]                            |

| 21   | I/O  | M               | P1[4]                            |

| 22   | I/O  | M               | P1[6]                            |

| 23   | I/O  | M               | P5[0]                            |

| 24   | I/O  | M               | P5[2]                            |

| 25   | I/O  | M               | P3[0]                            |

| 26   | I/O  | M               | P3[2]                            |

| 27   | I/O  | M               | P3[4]                            |

| 28   | I/O  | M               | P3[6]                            |

| 29   | 入力   | XRES            | 内部でプルダウンされている、アクティブ HIGH の外部リセット |

| 30   | I/O  | M               | P4[0]                            |

| 31   | I/O  | M               | P4[2]                            |

| 32   | I/O  | M               | P4[4]                            |

| 33   | I/O  | M               | P4[6]                            |

| 34   | I/O  | I, M            | P2[0]                            |

| 35   | I/O  | I, M            | P2[2]                            |

| 36   | I/O  | M               | P2[4]                            |

| 37   | I/O  | M               | P2[6]                            |

| 38   | I/O  | I, M, S         | P0[0]                            |

| 39   | I/O  | I/O, M, S       | P0[2]                            |

| 40   | I/O  | I/O, M, S       | P0[4]                            |

| ピン番号 | タイプ  | ピン名             | 説明                                                          |

|------|------|-----------------|-------------------------------------------------------------|

| デジタル | アナログ |                 |                                                             |

| 41   | I/O  | I, M, S         | P0[6]                                                       |

|      |      |                 | アナログ カラム マルチブレクサおよび SAR ADC 入力 <sup>[5]</sup>               |

| 42   | 電源   | V <sub>DD</sub> | 電源電圧                                                        |

| 43   | I/O  | I, M, S         | P0[7]                                                       |

|      |      |                 | アナログ カラム マルチブレクサおよび SAR ADC 入力 <sup>[5]</sup>               |

| 44   | I/O  | I/O, M, S       | P0[5]                                                       |

|      |      |                 | アナログ カラム マルチブレクサおよび SAR ADC 入力。アナログ カラム出力 <sup>[5, 6]</sup> |

| 45   | I/O  | I/O, M, S       | P0[3]                                                       |

|      |      |                 | アナログ カラム マルチブレクサおよび SAR ADC 入力。アナログ カラム出力 <sup>[5, 6]</sup> |

| 46   | I/O  | I, M, S         | P0[1]                                                       |

|      |      |                 | アナログ カラム マルチブレクサおよび SAR ADC 入力 <sup>[5]</sup>               |

| 47   | I/O  | M               | P2[7]                                                       |

|      |      |                 |                                                             |

| 48   | I/O  | M               | P2[5]                                                       |

|      |      |                 |                                                             |

凡例: A = アナログ、I = 入力、O = 出力、S = SAR ADC 入力、M = アナログ マルチブレクサバス入力。

### 注

11. QFN パッケージは、グランドに接続する必要があるセンター パッドを持っています (V<sub>SS</sub>)。

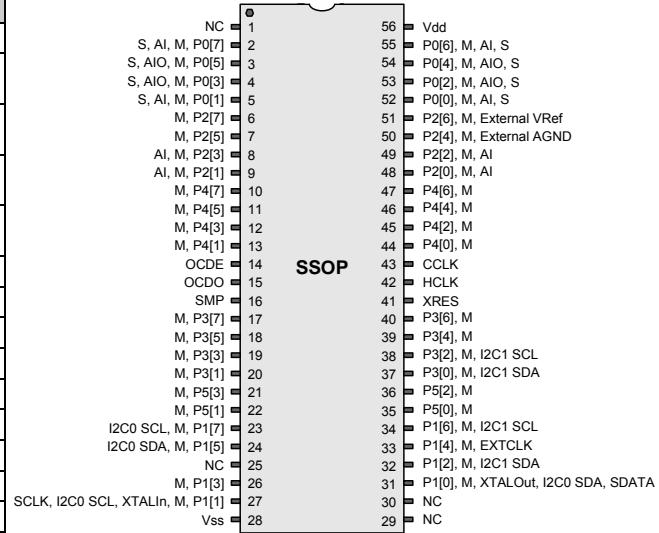

## 56 ピン製品のピン配置

56 ピン SSOP 製品は、CY8C28000 オンチップ デバッグ (OCD) PSoC デバイス用です。

注：この製品は、インサーキット デバッグのみに使用されます。量産製品用としては提供されません。

表 7. 56 ピン製品 (SSOP) のピン配置

| ピン番号 | タイプ  |           | ピン名             | 説明                                                              |

|------|------|-----------|-----------------|-----------------------------------------------------------------|

|      | デジタル | アナログ      |                 |                                                                 |

| 1    |      |           | NC              | 未接続                                                             |

| 2    | I/O  | I, M, S   | P0[7]           | アナログ カラム マルチプレクサおよび SAR ADC 入力                                  |

| 3    | I/O  | I/O, M, S | P0[5]           | アナログ カラム マルチプレクサおよび SAR ADC 入力。アナログ カラム出力                       |

| 4    | I/O  | I/O, M, S | P0[3]           | アナログ カラム マルチプレクサおよび SAR ADC 入力。アナログ カラム出力                       |

| 5    | I/O  | I, M, S   | P0[1]           | アナログ カラム マルチプレクサおよび SAR ADC 入力                                  |

| 6    | I/O  | M         | P2[7]           |                                                                 |

| 7    | I/O  | M         | P2[5]           |                                                                 |

| 8    | I/O  | I         | P2[3]           | スイッチト キャバシタ ブロックの直接入力                                           |

| 9    | I/O  | I         | P2[1]           | スイッチト キャバシタ ブロックの直接入力                                           |

| 10   | I/O  | M         | P4[7]           |                                                                 |

| 11   | I/O  | M         | P4[5]           |                                                                 |

| 12   | I/O  | I, M      | P4[3]           |                                                                 |

| 13   | I/O  | I, M      | P4[1]           |                                                                 |

| 14   | OCD  | M         | OCDE            | OCD 偶数データ I/O                                                   |

| 15   | OCD  | M         | OCDO            | OCD 奇数データ出力                                                     |

| 16   | 出力   |           | SMP             | 必要な外部部品に接続するスイッチ モード ポンプ (SMP)                                  |

| 17   | I/O  | M         | P3[7]           |                                                                 |

| 18   | I/O  | M         | P3[5]           |                                                                 |

| 19   | I/O  | M         | P3[3]           |                                                                 |

| 20   | I/O  | M         | P3[1]           |                                                                 |

| 21   | I/O  | M         | P5[3]           |                                                                 |

| 22   | I/O  | M         | P5[1]           |                                                                 |

| 23   | I/O  | M         | P1[7]           | I2C0 シリアル クロック (SCL)                                            |

| 24   | I/O  | M         | P1[5]           | I2C0 シリアル データ (SDA)                                             |

| 25   | NC   |           | NC              | 未接続                                                             |

| 26   | I/O  | M         | P1[3]           |                                                                 |

| 27   | I/O  | M         | P1[1]           | 水晶振動子入力 (XTALin)、I2C0 シリアル クロック (SCL)、ISSP-SCLK <sup>[4]</sup>  |

| 28   | 電源   |           | V <sub>SS</sub> | グランドに接続                                                         |

| 29   | NC   |           | NC              | 未接続                                                             |

| 30   | NC   |           | NC              | 未接続                                                             |

| 31   | I/O  | M         | P1[0]           | 水晶振動子出力 (XTALout)、I2C0 シリアル データ (SDA)、ISSP-SDATA <sup>[4]</sup> |

| 32   | I/O  | M         | P1[2]           | I2C1 シリアル データ (SDA)                                             |

| 33   | I/O  | M         | P1[4]           | オプションの外部クロック入力 (EXTCLK)                                         |

| 34   | I/O  | M         | P1[6]           | I2C1 シリアル クロック (SCL)                                            |

| 35   | I/O  | M         | P5[0]           |                                                                 |

| 36   | I/O  | M         | P5[2]           |                                                                 |

| 37   | I/O  | M         | P3[0]           | I2C1 シリアル データ (SDA)                                             |

| 38   | I/O  | M         | P3[2]           | I2C1 シリアル クロック (SCL)                                            |

| 39   | I/O  | M         | P3[4]           |                                                                 |

| 40   | I/O  | M         | P3[6]           |                                                                 |

## CY8C28000 56 ピン PSoC デバイス

量産用ではない

表 7. 56 ピン製品 (SSOP) のピン配置 ( 続き )

| ピン番号 | タイプ  |           | ピン名             | 説明                                        |

|------|------|-----------|-----------------|-------------------------------------------|

|      | デジタル | アナログ      |                 |                                           |

| 41   | 入力   |           | XRES            | 内部でプルダウンされている、アクティブ HIGH の外部リセット          |

| 42   | OCD  | M         | HCLK            | OCD 高速クロック出力                              |

| 43   | OCD  | M         | CCLK            | OCD CPU クロック出力                            |

| 44   | I/O  | M         | P4[0]           |                                           |

| 45   | I/O  | M         | P4[2]           |                                           |

| 46   | I/O  | M         | P4[4]           |                                           |

| 47   | I/O  | M         | P4[6]           |                                           |

| 48   | I/O  | I, M      | P2[0]           | スイッチト キャバシタ ブロックの直接入力                     |

| 49   | I/O  | I, M      | P2[2]           | スイッチト キャバシタ ブロックの直接入力                     |

| 50   | I/O  | M         | P2[4]           | 外部アナログ グラウンド (AGND)                       |

| 51   | I/O  | M         | P2[6]           | 外部リファレンス電圧 (VRef)                         |

| 52   | I/O  | I, M, S   | P0[0]           | アナログ カラム マルチプレクサおよび SAR ADC 入力            |

| 53   | I/O  | I/O, M, S | P0[2]           | アナログ カラム マルチプレクサおよび SAR ADC 入力。アナログ カラム出力 |

| 54   | I/O  | I/O, M, S | P0[4]           | アナログ カラム マルチプレクサおよび SAR ADC 入力。アナログ カラム出力 |

| 55   | I/O  | I, M, S   | P0[6]           | アナログ カラム マルチプレクサおよび SAR ADC 入力            |

| 56   | 電源   |           | V <sub>DD</sub> | 電源電圧                                      |

凡例: A = アナログ、I = 入力、O = 出力、S = SAR ADC 入力、M = アナログ マルチプレクサ バス入力、OCD = オンチップ デバッグ。

## レジスタ リファレンス

本節では、CY8C28xxx PSoC デバイスのレジスター一覧を示します。レジスタの詳細については、CY8C28xxx PSoC デバイスの PSoC テクニカル リファレンス マニュアルを参照してください。

### レジスタの表記法

次の表に、本節で使用しているレジスタの表記法を示します。

| 表記法 | 説明               |

|-----|------------------|

| R   | 読み出しレジスタまたはビット   |

| W   | 書き込みレジスタまたはビット   |

| L   | 論理レジスタまたはビット     |

| C   | クリア可能なレジスタまたはビット |

| #   | アクセスはビット固有       |

### レジスタ マップ表

CY8C28xxx PSoC デバイスには、全部で 512 バイトのレジスタ アドレス空間があります。このレジスタ空間は I/O 空間と呼ばれ、2 つのバンクに分割されています。フラグ レジスタ (CPU\_F) の XIO ビットで、CPU の命令がどのレジスタ バンクにアクセスするか決まります。XIO ビットがセットされた場合、CPU 命令はバンク 1 のレジスタにアクセスします。XIO ビットがクリアされた場合、CPU 命令はバンク 0 のレジスタにアクセスします。

注：次のレジスタ マップ表では、空白のフィールドは予約されており、アクセスしてはなりません。

**表8. CY8C28x03 のバンク 0 のレジスタ マップ表 : ユーザー空間**

| 名前       | アドレス (0, 16 進) | アクセス | 名前       | アドレス (0, 16 進) | アクセス | 名前       | アドレス (0, 16 進) | アクセス | 名前        | アドレス (0, 16 進) | アクセス |

|----------|----------------|------|----------|----------------|------|----------|----------------|------|-----------|----------------|------|

| PRT0DR   | 00             | RW   | DBC20DR0 | 40             | #    |          | 80             |      | RDI2RI    | C0             | RW   |

| PRT0IE   | 01             | RW   | DBC20DR1 | 41             | W    |          | 81             |      | RDI2SYN   | C1             | RW   |

| PRT0GS   | 02             | RW   | DBC20DR2 | 42             | RW   |          | 82             |      | RDI2IS    | C2             | RW   |

| PRT0DM2  | 03             | RW   | DBC21CR0 | 43             | #    |          | 83             |      | RDI2LT0   | C3             | RW   |

| PRT1DR   | 04             | RW   | DBC21DR0 | 44             | #    |          | 84             |      | RDI2LT1   | C4             | RW   |

| PRT1IE   | 05             | RW   | DBC21DR1 | 45             | W    |          | 85             |      | RDI2RO0   | C5             | RW   |

| PRT1GS   | 06             | RW   | DBC21DR2 | 46             | RW   |          | 86             |      | RDI2RO1   | C6             | RW   |

| PRT1DM2  | 07             | RW   | DBC21CR0 | 47             | #    |          | 87             |      | RDI2DSM   | C7             | RW   |

| PRT2DR   | 08             | RW   | DCC22DR0 | 48             | #    |          | 88             |      |           | C8             |      |

| PRT2IE   | 09             | RW   | DCC22DR1 | 49             | W    |          | 89             |      |           | C9             |      |

| PRT2GS   | 0A             | RW   | DCC22DR2 | 4A             | RW   |          | 8A             |      |           | CA             |      |

| PRT2DM2  | 0B             | RW   | DCC22CR0 | 4B             | #    |          | 8B             |      |           | CB             |      |

| PRT3DR   | 0C             | RW   | DCC23DR0 | 4C             | #    |          | 8C             |      |           | CC             |      |

| PRT3IE   | 0D             | RW   | DCC23DR1 | 4D             | W    |          | 8D             |      |           | CD             |      |

| PRT3GS   | 0E             | RW   | DCC23DR2 | 4E             | RW   |          | 8E             |      |           | CE             |      |

| PRT3DM2  | 0F             | RW   | DCC23CR0 | 4F             | #    |          | 8F             |      |           | CF             |      |

| PRT4DR   | 10             | RW   |          | 50             |      |          | 90             |      | CUR_PP    | D0             | RW   |

| PRT4IE   | 11             | RW   |          | 51             |      |          | 91             |      | STK_PP    | D1             | RW   |

| PRT4GS   | 12             | RW   |          | 52             |      |          | 92             |      |           | D2             |      |

| PRT4DM2  | 13             | RW   |          | 53             |      |          | 93             |      | IDX_PP    | D3             | RW   |

| PRT5DR   | 14             | RW   |          | 54             |      |          | 94             |      | MVR_PP    | D4             | RW   |

| PRT5IE   | 15             | RW   |          | 55             |      |          | 95             |      | MVW_PP    | D5             | RW   |

| PRT5GS   | 16             | RW   |          | 56             |      |          | 96             |      | I2C0_CFG  | D6             | RW   |

| PRT5DM2  | 17             | RW   |          | 57             |      |          | 97             |      | I2C0_SCR  | D7             | #    |

|          | 18             |      |          | 58             |      |          | 98             |      | I2C0_DR   | D8             | RW   |

|          | 19             |      |          | 59             |      |          | 99             |      | I2C0_MSCR | D9             | #    |

|          | 1A             |      |          | 5A             |      |          | 9A             |      | INT_CLR0  | DA             | RW   |

|          | 1B             |      |          | 5B             |      |          | 9B             |      | INT_CLR1  | DB             | RW   |

|          | 1C             |      |          | 5C             |      |          | 9C             |      | INT_CLR2  | DC             | RW   |

|          | 1D             |      |          | 5D             |      |          | 9D             |      | INT_CLR3  | DD             | RW   |

|          | 1E             |      |          | 5E             |      |          | 9E             |      | INT_MSK3  | DE             | RW   |

|          | 1F             |      |          | 5F             |      |          | 9F             |      | INT_MSK2  | DF             | RW   |

| DBC00DR0 | 20             | #    |          | 60             |      |          | A0             |      | INT_MSK0  | E0             | RW   |

| DBC00DR1 | 21             | W    |          | 61             |      |          | A1             |      | INT_MSK1  | E1             | RW   |

| DBC00DR2 | 22             | RW   |          | 62             |      |          | A2             |      | INT_VC    | E2             | RC   |

| DBC00CR0 | 23             | #    |          | 63             |      |          | A3             |      | RES_WDT   | E3             | W    |

| DBC01DR0 | 24             | #    |          | 64             |      |          | A4             |      | I2C1_SCR  | E4             | #    |

| DBC01DR1 | 25             | W    |          | 65             |      |          | A5             |      | I2C1_MSCR | E5             | #    |

| DBC01DR2 | 26             | RW   |          | 66             |      |          | A6             |      |           | E6             |      |

| DBC01CR0 | 27             | #    | I2C1_DR  | 67             | RW   |          | A7             |      |           | E7             |      |

| DCC02DR0 | 28             | #    |          | 68             |      | MUL1_X   | A8             | W    | MUL0_X    | E8             | W    |

| DCC02DR1 | 29             | W    |          | 69             |      | MUL1_Y   | A9             | W    | MUL0_Y    | E9             | W    |

| DCC02DR2 | 2A             | RW   | SADC_DH  | 6A             | RW   | MUL1_DH  | AA             | R    | MUL0_DH   | EA             | R    |

| DCC02CR0 | 2B             | #    | SADC_DL  | 6B             | RW   | MUL1_DL  | AB             | R    | MUL0_DL   | EB             | R    |

| DCC03DR0 | 2C             | #    | TMP_DR0  | 6C             | RW   | ACC1_DR1 | AC             | RW   | ACC0_DR1  | EC             | RW   |

| DCC03DR1 | 2D             | W    | TMP_DR1  | 6D             | RW   | ACC1_DR0 | AD             | RW   | ACC0_DR0  | ED             | RW   |

| DCC03DR2 | 2E             | RW   | TMP_DR2  | 6E             | RW   | ACC1_DR3 | AE             | RW   | ACC0_DR3  | EE             | RW   |

| DCC03CR0 | 2F             | #    | TMP_DR3  | 6F             | RW   | ACC1_DR2 | AF             | RW   | ACC0_DR2  | EF             | RW   |

| DBC10DR0 | 30             | #    |          | 70             |      | RDI0RI   | B0             | RW   |           | F0             |      |

| DBC10DR1 | 31             | W    |          | 71             |      | RDI0SYN  | B1             | RW   |           | F1             |      |

| DBC10DR2 | 32             | RW   |          | 72             |      | RDI0IS   | B2             | RW   |           | F2             |      |

| DBC10CR0 | 33             | #    |          | 73             |      | RDI0LT0  | B3             | RW   |           | F3             |      |

| DBC11DR0 | 34             | #    |          | 74             |      | RDI0LT1  | B4             | RW   |           | F4             |      |

| DBC11DR1 | 35             | W    |          | 75             |      | RDI0RO0  | B5             | RW   |           | F5             |      |

| DBC11DR2 | 36             | RW   |          | 76             |      | RDI0RO1  | B6             | RW   |           | F6             |      |

| DBC11CR0 | 37             | #    |          | 77             |      | RDI0DSM  | B7             | RW   | CPU_F     | F7             | RL   |

| DCC12DR0 | 38             | #    |          | 78             |      | RDI1RI   | B8             | RW   |           | F8             |      |

| DCC12DR1 | 39             | W    |          | 79             |      | RDI1SYN  | B9             | RW   |           | F9             |      |

| DCC12DR2 | 3A             | RW   |          | 7A             |      | RDI1IS   | BA             | RW   |           | FA             |      |

| DCC12CR0 | 3B             | #    |          | 7B             |      | RDI1LT0  | BB             | RW   |           | FB             |      |

| DCC13DR0 | 3C             | #    |          | 7C             |      | RDI1LT1  | BC             | RW   |           | FC             |      |

| DCC13DR1 | 3D             | W    |          | 7D             |      | RDI1RO0  | BD             | RW   |           | FD             |      |

| DCC13DR2 | 3E             | RW   |          | 7E             |      | RDI1RO1  | BE             | RW   | CPU_SCR1  | FE             | #    |

| DCC13CR0 | 3F             | #    |          | 7F             |      | RDI1DSM  | BF             | RW   | CPU_SCR0  | FF             | #    |

空白のフィールドは予約されているため、アクセスしてはいけない

# アクセスはビット固有

\* アドレスは二重目的。251 ページの「マッピングの例外」を参照してください。

**表9. CY8C28x03 のバンク 1 のレジスタ マップ表：コンフィギュレーション空間**

| 名前       | アドレス(1、16進) | アクセス | 名前         | アドレス(1、16進) | アクセス | 名前          | アドレス(1、16進) | アクセス | 名前        | アドレス(1、16進) | アクセス |

|----------|-------------|------|------------|-------------|------|-------------|-------------|------|-----------|-------------|------|

| PRT0DM0  | 00          | RW   | DBC20FN    | 40          | RW   |             | 80          |      | RDI2RI    | C0          | RW   |

| PRT0DM1  | 01          | RW   | DBC20IN    | 41          | RW   | SADC_TSCMPL | 81          | RW   | RDI2SYN   | C1          | RW   |

| PRT0IC0  | 02          | RW   | DBC20OU    | 42          | RW   | SADC_TSCMPH | 82          | RW   | RDI2IS    | C2          | RW   |

| PRT0IC1  | 03          | RW   | DBC21CR1   | 43          | RW   |             | 83          |      | RDI2LT0   | C3          | RW   |

| PRT1DM0  | 04          | RW   | DBC21FN    | 44          | RW   |             | 84          |      | RDI2LT1   | C4          | RW   |

| PRT1DM1  | 05          | RW   | DBC21IN    | 45          | RW   |             | 85          |      | RDI2R00   | C5          | RW   |

| PRT1IC0  | 06          | RW   | DBC21OU    | 46          | RW   |             | 86          |      | RDI2R01   | C6          | RW   |

| PRT1IC1  | 07          | RW   | DBC21CR1   | 47          | RW   |             | 87          |      | RDI2DSM   | C7          | RW   |

| PRT2DM0  | 08          | RW   | DCC22FN    | 48          | RW   |             | 88          |      |           | C8          |      |

| PRT2DM1  | 09          | RW   | DCC22IN    | 49          | RW   |             | 89          |      |           | C9          |      |

| PRT2IC0  | 0A          | RW   | DCC22OU    | 4A          | RW   |             | 8A          |      |           | CA          |      |

| PRT2IC1  | 0B          | RW   | DCC22CR1   | 4B          | RW   |             | 8B          |      |           | CB          |      |

| PRT3DM0  | 0C          | RW   | DCC23FN    | 4C          | RW   |             | 8C          |      |           | CC          |      |

| PRT3DM1  | 0D          | RW   | DCC23IN    | 4D          | RW   |             | 8D          |      |           | CD          |      |

| PRT3IC0  | 0E          | RW   | DCC23OU    | 4E          | RW   |             | 8E          |      |           | CE          |      |

| PRT3IC1  | 0F          | RW   | DCC23CR1   | 4F          | RW   |             | 8F          |      |           | CF          |      |

| PRT4DM0  | 10          | RW   |            | 50          |      |             | 90          |      | GDI_O_IN  | D0          | RW   |

| PRT4DM1  | 11          | RW   |            | 51          |      |             | 91          |      | GDI_E_IN  | D1          | RW   |

| PRT4IC0  | 12          | RW   |            | 52          |      |             | 92          |      | GDI_O_OU  | D2          | RW   |

| PRT4IC1  | 13          | RW   |            | 53          |      |             | 93          |      | GDI_E_OU  | D3          | RW   |

| PRT5DM0  | 14          | RW   |            | 54          |      |             | 94          |      |           | D4          |      |

| PRT5DM1  | 15          | RW   |            | 55          |      |             | 95          |      |           | D5          |      |

| PRT5IC0  | 16          | RW   |            | 56          |      |             | 96          |      |           | D6          |      |

| PRT5IC1  | 17          | RW   |            | 57          |      |             | 97          |      |           | D7          |      |

|          | 18          |      |            | 58          |      |             | 98          |      |           | D8          |      |

|          | 19          |      |            | 59          |      |             | 99          |      |           | D9          |      |

|          | 1A          |      |            | 5A          |      |             | 9A          |      |           | DA          |      |

|          | 1B          |      |            | 5B          |      |             | 9B          |      |           | DB          |      |

|          | 1C          |      |            | 5C          |      |             | 9C          |      |           | DC          |      |

|          | 1D          |      |            | 5D          |      |             | 9D          |      | OSC_GO_EN | DD          | RW   |

|          | 1E          |      |            | 5E          |      |             | 9E          |      | OSC_CR4   | DE          | RW   |

|          | 1F          |      |            | 5F          |      |             | 9F          |      | OSC_CR3   | DF          | RW   |

| DBC00FN  | 20          | RW   |            | 60          |      | GDI_O_IN_CR | A0          | RW   | OSC_CR0   | E0          | RW   |

| DBC00IN  | 21          | RW   |            | 61          |      | GDI_E_IN_CR | A1          | RW   | OSC_CR1   | E1          | RW   |

| DBC00OU  | 22          | RW   |            | 62          |      | GDI_O_OU_CR | A2          | RW   | OSC_CR2   | E2          | RW   |

| DBC00CR1 | 23          | RW   |            | 63          |      | GDI_E_OU_CR | A3          | RW   | VLT_CR    | E3          | RW   |

| DBC01FN  | 24          | RW   |            | 64          |      | RTC_H       | A4          | RW   | VLT_CMP   | E4          | RW   |

| DBC01IN  | 25          | RW   |            | 65          |      | RTC_M       | A5          | RW   |           | E5          |      |

| DBC01OU  | 26          | RW   |            | 66          |      | RTC_S       | A6          | RW   |           | E6          |      |

| DBC01CR1 | 27          | RW   |            | 67          |      | RTC_CR      | A7          | RW   |           | E7          |      |

| DCC02FN  | 28          | RW   |            | 68          |      | SADC_CR0    | A8          | RW   | IMO_TR    | E8          | RW   |

| DCC02IN  | 29          | RW   |            | 69          |      | SADC_CR1    | A9          | RW   | ILO_TR    | E9          | RW   |

| DCC02OU  | 2A          | RW   |            | 6A          |      | SADC_CR2    | AA          | RW   | BDG_TR    | EA          | RW   |

| DCC02CR1 | 2B          | RW   | I2C1_CFG   | 6B          | RW   | SADC_CR3    | AB          | RW   | ECO_TR    | EB          | RW   |

| DCC03FN  | 2C          | RW   | TMP_DR0    | 6C          | RW   | SADC_CR4    | AC          | RW   |           | EC          |      |

| DCC03IN  | 2D          | RW   | TMP_DR1    | 6D          | RW   | I2C0_ADDR   | AD          | RW   |           | ED          |      |

| DCC03OU  | 2E          | RW   | TMP_DR2    | 6E          | RW   | I2C1_ADDR   | AE          | RW   |           | EE          |      |

| DCC03CR1 | 2F          | RW   | TMP_DR3    | 6F          | RW   | AMUX_CLK    | AF          | RW   |           | EF          |      |

| DBC10FN  | 30          | RW   |            | 70          |      | RDI0RI      | B0          | RW   |           | F0          |      |

| DBC10IN  | 31          | RW   | SADC_TSCR0 | 71          | RW   | RDI0SYN     | B1          | RW   |           | F1          |      |

| DBC10OU  | 32          | RW   | SADC_TSCR1 | 72          | RW   | RDI0IS      | B2          | RW   |           | F2          |      |

| DBC10CR1 | 33          | RW   |            | 73          |      | RDI0LT0     | B3          | RW   |           | F3          |      |

| DBC11FN  | 34          | RW   |            | 74          |      | RDI0LT1     | B4          | RW   |           | F4          |      |

| DBC11IN  | 35          | RW   |            | 75          |      | RDI0R00     | B5          | RW   |           | F5          |      |

| DBC11OU  | 36          | RW   |            | 76          |      | RDI0R01     | B6          | RW   |           | F6          |      |

| DBC11CR1 | 37          | RW   |            | 77          |      | RDI0DSM     | B7          | RW   | CPU_F     | F7          | RL   |

| DCC12FN  | 38          | RW   |            | 78          |      | RDI1RI      | B8          | RW   |           | F8          |      |

| DCC12IN  | 39          | RW   |            | 79          |      | RDI1SYN     | B9          | RW   |           | F9          |      |

| DCC12OU  | 3A          | RW   |            | 7A          |      | RDI1IS      | BA          | RW   | FLS_PR1   | FA          | RW   |

| DCC12CR1 | 3B          | RW   |            | 7B          |      | RDI1LT0     | BB          | RW   |           | FB          |      |

| DCC13FN  | 3C          | RW   |            | 7C          |      | RDI1LT1     | BC          | RW   |           | FC          |      |

| DCC13IN  | 3D          | RW   |            | 7D          |      | RDI1R00     | BD          | RW   |           | FD          |      |

| DCC13OU  | 3E          | RW   |            | 7E          |      | RDI1R01     | BE          | RW   | CPU_SCR1  | FE          | #    |

| DCC13CR1 | 3F          | RW   |            | 7F          |      | RDI1DSM     | BF          | RW   | CPU_SCR0  | FF          | #    |

空白のフィールドは予約されているため、アクセスしてはいけない

# アクセスはビット固有

\* アドレスは二重目的。251 ページの「マッピングの例外」を参照してください。

表 10. CY8C28x13 のバンク 0 のレジスタ マップ表 : ユーザー空間

| 名前       | アドレス (0..16 進) | アクセス | 名前       | アドレス (0..16 進) | アクセス | 名前       | アドレス (0..16 進) | アクセス | 名前        | アドレス (0..16 進) | アクセス |

|----------|----------------|------|----------|----------------|------|----------|----------------|------|-----------|----------------|------|

| PRT0DR   | 00             | RW   | DBC20DR0 | 40             | #    |          | 80             |      | RDI2RI    | C0             | RW   |

| PRT0IE   | 01             | RW   | DBC20DR1 | 41             | W    |          | 81             |      | RDI2SYN   | C1             | RW   |

| PRT0GS   | 02             | RW   | DBC20DR2 | 42             | RW   |          | 82             |      | RDI2IS    | C2             | RW   |

| PRT0DM2  | 03             | RW   | DBC20CR0 | 43             | #    |          | 83             |      | RDI2LT0   | C3             | RW   |

| PRT1DR   | 04             | RW   | DBC21DR0 | 44             | #    |          | 84             |      | RDI2LT1   | C4             | RW   |

| PRT1IE   | 05             | RW   | DBC21DR1 | 45             | Ω    |          | 85             |      | RDI2RO0   | C5             | RW   |

| PRT1GS   | 06             | RW   | DBC21DR2 | 46             | RW   |          | 86             |      | RDI2RO1   | C6             | RW   |

| PRT1DM2  | 07             | RW   | DBC21CR0 | 47             | #    |          | 87             |      | RDI2DSM   | C7             | RW   |

| PRT2DR   | 08             | RW   | DCC22DR0 | 48             | #    |          | 88             |      |           | C8             |      |

| PRT2IE   | 09             | RW   | DCC22DR1 | 49             | W    |          | 89             |      |           | C9             |      |

| PRT2GS   | 0A             | RW   | DCC22DR2 | 4A             | RW   |          | 8A             |      |           | CA             |      |

| PRT2DM2  | 0B             | RW   | DCC22CR0 | 4B             | #    |          | 8B             |      |           | CB             |      |

| PRT3DR   | 0C             | RW   | DCC23DR0 | 4C             | #    |          | 8C             |      |           | CC             |      |

| PRT3IE   | 0D             | RW   | DCC23DR1 | 4D             | W    |          | 8D             |      |           | CD             |      |

| PRT3GS   | 0E             | RW   | DCC23DR2 | 4E             | RW   |          | 8E             |      |           | CE             |      |

| PRT3DM2  | 0F             | RW   | DCC23CR0 | 4F             | #    |          | 8F             |      |           | CF             |      |

| PRT4DR   | 10             | RW   |          | 50             |      |          | 90             |      | CUR_PP    | D0             | RW   |

| PRT4IE   | 11             | RW   |          | 51             |      |          | 91             |      | STK_PP    | D1             | RW   |

| PRT4GS   | 12             | RW   |          | 52             |      |          | 92             |      |           | D2             |      |

| PRT4DM2  | 13             | RW   |          | 53             |      |          | 93             |      | IDX_PP    | D3             | RW   |

| PRT5DR   | 14             | RW   |          | 54             |      |          | 94             |      | MVR_PP    | D4             | RW   |

| PRT5IE   | 15             | RW   |          | 55             |      |          | 95             |      | MVW_PP    | D5             | RW   |

| PRT5GS   | 16             | RW   |          | 56             |      |          | 96             |      | I2C0_CFG  | D6             | RW   |

| PRT5DM2  | 17             | RW   |          | 57             |      |          | 97             |      | I2C0_SCR  | D7             | #    |

|          | 18             |      |          | 58             |      |          | 98             |      | I2C0_DR   | D8             | RW   |

|          | 19             |      |          | 59             |      |          | 99             |      | I2C0_MSCR | D9             | #    |

|          | 1A             |      |          | 5A             |      |          | 9A             |      | INT_CLR0  | DA             | RW   |

|          | 1B             |      |          | 5B             |      |          | 9B             |      | INT_CLR1  | DB             | RW   |

|          | 1C             |      |          | 5C             |      |          | 9C             |      | INT_CLR2  | DC             | RW   |

|          | 1D             |      |          | 5D             |      |          | 9D             |      | INT_CLR3  | DD             | RW   |

|          | 1E             |      |          | 5E             |      |          | 9E             |      | INT_MSK3  | DE             | RW   |

|          | 1F             |      |          | 5F             |      |          | 9F             |      | INT_MSK2  | DF             | RW   |

| DBC00DR0 | 20             | #    |          | 60             |      | DEC0_DH  | A0             | RC   | INT_MSK0  | E0             | RW   |

| DBC00DR1 | 21             | W    | AMUX_CFG | 61             | RW   | DEC0_DL  | A1             | RC   | INT_MSK1  | E1             | RW   |

| DBC00DR2 | 22             | RW   |          | 62             |      | DEC1_DH  | A2             | RC   | INT_VC    | E2             | RC   |

| DBC00CR0 | 23             | #    |          | 63             |      | DEC1_DL  | A3             | RC   | RES_WDT   | E3             | W    |

| DBC01DR0 | 24             | #    |          | 64             |      |          | A4             |      |           | E4             |      |

| DBC01DR1 | 25             | W    |          | 65             |      |          | A5             |      |           | E5             |      |

| DBC01DR2 | 26             | RW   |          | 66             |      |          | A6             |      | DEC_CR0*  | E6             | RW   |

| DBC01CR0 | 27             | #    |          | 67             |      |          | A7             |      | DEC_CR1*  | E7             | RW   |

| DCC02DR0 | 28             | #    |          | 68             |      | MUL1_X   | A8             | W    | MUL0_X    | E8             | W    |

| DCC02DR1 | 29             | W    |          | 69             |      | MUL1_Y   | A9             | W    | MUL0_Y    | E9             | W    |

| DCC02DR2 | 2A             | RW   | SADC_DH  | 6A             | RW   | MUL1_DH  | AA             | R    | MUL0_DH   | EA             | R    |

| DCC02CR0 | 2B             | #    | SADC_DL  | 6B             | RW   | MUL1_DL  | AB             | R    | MUL0_DL   | EB             | R    |

| DCC03DR0 | 2C             | #    | TMP_DR0  | 6C             | RW   | ACC1_DR1 | AC             | RW   | ACCO_DR1  | EC             | RW   |

| DCC03DR1 | 2D             | W    | TMP_DR1  | 6D             | RW   | ACC1_DR0 | AD             | RW   | ACCO_DR0  | ED             | RW   |

| DCC03DR2 | 2E             | RW   | TMP_DR2  | 6E             | RW   | ACC1_DR3 | AE             | RW   | ACCO_DR3  | EE             | RW   |

| DCC03CR0 | 2F             | #    | TMP_DR3  | 6F             | RW   | ACC1_DR2 | AF             | RW   | ACCO_DR2  | EF             | RW   |

| DBC10DR0 | 30             | #    |          | 70             |      | RDI0RI   | B0             | RW   |           | F0             |      |

| DBC10DR1 | 31             | W    |          | 71             |      | RDI0SYN  | B1             | RW   |           | F1             |      |

| DBC10DR2 | 32             | RW   |          | 72             |      | RDI0IS   | B2             | RW   |           | F2             |      |

| DBC10CR0 | 33             | #    |          | 73             |      | RDI0LT0  | B3             | RW   |           | F3             |      |

| DBC11DR0 | 34             | #    |          | 74             |      | RDI0LT1  | B4             | RW   |           | F4             |      |

| DBC11DR1 | 35             | W    |          | 75             |      | RDI0R00  | B5             | RW   |           | F5             |      |

| DBC11DR2 | 36             | RW   |          | 76             |      | RDI0R01  | B6             | RW   |           | F6             |      |

| DBC11CR0 | 37             | #    |          | 77             |      | RDI0DSM  | B7             | RW   | CPU_F     | F7             | RL   |

| DCC12DR0 | 38             | #    |          | 78             |      | RDI1RI   | B8             | RW   |           | F8             |      |

| DCC12DR1 | 39             | W    |          | 79             |      | RDI1SYN  | B9             | RW   |           | F9             |      |

| DCC12DR2 | 3A             | RW   |          | 7A             |      | RDI1IS   | BA             | RW   |           | FA             |      |

| DCC12CR0 | 3B             | #    |          | 7B             |      | RDI1LT0  | BB             | RW   |           | FB             |      |

| DCC13DR0 | 3C             | #    |          | 7C             |      | RDI1LT1  | BC             | RW   | DAC1_D    | FC             | RW   |

| DCC13DR1 | 3D             | W    |          | 7D             |      | RDI1R00  | BD             | RW   | DAC0_D    | FD             | RW   |

| DCC13DR2 | 3E             | RW   |          | 7E             |      | RDI1R01  | BE             | RW   | CPU_SCR1  | FE             | #    |

| DCC13CR0 | 3F             | #    |          | 7F             |      | RDI1DSM  | BF             | RW   | CPU_SCR0  | FF             | #    |

空白のフィールドは予約されているため、アクセスしてはいけない

# アクセスはビット固有

\* アドレスは二重目的。251 ページの「マッピングの例外」を参照してください。

**表 11. CY8C28x13 のバンク 1 のレジスタ マップ表 : コンフィギュレーション空間**

| 名前       | アドレス(1、16進) | アクセス | 名前            | アドレス(1、16進) | アクセス | 名前          | アドレス(1、16進) | アクセス | 名前        | アドレス(1、16進) | アクセス |

|----------|-------------|------|---------------|-------------|------|-------------|-------------|------|-----------|-------------|------|

| PRT0DM0  | 00          | RW   | DBC20FN       | 40          | RW   |             | 80          |      | RDI2RI    | C0          | RW   |

| PRT0DM1  | 01          | RW   | DBC20IN       | 41          | RW   | SADC_TSCMPL | 81          | RW   | RDI2SYN   | C1          | RW   |

| PRT0IC0  | 02          | RW   | DBC20OU       | 42          | RW   | SADC_TSCMPH | 82          | RW   | RDI2IS    | C2          | RW   |

| PRT0IC1  | 03          | RW   | DBC20CR1      | 43          | RW   | ACE_AMD_CR1 | 83          | RW   | RDI2LT0   | C3          | RW   |

| PRT1DM0  | 04          | RW   | DBC21FN       | 44          | RW   |             | 84          |      | RDI2LT1   | C4          | RW   |

| PRT1DM1  | 05          | RW   | DBC21IN       | 45          | RW   | ACE_PWM_CR  | 85          | RW   | RDI2RO0   | C5          | RW   |

| PRT1IC0  | 06          | RW   | DBC21OU       | 46          | RW   | ACE_ADC0_CR | 86          | RW   | RDI2R01   | C6          | RW   |

| PRT1IC1  | 07          | RW   | DBC21CR1      | 47          | RW   | ACE_ADC1_CR | 87          | RW   | RDI2DSM   | C7          | RW   |

| PRT2DM0  | 08          | RW   | DCC22FN       | 48          | RW   |             | 88          |      |           | C8          |      |

| PRT2DM1  | 09          | RW   | DCC22IN       | 49          | RW   | ACE_CLK_CR0 | 89          | RW   |           | C9          |      |

| PRT2IC0  | 0A          | RW   | DCC22OU       | 4A          | RW   | ACE_CLK_CR1 | 8A          | RW   |           | CA          |      |

| PRT2IC1  | 0B          | RW   | DCC22CR1      | 4B          | RW   | ACE_CLK_CR3 | 8B          | RW   |           | CB          |      |

| PRT3DM0  | 0C          | RW   | DCC23FN       | 4C          | RW   |             | 8C          | RW   |           | CC          |      |

| PRT3DM1  | 0D          | RW   | DCC23IN       | 4D          | RW   | ACE01CR1    | 8D          | RW   |           | CD          |      |

| PRT3IC0  | 0E          | RW   | DCC23OU       | 4E          | RW   | ACE01CR2    | 8E          | RW   |           | CE          |      |

| PRT3IC1  | 0F          | RW   | DCC23CR1      | 4F          | RW   | ASE11CR0    | 8F          | RW   |           | CF          |      |

| PRT4DM0  | 10          | RW   |               | 50          |      |             | 90          |      | GDI_O_IN  | D0          | RW   |

| PRT4DM1  | 11          | RW   |               | 51          |      | DEC0_CR0    | 91          | RW   | GDI_E_IN  | D1          | RW   |

| PRT4IC0  | 12          | RW   |               | 52          |      | DEC_CR3     | 92          | RW   | GDI_O_OU  | D2          | RW   |

| PRT4IC1  | 13          | RW   |               | 53          |      |             | 93          |      | GDI_E_OU  | D3          | RW   |

| PRT5DM0  | 14          | RW   |               | 54          |      |             | 94          |      | DEC0_CR   | D4          | RW   |

| PRT5DM1  | 15          | RW   |               | 55          |      | DEC1_CR0    | 95          | RW   | DEC1_CR   | D5          | RW   |

| PRT5IC0  | 16          | RW   |               | 56          |      |             | 96          |      |           | D6          |      |

| PRT5IC1  | 17          | RW   |               | 57          |      |             | 97          |      |           | D7          |      |

|          | 18          |      |               | 58          |      |             | 98          |      | MUX_CR0   | D8          | RW   |

|          | 19          |      |               | 59          |      |             | 99          |      | MUX_CR1   | D9          | RW   |