# プログラマブル システムオンチップ (PSoC®)

## 概要

PSoC® は、Arm® Cortex™ CPU ( シングルおよびマルチコア ) を内蔵したプログラマブル組込みシステム コントローラー ファミリ用の、拡張可能かつ再構成可能なプラットフォーム アーキテクチャです。超低消費電力 40nm プラットフォームに基づいて設計される PSoC 63 デバイス ファミリは、デュアル コア マイクロコントローラおよび低消費電力フラッシュ技術とデジタル プログラマブル ロジック、高性能アナログ - デジタルおよびデジタル - アナログ変換器、低消費電力コンパレータ、標準通信およびタイミング ペリフェラルの組合せです。PSoC 63 ファミリは、BLE 5.0 準拠のワイヤレス接続を提供します。

## 特徴

### 32 ビット デュアル コア CPU サブシステム

- シングル サイクルの乗算に対応した 150MHz Arm Cortex-M4F CPU ( 浮動小数点およびメモリ保護ユニット )

- 100MHz Cortex M0+ CPU

- ユーザー選択可能なコア ロジック動作 (1.1V または 0.9V)

- ハードウェアでサポートされるプロセッサ間の通信

- M4 と M0+ CPU のそれぞれに 8KB の 4 ウェイ セット アソシティブ命令キャッシュ

- 1.1V コア動作のアクティブ CPU 電力消費スロープ : チップ 電源電圧が 3.3V であり、内部降圧レギュレータがある場合、Cortex M4 は 40 $\mu$ A/MHz、Cortex M0+ は 20 $\mu$ A/MHz

- 0.9V コア動作のアクティブ CPU 電力消費スロープ : チップ 電源電圧が 3.3V であり、内部降圧レギュレータがある場合、Cortex M4 は 22 $\mu$ A/MHz、Cortex M0+ は 15 $\mu$ A/MHz

- それぞれ 16 チャネルずつの 2 つの DMA コントローラー

### フラッシュ メモリ サブシステム

- 32KB EEPROM 領域と 32KB セキュア フラッシュを含む 1MB アプリケーション フラッシュ

- 128 ビット幅 フラッシュ アクセスによる消費電力削減

- フラッシュ読み出し中に フラッシュ 更新を可能にする フラッシュ Read-While-Write (RWW)

- 保持粒度が選択可能な SRAM

- 288KB 内蔵 SRAM

- 32KB 保持境界 (32K ステップで 32K ~ 288K 保持可能)

- 検証およびセキュリティのためのワンタイム プログラマブル (OTP) E-Fuse メモリ

### Bluetooth Low Energy (Bluetooth Smart) BT 5.0 サブシステム

- 50Ω アンテナ駆動に対応する 2.4GHz RF トランシーバ

- デジタル PHY

- マスターとスレーブ モードに対応した Link Layer エンジン

- 最大 4dBm のプログラマブル出力パワー

- RX 感度 : -95dBm

- RSSI: 4dB 分解能

- 5.7mA TX (0dBm) と 6.7mA RX (2Mbps) 電流、3.3V バッテリ および 内部 SIMO 降圧コンバータを備える

- 4 つの接続を同時にサポートする Link Layer エンジン

- 2Mbps LE データ速度をサポート

### 低消費電力 (1.7V ~ 3.6V) 動作

- 細かい電源管理用のアクティブ、低消費電力アクティブ、スリープ、低消費電力スリープ、ディープ スリープ および ハイバネート モード

- 3.3V の外部電源と内部降圧レギュレータで、64K SRAM 保持 のディープ スリープ モード 電流は 7 $\mu$ A

- オンチップ Single In Multiple Out (SIMO) DC-DC 降圧コンバータ、1 $\mu$ A 未満の静止電流

- 64 バイト メモリとリアルタイムクロックを備えるバックアップ ドメイン

### 柔軟なクロッキング オプション

- オンチップ 水晶発振器 (4 ~ 33MHz の高速水晶および 32kHz 時計用水晶)

- クロック周波数遙倍用の位相ロック ループ (PLL)

- 精度が  $\pm 1\%$  の 8MHz 内部主発振器 (IMO)

- 精度が  $\pm 10\%$  の 超低消費電力の 32kHz 内部低速発振器 (ILO)

- 精度向上のために 32kHz WCO 入力にロック可能な IMO

- IMO 周波数遙倍用の周波数ロック ループ (FLL)

### シリアル通信

- 9 個の独立した実行時再設定可能なシリアル通信ブロック (SCB)。それぞれ I<sup>2</sup>C、SPI または UART としてソフトウェアで設定可能

### タイミングおよびパルス幅変調

- 32 個の 16 ビット タイマー／カウンター パルス幅変調器 (TCPWM) ブロック

- 中央揃え、エッジ、および疑似ランダム モード

- キル信号のコンパレータ ベースのトリガ

### 最大 78 個のプログラマブル GPIO

- 駆動モード、駆動強度およびスルーレートはプログラム可能

- 6 本の過電圧耐性 (OVT) ピン

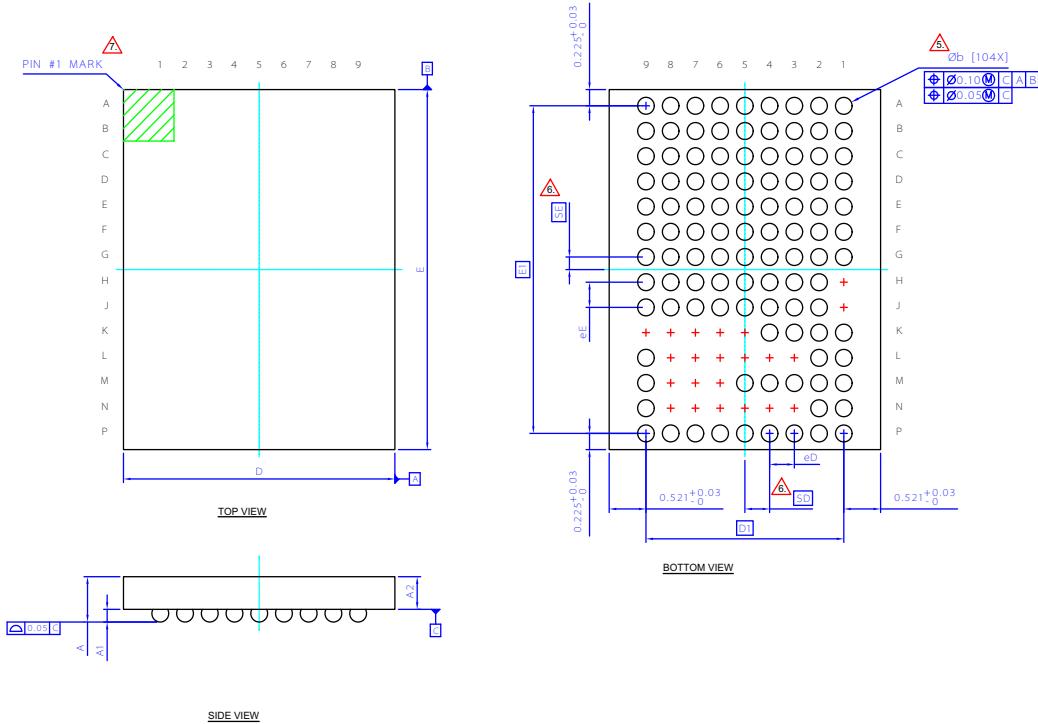

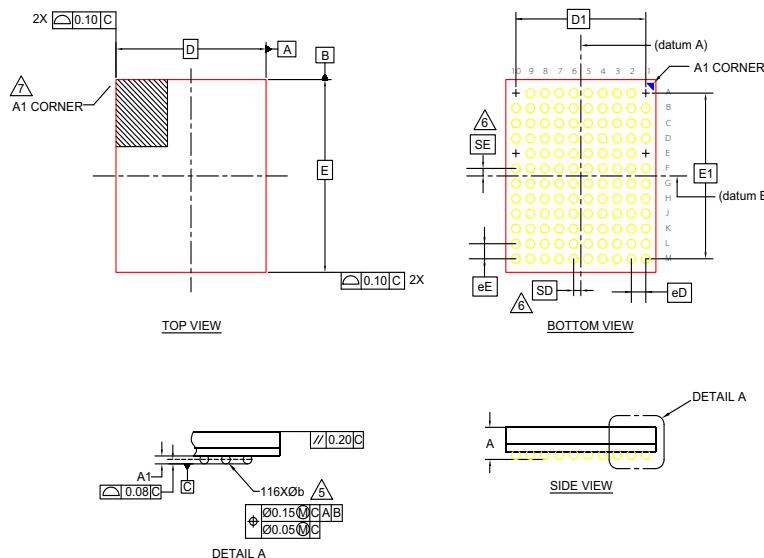

### パッケージ

- PSoC 6 と BLE 無線を備えた 116-BGA と 104-MCSP パッケージ

エラッタ : シリコン チップ エラッタに関する情報については、63 ページの「エラッタ」をご参照ください。詳細には、トリガー条件、影響を受けるデバイス、および提案する回避策が含まれています。

## オーディオ サブシステム

- I2S インターフェース。最大 192ksps ワード クロック

- ステレオ デジタル マイク用の 2 本の PDM チャネル

## QSPI インターフェース

- 外部 Quad-SPI フラッシュから直接実行 (Execute-In-Place、XIP)

- オンザフライの暗号化と復号化

- 低い消費電力でXIP性能を向上させる4KBのQSPIキャッシュ

- 1、2、4 およびデュアル - クアッド インターフェースに対応

## プログラマブル アナログ

- 差動とシングルエンド モードおよび信号加算平均に対応したチャネルシーケンサを備えた 12 ビットの 1Msps SAR ADC

- セトリング時間が 5μs 未満の 1 個の 12 ビット電圧モード DAC

- 低消費電力動作モードの 2 個のオペアンプ

- ディープスリープ モードおよびハイバネート モードで動作する 2 個の低消費電力コンバーラータ

- ADC に接続される内蔵の温度センサー

## プログラマブル デジタル

- 12 個のプログラマブルロジック ブロック、それぞれに 8 つのマクロセルと 1 つの 8 ビット データ パス (ユニバーサル デジタル ブロック (UDB) と呼ばれる)

- ドラッグ アンド ドロップ ブール プリミティブ (ゲート、レジスタ)、または Verilog プログラマブル ブロックとして使用可能

- サイプレス提供のペリフェラル コンポーネント ライブラリで UDB を使用し、通信ペリフェラル (LIN、UART、SPI、I<sup>2</sup>C、S/PDIF や他のプロトコル)、波形ジェネレータ、疑似ランダム シーケンス (PRS) などの機能が実装可能

- GPIO ピンを入出力とする信号に対するブール演算を可能にする Smart I/O (プログラマブル I/O) ブロック

- ディープスリープ中に利用可能な、Smart\_IO ブロックを備えた 2 つのポート

## 静電容量センシング

- クラス最高の SNR、耐水性および近接センシングを提供するサイプレスの静電容量シグマ - デルタ (CSD)

- 自己容量と相互容量の両方を動的に使用する相互静電容量センシング (サイプレス CSX)

- 非常に低い電流によるウェイク オン タッチ

- 静電容量センシングの設計を迅速かつ容易にするサイプレス 提供のソフトウェア コンポーネント

- 自動のハードウェア チューニング (SmartSense™)

## エネルギー プロファイラー

- 異なる電力モードに費やした時間の履歴を提供するブロック

- 消費エネルギーの監視および最適化用にソフトウェア エネルギー プロファイリングが可能

## PSoC Creator 設計環境

- 回路図設計の入力とアナログとデジタルの自動配線によるビルト、およびコード開発とデバッグを提供する統合開発環境

- すべての固定機能とプログラマブル ペリフェラル向けの アプリケーション プログラミング インターフェース (API コンポーネント)

- アプリケーション レベル関数の呼び出しおよびプロファイルを備えた Bluetooth Smart コンポーネント (BLE4.2 準拠 プロトコル スタック)

## 業界標準ツールとの互換性

- 回路図の入力後、開発は Arm ベースの業界標準開発ツールで行うことが可能

- PSoC Creator で設定してから、コード開発とデバッグのために Arm / Keil または IAR IDE ヘクスポート

- 業界標準の Arm トレース エミュレーション トレース モジュールに対応

## プラットフォーム アーキテクチャに組み込まれたセキュリティ

- ROM ベースの信頼のルートに基づく多面的なセキュア アーキテクチャ

- システム保護属性が確立するまで、セキュア ブートは割込み不可

- ハードウェア ハッシュを使用したブート時認証

- 実行イメージの段階的な認証

- 保護されたルーチンのために実行専用モードでのコードのセキュア実行

- すべてのデバッグとテスト イングレス パスは無効にできる

## 暗号化アクセラレータ

- 対称および非対称暗号メソッド (AES、3DES、RSA、ECC) およびハッシュ関数 (SHA-512、SHA-256) のハードウェア アクセラレーション

- 真の乱数生成器 (TRNG) 機能

## 詳細情報

サイプレスは、[www.cypress.com](http://www.cypress.com) に大量のデータを掲載しており、ユーザーがデザインに適切な PSoC デバイスを選択し、迅速かつ効率的にデザインに統合する手助けをしています。以下は PSoC 6 MCU のリソースの要約です。

### ■ 概要: PSoC ポートフォリオ、PSoC ロードマップ

### ■ 製品セレクタ: PSoC 6 MCU ページ

### ■ アプリケーション ノート: 基本レベルから上級レベルまでの幅広いトピックを提供します。

- [AN210781](#): Getting Started with PSoC 6 MCU BLE

- [AN218241](#): PSoC 6 MCU Hardware Design Considerations

- [AN213924](#): PSoC 6 MCU Bootloader Guide

- [AN215656](#): PSoC 6 MCU Dual-Core CPU System Design

- [AN219434](#): Importing PSoC Creator Code into an IDE

- [AN219528](#): PSoC 6 MCU Power Reduction Techniques

- [AN221111](#): PSoC 6 MCU: Creating a Secure System

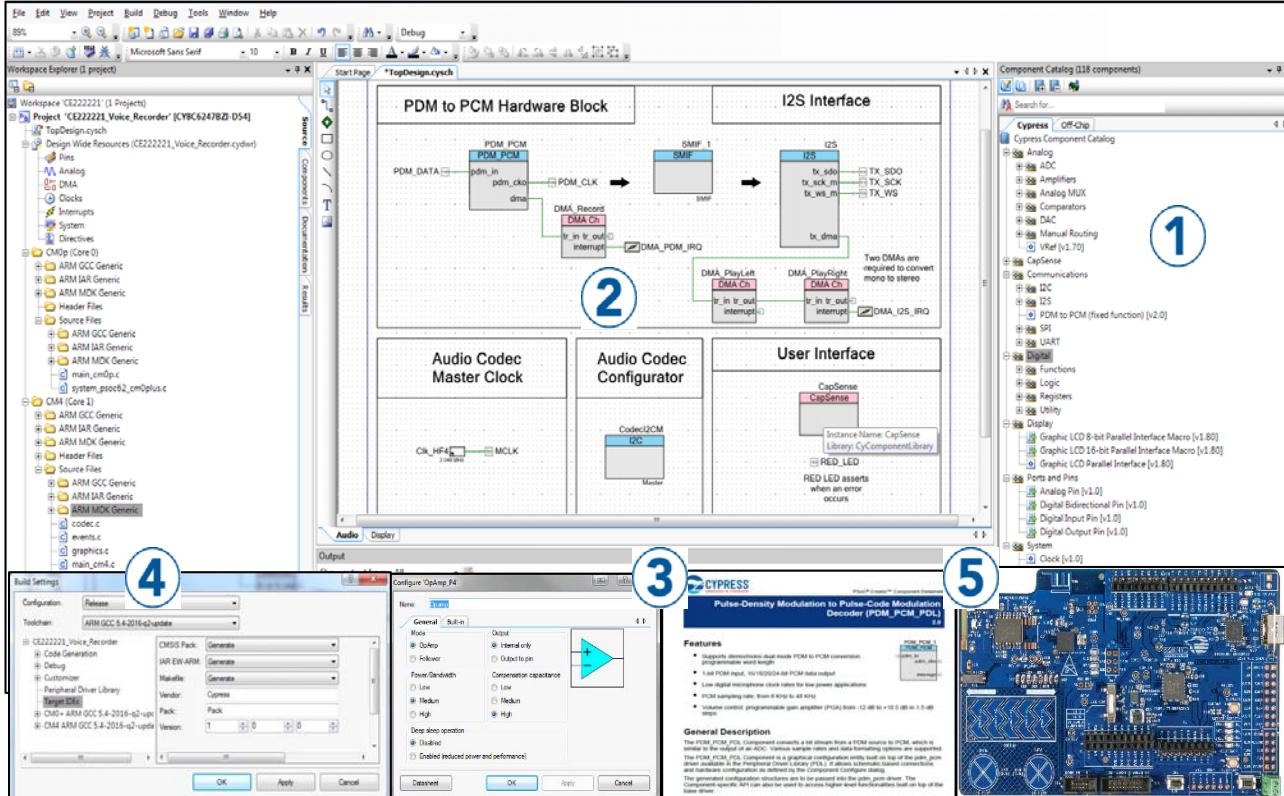

### PSoC Creator

PSoC Creator は無料で利用できる Windows ベースの統合設計環境 (IDE) です。このツールにより、お客様は PSoC 6 MCU のハードウェアとファームウェアシステムを同時に設計できます。PSoC Creator を使用すれば、以下のことができます。

1. 200 以上のコンポーネントを含むライブラリを利用

2. コンポーネントをドラッグ アンド ドロップして、メイン デザイン ワークスペースでハードウェアシステムデザインを構築

3. コンポーネント コンフィギュレーション ツールおよびコンポーネント データシートを使ってコンポーネントを設定

### ■ サンプル コード: 様々な製品機能と用途のために PSoC Creator サンプル プロジェクトを提供します。

### ■ テクニカル リファレンス マニュアル (TRM): PSoC 6 MCU アーキテクチャとレジスタの詳細な説明をします。

### ■ 開発ツール

- [CY8CKIT-062-Wi-Fi-BT](#): WiFi および Bluetooth 接続を備えた PSoC 62 シリーズ MCU に対応します。

- [CY8CKIT-062-BLE](#): Bluetooth Low-Energy (BLE) を備えた PSoC 63 シリーズ MCU に対応します。

### ■ トレーニングビデオ: PSoC Creator に関する幅広いビデオトレーニング リソースは [www.cypress.com/training](http://www.cypress.com/training) をご覧ください。

図 1. PSoC Creator の回路図入力およびコンポーネント

## 目次

|                           |    |

|---------------------------|----|

| ブロックおよび機能 .....           | 5  |

| 機能の説明 .....               | 6  |

| CPU およびメモリ サブシステム .....   | 6  |

| システム リソース .....           | 6  |

| BLE 無線およびサブシステム .....     | 7  |

| アナログ ブロック .....           | 7  |

| プログラマブル デジタル .....        | 8  |

| 固定機能デジタル .....            | 8  |

| GPIO .....                | 9  |

| 特殊機能ペリフェラル .....          | 9  |

| ピン配置 .....                | 10 |

| 電源 .....                  | 20 |

| 開発サポート .....              | 22 |

| ドキュメント .....              | 22 |

| オンライン .....               | 22 |

| ツール .....                 | 22 |

| 電気的仕様 .....               | 23 |

| 絶対最大定格 .....              | 23 |

| デバイス レベルの仕様 .....         | 23 |

| アナログ ペリフェラル .....         | 31 |

| デジタル ペリフェラル .....         | 39 |

| メモリ .....                 | 41 |

| システム リソース .....           | 42 |

| 注文情報 .....                | 54 |

| パッケージ .....               | 56 |

| 略号 .....                  | 59 |

| 本書の表記法 .....              | 62 |

| 測定単位 .....                | 62 |

| 正誤表 .....                 | 63 |

| 改訂履歴 .....                | 68 |

| セールス、ソリューションおよび法律情報 ..... | 69 |

| ワールドワイド販売と設計サポート .....    | 69 |

| 製品 .....                  | 69 |

| PSoC® ソリューション .....       | 69 |

| サイプレス開発者コミュニティ .....      | 69 |

| テクニカル サポート .....          | 69 |

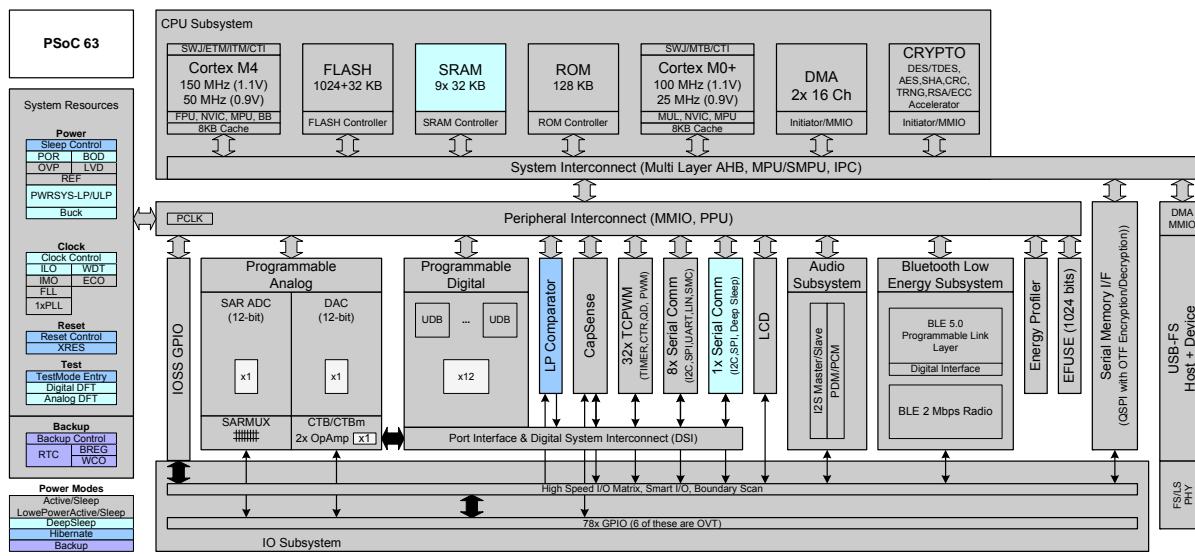

## ブロックおよび機能

PSoC 63 のブロック図を図 2 に示します。主なサブシステムは、CPU サブシステム、BLE サブシステム、システム リソース、ペリフェラル ブロックおよび I/O の 5 つのサブシステムです。

図 2. ブロック図

図 2 はチップのサブシステム、およびそれらの相互接続の非常に簡略化した図を示しています（実際には多層 AHB が使用されています）。カラーコーディングは、特定のブロックがまだ機能できる最低消費電力モードを示します（たとえば、LP コンパレータはディープ スリープ モードで機能します）。

PSoC 63 デバイスは、ハードウェアとファームウェアの両方についてプログラミング、テスト、デバッグおよびトレースの幅広いサポートを備えています。

デバッグオンチップ (DoC) 機能により、標準の量産デバイスを使用した最終システムでデバイスの完全なデバッグ処理が可能になります。専用のインターフェースやデバッグギング ポッド、シミュレータ、エミュレータは不要です。デバッグをサポートするために必要なものは、通常のプログラミングに使う接続だけです。

PSoC Creator 統合開発環境 (IDE) は、PSoC 63 デバイス用の完全に統合されたプログラミングとデバッグのサポートを提供します。SWJ (SWD および JTAG) インターフェースは、業界標準のサードパーティ製プローブと完全互換です。PSoC 63 ファミリは、デバッグ機能を無効にすることができます、非常に堅牢なフラッシュ保護に対応し、カスタマ独自の機能がオンチップ プログラマブル ブロックに実装できるようにするために、非常に高いセキュリティ レベルを提供します。

デバッグ回路はデフォルトで有効にされており、ファームウェアでのみ無効にすることができます。有効にされていない場合、再度有効にする唯一の方法は、デバイス全体を消去しフラッシュ保護をクリアしてデバッグ処理を有効にする新しいファームウェアでデバイスをプログラムし直すことです。

さらに、悪意を持ってデバイスを再プログラムすることに起因するフィッシング攻撃、またはフラッシュ プログラミング シーケンスを開始して割り込むことでセキュリティ システムを突破しようという意図が懸念されるアプリケーションに対して、すべてのデバイスインターフェースを恒久的に無効にすることができます。デバイスの最高レベルのセキュリティが有効になっている場合、すべてのプログラミング、デバッグおよびテスト インターフェースは無効にされます。セキュリティ レベルは、トレード オフの関係で利用できます。

## 機能の説明

### CPU およびメモリ サブシステム

#### CPU

PSoC 63 の CPU サブシステムは、2 つの Arm Cortex コアとその関連バスとメモリで構成されています。浮動小数点ユニットおよびメモリ保護ユニット (FPU および MPU) を備えた M4 および MPU を備えた M0+ です。Cortex M4 と M0+ には、8KB の 4 ウェイ セットアソシエイティブ命令キャッシュ (L1-Cache) があります。このサブシステムには、それぞれ 32 チャネルの独立 DMA コントローラー、暗号アクセラレータ ブロック、1MB のオンチップ フラッシュ、288KB の SRAM、および 128KB の ROM も含まれています。Cortex M0+ は、セキュアで割込み不可能なブート機能を提供します。これにより、ブート後にシステムの整合性は保護され、特権は適用されます。共有リソースは通常の Arm マルチレイヤバス アービトリエーションにてアクセスでき、排他アクセスはハードウェア セマフォおよび保護を実装するプロセッサ間通信 (IPC) スキームによってサポートされます。チップ電源電圧が 3.3V であり (内部降圧レギュレータが有効)、内部電源が 0.9V の場合、Cortex M4 と Cortex M0+ のアクティブ時消費電力はそれぞれ 26 $\mu$ A/MHz と 17 $\mu$ A/MHz です。

#### DMA コントローラー

それぞれ 16 チャネルの DMA コントローラーが 2 つあります。これらは、AHB マルチレイヤバスを使用して、ペリフェラルへの独立したアクセスをサポートします。

#### フラッシュ

PSoC 63 は 1MB のフラッシュ モジュール、長時間の保持のために EEPROM エミュレーションに使用できる追加の 32K のフラッシュ メモリ、および安全にロックでき、変更できない (ワンタイム プログラマブル) キーロックのみによりアクセスできる別個の 32KB のフラッシュ ブロックを搭載します。フラッシュ ブロックは、CPU がアクティブである間にフラッシュ 更新が実行できるように、RWW (Read-While-Write) 動作をサポートします。

#### 保持粒度 (Retention Granularity) が 32KB の SRAM

完全に保持されるか、またはユーザー指定の 32KB ブロック単位で保持できる 288 KB の SRAM メモリがあります。

#### SRAM

ブートおよびコンフィギュレーション ルーチンを含む監視 128KB ROM も提供されます。この ROM は、ユーザー フラッシュ の認証が必要な場合にセキュア ブートを保証します。

#### ワンタイム プログラマブル (OTP) eFuse

1024 ビットの OTP メモリは、チップごとに一意で変更不可能な識別子を提供できます。この変更不可能なキーは、セキュア フラッシュにアクセスするために使用されます。

## システム リソース

### 電源システム

電源システムは各モードに応じた電圧レベルを保証します。これを実現するために、機能の正常な動作に必要な電圧レベルを達成するまでモードへの移行を遅延させる (例えば、パワーオン リセット (POR) の時)、または電源が指定されたレベルを下回った場合にリセットを発生させます (電圧低下検出 (BOD))。このデザインは、電源電圧が規定されたレベル (例えば、1.7V) を下回ってからリセットが発生するまで安全なチップ動作を保証します。電圧シーケンスの要件はありません。VDD コア ロジック電源 (1.7 ~ 3.6V) は、1.1V または 0.9V のコア ロジック電源を生成するチップ搭載降圧レギュレータに供給します。動作周波数に応じて、降圧コンバータの静止電流は 1 $\mu$ A 未満になります。バックアップと呼ばれる個別の電源ドメインは備えられています。しかし、それは電源モードではありません。このドメインは VBACKUP ドメインから電力供給され、32kHz WCO、RTC およびバックアップ レジスタを含みます。バックアップ ドメインとして使用されない場合、VDD に接続されます。ポート 0 はこの電源から供給されます。ポート 0 のピン 5 (P0.5) は PMIC ウェイクアップ出力として設定できます (RTC によりクロック供給)。デフォルトで、P0.5 は抵抗プルアップ モードに駆動されます。

### クロック システム

PSoC 63 のクロック システムは、クロックを必要とするすべてのサブシステムにクロックを供給し、グリッチなしに異なるクロック ソース間で切り替えることを担当します。また、クロック システムはメタステーブル状態が発生しないように保証します。

PSoC 63 のクロック システムは、内蔵主発振器 (IMO)、内蔵速発振器 (ILO)、水晶発振器 (ECO および WCO)、PLL、FLL および外部クロック用の予備ピンから構成されます。PLL はスペクトラム拡散動作をサポートします。FLL は、PLL ロック イベント (最大 50 $\mu$ sかかる) を待つことなく、高速クロックで高速ウェイクアップを実現します。クロックはバッファリングされ、Smart I/O ポートのピンに引き出されます。

32kHz 発振器は、より高精度のクロックを使用して 2ppm 以内に調整可能です。ECO は  $\pm 20$ ppm の精度を提供し、外部水晶を使用します。

#### IMO クロック ソース

IMO は、PSoC 63 の内部クロックの第一供給源です。仕様の精度を達成するために出荷試験中に調整されます。デフォルト IMO 周波数は 8MHz です。IMO の許容誤差は  $\pm 1\%$  で、その電流消費は 10 $\mu$ A 未満です。より高い精度を得るために、IMO をより正確なクロック ソースにロックすることができます。32kHz WCO にロックすると、0.25% の精度が得られます。

#### ILO クロック ソース

ILO は超低消費電力発振器 (公称 32kHz) であり、ディープ スリープ モードでペリフェラルの動作用にクロックを生成するために使用することができます。ILO 駆動のカウンターは、精度を改善するために IMO に対して校正することができます。サイクロスは、校正を実行するソフトウェア コンポーネントを提供しています。

### ウォッチドッグ タイマー

ウォッチドッグ タイマーは、ILO または WCO をクロック ソースとして動作するクロック ブロックに実装されます。これにより、ウォッチドッグがディープ スリープ モードでも動作でき、タイムアウトが発生する前にウォッチドッグが処理されなかつた場合にリセットが生成されます。ウォッチドッグ リセットはリセット原因レジスタに記録されます。

### クロック分周器

ペリフェラルの使用とタイミングの目的で、整数と分数のクロック分周器が用意されています。クロック分周器は、非常に細かいクロック制御を可能にするために、長さが 16 および 24 ビットです。

### リセット

PSoC 63 は、ソフトウェア リセットを含む様々なソースからリセットできます。リセット イベントは非同期であり、デバイスを既知の状態に復帰させることが保証されています。リセットの原因は、リセット中にも保持され、ソフトウェアがリセットの原因を判断できるようにレジスタに記録されます。電源投入または再設定中にコンフィギュレーションおよび複数のピン機能に伴う複雑さを避けるために、XRES ピンが外部リセット用に確保されています。

### BLE 無線およびサブシステム

PSoC 63 は、物理層 (PHY) エンジンと Link Layer (LL) エンジンを含む Bluetooth Smart サブシステムおよび組み込みセキュリティ エンジンを内蔵しています。物理層は、Bluetooth Smart Bluetooth 仕様 5.0 に準拠している 2.4GHz ISM バンドを介して 2Mbps で GFSK パケットを送受信するデジタル PHY と RF トランシーバーからなります。ベースバンド コントローラーは、マスターとスレーブ モードの両方に対応する複合ハードウェアとファームウェア実装です。HCI やリンク制御などの重要なプロトコル要素はファームウェアに実装されます。暗号化、CRC、データ ホワイトニング、アクセス コード相関などのタイム クリティカルな機能ブロックはハードウェア (LL エンジン内) に実装されます。

RF トランシーバーは、マッチング/フィルタリング ネットワークを介して 50Ω アンテナを駆動するシングルエンド RF ポートピンを提供する集積バランを備えています。受信ではこのブロックで GFSK 復調を行って、アンテナからの RF 信号をデジタル ビット ストリームに変換します。送信ではこのブロックで GFSK 変調を行った後、デジタル ベースバンド信号を無線周波数に変換しアンテナから送信します。

BLESS の主な特長は以下の通りです：

- 論理リンク制御と適応プロトコル (L2CAP)、属性プロトコル (ATT)、セキュリティ マネージャ (SM) プロトコルに対応するマスターとスレーブ シングルモード プロトコル スタック

- 一般属性プロファイル (GATT)、一般アクセス プロファイル (GAP) および L2CAP への API アクセス

- L2CAP 接続向けチャネル (Bluetooth 4.1 の機能)

- GAP 機能

- ブロードキャスター、オブザーバー、ペリフェラル、セントラルの役割

- セキュリティ モード 1: レベル 1, 2, 3

- ユーザー定義の通知データ

- 複数の接続に対応

#### ■ GATT 機能

- GATT クライアントとサーバー

- GATT サブプロシージャに対応

- 32 ビット ユニバーサル 意識別子 (UUID)

(Bluetooth 4.1 機能)

#### ■ セキュリティ マネージャ (SM)

- ペアリング方式: Just works、Passkey Entry、Out of Band

- LE セキュア コネクション ペアリング モデル

- 認証済みの中間者攻撃 (MITM) 保護とデータ署名

#### ■ リンク層 (LL)

- マスターとスレーブの役割

- 128 ビット AES エンジン

- 低デューティ比通知

- LE Ping

#### ■ SIG が採用したすべての BLE プロファイルに対応

- Adv (1.28s, 31 バイト, 0dBm) と Con (300ms, 0byte, 0dBm) の電力レベルはそれぞれ 42 $\mu$ W と 70 $\mu$ W です。

### アナログ ブロック

#### 12 ビット SAR ADC

12 ビットかつ 1Msps の SAR ADC は 18MHz の最大クロックレートで動作でき、12 ビット変換を行なうためにその周波数で少なくとも 18 クロックを必要とします。

ユーザー向けにブロック機能を拡張するために、それにリファレンス バッファを追加し (±1% まで調整可能)、また  $V_{DD}$ 、 $V_{DD}/2$ 、 $V_{REF}$  の 3 つの内部基準電圧オプション (定格電圧が 1.024V) および GPIO ピンを介した外部基準電圧を選択できるようにします。サンプル ホールド (S/H) のアーチャがプログラマ可能であるため、SAR 入力を駆動するアンプのセトリング時間を規定するゲイン帯域幅要件を必要に応じて緩和することができます。適切なリファレンス電圧が使用され、システム ノイズ レベルが許す限り、システム性能は真の 12 ビット精度で 65dB です。ノイズの多い条件で性能を改善するために、内部リファレンス アンプに外部バイパス コンデンサを (固定したピン位置に) 用意することができます。

SAR は 8 入力シーケンサを介して、決められたピンに接続されます。シーケンサは、スイッチング オーバーヘッドの必要はなく、選択されたチャネルを自律的に巡回します (シーケンサ スキヤン) (つまり、合計サンプリング帯域幅は、単一のチャネルか複数のチャネルであるかにかかわらず 1Msps です)。シーケンサの切り替えは、スタート マシンまたはファームウェアによる切り替えにより行われます。シーケンサの 1 つの機能は、CPU 割込みサービスの要件を軽減するための各チャネルのバッファリングです。信号を様々なソース インピーダンスと周波数に適合させるために、チャネル毎に異なるサンプリング時間をプログラムすることができます。また、数値化された値がプログラムされた範囲を超えた場合、上限と下限のレンジ レジスタにより信号範囲を指定することにより、対応する範囲外の割込みとして処理されます。これにより、シーケンサ スキヤンが完了した後で CPU が値を読み出し、ソフトウェアにより値が範囲内であるかの確認を待たずに、範囲外の値を早く検出することができます。

SAR は、校正およびその他の温度に依存する機能のために、内蔵温度センサーの出力を数値化することができます。SAR は高速クロック（最大 18MHz）を必要とするため、ディープスリープとハイバネート モードに対応していません。SAR 動作範囲は 1.71V ~ 3.6V です。

#### 温度センサー

PSoC 63 は 1 個の温度センサーを内蔵しています。これは電流源によってバイアスされたダイオードからなります。この電流源は電力を節約するために無効にできます。温度センサーは ADC に接続されています。ここで校正と直線化を含むサイプレスが提供したソフトウェアを使用し、温度センサーの電圧を数値化し、温度の値を生成します。

#### 12 ビットのデジタル アナログ変換器

チップには、5μs 以内で安定する 12 ビット電圧モードの DAC が内蔵されています。DAC はユーザー定義の波形を生成するために DMA コントローラーによって駆動されます。チップからの DAC 出力は、抵抗ラダー出力（グランド近傍で高度にリニア）またはバッファ付き出力のいずれかです。

#### 2 個のオペアンプのある連続時間ブロック (CTBm)

このブロックは 2 つのオペアンプで構成されます。それらは入力と出力が固定ピンに接続され、3 つの電力モードとコンパレータ モードを備えています。これらのオペアンプの出力は、SAR 入力のバッファとして使用できます。これらのオペアンプの非反転入力は 2 つのピンのいずれかに接続することができ、従って、独立したセンサーを異なる時間に使用することができます。ピンの選択はファームウェアを使って行われます。オペアンプは 4 つの電力レベルのいずれかに設定できます。最低レベルは、ディープスリープ モードで低性能連続時間機能を実行できるようにディープスリープ モードでの動作を可能にします。DAC 出力はオペアンプにてバッファリングすることができます。

#### 低消費電力コンパレータ

PSoC 63 は、ディープスリープとハイバネート モードで動作できる低消費電力コンパレータの一対を内蔵しています。これにより、ディープスリープおよびハイバネート モード中に外部電圧レベルを監視する能力を維持しながらアナログシステム ブロックを無効にすることができます。コンパレータ出力は、システム ウェイクアップ回路がコンパレータの切り替えイベントによりアクティブになる非同期電力モード（ハイバネート）で動作する場合を除き、準安定状態を避けるため、通常同期化されています。

#### プログラマブル デジタル

##### Smart I/O

チップのサブシステムから GPIO ピンへの信号、またはチップに入力される信号に対してブール演算を可能にする 2 つの Smart I/O ブロックがあります。動作は同期または非同期であり、ブロックはディープスリープおよびハイバネートなどの低消費電力モードで動作します。これにより、例えば、より多くの電力を消費し、偽のウェイクアップを生成する可能性がある一般的な I/O 割込みでウェイクアップする代わりに、CPU がウェイクアップすべき論理条件の検出が可能になります。

##### ユニバーサル デジタル ブロック (UDB) およびポート インターフェース

PSoC 6 A-BLE は 12 個の UDB を内蔵しています。また UDB アレイは、通信と制御用にペリフェラルとポートからの信号を UDB に、また UDB を介して送信することを可能にする切り替えられたデジタルシステム相互接続 (DSI) ファブリックを提供しています。

#### 固定機能デジタル

##### タイマー／カウンター／PWM ブロック

タイマー／カウンター／PWM ブロックは、ユーザーがプログラム可能な周期長の 32 個のカウンターから構成されます。キャプチャレジスタは、I/O イベントなどのイベントの時にカウント値を記録します。周期レジスタは、カウンターのカウントが周期レジスタのカウントに等しくなる時にカウントを停止、または自動的にリロードします。比較レジスタは、PWM デューティ比の出力として使用される比較値信号を生成します。ブロックは真出力とコンプリメンタリー出力（それらの間のオフセットがプログラム可能）も提供しており、これらをプログラム可能なデッドバンド付きコンプリメンタリー PWM 出力として使用することを可能にします。また、出力を事前に決定された状態に移行させるキル (Kill) 入力もあります。例えば、モーター駆動システムでは、過電流状態となり FET を駆動している PWM をソフトウェアの介入なしに直ちに止める必要がある時、キル入力が使用されます。8 個の 32 ビット カウンターと 24 個の 16 ビット カウンターがあります。

##### シリアル通信ブロック (SCB)

PSoC 63 は 9 個の SCB を内蔵しています。それぞれ I<sup>2</sup>C、UART、または SPI インターフェースを実装できます。1 つの SCB はディープスリープで動作し、外部クロックによりクロック供給されます。この SCB はスレーブ モードでのみ動作します（外部クロックが必要）。

**I<sup>2</sup>C モード** : ハードウェア I<sup>2</sup>C ブロックは、完全なマルチマスターとスレーブ インターフェースを実装します（マルチマスターのアービトレーションが可能）。このブロックは、最大 1Mbps (ファースト モード プラス) で動作でき、CPU 用の割込みオーバヘッドとレイテンシを削減するためにバッファリング オプションを柔軟に選択できます。また、PSoC 63 のメモリでメールボックス アドレス範囲を作り、メモリ アレイへの読み出しと書き込みの I<sup>2</sup>C 通信を効果的に削減する EzI<sup>2</sup>C にも対応しています。更に、ブロックは送受信用に深さ 8 の FIFO にも対応しています。これは、CPU がデータを読み出す一定の時間を増加することで、時間通りに CPU が読み出すデータがないことに起因したクロック ストレッチの必要性を大幅に低減します。FIFO モードはすべてのチャネルに対応し、DMA がない場合に非常に有用です。

I<sup>2</sup>C ペリフェラルは、NXP I<sup>2</sup>C バス仕様とユーザー マニュアル (UM10204) で定義された通りに I<sup>2</sup>C 標準モード、ファースト モード、ファースト モード プラスのデバイスと互換性があります。I<sup>2</sup>C バス I/O は、オープンドレイン モードにある GPIO を使って実装されます。

**UART モード** : これは最大 1Mbps で動作するフル機能の UART です。基本の UART プロトコルから少し発展した車載向けシングルワイヤ インターフェース (LIN)、赤外線インターフェース (IrDA)、SmartCard (ISO7816) プロトコルに対応しています。また、共通の RX と TX ラインを介して接続したペリフェラルのアドレス指定を可能にする 9 ビット マルチプロセッサ モードに対応しています。パリティ エラー、ブレーク検出、フレーム エラーなどの一般的な UART 機能がサポートされています。深さ 8 の FIFO は、非常に大きい CPU サービス レイテンシを許容します。

**SPI モード** : SPI モードは Motorola SPI、TI セキュア シンプルペアリング (SSP) (SPI コーデックの同期化用の開始パルスを本質的に追加)、National Microwire (半二重の SPI) に完全に対応しています。SPI ブロックは FIFO を使用することができます、データ交換がメモリ内のアレイへの読み書きまで簡略化された EzSPI モードにも対応しています。SPI インターフェースは 48MHz の SPI クロックで動作します。

USB フルスピード デュアル ロール ホストおよびデバイス インターフェース

PSoC 6A-BLE-2 には、デュアル ロール USB ホストおよびデバイス インターフェースが搭載されます。デバイスは、最大 8 つのエンドポイントを持つことができます。512 バイトの SRAM バッファが用意され、DMA がサポートされます。

#### QSPI インターフェース

80MHz で動作する Quad-SPI (QSPI) インターフェース (1,2 または 4 ビット幅に選択可能) も備えています。また、このブロックでは、適度な速度で直接実行の動作をサポートするために動作中の暗号化と復号化も用意されます。

#### GPIO

PSoC 63 は最大 104 の GPIO があります。GPIO ブロックは以下を実装します：

■ 8 つの駆動強度モード：

- アナログ入力モード (入力と出力バッファが無効)

- 入力のみ

- 弱プルアップ、強プルダウン

- 強プルアップ、弱プルダウン

- オープンドレイン、強プルダウン

- オープンドレイン、強プルアップ

- 強プルアップ、強プルダウン

- 弱プルアップ、弱プルダウン

■ 入力閾値選択 (CMOS または LVTTL)

■ 前のステートをラッチするためのホールド モード (ディープスリープ モードとハイバネート モードで I/O ステートを維持するため)

■ EMI を改善するために、dV/dt に起因するノイズを制御するために選択可能なスルーレート

ピンは、8 ビット幅のポートと呼ばれる論理エンティティに構成されています。電源投入とリセットの間、入力に過電流を与える、過剰なターンオン電流を発生させないために、ブロックは無効状態にされます。高速 I/O マトリックス (HSIOM) として知られている多重化ネットワークは、I/O ピンに接続できる複数の信号間を多重化するのに使用されます。データ出力とピンステートレジスタは、それぞれピン上で駆動される値とそれらのピンの状態を格納します。

各 I/O ピンは有効になった場合に割込みを生成でき、各 I/O ポートにはそれに対応する割込み要求 (IRQ) と割込みサービスルーチン (ISR) ベクタがあります。6 つの GPIO ピンは、入力電圧が VDD よりも高い過電圧耐性 (OVT) 動作に対応することができます。これらのピンは、機能に影響を与えることなく、動作中の I<sup>2</sup>C バスへの物理接続を維持しながらチップの電源を切るために I<sup>2</sup>C 機能に使用される場合があります。

GPIO ピンは、16mA またはそれ以上の電流を吸い込むために連結することができます。GPIO ピンは 3.6V より高くプルアップすることができません。

#### 特殊機能ペリフェラル

##### CapSense

CapSense は、アナログ マルチプレクサ バスに接続できる CapSense シグマ - デルタ (CSD) ブロックにより、PSoC 63 のすべてのピンでサポートされています。どの GPIO ピンもアナログ スイッチを介してこの AMUX バスに接続できます。従って、CapSense 機能はソフトウェアで制御されて、システム内のいかなる使用可能なピンやピン グループに提供することができます。使い易さのために、サイプレスは CapSense ブロックのソフトウェア コンポーネントを提供しています。

シールド電圧は、耐水機能を実現するために他の多重化バス上で駆動することができます。耐水性は、シールド電極を検知電極と同位相で駆動して提供されます。その検知電極はシールド静電容量が検知された入力を減衰させることを防ぐためのものです。近接センシングも実装することができます。

CapSense ブロックは高性能で、低ノイズのプログラマブル ブロックです (感度と柔軟性を向上させるためにリファレンス電圧と電流源の範囲をプログラム可能)。さらに、外部リファレンス電圧も利用できます。VDDA およびグランドのセンシングを代替し、消費電力関連ノイズをゼロにする全波 CSD モードがあります。

CapSense ブロックは、2 個の 7 ビット IDAC を備えています。これらは、CapSense を使用しない (両方の IDAC とも使用可能) 場合、または CapSense の耐水機能を利用しない場合 (どちらか一方の IDAC が使用可能)、一般用途に使用することができます。IDAC の 1 つを使用することにより、(低速の) 10 ビット スロープ ADC を実現できます。

このブロックは、スワイプ、タップ、タッチによるウェイクアップ (1.8V で 3 $\mu$ A 未満)、相互容量、および他のタイプなどのセンシング機能を実装することができます。

##### オーディオ サブシステム

このサブシステムは、I2S ブロックと 2 つの PDM チャネルで構成されています。PDM チャネルは、PDM マイクのビットストリーム出力とインターフェースします。PDM 処理チャネルはドループ補正を提供し、384kHz ~ 3.072MHz のクロック速度で動作でき、最大 48ksps のオーディオサンプリング速度で 16 ~ 24 ビットのワード長を生成します。

I2S インターフェースは、最大 192ksps のワード クロック レート (8 ビット ~ 32 ビットのワード) でマスター モードとスレーブ モードの両方をサポートします。

## ピン配置

表1. 116-BGA と 104-MCSP パッケージのピン配置

| 104-MCSP-BLE |         | 116-BGA-BLE                      |         |

|--------------|---------|----------------------------------|---------|

| ピン           | 名称      | ピン                               | 名称      |

| C7           | VCCD    | A2                               | VCCD    |

| C6           | VDDD    | B1                               | VDDD    |

| C9           | VBACKUP | C1                               | VBACKUP |

| D8           | P0.0    | C2                               | P0.0    |

| E6           | P0.1    | D3                               | P0.1    |

| D9           | P0.2    | E4                               | P0.2    |

| E7           | P0.3    | E3                               | P0.3    |

| E8           | P0.4    | F3                               | P0.4    |

| E9           | P0.5    | D2                               | P0.5    |

| E5           | XRES    | E2                               | XRES    |

| F5           | P1.0    | G3                               | P1.0    |

| F6           | P1.1    | F2                               | P1.1    |

|              |         | J5                               | P1.2    |

| F9           | P1.3    | J4                               | P1.3    |

| F8           | P1.4    | J3                               | P1.4    |

| F7           | P1.5    | J2                               | P1.5    |

| G9           | VDD_NS  | H3                               | VDD_NS  |

| G8           | VIND1   | F1                               | VIND1   |

| H8           | VIND2   | G1                               | VIND2   |

| J8           | VBUCK1  | G2                               | VBUCK1  |

| H9           | VRF     | H1                               | VRF     |

| L9           | VDDR1   | L2                               | VDDR1   |

| N9           | VSSR    | J1、K2、K3、K4、K5、L1、L3、L4、L5、M3、M8 |         |

| M9           | ANT     | K1                               | ANT     |

| M9           | ANT     | K1                               | ANT     |

| K2           | P6.1    | J8                               | P6.1    |

| M2           | P6.2    | L9                               | P6.2    |

| L1           | P6.3    | K9                               | P6.3    |

| J2           | P6.4    | J9                               | P6.4    |

| K1           | P6.5    | M10                              | P6.5    |

| N2           | P6.6    | L10                              | P6.6    |

| M1           | P6.7    | K10                              | P6.7    |

| 104-MCSP-BLE |          | 116-BGA-BLE                      |          |

|--------------|----------|----------------------------------|----------|

| ピン           | 名称       | ピン                               | 名称       |

| N9           | VSSR     | J1、K2、K3、K4、K5、L1、L3、L4、L5、M3、M8 |          |

| P9           | VDDR2    | M1                               | VDDR2    |

| P6,P7        | VSSR     | J1、K2、K3、K4、K5、L1、L3、L4、L5、M3、M8 |          |

| P8           | VDDR3    | M2                               | VDDR3    |

| P1           | VSS      | J1、K2、K3、K4、K5、L1、L3、L4、L5、M3、M8 |          |

| M5           | XI       | M4                               | XI       |

| P5           | XO       | M5                               | XO       |

| M3           | VSSR     | J1、K2、K3、K4、K5、L1、L3、L4、L5、M3、M8 |          |

| M4           | DVDD     | M6                               | DVDD     |

| P1           | VSS      | J1、K2、K3、K4、K5、L1、L3、L4、L5、M3、M8 |          |

| P4           | VDCDC    | M7                               | VDCDC    |

| P2           | NC       |                                  |          |

| P3           | VSSR     | J1、K2、K3、K4、K5、L1、L3、L4、L5、M3、M8 |          |

| L2           | VDDR_HVL | L7                               | VDDR_HVL |

| J7           | P5.0     | L6                               | P5.0     |

| J5           | P5.1     | K6                               | P5.1     |

| J6           | P5.2     | J6                               | P5.2     |

| H7           | P5.3     | K7                               | P5.3     |

| H6           | P5.4     | J7                               | P5.4     |

| J4           | P5.5     | L8                               | P5.5     |

| K3           | P5.6     | M9                               | P5.6     |

| K4           | P5.7     |                                  |          |

| L2           | VDDR_HVL | L7                               | VDDR_HVL |

| L2           | VDDR_HVL | L7                               | VDDR_HVL |

| J3           | P6.0     | K8                               | P6.0     |

| B2           | P10.1    | A8                               | P10.1    |

| C3           | P10.2    | F6                               | P10.2    |

| E4           | P10.3    | E6                               | P10.3    |

| A2           | P10.4    | D6                               | P10.4    |

| A3           | P10.5    | B7                               | P10.5    |

| D5           | P10.6    | A7                               | P10.6    |

| B3           | P10.7    |                                  |          |

**表1. 116-BGA と 104-MCSP パッケージのピン配置(続き)**

| 104-MCSP-BLE |        | 116-BGA-BLE |        |

|--------------|--------|-------------|--------|

| ピン           | 名称     | ピン          | 名称     |

| N1           | P7.0   | J10         | P7.0   |

| G6           | P7.1   | H10         | P7.1   |

| H4           | P7.2   | H8          | P7.2   |

| G5           | P7.3   | H7          | P7.3   |

| H3           | P7.4   | H6          | P7.4   |

| H2           | P7.5   | G9          | P7.5   |

| G3           | P7.6   | G8          | P7.6   |

| G2           | P7.7   | G7          | P7.7   |

| D1           | VDDIO1 | G10         | VDDIO1 |

| G4           | P8.0   | F10         | P8.0   |

| G1           | P8.1   | F9          | P8.1   |

| F3           | P8.2   | F8          | P8.2   |

| F2           | P8.3   | F7          | P8.3   |

| F1           | P8.4   | G6          | P8.4   |

| E3           | P8.5   | E9          | P8.5   |

| E1           | P8.6   | E8          | P8.6   |

| E2           | P8.7   | E7          | P8.7   |

| A1           | VDDA   | A9          | VDDA   |

| D2           | P9.0   | D10         | P9.0   |

| C1           | P9.1   | D9          | P9.1   |

| D3           | P9.2   | D8          | P9.2   |

| B1           | P9.3   | D7          | P9.3   |

|              |        | C10         | P9.4   |

|              |        | C9          | P9.5   |

|              |        | C8          | P9.6   |

|              |        | C7          | P9.7   |

| 104-MCSP-BLE |        | 116-BGA-BLE    |        |

|--------------|--------|----------------|--------|

| ピン           | 名称     | ピン             | 名称     |

| C4           | P11.0  | F5             | P11.0  |

| C5           | P11.1  | E5             | P11.1  |

| D6           | P11.2  | D5             | P11.2  |

|              |        | B10            | VREF   |

| A1           | VDDA   | A9             | VDDA   |

| A1           | VDDA   | A9             | VDDA   |

| C2           | P10.0  | B8             | P10.0  |

| B4           | P11.3  | C6             | P11.3  |

| A4           | P11.4  | B6             | P11.4  |

| B5           | P11.5  | A6             | P11.5  |

| A5           | P11.6  | B5             | P11.6  |

| A6           | P11.7  | A5             | P11.7  |

| B6           | VDDIO0 | B3             | VDDIO0 |

| D7、D4、F4、G7  | VSS    | B2、B9、H2、H9、D1 | VSS    |

| B7           | P12.0  | A4             | P12.0  |

| A7           | P12.1  | B4             | P12.1  |

| B8           | P12.2  | C4             | P12.2  |

| A8           | P12.3  | A3             | P12.3  |

| C8           | P12.4  | C5             | P12.4  |

|              |        | D4             | P12.5  |

|              |        | G5             | P12.6  |

|              |        | H5             | P12.7  |

| A9           | P13.0  | H4             | P13.0  |

| B9           | P13.1  | G4             | P13.1  |

|              |        | F4             | P13.6  |

|              |        | C3             | P13.7  |

パッケージ タイプに応じたポートへの電源の対応は次のとおりです。

- P0: VBACKUP

- P1: VDDD。ポート 1 のピンは過電圧耐性 (OVT) です。

- P5、P6、P7、P8: VDDIO1

- P9、P10: VDDA

- P11、P12、P13: VDDIO0

各ポートピンには複数の代替機能があります。表 2 に示します。

表 2. 複数の代替機能

| ポート／ピン | ACT #0                   | ACT #1                    | DS #2 | ACT #4         | ACT #5            | ACT #6           | ACT #7               | ACT #8               | ACT #9             | ACT #10                | ACT #12                | ACT #13 | ACT #14 | ACT #15 | DS #4 | DS #5           | DS #6 |

|--------|--------------------------|---------------------------|-------|----------------|-------------------|------------------|----------------------|----------------------|--------------------|------------------------|------------------------|---------|---------|---------|-------|-----------------|-------|

| P0.0   | tcpwm[0].line[0]:0       | tcpwm[1].line[0]:0        |       | srss.ext_clk:0 |                   |                  |                      | scb[0].spi_select1:0 |                    |                        | peri.tr_io_input[0]:0  |         |         |         |       |                 |       |

| P0.1   | tcpwm[0].line_compl[0]:0 | tcpwm[1].line_compl[0]:0  |       |                |                   |                  |                      | scb[0].spi_select2:0 |                    |                        | peri.tr_io_input[1]:0  |         |         |         |       | cpuss.swj_trstn |       |

| P0.2   | tcpwm[0].line[1]:0       | tcpwm[1].line[1]:0        |       |                | scb[0].uart_rx:0  | scb[0].i2c_scl:0 | scb[0].spi_miso:0    |                      |                    |                        |                        |         |         |         |       |                 |       |

| P0.3   | tcpwm[0].line_compl[1]:0 | tcpwm[1].line_compl[1]:0  |       |                | scb[0].uart_tx:0  | scb[0].i2c_sda:0 | scb[0].spi_miso:0    |                      |                    |                        |                        |         |         |         |       |                 |       |

| P0.4   | tcpwm[0].line[2]:0       | tcpwm[1].line[2]:0        |       |                | scb[0].uart_rts:0 |                  | scb[0].spi_clk:0     |                      |                    |                        | peri.tr_io_output[0]:2 |         |         |         |       |                 |       |

| P0.5   | tcpwm[0].line_compl[2]:0 | tcpwm[1].line_compl[2]:0  |       | srss.ext_clk:1 | scb[0].uart_cts:0 |                  | scb[0].spi_select0:0 |                      |                    |                        | peri.tr_io_output[1]:2 |         |         |         |       |                 |       |

| P1.0   | tcpwm[0].line[3]:0       | tcpwm[1].line[3]:0        |       |                | scb[7].uart_rx:0  | scb[7].i2c_scl:0 | scb[7].spi_miso:0    |                      |                    | peri.tr_io_input[2]:0  |                        |         |         |         |       |                 |       |

| P1.1   | tcpwm[0].line_compl[3]:0 | tcpwm[1].line_compl[3]:0  |       |                | scb[7].uart_tx:0  | scb[7].i2c_sda:0 | scb[7].spi_miso:0    |                      |                    | peri.tr_io_input[3]:0  |                        |         |         |         |       |                 |       |

| P1.2   | tcpwm[0].line[4]:4       | tcpwm[1].line[12]:1       |       |                | scb[7].uart_rts:0 |                  | scb[7].spi_clk:0     |                      |                    |                        |                        |         |         |         |       |                 |       |

| P1.3   | tcpwm[0].line_compl[4]:4 | tcpwm[1].line_compl[12]:1 |       |                | scb[7].uart_cts:0 |                  | scb[7].spi_select0:0 |                      |                    |                        |                        |         |         |         |       |                 |       |

| P1.4   | tcpwm[0].line[5]:4       | tcpwm[1].line[13]:1       |       |                |                   |                  | scb[7].spi_select1:0 |                      |                    |                        |                        |         |         |         |       |                 |       |

| P1.5   | tcpwm[0].line_compl[5]:4 | tcpwm[1].line_compl[14]:1 |       |                |                   |                  | scb[7].spi_select2:0 |                      |                    |                        |                        |         |         |         |       |                 |       |

| P5.0   | tcpwm[0].line[4]:0       | tcpwm[1].line[4]:0        |       |                | scb[5].uart_rx:0  | scb[5].i2c_scl:0 | scb[5].spi_miso:0    |                      | audioss.clk_i2s_if | peri.tr_io_input[10]:0 |                        |         |         |         |       |                 |       |

| P5.1   | tcpwm[0].line_compl[4]:0 | tcpwm[1].line_compl[4]:0  |       |                | scb[5].uart_tx:0  | scb[5].i2c_sda:0 | scb[5].spi_miso:0    |                      | audioss.tx_sck     | peri.tr_io_input[11]:0 |                        |         |         |         |       |                 |       |

| P5.2   | tcpwm[0].line[5]:0       | tcpwm[1].line[5]:0        |       |                | scb[5].uart_rts:0 |                  | scb[5].spi_clk:0     |                      | audioss.tx_ws      |                        |                        |         |         |         |       |                 |       |

| P5.3   | tcpwm[0].line_compl[5]:0 | tcpwm[1].line_compl[5]:0  |       |                | scb[5].uart_cts:0 |                  | scb[5].spi_select0:0 |                      | audioss.tx_sdo     |                        |                        |         |         |         |       |                 |       |

| P5.4   | tcpwm[0].line[6]:0       | tcpwm[1].line[6]:0        |       |                |                   |                  | scb[5].spi_select1:0 |                      | audioss.rx_sck     |                        |                        |         |         |         |       |                 |       |

| P5.5   | tcpwm[0].line_compl[6]:0 | tcpwm[1].line_compl[6]:0  |       |                |                   |                  | scb[5].spi_select2:0 |                      | audioss.rx_ws      |                        |                        |         |         |         |       |                 |       |

表 2. 複数の代替機能 ( 続き )

| ポート／<br>ピン | ACT #0                         | ACT #1                        | DS #2                | ACT #4 | ACT #5 | ACT #6                | ACT #7               | ACT #8                   | ACT #9                | ACT #10            | ACT #12                    | ACT #13                   | ACT #14                               | ACT #15                   | DS #4 | DS #5                    | DS #6                    |  |

|------------|--------------------------------|-------------------------------|----------------------|--------|--------|-----------------------|----------------------|--------------------------|-----------------------|--------------------|----------------------------|---------------------------|---------------------------------------|---------------------------|-------|--------------------------|--------------------------|--|

| P5.6       | tcpwm[0].i<br>ne[7]:0          | tcpwm[1].line<br>[7]:0        |                      |        |        |                       |                      | scb[5].spi<br>_select3:0 |                       | audioss.rx<br>_sdi |                            |                           |                                       |                           |       |                          |                          |  |

| P5.7       | tcpwm[0].i<br>ne_comp<br>[7]:0 | tcpwm[1].line<br>_compl[7]:0  |                      |        |        |                       |                      | scb[3].spi<br>_select3:0 |                       |                    |                            |                           |                                       |                           |       |                          |                          |  |

| P6.0       | tcpwm[0].i<br>ne[0]:1          | tcpwm[1].line<br>[8]:0        | scb[8].i2<br>c_scl:0 |        |        | scb[3].ua<br>rt_rx:0  | scb[3].i2<br>c_scl:0 | scb[3].spi<br>_mosi:0    |                       |                    |                            | cpuss.fault<br>_out[0]    |                                       |                           |       | scb[8].spi<br>_mosi:0    |                          |  |

| P6.1       | tcpwm[0].i<br>ne_comp<br>[0]:1 | tcpwm[1].line<br>_compl[8]:0  | scb[8].i2<br>c_sda:0 |        |        | scb[3].ua<br>rt_tx:0  | scb[3].i2<br>c_sda:0 | scb[3].spi<br>_miso:0    |                       |                    |                            | cpuss.fault<br>_out[1]    |                                       |                           |       | scb[8].spi<br>_miso:0    |                          |  |

| P6.2       | tcpwm[0].i<br>ne[1]:1          | tcpwm[1].line<br>[9]:0        |                      |        |        | scb[3].ua<br>rt_rts:0 |                      | scb[3].spi<br>_clk:0     |                       |                    |                            |                           |                                       |                           |       | scb[8].spi<br>_clk:0     |                          |  |

| P6.3       | tcpwm[0].i<br>ne_comp<br>[1]:1 | tcpwm[1].line<br>_compl[9]:0  |                      |        |        | scb[3].ua<br>rt_cts:0 |                      | scb[3].spi<br>_select0:0 |                       |                    |                            |                           |                                       |                           |       | scb[8].spi<br>_select0:0 |                          |  |

| P6.4       | tcpwm[0].i<br>ne[2]:1          | tcpwm[1].line<br>[10]:0       | scb[8].i2<br>c_scl:1 |        |        | scb[6].ua<br>rt_rx:2  | scb[6].i2<br>c_scl:2 | scb[6].spi<br>_mosi:2    |                       |                    | peri.tr_io_i<br>nput[12]:0 | peri.tr_io<br>output[0]:1 |                                       |                           |       | cpuss.swj_<br>swo_tdo    | scb[8].spi<br>_mosi:1    |  |

| P6.5       | tcpwm[0].i<br>ne_comp<br>[2]:1 | tcpwm[1].line<br>_compl[10]:0 | scb[8].i2<br>c_sda:1 |        |        | scb[6].ua<br>rt_tx:2  | scb[6].i2<br>c_sda:2 | scb[6].spi<br>_miso:2    |                       |                    | peri.tr_io_i<br>nput[13]:0 | peri.tr_io<br>output[1]:1 |                                       |                           |       | cpuss.swj_<br>swdoe_tdi  | scb[8].spi<br>_miso:1    |  |

| P6.6       | tcpwm[0].i<br>ne[3]:1          | tcpwm[1].line<br>[11]:0       |                      |        |        | scb[6].ua<br>rt_rts:2 |                      | scb[6].spi<br>_clk:2     |                       |                    |                            |                           |                                       |                           |       | cpuss.swj_<br>swdio_tms  | scb[8].spi<br>_clk:1     |  |

| P6.7       | tcpwm[0].i<br>ne_comp<br>[3]:1 | tcpwm[1].line<br>_compl[11]:0 |                      |        |        | scb[6].ua<br>rt_cts:2 |                      | scb[6].spi<br>_select0:2 |                       |                    |                            |                           |                                       |                           |       | cpuss.swj_<br>swclk_tclk | scb[8].spi<br>_select0:1 |  |

| P7.0       | tcpwm[0].i<br>ne[4]:1          | tcpwm[1].line<br>[12]:0       |                      |        |        | scb[4].ua<br>rt_rx:1  | scb[4].i2<br>c_scl:1 | scb[4].spi<br>_mosi:1    |                       |                    | peri.tr_io_i<br>nput[14]:0 |                           | cpuss.trace_-<br>clock                |                           |       |                          |                          |  |

| P7.1       | tcpwm[0].i<br>ne_comp<br>[4]:1 | tcpwm[1].line<br>_compl[12]:0 |                      |        |        | scb[4].ua<br>rt_tx:1  | scb[4].i2<br>c_sda:1 | scb[4].spi<br>_miso:1    |                       |                    | peri.tr_io_i<br>nput[15]:0 |                           |                                       |                           |       |                          |                          |  |

| P7.2       | tcpwm[0].i<br>ne[5]:1          | tcpwm[1].line<br>[13]:0       |                      |        |        | scb[4].ua<br>rt_rts:1 |                      | scb[4].spi<br>_clk:1     |                       |                    |                            |                           |                                       |                           |       |                          |                          |  |

| P7.3       | tcpwm[0].i<br>ne_comp<br>[5]:1 | tcpwm[1].line<br>_compl[13]:0 |                      |        |        | scb[4].ua<br>rt_cts:1 |                      | scb[4].spi<br>_select0:1 |                       |                    |                            |                           |                                       |                           |       |                          |                          |  |

| P7.4       | tcpwm[0].i<br>ne[6]:1          | tcpwm[1].line<br>[14]:0       |                      |        |        |                       |                      | scb[4].spi<br>_select1:1 |                       |                    |                            |                           | bless.ext_l-<br>na_rx_ctl_out         | cpuss.trac<br>e_data[3]:2 |       |                          |                          |  |

| P7.5       | tcpwm[0].i<br>ne_comp<br>[6]:1 | tcpwm[1].line<br>_compl[14]:0 |                      |        |        |                       |                      | scb[4].spi<br>_select2:1 |                       |                    |                            |                           | bless.ext_pa_t<br>x_ctl_out           | cpuss.trac<br>e_data[2]:2 |       |                          |                          |  |

| P7.6       | tcpwm[0].i<br>ne[7]:1          | tcpwm[1].line<br>[15]:0       |                      |        |        |                       |                      | scb[4].spi<br>_select3:1 |                       |                    |                            |                           | bless.ext_pa_l-<br>na_chip_en_ou<br>t | cpuss.trac<br>e_data[1]:2 |       |                          |                          |  |

| P7.7       | tcpwm[0].i<br>ne_comp<br>[7]:1 | tcpwm[1].line<br>_compl[15]:0 |                      |        |        |                       |                      | scb[3].spi<br>_select1:0 | cpuss.clk_<br>fm_pump |                    |                            |                           |                                       | cpuss.trac<br>e_data[0]:2 |       |                          |                          |  |

表 2. 複数の代替機能 ( 続き )

| ポート／<br>ピン | ACT #0                         | ACT #1                        | DS #2 | ACT #4 | ACT #5 | ACT #6                | ACT #7               | ACT #8                   | ACT #9 | ACT #10                 | ACT #12                        | ACT #13 | ACT #14 | ACT #15                   | DS #4 | DS #5 | DS #6 |

|------------|--------------------------------|-------------------------------|-------|--------|--------|-----------------------|----------------------|--------------------------|--------|-------------------------|--------------------------------|---------|---------|---------------------------|-------|-------|-------|

| P8.0       | tcpwm[0].i<br>ne[0]:2          | tcpwm[1].line<br>[16]:0       |       |        |        | scb[4].ua<br>rt_rx:0  | scb[4].i2<br>c_scl:0 | scb[4].spi<br>_mosi:0    |        |                         | peri.tr_i<br>o_i<br>nput[16]:0 |         |         |                           |       |       |       |

| P8.1       | tcpwm[0].i<br>ne_comp<br>[0]:2 | tcpwm[1].line<br>_compl[16]:0 |       |        |        | scb[4].ua<br>rt_tx:0  | scb[4].i2<br>c_sda:0 | scb[4].spi<br>_miso:0    |        |                         | peri.tr_i<br>o_i<br>nput[17]:0 |         |         |                           |       |       |       |

| P8.2       | tcpwm[0].i<br>ne[1]:2          | tcpwm[1].line<br>[17]:0       |       |        |        | scb[4].ua<br>rt_rts:0 |                      | scb[4].spi<br>_clk:0     |        |                         |                                |         |         |                           |       |       |       |

| P8.3       | tcpwm[0].i<br>ne_comp<br>[1]:2 | tcpwm[1].line<br>_compl[17]:0 |       |        |        | scb[4].ua<br>rt_cts:0 |                      | scb[4].spi<br>_select0:0 |        |                         |                                |         |         |                           |       |       |       |

| P8.4       | tcpwm[0].i<br>ne[2]:2          | tcpwm[1].line<br>[18]:0       |       |        |        |                       |                      | scb[4].spi<br>_select1:0 |        |                         |                                |         |         |                           |       |       |       |

| P8.5       | tcpwm[0].i<br>ne_comp<br>[2]:2 | tcpwm[1].line<br>_compl[18]:0 |       |        |        |                       |                      | scb[4].spi<br>_select2:0 |        |                         |                                |         |         |                           |       |       |       |

| P8.6       | tcpwm[0].i<br>ne[3]:2          | tcpwm[1].line<br>[19]:0       |       |        |        |                       |                      | scb[4].spi<br>_select3:0 |        |                         |                                |         |         |                           |       |       |       |

| P8.7       | tcpwm[0].i<br>ne_comp<br>[3]:2 | tcpwm[1].line<br>_compl[19]:0 |       |        |        |                       |                      | scb[3].spi<br>_select2:0 |        |                         |                                |         |         |                           |       |       |       |

| P9.0       | tcpwm[0].i<br>ne[4]:2          | tcpwm[1].line<br>[20]:0       |       |        |        | scb[2].ua<br>rt_rx:0  | scb[2].i2<br>c_scl:0 | scb[2].spi<br>_mosi:0    |        |                         | peri.tr_i<br>o_i<br>nput[18]:0 |         |         | cpuss.trac<br>e_data[3]:0 |       |       |       |

| P9.1       | tcpwm[0].i<br>ne_comp<br>[4]:2 | tcpwm[1].line<br>_compl[20]:0 |       |        |        | scb[2].ua<br>rt_tx:0  | scb[2].i2<br>c_sda:0 | scb[2].spi<br>_miso:0    |        |                         | peri.tr_i<br>o_i<br>nput[19]:0 |         |         | cpuss.trac<br>e_data[2]:0 |       |       |       |

| P9.2       | tcpwm[0].i<br>ne[5]:2          | tcpwm[1].line<br>[21]:0       |       |        |        | scb[2].ua<br>rt_rts:0 |                      | scb[2].spi<br>_clk:0     |        | pass.dsi_ct<br>b_cmp0:1 |                                |         |         | cpuss.trac<br>e_data[1]:0 |       |       |       |

| P9.3       | tcpwm[0].i<br>ne_comp<br>[5]:2 | tcpwm[1].line<br>_compl[21]:0 |       |        |        | scb[2].ua<br>rt_cts:0 |                      | scb[2].spi<br>_select0:0 |        | pass.dsi_ct<br>b_cmp1:1 |                                |         |         | cpuss.trac<br>e_data[0]:0 |       |       |       |

| P9.4       | tcpwm[0].i<br>ne[7]:5          | tcpwm[1].line<br>[0]:2        |       |        |        |                       |                      | scb[2].spi<br>_select1:0 |        |                         |                                |         |         |                           |       |       |       |

| P9.5       | tcpwm[0].i<br>ne_comp<br>[7]:5 | tcpwm[1].line<br>_compl[0]:2  |       |        |        |                       |                      | scb[2].spi<br>_select2:0 |        |                         |                                |         |         |                           |       |       |       |

| P9.6       | tcpwm[0].i<br>ne[0]:6          | tcpwm[1].line<br>[1]:2        |       |        |        |                       |                      | scb[2].spi<br>_select3:0 |        |                         |                                |         |         |                           |       |       |       |

| P9.7       | tcpwm[0].i<br>ne_comp<br>[0]:6 | tcpwm[1].line<br>_compl[1]:2  |       |        |        |                       |                      |                          |        |                         |                                |         |         |                           |       |       |       |

| P10.0      | tcpwm[0].i<br>ne[6]:2          | tcpwm[1].line<br>[22]:0       |       |        |        | scb[1].ua<br>rt_rx:1  | scb[1].i2<br>c_scl:1 | scb[1].spi<br>_mosi:1    |        |                         | peri.tr_i<br>o_i<br>nput[20]:0 |         |         | cpuss.trac<br>e_data[3]:1 |       |       |       |

| P10.1      | tcpwm[0].i<br>ne_comp<br>[6]:2 | tcpwm[1].line<br>_compl[22]:0 |       |        |        | scb[1].ua<br>rt_tx:1  | scb[1].i2<br>c_sda:1 | scb[1].spi<br>_miso:1    |        |                         | peri.tr_i<br>o_i<br>nput[21]:0 |         |         | cpuss.trac<br>e_data[2]:1 |       |       |       |

表 2. 複数の代替機能 ( 続き )

| ポート／<br>ピン | ACT #0                         | ACT #1                        | DS #2 | ACT #4 | ACT #5                | ACT #6                | ACT #7                   | ACT #8                   | ACT #9              | ACT #10 | ACT #12                    | ACT #13                    | ACT #14 | ACT #15                   | DS #4 | DS #5 | DS #6 |

|------------|--------------------------------|-------------------------------|-------|--------|-----------------------|-----------------------|--------------------------|--------------------------|---------------------|---------|----------------------------|----------------------------|---------|---------------------------|-------|-------|-------|

| P10.2      | tcpwm[0].i<br>ne[7]:2          | tcpwm[1].line<br>[23]:0       |       |        | scb[1].ua<br>rt_rts:1 |                       | scb[1].spi<br>_clk:1     |                          |                     |         |                            |                            |         | cpuss.trac<br>e_data[1]:1 |       |       |       |

| P10.3      | tcpwm[0].i<br>ne_comp<br>[7]:2 | tcpwm[1].line<br>_compl[23]:0 |       |        | scb[1].ua<br>rt_cts:1 |                       | scb[1].spi<br>_select0:1 |                          |                     |         |                            |                            |         | cpuss.trac<br>e_data[0]:1 |       |       |       |

| P10.4      | tcpwm[0].i<br>ne[0]:3          | tcpwm[1].line<br>[0]:1        |       |        |                       |                       | scb[1].spi<br>_select1:1 | audioss.p<br>dm_clk      |                     |         |                            |                            |         |                           |       |       |       |

| P10.5      | tcpwm[0].i<br>ne_comp<br>[0]:3 | tcpwm[1].line<br>_compl[0]:1  |       |        |                       |                       | scb[1].spi<br>_select2:1 | audioss.p<br>dm_data     |                     |         |                            |                            |         |                           |       |       |       |

| P10.6      | tcpwm[0].i<br>ne[1]:6          | tcpwm[1].line<br>[2]:2        |       |        |                       |                       | scb[1].spi<br>_select3:1 |                          |                     |         |                            |                            |         |                           |       |       |       |

| P10.7      | tcpwm[0].i<br>ne_comp<br>[1]:6 | tcpwm[1].line<br>_compl[2]:2  |       |        |                       |                       |                          |                          |                     |         |                            |                            |         |                           |       |       |       |

| P11.0      | tcpwm[0].i<br>ne[1]:3          | tcpwm[1].line<br>[1]:1        |       |        | smif.spi<br>_select2  | scb[5].ua<br>rt_rx:1  | scb[5].i2<br>c_scl:1     | scb[5].spi<br>_mosi:1    |                     |         | peri.tr.io.i<br>nput[22]:0 |                            |         |                           |       |       |       |

| P11.1      | tcpwm[0].i<br>ne_comp<br>[1]:3 | tcpwm[1].line<br>_compl[1]:1  |       |        | smif.spi<br>_select1  | scb[5].ua<br>rt_tx:1  | scb[5].i2<br>c_sda:1     | scb[5].spi<br>_miso:1    |                     |         | peri.tr.io.i<br>nput[23]:0 |                            |         |                           |       |       |       |

| P11.2      | tcpwm[0].i<br>ne[2]:3          | tcpwm[1].line<br>[2]:1        |       |        | smif.spi<br>_select0  | scb[5].ua<br>rt_rts:1 |                          | scb[5].spi<br>_clk:1     |                     |         |                            |                            |         |                           |       |       |       |

| P11.3      | tcpwm[0].i<br>ne_comp<br>[2]:3 | tcpwm[1].line<br>_compl[2]:1  |       |        | smif.spi<br>_data3    | scb[5].ua<br>rt_cts:1 |                          | scb[5].spi<br>_select0:1 |                     |         |                            | peri.tr.io.o<br>utput[0]:0 |         |                           |       |       |       |

| P11.4      | tcpwm[0].i<br>ne[3]:3          | tcpwm[1].line<br>[3]:1        |       |        | smif.spi<br>_data2    |                       |                          | scb[5].spi<br>_select1:1 |                     |         |                            | peri.tr.io.o<br>utput[1]:0 |         |                           |       |       |       |

| P11.5      | tcpwm[0].i<br>ne_comp<br>[3]:3 | tcpwm[1].line<br>_compl[3]:1  |       |        | smif.spi<br>_data1    |                       |                          | scb[5].spi<br>_select2:1 |                     |         |                            |                            |         |                           |       |       |       |

| P11.6      |                                |                               |       |        | smif.spi<br>_data0    |                       |                          | scb[5].spi<br>_select3:1 |                     |         |                            |                            |         |                           |       |       |       |

| P11.7      |                                |                               |       |        | smif.spi<br>_clk      |                       |                          |                          |                     |         |                            |                            |         |                           |       |       |       |

| P12.0      | tcpwm[0].i<br>ne[4]:3          | tcpwm[1].line<br>[4]:1        |       |        | smif.spi<br>_data4    | scb[6].ua<br>rt_rx:0  | scb[6].i2<br>c_scl:0     | scb[6].spi<br>_mosi:0    |                     |         | peri.tr.io.i<br>nput[24]:0 |                            |         |                           |       |       |       |

| P12.1      | tcpwm[0].i<br>ne_comp<br>[4]:3 | tcpwm[1].line<br>_compl[4]:1  |       |        | smif.spi<br>_data5    | scb[6].ua<br>rt_tx:0  | scb[6].i2<br>c_sda:0     | scb[6].spi<br>_miso:0    |                     |         | peri.tr.io.i<br>nput[25]:0 |                            |         |                           |       |       |       |

| P12.2      | tcpwm[0].i<br>ne[5]:3          | tcpwm[1].line<br>[5]:1        |       |        | smif.spi<br>_data6    | scb[6].ua<br>rt_rts:0 |                          | scb[6].spi<br>_clk:0     |                     |         |                            |                            |         |                           |       |       |       |

| P12.3      | tcpwm[0].i<br>ne_comp<br>[5]:3 | tcpwm[1].line<br>_compl[5]:1  |       |        | smif.spi<br>_data7    | scb[6].ua<br>rt_cts:0 |                          | scb[6].spi<br>_select0:0 |                     |         |                            |                            |         |                           |       |       |       |

| P12.4      | tcpwm[0].i<br>ne[6]:3          | tcpwm[1].line<br>[6]:1        |       |        | smif.spi<br>_select3  |                       |                          | scb[6].spi<br>_select1:0 | audioss.p<br>dm_clk |         |                            |                            |         |                           |       |       |       |

**表 2. 複数の代替機能 ( 続き )**

| ポート／<br>ピン | ACT #0                          | ACT #1                        | DS #2 | ACT #4 | ACT #5                | ACT #6               | ACT #7                   | ACT #8                   | ACT #9               | ACT #10                    | ACT #12 | ACT #13 | ACT #14 | ACT #15 | DS #4 | DS #5 | DS #6 |

|------------|---------------------------------|-------------------------------|-------|--------|-----------------------|----------------------|--------------------------|--------------------------|----------------------|----------------------------|---------|---------|---------|---------|-------|-------|-------|

| P12.5      | tcpwm[0].l<br>ine_comp<br>[6]:3 | tcpwm[1].line<br>_compl[6]:1  |       |        |                       |                      |                          | scb[6].spi<br>_select2:0 | audioss.p<br>dm_data |                            |         |         |         |         |       |       |       |

| P12.6      | tcpwm[0].l<br>ine[7]:3          | tcpwm[1].line<br>[7]:1        |       |        |                       |                      |                          | scb[6].spi<br>_select3:0 |                      |                            |         |         |         |         |       |       |       |

| P12.7      | tcpwm[0].l<br>ine_comp<br>[7]:3 | tcpwm[1].line<br>_compl[7]:1  |       |        |                       |                      |                          |                          |                      |                            |         |         |         |         |       |       |       |

| P13.0      | tcpwm[0].l<br>ine[0]:4          | tcpwm[1].line<br>[8]:1        |       |        | scb[6].ua<br>rt_rx:1  | scb[6].i2<br>c_scl:1 | scb[6].spi<br>_mosi:1    |                          |                      | peri.tr_io_i<br>nput[26]:0 |         |         |         |         |       |       |       |

| P13.1      | tcpwm[0].l<br>ine_comp<br>[0]:4 | tcpwm[1].line<br>_compl[8]:1  |       |        | scb[6].ua<br>rt_tx:1  | scb[6].i2<br>c_sda:1 | scb[6].spi<br>_miso:1    |                          |                      | peri.tr_io_i<br>nput[27]:0 |         |         |         |         |       |       |       |

| P13.2      | tcpwm[0].l<br>ine[1]:4          | tcpwm[1].line<br>[9]:1        |       |        | scb[6].ua<br>rt_rts:1 |                      | scb[6].spi<br>_clk:1     |                          |                      |                            |         |         |         |         |       |       |       |

| P13.3      | tcpwm[0].l<br>ine_comp<br>[1]:4 | tcpwm[1].line<br>_compl[9]:1  |       |        | scb[6].ua<br>rt_cts:1 |                      | scb[6].spi<br>_select0:1 |                          |                      |                            |         |         |         |         |       |       |       |

| P13.4      | tcpwm[0].l<br>ine[2]:4          | tcpwm[1].line<br>[10]:1       |       |        |                       |                      | scb[6].spi<br>_select1:1 |                          |                      |                            |         |         |         |         |       |       |       |

| P13.5      | tcpwm[0].l<br>ine_comp<br>[2]:4 | tcpwm[1].line<br>_compl[10]:1 |       |        |                       |                      | scb[6].spi<br>_select2:1 |                          |                      |                            |         |         |         |         |       |       |       |

| P13.6      | tcpwm[0].l<br>ine[3]:4          | tcpwm[1].line<br>[11]:1       |       |        |                       |                      | scb[6].spi<br>_select3:1 |                          |                      |                            |         |         |         |         |       |       |       |

| P13.7      | tcpwm[0].l<br>ine_comp<br>[3]:4 | tcpwm[1].line<br>_compl[11]:1 |       |        |                       |                      |                          |                          |                      |                            |         |         |         |         |       |       |       |

アナログ、Smart I/O および DSI 代替ポートピン機能を表 3 に示されます。

表 3. ポート ピン アナログ、Smart I/O および DSI 機能

| ポート／ピン | 名称    | アナログ             | デジタル HV                               | DSI               | SMARTIO | USB            |

|--------|-------|------------------|---------------------------------------|-------------------|---------|----------------|

| P0.0   | P0.0  | wco_in           |                                       | dsi[0].port_if[0] |         |                |

| P0.1   | P0.1  | wco_out          |                                       | dsi[0].port_if[1] |         |                |

| P0.2   | P0.2  |                  |                                       | dsi[0].port_if[2] |         |                |

| P0.3   | P0.3  |                  |                                       | dsi[0].port_if[3] |         |                |

| P0.4   | P0.4  |                  | pmic_wakeup_in<br>hibernate_wakeup[1] | dsi[0].port_if[4] |         |                |

| P0.5   | P0.5  |                  | pmic_wakeup_out                       | dsi[0].port_if[5] |         |                |

| P1.0   | P1.0  |                  |                                       | dsi[1].port_if[0] |         |                |

| P1.1   | P1.1  |                  |                                       | dsi[1].port_if[1] |         |                |

| P1.2   | P1.2  |                  |                                       | dsi[1].port_if[2] |         |                |

| P1.3   | P1.3  |                  |                                       | dsi[1].port_if[3] |         |                |

| P1.4   | P1.4  |                  | hibernate_wakeup[0]                   | dsi[1].port_if[4] |         |                |

| P1.5   | P1.5  |                  |                                       | dsi[1].port_if[5] |         |                |

| P14.0  | USBDP |                  |                                       |                   |         | usb.usb_dp_pad |

| P14.1  | USBDM |                  |                                       |                   |         | usb.usb_dm_pad |

| P2.0   | P2.0  |                  |                                       | dsi[2].port_if[0] |         |                |

| P2.1   | P2.1  |                  |                                       | dsi[2].port_if[1] |         |                |

| P2.2   | P2.2  |                  |                                       | dsi[2].port_if[2] |         |                |

| P2.3   | P2.3  |                  |                                       | dsi[2].port_if[3] |         |                |

| P2.4   | P2.4  |                  |                                       | dsi[2].port_if[4] |         |                |

| P2.5   | P2.5  |                  |                                       | dsi[2].port_if[5] |         |                |

| P2.6   | P2.6  |                  |                                       | dsi[2].port_if[6] |         |                |

| P2.7   | P2.7  |                  |                                       | dsi[2].port_if[7] |         |                |

| P3.0   | P3.0  |                  |                                       |                   |         |                |

| P3.1   | P3.1  |                  |                                       |                   |         |                |

| P3.2   | P3.2  |                  |                                       |                   |         |                |

| P3.3   | P3.3  |                  |                                       |                   |         |                |

| P3.4   | P3.4  |                  |                                       |                   |         |                |

| P3.5   | P3.5  |                  |                                       |                   |         |                |

| P4.0   | P4.0  |                  |                                       | dsi[0].port_if[6] |         |                |

| P4.1   | P4.1  |                  |                                       | dsi[0].port_if[7] |         |                |

| P4.2   | P4.2  |                  |                                       | dsi[1].port_if[6] |         |                |

| P4.3   | P4.3  |                  |                                       | dsi[1].port_if[7] |         |                |

| P5.0   | P5.0  |                  |                                       | dsi[3].port_if[0] |         |                |

| P5.1   | P5.1  |                  |                                       | dsi[3].port_if[1] |         |                |

| P5.2   | P5.2  |                  |                                       | dsi[3].port_if[2] |         |                |

| P5.3   | P5.3  |                  |                                       | dsi[3].port_if[3] |         |                |

| P5.4   | P5.4  |                  |                                       | dsi[3].port_if[4] |         |                |

| P5.5   | P5.5  |                  |                                       | dsi[3].port_if[5] |         |                |

| P5.6   | P5.6  | lpcomp.inp_comp0 |                                       | dsi[3].port_if[6] |         |                |

| P5.7   | P5.7  | lpcomp.inn_comp0 |                                       | dsi[3].port_if[7] |         |                |

**表3. ポート ピン アナログ、Smart I/O および DSI 機能 ( 続き )**

| ポート／<br>ピン | 名称    | アナログ                                 | デジタル HV  | DSI                | SMARTIO          | USB |

|------------|-------|--------------------------------------|----------|--------------------|------------------|-----|

| P6.0       | P6.0  |                                      |          | dsi[4].port_if[0]  |                  |     |

| P6.1       | P6.1  |                                      |          | dsi[4].port_if[1]  |                  |     |

| P6.2       | P6.2  | lpcomp.inp_comp1                     |          | dsi[4].port_if[2]  |                  |     |

| P6.3       | P6.3  | lpcomp.inn_comp1                     |          | dsi[4].port_if[3]  |                  |     |

| P6.4       | P6.4  |                                      |          | dsi[4].port_if[4]  |                  |     |

| P6.5       | P6.5  |                                      |          | dsi[4].port_if[5]  |                  |     |

| P6.6       | P6.6  |                                      | swd_data | dsi[4].port_if[6]  |                  |     |

| P6.7       | P6.7  |                                      | swd_clk  | dsi[4].port_if[7]  |                  |     |

| P7.0       | P7.0  |                                      |          | dsi[5].port_if[0]  |                  |     |

| P7.1       | P7.1  | csd.cmodpadd<br>csd.cmodpads         |          | dsi[5].port_if[1]  |                  |     |

| P7.2       | P7.2  | csd.csh_tankpadd<br>csd.csh_tankpads |          | dsi[5].port_if[2]  |                  |     |

| P7.3       | P7.3  | csd.vref_ext                         |          | dsi[5].port_if[3]  |                  |     |

| P7.4       | P7.4  |                                      |          | dsi[5].port_if[4]  |                  |     |

| P7.5       | P7.5  |                                      |          | dsi[5].port_if[5]  |                  |     |

| P7.6       | P7.6  |                                      |          | dsi[5].port_if[6]  |                  |     |

| P7.7       | P7.7  | csd.cshieldpads                      |          | dsi[5].port_if[7]  |                  |     |

| P8.0       | P8.0  |                                      |          | dsi[11].port_if[0] | smartio[8].io[0] |     |

| P8.1       | P8.1  |                                      |          | dsi[11].port_if[1] | smartio[8].io[1] |     |

| P8.2       | P8.2  |                                      |          | dsi[11].port_if[2] | smartio[8].io[2] |     |

| P8.3       | P8.3  |                                      |          | dsi[11].port_if[3] | smartio[8].io[3] |     |

| P8.4       | P8.4  |                                      |          | dsi[11].port_if[4] | smartio[8].io[4] |     |

| P8.5       | P8.5  |                                      |          | dsi[11].port_if[5] | smartio[8].io[5] |     |

| P8.6       | P8.6  |                                      |          | dsi[11].port_if[6] | smartio[8].io[6] |     |

| P8.7       | P8.7  |                                      |          | dsi[11].port_if[7] | smartio[8].io[7] |     |

| P9.0       | P9.0  | ctb_oa0+                             |          | dsi[10].port_if[0] | smartio[9].io[0] |     |

| P9.1       | P9.1  | ctb_oa0-                             |          | dsi[10].port_if[1] | smartio[9].io[1] |     |

| P9.2       | P9.2  | ctb_oa0_out                          |          | dsi[10].port_if[2] | smartio[9].io[2] |     |

| P9.3       | P9.3  | ctb_oa1_out                          |          | dsi[10].port_if[3] | smartio[9].io[3] |     |

| P9.4       | P9.4  | ctb_oa1-                             |          | dsi[10].port_if[4] | smartio[9].io[4] |     |

| P9.5       | P9.5  | ctb_oa1+                             |          | dsi[10].port_if[5] | smartio[9].io[5] |     |

| P9.6       | P9.6  | ctb_oa0+                             |          | dsi[10].port_if[6] | smartio[9].io[6] |     |

| P9.7       | P9.7  | ctb_oa1+<br>または ext_vref             |          | dsi[10].port_if[7] | smartio[9].io[7] |     |

| P10.0      | P10.0 | sarmux[0]                            |          | dsi[9].port_if[0]  |                  |     |

| P10.1      | P10.1 | sarmux[1]                            |          | dsi[9].port_if[1]  |                  |     |

| P10.2      | P10.2 | sarmux[2]                            |          | dsi[9].port_if[2]  |                  |     |

| P10.3      | P10.3 | sarmux[3]                            |          | dsi[9].port_if[3]  |                  |     |

| P10.4      | P10.4 | sarmux[4]                            |          | dsi[9].port_if[4]  |                  |     |

| P10.5      | P10.5 | sarmux[5]                            |          | dsi[9].port_if[5]  |                  |     |

**表3. ポート ピン アナログ、Smart I/O および DSI 機能 ( 続き )**

| ポート／<br>ピン | 名称    | アナログ         | デジタル HV | DSI               | SMARTIO | USB |

|------------|-------|--------------|---------|-------------------|---------|-----|

| P10.6      | P10.6 | sarmux[6]    |         | dsi[9].port_if[6] |         |     |

| P10.7      | P10.7 | sarmux[7]    |         | dsi[9].port_if[7] |         |     |

| P11.0      | P11.0 |              |         | dsi[8].port_if[0] |         |     |

| P11.1      | P11.1 |              |         | dsi[8].port_if[1] |         |     |

| P11.2      | P11.2 |              |         | dsi[8].port_if[2] |         |     |

| P11.3      | P11.3 |              |         | dsi[8].port_if[3] |         |     |

| P11.4      | P11.4 |              |         | dsi[8].port_if[4] |         |     |

| P11.5      | P11.5 |              |         | dsi[8].port_if[5] |         |     |

| P11.6      | P11.6 |              |         | dsi[8].port_if[6] |         |     |

| P11.7      | P11.7 |              |         | dsi[8].port_if[7] |         |     |

| P12.0      | P12.0 |              |         | dsi[7].port_if[0] |         |     |

| P12.1      | P12.1 |              |         | dsi[7].port_if[1] |         |     |

| P12.2      | P12.2 |              |         | dsi[7].port_if[2] |         |     |

| P12.3      | P12.3 |              |         | dsi[7].port_if[3] |         |     |

| P12.4      | P12.4 |              |         | dsi[7].port_if[4] |         |     |

| P12.5      | P12.5 |              |         | dsi[7].port_if[5] |         |     |

| P12.6      | P12.6 | srss.eco_in  |         | dsi[7].port_if[6] |         |     |

| P12.7      | P12.7 | srss.eco_out |         | dsi[7].port_if[7] |         |     |

| P13.0      | P13.0 |              |         | dsi[6].port_if[0] |         |     |

| P13.1      | P13.1 |              |         | dsi[6].port_if[1] |         |     |

| P13.2      | P13.2 |              |         | dsi[6].port_if[2] |         |     |

| P13.3      | P13.3 |              |         | dsi[6].port_if[3] |         |     |

| P13.4      | P13.4 |              |         | dsi[6].port_if[4] |         |     |

| P13.5      | P13.5 |              |         | dsi[6].port_if[5] |         |     |

| P13.6      | P13.6 |              |         | dsi[6].port_if[6] |         |     |

| P13.7      | P13.7 |              |         | dsi[6].port_if[7] |         |     |

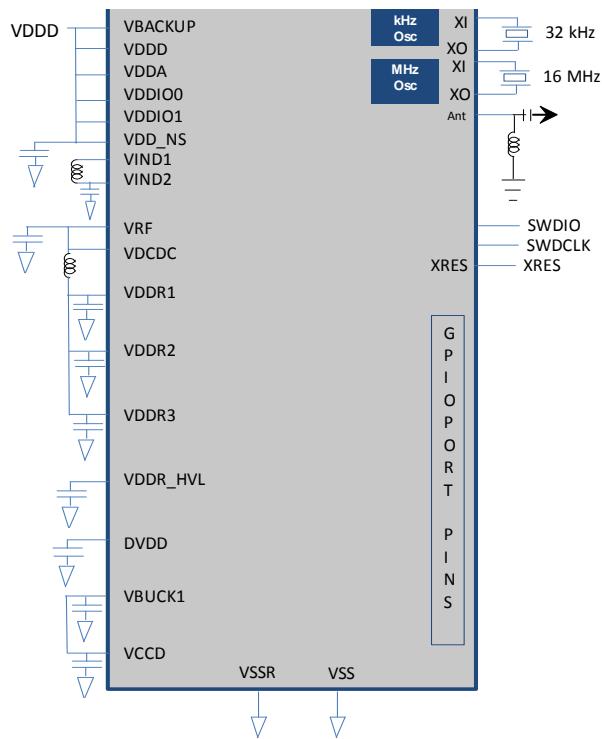

## 電源

電源システム図 (図 3 を参照) は、PSoC 63 の電源ピンの一般的な要件を示します。この図には、デカッピングが必要な無線ピンも示されています。PSoC 63 の電源スキームにより、異なる VDDIO と VDDA の接続が可能になります。シーケンス要件を分析および指定する必要がないため、ユーザーは電源を任意の順序で提供することができ、電源システムは動作を開始する前にすべてのドメインで電力が良好であることを保証する責任を負います。VDDIO、VDDA および VDDIO は、チップ上にオーミック接続されていない別個のネットである場合があります。異なるパッケージ要件に応じて、これらはチップ外で接続する必要があります。

電源システムは LDO に加えて降圧レギュレータを備えています。複数の出力を備えた単入力多出力 (SIMO) 降圧レギュレータにより、インダクタを使用しなくてもよく、無線ブロックに高効率の電源を供給することができます。

図 3 に示します。

図 3. 無線ブロックとの SOC 電源接続 (104-CSP および 116-BGA パッケージ)

図 3 は、PSoC への電源ピンおよび PSoC と無線ブロックとの接続を示します。また、どのピンにバイパス コンデンサが必要かを示します。

電源ピンの説明は以下の通りです。

1. VBACKUP はバックアップ ドメインへの電源です。バックアップ ドメインは、32kHz WCO、RTC およびバックアップ レジスタを含み、RTC タイマーまたは外部入力によりチップにウェイクアップ割込みを生成することができます。RTC タイマーまたは外部入力により、ウェイクアップ 割り込みをチップに生成できます。また、外部回路をウェイクアップするための出力も生成することもできます。別のバッテリ バックアップ ドメインとして使用されない場合、VDDD に接続されます。VBACKUP はポート 0 に電源供給します。

2. VDDD は主デジタル電源入力 (1.7 ~ 3.6V) であり、内部レギュレータとポート 1 への入力を提供します。

3. VDDA はアナログ ペリフェラルの電源です (1.7 ~ 3.6V)。これは PCB 上の VDDIOA に接続する必要があります。

4. VDDIOA はポート 9 と 10 への電源です。提供される場合、PCB 上の VDDA に接続する必要があります。VDDIOA が提供されない場合、ポート 9 および 10 は VDDA によって給電されます。

5. VDD\_NS は降圧レギュレータへの電源入力であり、VDDD と同じ電位でなければなりません。VDD\_NS とグランド間のバイパス コンデンサは  $10\mu\text{F}$  でなければなりません。

6. VDDIO0 は、提供される場合、ポート 11 ~ 13 の電源です。そうでない場合、これらのポートは VDDD によって供給されます。

7. VDDIO1 は、提供される場合、ポート 5 ~ 8 の電源です。そうでない場合、これらのポートは VDDA によって供給されます。

8. VDDIOR は BGA 124 でのみポート 2 ~ 4 の電源です。

図 3 に示すように、上記のピンはすべて VDDD に短絡可能です。

9. VRF は無線ブロックへの SIMO 降圧レギュレータの出力であり、VDCDC に接続してデカップリングする必要があります。

10. VDCDC は無線ブロックへのデジタル電源入力で、VRF に接続する必要があります。

11. VDDR1、VDDR2 および VDDR3 ピンは無線ブロックのサブシステムに使用されますが、個別にデカップリングし、高周波電源ノイズをフィルタリングするためにビーズを介して VDCDC に接続する必要があります。

12. VDDR\_HVL は、PSoC 63 サブシステムからの無線ブロックへの調整された出力であり、デカップリングする必要があります。

13. DVDD は、無線ブロックからのデジタル LDO 出力であり、デカップリングする必要があります。

14. VBUCK1 は、内部コア ロジックへの SIMO 降圧レギュレータ出力であり、VCCD に接続する必要があります。

15. VCCD は内部コア ロジックであり、VBUCK1 に接続してデカップリングする必要があります。

電源電圧範囲は 1.71V ~ 3.6V で、すべての機能と回路がその範囲において動作します。すべてのグランド ピンを PCB 上で短絡する必要があります。バイパス コンデンサは、VDDD と VDDA からグランド および 図に示されているとおり使用する必要があります。この周波数範囲でのシステムの標準的な値は、 $10\mu\text{F}$  レンジのコンデンサをより小さいコンデンサ ( 例えば  $0.1\mu\text{F}$  ) と並列で使用します。これらは単に経験則であり、重要なアプリケーションに対しては、設計に最適なバイパスを得るために、PCB レイアウト、リード インダクタンス、バイパス コンデンサ寄生容量をシミュレートする必要があることにご留意ください。降圧レギュレータ出力コンデンサの推奨値は  $\text{Vrf}$  の場合に  $10\mu\text{F}$ 、VBUCK1 の場合に  $4.7\mu\text{F}$  です。Vind2 に接続されるコンデンサは  $100\text{nF}$  である必要があります。すべてのコンデンサは  $\pm 20\%$  またはそれより高精度のもので、インダクタの推奨値は  $2.2\mu\text{H} \pm 20\%$  です。

( 例えば、TDK MLP2012H2R2MT0S1)。

## 開発サポート

PSoC 63 ファミリには、ユーザーの開発プロセスを支援する豊富なドキュメント、開発ツールおよびオンライン リソースが用意されています。詳細については <http://www.cypress.com/products/32-bit-arm-cortex-m4-psoc-6> をご覧ください。

### ドキュメント